#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                  |

|---------------------------------|---------------------------------------------------------------------------|

| Core Processor                  | ARM1136JF-S                                                               |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                            |

| Speed                           | 532MHz                                                                    |

| Co-Processors/DSP               | Multimedia; GPU, IPU, MPEG-4, VFP                                         |

| RAM Controllers                 | DDR                                                                       |

| Graphics Acceleration           | Yes                                                                       |

| Display & Interface Controllers | Keyboard, Keypad, LCD                                                     |

| Ethernet                        | -                                                                         |

| SATA                            | -                                                                         |

| USB                             | USB 2.0 (3)                                                               |

| Voltage - I/O                   | 1.8V, 2.0V, 2.5V, 2.7V, 3.0V                                              |

| Operating Temperature           | 0°C ~ 70°C (TA)                                                           |

| Security Features               | Random Number Generator, RTIC, Secure Fusebox, Secure JTAG, Secure Memory |

| Package / Case                  | 457-LFBGA                                                                 |

| Supplier Device Package         | 457-LFBGA (14x14)                                                         |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx31vkn5r2     |

|                                 |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Block<br>Mnemonic | Block Name                                   | Functional<br>Grouping     | Brief Description                                                                                                                                                                              | Section/<br>Page        |  |  |  |  |

|-------------------|----------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|--|--|--|

| Fusebox           | Fusebox                                      | ROM                        | The Fusebox is a ROM that is factory configured by Freescale.                                                                                                                                  |                         |  |  |  |  |

| GPIO              | General<br>Purpose I/O<br>Module             | Pins                       | The GPIO provides several groups of 32-bit bidirectional, general purpose I/O. This peripheral provides dedicated general-purpose signals that can be configured as either inputs or outputs.  | _                       |  |  |  |  |

| GPT               | General<br>Purpose Timer                     | Timer<br>Peripheral        | The GPT is a multipurpose module used to measure intervals or generate periodic output.                                                                                                        | _                       |  |  |  |  |

| GPU               | Graphics<br>Processing Unit                  | Multimedia<br>Peripheral   | The GPU provides hardware acceleration for 2D and 3D graphics algorithms.                                                                                                                      | _                       |  |  |  |  |

| l <sup>2</sup> C  | Inter IC<br>Communication                    | Connectivity<br>Peripheral | The I <sup>2</sup> C provides serial interface for controlling the Sensor Interface<br>and other external devices. Data rates of up to 100 Kbits/s are<br>supported.                           | 4.3.13/56               |  |  |  |  |

| IIM               | IC Identification<br>Module                  | ID                         | The IIM provides an interface for reading device identification.                                                                                                                               | _                       |  |  |  |  |

| IPU               | Image<br>Processing Unit                     | Multimedia<br>Peripheral   | The IPU processes video and graphics functions in the MCIMX31 and interfaces to video, still image sensors, and displays.                                                                      | 4.3.14/57,<br>4.3.15/59 |  |  |  |  |

| KPP               | Keypad Port                                  | Connectivity<br>Peripheral | The KPP is used for keypad matrix scanning or as a general purpose I/O. This peripheral simplifies the software task of scanning a keypad matrix.                                              | _                       |  |  |  |  |

| MPEG-4            | MPEG-4 Video<br>Encoder                      | Multimedia<br>Peripherals  | The MPEG-4 encoder accelerates video compression, following the MPEG-4 standard                                                                                                                | _                       |  |  |  |  |

| MSHC              | Memory Stick<br>Host Controller              | Connectivity<br>Peripheral | The MSHC is placed in between the AIPS and the customer memory stick to support data transfer from the MCIMX31 to the customer memory stick.                                                   | 4.3.16/84               |  |  |  |  |

| PADIO             | Pads I/O                                     | Buffers and<br>Drivers     | The PADIO serves as the interface between the internal modules and the device's external connections.                                                                                          | 4.3.1/22                |  |  |  |  |

| PCMCIA            | РСМ                                          | Connectivity<br>Peripheral | The PCMCIA Host Adapter provides the control logic for PCMCIA socket interfaces.                                                                                                               | 4.3.17/86               |  |  |  |  |

| PWM               | Pulse-Width<br>Modulator                     | Timer<br>Peripheral        | The PWM has a 16-bit counter and is optimized to generate sound from stored sample audio images. It can also generate tones.                                                                   | 4.3.18/88               |  |  |  |  |

| RNGA              | Random<br>Number<br>Generator<br>Accelerator | Security                   | The RNGA module is a digital integrated circuit capable of generating 32-bit random numbers. It is designed to comply with FIPS-140 standards for randomness and non-determinism.              | _                       |  |  |  |  |

| RTC               | Real Time Clock                              | Timer<br>Peripheral        | The RTC module provides a current stamp of seconds, minutes, hours, and days. Alarm and timer functions are also available for programming. The RTC supports dates from the year 1980 to 2050. | —                       |  |  |  |  |

| RTIC              | Run-Time<br>Integrity<br>Checkers            | Security                   | The RTIC ensures the integrity of the peripheral memory contents and assists with boot authentication.                                                                                         |                         |  |  |  |  |

# 4 Electrical Characteristics

This section provides the device-level and module-level electrical characteristics for the MCIMX31.

## 4.1 Chip-Level Conditions

This section provides the device-level electrical characteristics for the IC. See Table 4 for a quick reference to the individual tables and sections.

| For these characteristics,                                              | Topic appears |

|-------------------------------------------------------------------------|---------------|

| Table 5, "Absolute Maximum Ratings"                                     | on page 10    |

| Table 7, "Thermal Resistance Data—19 $\times$ 19 mm Package"            | on page 11    |

| Table 8, "Operating Ranges"                                             | on page 13    |

| Table 9, "Specific Operating Ranges for Silicon Revision 2.0"           | on page 14    |

| Table 10, "Interface Frequency"                                         | on page 14    |

| Section 4.1.1, "Supply Current Specifications"                          | on page 16    |

| Section 4.2, "Supply Power-Up/Power-Down Requirements and Restrictions" | on page 19    |

Table 4. MCIMX31 Chip-Level Conditions

### CAUTION

Stresses beyond those listed under Table 5 may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under Table 8, "Operating Ranges," on page 13 is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

| Parameter                                                 | Symbol                                | Min  | Max       | Units |

|-----------------------------------------------------------|---------------------------------------|------|-----------|-------|

| Supply Voltage (Core)                                     | QVCC <sub>max</sub>                   | -0.5 | 1.65      | V     |

| Supply Voltage (I/O)                                      | NVCC <sub>max</sub>                   | -0.5 | 3.3       | V     |

| Input Voltage Range                                       | V <sub>Imax</sub>                     | -0.5 | NVCC +0.3 | V     |

| Storage Temperature                                       | T <sub>storage</sub>                  | -40  | 125       | °C    |

| ESD Damage Immunity:                                      |                                       |      |           |       |

| Human Body Model (HBM)                                    | V                                     | —    | 1500      | V     |

| Machine Model (MM)                                        | V <sub>esd</sub>                      | —    | 200       | v     |

| Charge Device Model (CDM)                                 |                                       | —    | 500       |       |

| Offset voltage allowed in run mode between core supplies. | V <sub>core_offset</sub> <sup>1</sup> | _    | 15        | mV    |

<sup>1</sup> The offset is the difference between all core voltage pair combinations of QVCC, QVCC1, and QVCC4.

Table 6 provides the thermal resistance data for the  $14 \times 14$  mm, 0.5 mm pitch package.

| Rating                                       | Board                   | Symbol              | Value | Unit | Notes   |

|----------------------------------------------|-------------------------|---------------------|-------|------|---------|

| Junction to Ambient (natural convection)     | Single layer board (1s) | $R_{	ext{	heta}JA}$ | 56    | °C/W | 1, 2, 3 |

| Junction to Ambient (natural convection)     | Four layer board (2s2p) | $R_{	ext{	heta}JA}$ | 30    | °C/W | 1, 3    |

| Junction to Ambient (@200 ft/min)            | Single layer board (1s) | $R_{\thetaJMA}$     | 46    | °C/W | 1, 2, 3 |

| Junction to Ambient (@200 ft/min)            | Four layer board (2s2p) | $R_{\thetaJMA}$     | 26    | °C/W | 1, 3    |

| Junction to Board                            | —                       | $R_{\theta JB}$     | 17    | °C/W | 1, 4    |

| Junction to Case                             | —                       | $R_{	ext{	heta}JC}$ | 10    | °C/W | 1, 5    |

| Junction to Package Top (natural convection) | —                       | $\Psi_{JT}$         | 2     | °C/W | 1, 6    |

### Table 6. Thermal Resistance Data—14 imes 14 mm Package

### NOTES

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per JEDEC JESD51-2 with the single layer board horizontal. Board meets JESD51-9 specification.

- 3. Per JEDEC JESD51-6 with the board horizontal.

- 4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- 6. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

Table 7 provides the thermal resistance data for the  $19 \times 19$  mm, 0.8 mm pitch package.

| Rating                                       | Board                   | Symbol               | Value | Unit | Notes   |

|----------------------------------------------|-------------------------|----------------------|-------|------|---------|

| Junction to Ambient (natural convection)     | Single layer board (1s) | $R_{	ext{	heta}JA}$  | 46    | °C/W | 1, 2, 3 |

| Junction to Ambient (natural convection)     | Four layer board (2s2p) | $R_{	ext{	heta}JA}$  | 29    | °C/W | 1, 2, 3 |

| Junction to Ambient (@200 ft/min)            | Single layer board (1s) | $R_{	ext{	heta}JMA}$ | 38    | °C/W | 1, 2, 3 |

| Junction to Ambient (@200 ft/min)            | Four layer board (2s2p) | $R_{	ext{	heta}JMA}$ | 25    | °C/W | 1, 2, 3 |

| Junction to Board                            | _                       | $R_{	heta JB}$       | 19    | °C/W | 1, 3    |

| Junction to Case (Top)                       | _                       | $R_{\theta JCtop}$   | 10    | °C/W | 1, 4    |

| Junction to Package Top (natural convection) | _                       | $\Psi_{JT}$          | 2     | °C/W | 1, 5    |

Table 7. Thermal Resistance Data—19 imes 19 mm Package

## 4.2 Supply Power-Up/Power-Down Requirements and Restrictions

Any MCIMX31 board design must comply with the power-up and power-down sequence guidelines as described in this section to guarantee reliable operation of the device. Any deviation from these sequences may result in any or all of the following situations:

- Cause excessive current during power up phase

- Prevent the device from booting

- Cause irreversible damage to the MCIMX31 (worst-case scenario)

## 4.2.1 Powering Up

The Power On Reset ( $\overline{POR}$ ) pin must be kept asserted (low) throughout the power up sequence. Power up logic must guarantee that all power sources reach their target values prior to the release (de-assertion) of  $\overline{POR}$ . Figure 2 shows the power-up sequence for silicon Revisions 1.2 and previous. Figure 3 and Figure 4 show the power-up sequence for silicon Revision 2.0.

### NOTE

Stages need to be performed in the order shown; however, *within* each stage, supplies can be powered up in any order. For example, supplies IOQVDD, NVCC1, and NVCC3 through NVCC10 do not need to be powered up in the order shown.

### CAUTION

NVCC6 and NVCC9 must be at the same voltage potential. These supplies are connected together on-chip to optimize ESD damage immunity.

## 4.3.5.2 PIO Mode Timing

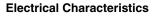

Figure 11 shows timing for PIO read, and Table 25 lists the timing parameters for PIO read.

Figure 11. PIO Read Timing Diagram

| Table 25. PIO Read Timing Parameters |                             |                                                                                                                                                                                                               |                                |  |  |

|--------------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--|--|

| ATA<br>Parameter                     | Parameter<br>from Figure 11 | Value                                                                                                                                                                                                         | Controlling<br>Variable        |  |  |

| t1                                   | t1                          | t1 (min) = time_1 * T - (tskew1 + tskew2 + tskew5)                                                                                                                                                            | time_1                         |  |  |

| t2                                   | t2r                         | t2 min) = time_2r * T - (tskew1 + tskew2 + tskew5)                                                                                                                                                            | time_2r                        |  |  |

| t9                                   | t9                          | t9 (min) = time_9 * T - (tskew1 + tskew2 + tskew6)                                                                                                                                                            | time_3                         |  |  |

| t5                                   | t5                          | t5 (min) = tco + tsu + tbuf + tbuf + tcable1 + tcable2                                                                                                                                                        | If not met, increase<br>time_2 |  |  |

| t6                                   | t6                          | 0                                                                                                                                                                                                             | —                              |  |  |

| tA                                   | tA                          | $tA (min) = (1.5 + time_ax) * T - (tco + tsui + tcable2 + tcable2 + 2*tbuf)$                                                                                                                                  | time_ax                        |  |  |

| trd                                  | trd1                        | $\label{eq:trd1} \begin{array}{l} (max) = (-trd) + (tskew3 + tskew4) \\ trd1 \ (min) = (time\_pio\_rdx - 0.5)^{*}T - (tsu + thi) \\ (time\_pio\_rdx - 0.5) \ ^{*}T > tsu + thi + tskew3 + tskew4 \end{array}$ | time_pio_rdx                   |  |  |

| tO                                   | —                           | t0 (min) = (time_1 + time_2 + time_9) * T                                                                                                                                                                     | time_1, time_2r, time_9        |  |  |

Figure 12 shows timing for PIO write, and Table 26 lists the timing parameters for PIO write.

| Parameter                                 | Min | Тур | Max | Unit | Comments                                   |

|-------------------------------------------|-----|-----|-----|------|--------------------------------------------|

| Phase lock time                           | —   | _   | 100 | μs   | In addition to the frequency               |

| Maximum allowed PLL supply voltage ripple | —   | _   | 25  | mV   | F <sub>modulation</sub> < 50 kHz           |

| Maximum allowed PLL supply voltage ripple |     | _   | 20  | mV   | 50 kHz < F <sub>modulation</sub> < 300 kHz |

| Maximum allowed PLL supply voltage ripple |     | _   | 25  | mV   | F <sub>modulation</sub> > 300 kHz          |

| PLL output clock phase jitter             | _   | _   | 5.2 | ns   | Measured on CLKO pin                       |

| PLL output clock period jitter            | —   | _   | 420 | ps   | Measured on CLKO pin                       |

### Table 31. DPLL Specifications (continued)

<sup>1</sup> The user or board designer must take into account that the use of a frequency other than 26 MHz would require adjustment to the DPTC–DVFS table, which is incorporated into operating system code.

<sup>2</sup> The PLL reference frequency must be ≤ 35 MHz. Therefore, for frequencies between 35 MHz and 70 MHz, program the predivider to divide by 2 or more. If the CKIH frequency is above 70 MHz, program the predivider to 3 or more. For PD bit description, see the reference manual.

## 4.3.9 EMI Electrical Specifications

This section provides electrical parametrics and timings for EMI module.

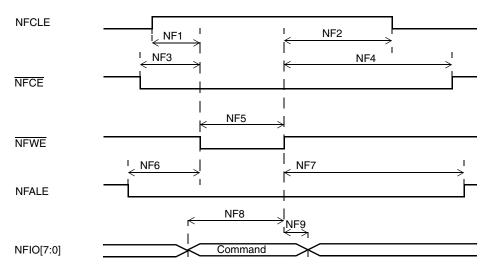

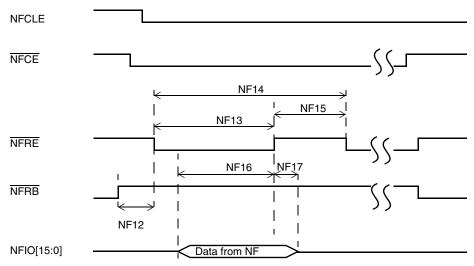

## 4.3.9.1 NAND Flash Controller Interface (NFC)

The NFC supports normal timing mode, using two flash clock cycles for one access of  $\overline{\text{RE}}$  and  $\overline{\text{WE}}$ . AC timings are provided as multiplications of the clock cycle and fixed delay. Figure 23, Figure 24, Figure 25, and Figure 26 depict the relative timing requirements among different signals of the NFC at module level, for normal mode, and Table 32 lists the timing parameters.

Figure 23. Command Latch Cycle Timing Dlagram

Figure 26. Read Data Latch Cycle Timing Dlagram

| ID   | Parameter           | Symbol | Timing<br>ymbol T = NFC Clock Cycle <sup>2</sup> |        | Example Timing for NFC Clock $\approx$ 33 MHz T = 30 ns |     | Unit |

|------|---------------------|--------|--------------------------------------------------|--------|---------------------------------------------------------|-----|------|

|      |                     |        | Min                                              | Max    | Min                                                     | Мах |      |

| NF1  | NFCLE Setup Time    | tCLS   | T–1.0 ns                                         | _      | 29                                                      | _   | ns   |

| NF2  | NFCLE Hold Time     | tCLH   | T–2.0 ns                                         | _      | 28                                                      | _   | ns   |

| NF3  | NFCE Setup Time     | tCS    | T–1.0 ns                                         |        | 29                                                      | _   | ns   |

| NF4  | NFCE Hold Time      | tCH    | T–2.0 ns                                         | _      | 28                                                      | _   | ns   |

| NF5  | NF_WP Pulse Width   | tWP    | T–1.5 ns                                         |        | 28.5                                                    |     | ns   |

| NF6  | NFALE Setup Time    | tALS   | Т                                                | _      | 30                                                      | _   | ns   |

| NF7  | NFALE Hold Time     | tALH   | T–3.0 ns                                         | _      | 27                                                      | _   | ns   |

| NF8  | Data Setup Time     | tDS    | Т                                                | _      | 30                                                      | _   | ns   |

| NF9  | Data Hold Time      | tDH    | T–5.0 ns                                         | _      | 25                                                      | _   | ns   |

| NF10 | Write Cycle Time    | tWC    | 2T                                               |        | 60                                                      |     | ns   |

| NF11 | NFWE Hold Time      | tWH    | T–2                                              | 2.5 ns | 27.5                                                    |     | ns   |

| NF12 | Ready to NFRE Low   | tRR    | 6T                                               | _      | 180                                                     | _   | ns   |

| NF13 | NFRE Pulse Width    | tRP    | 1.5T                                             | _      | 45                                                      | _   | ns   |

| NF14 | READ Cycle Time     | tRC    | 2T                                               |        | 60                                                      | _   | ns   |

| NF15 | NFRE High Hold Time | tREH   | 0.5T–2.5 ns                                      |        | 12.5                                                    | _   | ns   |

| NF16 | Data Setup on READ  | tDSR   | 1                                                | N/A    | 10                                                      | —   | ns   |

| NF17 | Data Hold on READ   | tDHR   | 1                                                | N/A    | 0                                                       | _   | ns   |

| Table 32. NFC | Timing | Parameters <sup>1</sup> |

|---------------|--------|-------------------------|

|---------------|--------|-------------------------|

<sup>1</sup> The flash clock maximum frequency is 50 MHz.

<sup>2</sup> Subject to DPLL jitter specification on Table 31, "DPLL Specifications," on page 37.

| ID   | Parameter                           | Symbol | Min | Max | Unit  |

|------|-------------------------------------|--------|-----|-----|-------|

| SD9  | Data out hold time <sup>1</sup>     | tOH    | 1.8 | _   | ns    |

| SD10 | Active to read/write command period | tRC    | 10  | _   | clock |

#### Table 34. DDR/SDR SDRAM Read Cycle Timing Parameters (continued)

<sup>1</sup> Timing parameters are relevant only to SDR SDRAM. For the specific DDR SDRAM data related timing parameters, see Table 38 and Table 39.

### NOTE

SDR SDRAM CLK parameters are being measured from the 50% point—that is, high is defined as 50% of signal value and low is defined as 50% of signal value. SD1 + SD2 does not exceed 7.5 ns for 133 MHz.

The timing parameters are similar to the ones used in SDRAM data sheets—that is, Table 34 indicates SDRAM requirements. All output signals are driven by the ESDCTL at the negative edge of SDCLK and the parameters are measured at maximum memory frequency.

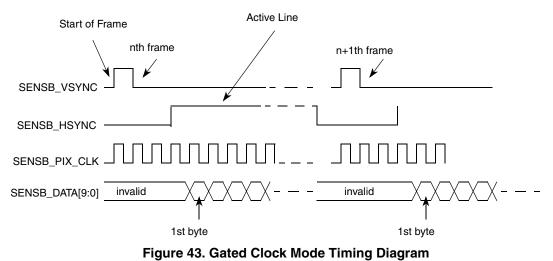

## 4.3.14.2.2 Gated Clock Mode

The SENSB\_VSYNC, SENSB\_HSYNC, and SENSB\_PIX\_CLK signals are used in this mode. See Figure 43.

A frame starts with a rising edge on SENSB\_VSYNC (all the timings correspond to straight polarity of the corresponding signals). Then SENSB\_HSYNC goes to high and hold for the entire line. Pixel clock is valid as long as SENSB\_HSYNC is high. Data is latched at the rising edge of the valid pixel clocks. SENSB\_HSYNC goes to low at the end of line. Pixel clocks then become invalid and the CSI stops receiving data from the stream. For next line the SENSB\_HSYNC timing repeats. For next frame the SENSB\_VSYNC timing repeats.

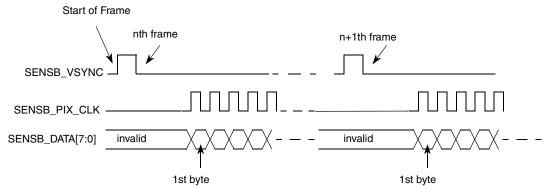

## 4.3.14.2.3 Non-Gated Clock Mode

The timing is the same as the gated-clock mode (described in Section 4.3.14.2.2, "Gated Clock Mode"), except for the SENSB\_HSYNC signal, which is not used. See Figure 44. All incoming pixel clocks are valid and will cause data to be latched into the input FIFO. The SENSB\_PIX\_CLK signal is inactive (states low) until valid data is going to be transmitted over the bus.

Figure 44. Non-Gated Clock Mode Timing Diagram

<sup>2</sup> Display interface clock down time

$$\[ dicd = \frac{1}{2}T_{\text{HSP}\_\text{CLK}} \cdot \text{ceil} \left[ \frac{2 \cdot \text{DISP3}\_\text{IF}\_\text{CLK}\_\text{DOWN}\_\text{WR}}{\text{HSP}\_\text{CLK}\_\text{PERIOD}} \right]$$

<sup>3</sup> Display interface clock up time

$Tdicu = \frac{1}{2}T_{HSP\_CLK} \cdot ceil \left[\frac{2 \cdot DISP3\_IF\_CLK\_UP\_WR}{HSP\_CLK\_PERIOD}\right]$

where CEIL(X) rounds the elements of X to the nearest integers towards infinity.

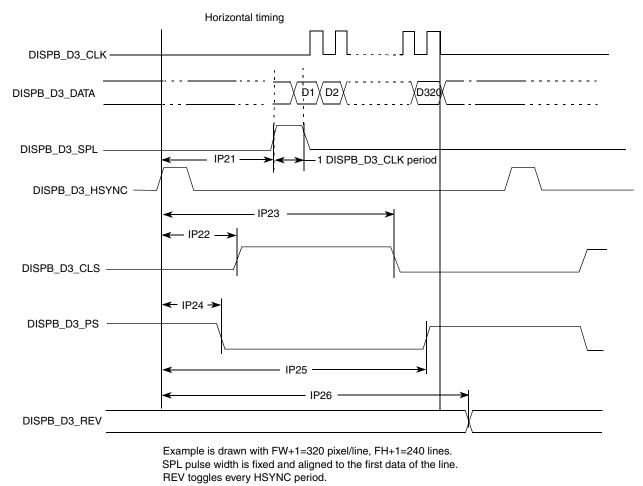

## 4.3.15.3 Interface to Sharp HR-TFT Panels

Figure 50 depicts the Sharp HR-TFT panel interface timing, and Table 49 lists the timing parameters. The CLS\_RISE\_DELAY, CLS\_FALL\_DELAY, PS\_FALL\_DELAY, PS\_RISE\_DELAY, REV\_TOGGLE\_DELAY parameters are defined in the SDC\_SHARP\_CONF\_1 and SDC\_SHARP\_CONF\_2 registers. For other Sharp interface timing characteristics, refer to Section 4.3.15.2.2, "Interface to Active Matrix TFT LCD Panels, Electrical Characteristics." The timing images correspond to straight polarity of the Sharp signals.

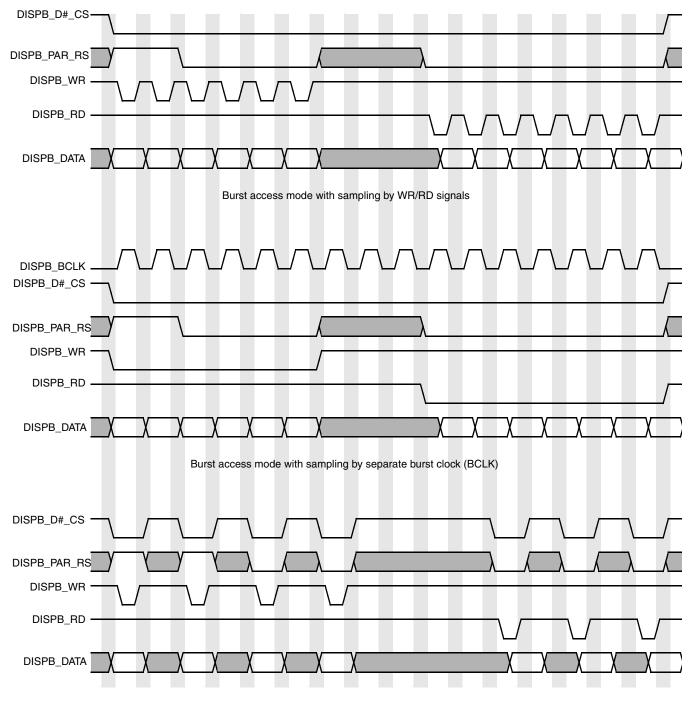

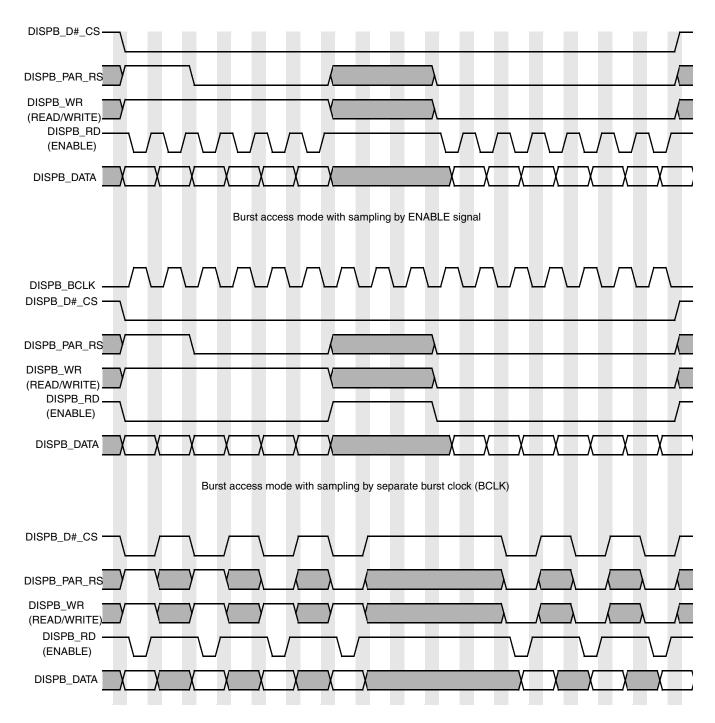

Single access mode (all control signals are not active for one display interface clock after each display access)

Figure 53. Asynchronous Parallel System 80 Interface (Type 2) Burst Mode Timing Diagram

Single access mode (all control signals are not active for one display interface clock after each display access)

### Figure 55. Asynchronous Parallel System 68k Interface (Type 2) Burst Mode Timing Diagram

Display read operation can be performed with wait states when each read access takes up to four display interface clock cycles according to the DISP0\_RD\_WAIT\_ST parameter in the DI\_DISP0\_TIME\_CONF\_3, DI\_DISP1\_TIME\_CONF\_3, DI\_DISP2\_TIME\_CONF\_3 Registers. Figure 56 shows timing of the parallel interface with read wait states.

Figure 64 depicts timing of the 5-wire serial interface (Type 2). For this interface, a separate RS line is added. When a burst is transmitted within single active chip select interval, the RS can be changed at boundaries of words.

Figure 64. 5-Wire Serial Interface (Type 2) Timing Diagram

| ID   | Parameter                                | Symbol | Min.                 | Typ. <sup>1</sup> | Max.                                              | Units |

|------|------------------------------------------|--------|----------------------|-------------------|---------------------------------------------------|-------|

| IP56 | Controls setup time for write            | Tdcsw  | Tdicuw–1.5           | Tdicuw            | —                                                 | ns    |

| IP57 | Controls hold time for write             | Tdchw  | Tdicpw-Tdicdw-1.5    | Tdicpw-Tdicdw     | —                                                 | ns    |

| IP58 | Slave device data delay <sup>8</sup>     | Tracc  | 0                    | —                 | Tdrp <sup>9</sup> –Tlbd <sup>10</sup> –Tdicur–1.5 | ns    |

| IP59 | Slave device data hold time <sup>8</sup> | Troh   | Tdrp-Tlbd-Tdicdr+1.5 | —                 | Tdicpr-Tdicdr-1.5                                 | ns    |

| IP60 | Write data setup time                    | Tds    | Tdicdw-1.5           | Tdicdw            | —                                                 | ns    |

| IP61 | Write data hold time                     | Tdh    | Tdicpw-Tdicdw-1.5    | Tdicpw-Tdicdw     | —                                                 | ns    |

| IP62 | Read period <sup>2</sup>                 | Tdicpr | Tdicpr–1.5           | Tdicpr            | Tdicpr+1.5                                        | ns    |

| IP63 | Write period <sup>3</sup>                | Tdicpw | Tdicpw-1.5           | Tdicpw            | Tdicpw+1.5                                        | ns    |

| IP64 | Read down time <sup>4</sup>              | Tdicdr | Tdicdr-1.5           | Tdicdr            | Tdicdr+1.5                                        | ns    |

| IP65 | Read up time <sup>5</sup>                | Tdicur | Tdicur–1.5           | Tdicur            | Tdicur+1.5                                        | ns    |

| IP66 | Write down time <sup>6</sup>             | Tdicdw | Tdicdw-1.5           | Tdicdw            | Tdicdw+1.5                                        | ns    |

| IP67 | Write up time <sup>7</sup>               | Tdicuw | Tdicuw-1.5           | Tdicuw            | Tdicuw+1.5                                        | ns    |

| IP68 | Read time point <sup>9</sup>             | Tdrp   | Tdrp-1.5             | Tdrp              | Tdrp+1.5                                          | ns    |

Table 51. Asynchronous Serial Interface Timing Parameters—Access Level (continued)

<sup>1</sup> The exact conditions have not been finalized, but will likely match the current customer requirement for their specific display. These conditions may be device specific.

<sup>2</sup> Display interface clock period value for read:

$Tdicpr = T_{HSP\_CLK} \cdot ceil \left[ \frac{DISP\#\_IF\_CLK\_PER\_RD}{HSP\_CLK\_PERIOD} \right]$

<sup>3</sup> Display interface clock period value for write:

$Tdicpw = T_{HSP\_CLK} \cdot ceil \left[ \frac{DISP\#\_IF\_CLK\_PER\_WR}{HSP\_CLK\_PERIOD} \right]$

<sup>4</sup> Display interface clock down time for read:

$Tdicdr = \frac{1}{2}T_{HSP\_CLK} \cdot ceil \left[\frac{2 \cdot DISP\#\_IF\_CLK\_DOWN\_RD}{HSP\_CLK\_PERIOD}\right]$

<sup>5</sup> Display interface clock up time for read:

$Tdicur = \frac{1}{2}T_{HSP\_CLK} \cdot ceil \left[\frac{2 \cdot DISP\#\_IF\_CLK\_UP\_RD}{HSP\_CLK\_PERIOD}\right]$

<sup>6</sup> Display interface clock down time for write:

$$\begin{bmatrix} \text{dicdw} &= \frac{1}{2} \text{T}_{\text{HSP}\_\text{CLK}} \cdot \text{ceil} \begin{bmatrix} \frac{2 \cdot \text{DISP}\#\_\text{IF}\_\text{CLK}\_\text{DOWN}\_\text{WR}}{\text{HSP}\_\text{CLK}\_\text{PERIOD}} \end{bmatrix}$$

<sup>7</sup> Display interface clock up time for write:

- <sup>8</sup> This parameter is a requirement to the display connected to the IPU.

- <sup>9</sup> Data read point:

$drp = T_{HSP_CLK} \cdot ceil \left[ \frac{DISP\#_READ_EN}{HSP_CLK_PERIOD} \right]$

<sup>10</sup> Loopback delay Tlbd is the cumulative propagation delay of read controls and read data. It includes an IPU output delay, a device-level output delay, board delays, a device-level input delay, an IPU input delay. This value is device specific.

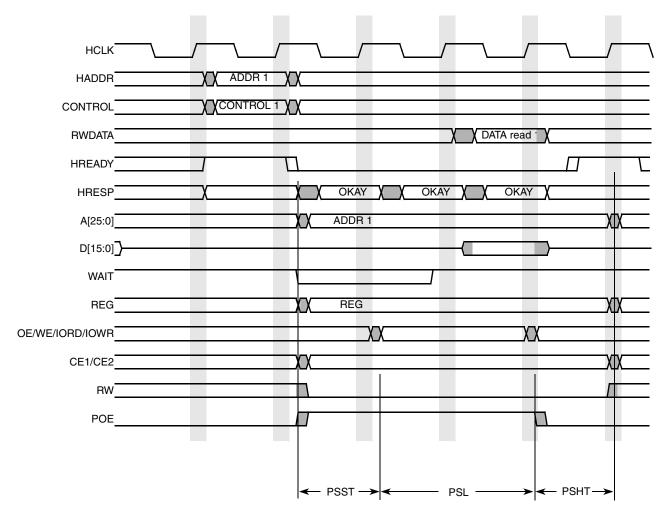

Figure 70. Read Accesses Timing Diagram—PSHT=1, PSST=1

| Symbol | Parameter                 | Min | Max | Unit  |

|--------|---------------------------|-----|-----|-------|

| PSHT   | PCMCIA strobe hold time   | 0   | 63  | clock |

| PSST   | PCMCIA strobe set up time | 1   | 63  | clock |

| PSL    | PCMCIA strobe length      | 1   | 128 | clock |

## 4.3.18 PWM Electrical Specifications

This section describes the electrical information of the PWM. The PWM can be programmed to select one of three clock signals as its source frequency. The selected clock signal is passed through a prescaler before being input to the counter. The output is available at the pulse-width modulator output (PWMO) external pin.

| ID       | Parameter                                      | Min   | Мах  | Unit |

|----------|------------------------------------------------|-------|------|------|

| External | Clock Operation                                |       |      | 1    |

| SS22     | (Tx/Rx) CK clock period                        | 81.4  | —    | ns   |

| SS23     | (Tx/Rx) CK clock high period                   | 36.0  | —    | ns   |

| SS24     | (Tx/Rx) CK clock rise time                     | _     | 6.0  | ns   |

| SS25     | (Tx/Rx) CK clock low period                    | 36.0  | —    | ns   |

| SS26     | (Tx/Rx) CK clock fall time                     | _     | 6.0  | ns   |

| SS27     | (Tx) CK high to FS (bl) high                   | -10.0 | 15.0 | ns   |

| SS29     | (Tx) CK high to FS (bl) low                    | 10.0  | —    | ns   |

| SS31     | (Tx) CK high to FS (wl) high                   | -10.0 | 15.0 | ns   |

| SS33     | (Tx) CK high to FS (wl) low                    | 10.0  | —    | ns   |

| SS37     | (Tx) CK high to STXD valid from high impedance | —     | 15.0 | ns   |

| SS38     | (Tx) CK high to STXD high/low                  | —     | 15.0 | ns   |

| SS39     | (Tx) CK high to STXD high impedance            | —     | 15.0 | ns   |

| Synchro  | nous External Clock Operation                  |       |      |      |

| SS44     | SRXD setup before (Tx) CK falling              | 10.0  | —    | ns   |

| SS45     | SRXD hold after (Tx) CK falling                | 2.0   | —    | ns   |

| SS46     | SRXD rise/fall time                            | —     | 6.0  | ns   |

|          |                                                |       |      |      |

Table 62. SSI Transmitter with External Clock Timing Parameters

| ID   | Parameter                          | Min   | Max  | Unit |

|------|------------------------------------|-------|------|------|

| SS28 | (Rx) CK high to FS (bl) high       | -10.0 | 15.0 | ns   |

| SS30 | (Rx) CK high to FS (bl) low        | 10.0  | _    | ns   |

| SS32 | (Rx) CK high to FS (wl) high       | -10.0 | 15.0 | ns   |

| SS34 | (Rx) CK high to FS (wl) low        | 10.0  | _    | ns   |

| SS35 | (Tx/Rx) External FS rise time      | —     | 6.0  | ns   |

| SS36 | (Tx/Rx) External FS fall time      | —     | 6.0  | ns   |

| SS40 | SRXD setup time before (Rx) CK low | 10.0  | _    | ns   |

| SS41 | SRXD hold time after (Rx) CK low   | 2.0   | _    | ns   |

Table 63. SSI Receiver with External Clock Timing Parameters (continued)

## 4.3.23 USB Electrical Specifications

This section describes the electrical information of the USBOTG port. The OTG port supports both serial and parallel interfaces.

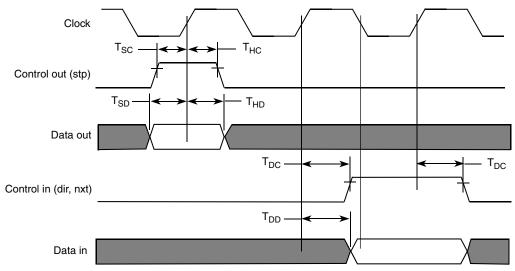

The high speed (HS) interface is supported via the ULPI (Ultra Low Pin Count Interface). Figure 85 depicts the USB ULPI timing diagram, and Table 64 lists the timing parameters.

Figure 85. USB ULPI Interface Timing Diagram

| Parameter                                  | Symbol   | Min | Мах | Units |

|--------------------------------------------|----------|-----|-----|-------|

| Setup time (control in, 8-bit data in)     | TSC, TSD | 6   | _   | ns    |

| Hold time (control in, 8-bit data in)      | THC, THD | 0   | _   | ns    |

| Output delay (control out, 8-bit data out) | TDC, TDD | _   | 9   | ns    |

<sup>1</sup> Timing parameters are given as viewed by transceiver side.

## 5.1.3.2 BGA Signal ID by Ball Grid Location–14 x 14 0.5 mm

Table 66 shows the device connection list for signals only, alpha-sorted by signal identification.

| Table 66. 14 x 14 BGA Signal ID by E | Ball Grid Location |

|--------------------------------------|--------------------|

|--------------------------------------|--------------------|

| A0         AD0           A1         AF           A10         AF1           A11         AC           A11         AC           A12         AD0           A13         AD0           A14         AF1           A15         AF1           A16         AF1           A18         AF1           A2         AB3 | 5<br>8<br>3<br>3<br>4<br>7<br>6<br>5<br>5<br>4<br>3<br>2 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| A10         AF1           A11         AC           A12         AD           A13         AD           A14         AF1           A15         AF1           A16         AF1           A18         AF1           A22         AB           A20         AF1                                                   | 8<br>3<br>3<br>4<br>7<br>6<br>5<br>4<br>3<br>2           |

| A11         AC           A12         AD           A13         AD           A13         AD           A14         AF1           A15         AF1           A16         AF1           A17         AF1           A18         AF1           A2         AB           A20         AF1                           | 3<br>3<br>4<br>7<br>6<br>5<br>4<br>3<br>2                |

| A12         AD3           A13         AD4           A13         AD4           A14         AF1           A15         AF1           A16         AF1           A17         AF1           A18         AF1           A19         AF1           A2         AB3           A20         AF1                      | 3<br>4<br>7<br>6<br>5<br>4<br>3<br>2                     |

| A13         AD4           A14         AF1           A15         AF1           A16         AF1           A17         AF1           A18         AF1           A19         AF1           A2         AB3           A20         AF1                                                                          | 4<br>7<br>6<br>5<br>4<br>3<br>2                          |

| A14         AF1           A15         AF1           A16         AF1           A17         AF1           A18         AF1           A19         AF1           A2         AB3           A20         AF1                                                                                                    | 7<br>6<br>5<br>4<br>3<br>2                               |

| A15         AF1           A16         AF1           A17         AF1           A18         AF1           A19         AF1           A2         AB3           A20         AF1                                                                                                                              | 6<br>5<br>4<br>3<br>2                                    |

| A16         AF1           A17         AF1           A18         AF1           A19         AF1           A2         AB3           A20         AF1                                                                                                                                                        | 5<br>4<br>3<br>2                                         |

| A17         AF1           A18         AF1           A19         AF1           A2         AB3           A20         AF1                                                                                                                                                                                  | 4<br>3<br>2                                              |

| A18         AF1           A19         AF1           A2         AB3           A20         AF1                                                                                                                                                                                                            | 3<br>2                                                   |

| A19         AF1           A2         AB3           A20         AF1                                                                                                                                                                                                                                      | 2                                                        |

| A2 AB3<br>A20 AF1                                                                                                                                                                                                                                                                                       |                                                          |

| A20 AF1                                                                                                                                                                                                                                                                                                 |                                                          |

|                                                                                                                                                                                                                                                                                                         | 5                                                        |

|                                                                                                                                                                                                                                                                                                         | 1                                                        |

| A21 AF1                                                                                                                                                                                                                                                                                                 | 0                                                        |

| A22 AFS                                                                                                                                                                                                                                                                                                 | 9                                                        |

| A23 AF8                                                                                                                                                                                                                                                                                                 | 8                                                        |

| A24 AF                                                                                                                                                                                                                                                                                                  | 7                                                        |

| A25 AF6                                                                                                                                                                                                                                                                                                 | 6                                                        |

| A3 AE4                                                                                                                                                                                                                                                                                                  | 4                                                        |

| A4 AA:                                                                                                                                                                                                                                                                                                  | 3                                                        |

| A5 AF4                                                                                                                                                                                                                                                                                                  | 4                                                        |

| A6 AB:                                                                                                                                                                                                                                                                                                  | 3                                                        |

| A7 AE                                                                                                                                                                                                                                                                                                   | 3                                                        |

| A8 AD                                                                                                                                                                                                                                                                                                   | 5                                                        |

| A9 AF:                                                                                                                                                                                                                                                                                                  | 3                                                        |

| ATA_CS0 J6                                                                                                                                                                                                                                                                                              |                                                          |

| ATA_CS1 F2                                                                                                                                                                                                                                                                                              |                                                          |

| ATA_DIOR E2                                                                                                                                                                                                                                                                                             |                                                          |

| ATA_DIOW H6                                                                                                                                                                                                                                                                                             | ;                                                        |

| ATA_DMACK F1                                                                                                                                                                                                                                                                                            |                                                          |

| ATA_RESET H3                                                                                                                                                                                                                                                                                            | ;                                                        |

| BATT_LINE F7                                                                                                                                                                                                                                                                                            |                                                          |

| BCLK AB2                                                                                                                                                                                                                                                                                                | 26                                                       |

| BOOT_MODE0 F20                                                                                                                                                                                                                                                                                          | )                                                        |

| BOOT_MODE1 C2 <sup>-</sup>                                                                                                                                                                                                                                                                              | 1                                                        |

| BOOT_MODE2 D24                                                                                                                                                                                                                                                                                          | 4                                                        |

| BOOT_MODE3 C22                                                                                                                                                                                                                                                                                          | 2                                                        |

| BOOT_MODE4 D26                                                                                                                                                                                                                                                                                          | 6                                                        |

| CAPTURE A22                                                                                                                                                                                                                                                                                             | 2                                                        |

| CAS AD2                                                                                                                                                                                                                                                                                                 | 20                                                       |

| CE_CONTROL A14                                                                                                                                                                                                                                                                                          | 4                                                        |

| CKIH F24                                                                                                                                                                                                                                                                                                | 4                                                        |

| Signal ID     | Ball Location |

|---------------|---------------|

| CKIL          | H21           |

| CLKO          | C23           |

| CLKSS         | G26           |

| COMPARE       | G18           |

| CONTRAST      | R24           |

| CS0           | AE23          |

| CS1           | AF23          |

| CS2           | AE21          |

| CS3           | AD22          |

| CS4           | AF24          |

| CS5           | AF22          |

| CSI_D10       | M24           |

| CSI_D11       | L26           |

| CSI_D12       | M21           |

| <br>CSI_D13   | M25           |

| <br>CSI_D14   | M20           |

| CSI D15       | M26           |

| CSI_D4        | L21           |

| CSI_D5        | K25           |

| CSI_D6        | L24           |

| <br>CSI_D7    | K26           |

| CSI_D8        | L20           |

| CSI_D9        | L25           |

| <br>CSI_HSYNC | K20           |

| CSI_MCLK      | K24           |

| CSI_PIXCLK    | J26           |

| CSI_VSYNC     | J25           |

| CSPI1_MISO    | P7            |

| CSPI1_MOSI    | P2            |

| CSPI1 SCLK    | N2            |

| CSPI1_SPI_RDY | N3            |

| CSPI1 SS0     | P3            |

| CSPI1_SS1     | P1            |

| CSPI1_SS2     | P6            |

| CSPI2_MISO    | A4            |

| CSPI2_MOSI    | E3            |

| CSPI2_SCLK    | C7            |

| CSPI2_SPI_RDY | B6            |

| CSPI2_SS0     | B5            |

| CSPI2_SS1     | C6            |

| CSPI2_SS2     | A5            |

| CSPI3_MISO    | G3            |

| CSPI3_MOSI    | D2            |

| - |  |

|---|--|

| - |  |

| ω |  |

|   |  |

### Table 71. Ball Map—19 x 19 0.8 mm Pitch

|    |                   |                |               |                   |                  |                  |                  | Та               | ble 7          | '1. Ba       | ll Map       | —19 x          | 19 0.        | 8 mm         | Pitch        | 1            |                |                |             |                |                  |               |                |     |

|----|-------------------|----------------|---------------|-------------------|------------------|------------------|------------------|------------------|----------------|--------------|--------------|----------------|--------------|--------------|--------------|--------------|----------------|----------------|-------------|----------------|------------------|---------------|----------------|-----|

|    | 1                 | 2              | 3             | 4                 | 5                | 6                | 7                | 8                | 9              | 10           | 11           | 12             | 13           | 14           | 15           | 16           | 17             | 18             | 19          | 20             | 21               | 22            | 23             | 7   |

| A  | GND               | GND            | GND           | CSPI2_<br>SS1     | USBOTG_<br>DATA6 | USBOTG<br>_DATA2 | USBOTG<br>_DIR   | USB_<br>PWR      | CTS1           | DTR_<br>DTE1 | DSR_<br>DTE1 | RXD2           | KEY_<br>ROW0 | KEY_<br>ROW3 | KEY_<br>COL0 | KEY_<br>COL5 | KEY_<br>COL7   | TDI            | SRX0        | COMPARE        | GND              | GND           | GND            | A   |

| в  | GND               | GND            | STXD4         | CSPI2_<br>MISO    | CSPI2_<br>SCLK   | USBOTG_<br>DATA5 | USBOTG_<br>NXT   | USB_<br>OC       | RTS1           | DSR_<br>DCE1 | RI_<br>DTE1  | RTS2           | KEY_<br>ROW1 | KEY_<br>ROW6 | KEY_<br>COL1 | KEY_<br>COL6 | TDO            | SIMPD0         | SCLK0       | GPIO1_2        | WATCH<br>DOG RST | GND           | GND            | в   |

| с  | GND               | GND            | SRXD4         | SRXD5             | CSPI2_<br>SS0    | USBOTG_<br>DATA7 | USBOTG_<br>DATA1 | USB_<br>BYP      | RXD1           | DCD_<br>DCE1 | DTR_<br>DCE2 | CTS2           | KEY_<br>ROW2 | KEY_<br>ROW7 | KEY_<br>COL3 | TMS          | SJC_<br>MOD    | SRST0          | GPIO1<br>_0 | CLKO           | BOOT_<br>MODE1   | GND           | GND            | с   |

| D  | STXD5             | CSPI3_<br>MISO | SFS4          | SCK5              | CSPI2_<br>MOSI   | CSPI2_SPI<br>RDY | USBOTG_<br>DATA4 | USBOTG_<br>CLK   | TXD1           | RI_<br>DCE1  | DCD_<br>DTE1 | CE_<br>CONTROL | KEY_<br>ROW5 | KEY_<br>COL2 | RTCK         | DE           | SVEN0          | CAPTURE        | GPIO1<br>5  | BOOT_<br>MODE2 | GPIO1_4          | GND           | GND            | D   |

| Е  | ATA_<br>CS0       | ATA_<br>DMACK  | ATA_<br>DIOR  | CSPI3_<br>MOSI    |                  |                  |                  |                  |                |              |              |                |              |              |              |              |                |                |             | BOOT_<br>MODE4 | CKIL             | DVFS0         | DVFS1          | Е   |

| F  | PC_<br>RST        | PWMO           | ATA_<br>RESET | CSPI3_<br>SPI RDY |                  | BATT_<br>LINE    | CSPI2_<br>SS2    | USBOTG_<br>DATA3 | USBOT<br>G_STP | DTR_<br>DCE1 | TXD2         | KEY_<br>ROW4   | KEY_<br>COL4 | тск          | TRSTB        | STX0         | BOOT_<br>MODE0 | BOOT_<br>MODE3 |             | POWER_<br>FAIL | POR              | RESET_        | СКІН           | F   |

| G  | PC_VS2            | PC_<br>BVD1    | PC_<br>RW     | ATA_<br>CS1       |                  | SCK4             | SFS5             | USBOTG_<br>DATA0 | NVCC5          | NVCC5        | NVCC6        | NVCC6          | NVCC6        | NVCC9        | NVCC1        | NVCC1        | GPIO1_1        | GPIO1_6        |             | GPIO1_3        | VPG0             | VPG1          | GPIO3_0        | G   |

| н  | PC_CD2            | PC_<br>READY   | PC_<br>VS1    | PC_<br>BVD2       |                  | ATA_<br>DIOW     | CSPI3_<br>SCLK   | NVCC5            | NVCC5          | NVCC8        | NVCC8        | NVCC6          | QVCC         | NVCC4        | NVCC7        | NVCC1        | CLKSS          | VSTBY          |             | CSI_<br>MCLK   | CSI_<br>VSYNC    | CSI_HSY<br>NC | CSI_PIX<br>CLK | н   |

| J  | SD1_<br>DATA1     | SD1_<br>DATA2  | PC_<br>CD1    | PC_<br>WAIT       |                  | PC_POE           | IOIS16           | QVCC1            | QVCC1          | QVCC1        | NVCC8        | GND            | GND          | QVCC         | NVCC4        | NVCC7        | NVCC1          | I2C_<br>CLK    |             | CSI_D4         | CSI_D5           | CSI_D7        | CSI_D8         | J   |

| к  | USBH2_<br>DATA1   | SD1_<br>CLK    | SD1_<br>CMD   | SD1_<br>DATA0     |                  | PC_<br>PWRON     | NVCC3            | NVCC3            | QVCC1          | GND          | GND          | GND            | GND          | GND          | NVCC4        | NVCC7        | GPIO3_1        | I2C_<br>DAT    |             | CSI_D9         | CSI_<br>D10      | CSI_<br>D11   | CSI_<br>D12    | к   |

| L  | USBH2_<br>CLK     | USBH2_<br>DIR  | USBH2_<br>STP | USBH2_<br>NXT     |                  | SD1_<br>DATA3    | NVCC3            | NVCC3            | QVCC4          | GND          | GND          | GND            | GND          | GND          | QVCC         | NVCC7        | CSI_D6         | CSI_<br>D14    |             | CSI_D13        | CSI_D15          | VSYNC0        | HSYNC          | L   |

| м  | CSPI1_S<br>PI_RDY | CSPI1_<br>SS0  | CSPI1_<br>SS2 | CSPI1_<br>SCLK    |                  | USBH2_<br>DATA0  | QVCC4            | QVCC4            | GND            | GND          | GND          | GND            | GND          | GND          | QVCC         | NVCC7        | DRDY0          | SD_D_<br>IO    |             | SD_D_I         | SD_D_<br>CLK     | LCS0          | FPSHIFT        | м   |

| N  | CSPI1_<br>MOSI    | CSPI1_<br>MISO | SRXD3         | STXD3             |                  | CSPI1_<br>SS1    | NC <sup>1</sup>  | QVCC4            | QVCC           | GND          | GND          | GND            | GND          | GND          | QVCC         | NVCC2        | D3_<br>SPL     | READ           |             | VSYNC3         | CONTRAST         | WRITE         | LCS1           | N   |

| Р  | SCK3              | SFS3           | STXD6         | SFS6              |                  | NFWP             | NC <sup>1</sup>  | NVCC10           | QVCC           | GND          | GND          | GND            | GND          | GND          | QVCC         | NVCC2        | UGND           | UVCC           |             | D3_CLS         | D3_<br>REV       | PAR_<br>RS    | SER_<br>RS     | Р   |

| R  | SRXD6             | SCK6           | NFRB          | NFCE              |                  | D13              | NVCC10           | NVCC10           | NVCC1<br>0     | QVCC         | QVCC         | GND            | QVCC         | QVCC         | NVCC2        | NVCC2        | LD8            | LD11           |             | LD3            | LD2              | LD1           | LD0            | R   |

| т  | NFCLE             | NFALE          | NFWE          | NFRE              |                  | D8               | D4               | IOQVDD           | NVCC1<br>0     | NVCC22       | NVCC21       | NVCC21         | NVCC21       | NVCC2        | FUSE_<br>VDD | FVCC         | M_<br>REQUEST  | OE             |             | LD7            | LD6              | LD5           | LD4            | т   |

| U  | D15               | D14            | D12           | D11               |                  | D0               | NVCC22           | NVCC22           | NVCC2<br>2     | NVCC22       | NVCC21       | SVCC           | SGND         | MGND         | MVCC         | FGND         | CS0            | M_<br>GRANT    |             | LD12           | NC               | LD10          | LD9            | U   |

| v  | D10               | D9             | D6            | D3                |                  | NVCC22           | NVCC22           | NVCC22           | NVCC2<br>2     | NVCC22       | A22          | A20            | A18          | A16          | A10          | SDCKE1       | LBA            | RW             |             | LD16           | LD15             | LD14          | LD13           | v   |

| w  | D7                | D5             | D2            | D1                |                  |                  |                  |                  |                |              |              |                |              |              |              |              |                |                |             | BCLK           | EB1              | EB0           | LD17           | w   |

| Y  | GND               | MA10           | A13           | A8                | A4               | A0               | SDBA1            | A25              | A24            | A23          | A21          | A19            | A17          | A15          | A14          | DQM1         | SDCKE0         | CS2            | CS3         | CS4            | ECB              | CS1           | GND            | Y   |

| A  | GND               | GND            | A12           | A7                | A3               | SDBA0            | SD30             | SD28             | SD24           | SD20         | SD17         | SD15           | SD12         | SD9          | SD6          | SD4          | SD1            | DQM2           | RAS         | CAS            | CS5              | GND           | GND            | A.A |

| ۱В | GND               | GND            | A11           | A6                | A2               | SDQS3            | SD29             | SD26             | SDQS2          | SD21         | SD18         | SDQS1          | SD13         | SD10         | SD7          | SDQS0        | SD2            | DQM3           | DQM0        | SDWE           | GND              | GND           | GND            | AE  |

| ٩C | GND               | GND            | A9            | A5                | A1               | SD31             | SD27             | SD25             | SD23           | SD22         | SD19         | SD16           | SD14         | SD11         | SD8          | SD5          | SD3            | SD0            | SDCLK       | SDCLK          | GND              | GND           | GND            | AC  |

|    | 1                 | 2              | 3             | 4                 | 5                | 6                | 7                | 8                | 9              | 10           | 11           | 12             | 13           | 14           | 15           | 16           | 17             | 18             | 19          | 20             | 21               | 22            | 23             | •   |

<sup>1</sup> These contacts are not used and must be floated by the user.

#### How to Reach Us:

Home Page: www.freescale.com

E-mail: support@freescale.com

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064, Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Preescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-521-6274 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Document Number: MCIMX31 Rev. 4.1 11/2008 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. ARM, ARM Thumb, Jazelle, and the ARM Powered logo are registered trademarks of ARM Limited. ARM1136JF-S, ARM11, Embedded Trace Kit, Embedded Trace Macrocell, ETM, Embedded Trace Buffer, and ETB are trademarks of ARM Limited. All other product or service names are the property of their respective owners. Java and all other Java-based marks are trademarks or registered trademarks of Sun Microsystems, Inc. in the U.S. and other countries. France Telecom – TDF – Groupe des ecoles des telecommunications Turbo codes patents license.

© Freescale Semiconductor, Inc. 2005, 2006, 2007. All rights reserved.