Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 32MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT     |

| Number of I/O              | 40                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 6K x 8                                                                |

| RAM Size                   | 20K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                           |

| Data Converters            | A/D 10x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-LQFP                                                               |

| Supplier Device Package    | 48-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l083cbt6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|            | grid array package outline1                                             | 22 |

|------------|-------------------------------------------------------------------------|----|

| Figure 43. | UFBGA100 - 100-pin, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball      |    |

|            | grid array package recommended footprint1                               | 23 |

| Figure 44. | UFBGA100 marking example (package top view)1                            | 24 |

| Figure 45. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline       | 25 |

| Figure 46. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat recommended footprint |    |

| Figure 47. | LQFP64 marking example (package top view)1                              |    |

| Figure 48. | TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch thin profile fine pitch ball  |    |

| U U        | grid array package outline                                              | 28 |

| Figure 49. | TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ball |    |

| U          | ,grid array recommended footprint                                       | 29 |

| Figure 50. | TFBGA64 marking example (package top view)1                             |    |

| Figure 51. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline         |    |

| Figure 52. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat recommended footprint   |    |

| Figure 53. | LQFP48 marking example (package top view)                               |    |

| Figure 54. | Thermal resistance                                                      |    |

|            |                                                                         |    |

|                                                | Functionalities depending on the operating power supply range |                                     |                            |                           |  |  |  |  |

|------------------------------------------------|---------------------------------------------------------------|-------------------------------------|----------------------------|---------------------------|--|--|--|--|

| Operating power<br>supply range                | DAC and ADC operation                                         | Dynamic<br>voltage scaling<br>range | I/O operation              | USB                       |  |  |  |  |

| V <sub>DD</sub> = 1.65 to 1.71 V               | ADC only,<br>conversion time<br>up to 570 ksps                | Range 2 or<br>range 3               | Degraded speed performance | Not functional            |  |  |  |  |

| V <sub>DD</sub> = 1.71 to 1.8 V <sup>(1)</sup> | ADC only,<br>conversion time<br>up to 1.14 Msps               | Range 1, range 2<br>or range 3      | Degraded speed performance | Functional <sup>(2)</sup> |  |  |  |  |

| $V_{DD}$ = 1.8 to 2.0 V <sup>(1)</sup>         | Conversion time<br>up to 1.14 Msps                            | Range1, range 2<br>or range 3       | Degraded speed performance | Functional <sup>(2)</sup> |  |  |  |  |

| V <sub>DD</sub> = 2.0 to 2.4 V                 | Conversion time<br>up to<br>1.14 Msps                         | Range 1, range 2<br>or range 3      | Full speed operation       | Functional <sup>(2)</sup> |  |  |  |  |

| V <sub>DD</sub> = 2.4 to 3.6 V                 | Conversion time<br>up to<br>1.14 Msps                         | Range 1, range 2<br>or range 3      | Full speed operation       | Functional <sup>(2)</sup> |  |  |  |  |

| Table 3. Functionalities | depending on the operating | g power supply range |

|--------------------------|----------------------------|----------------------|

CPU frequency changes from initial to final must respect "fcpu initial <4\*fcpu final". It must also respect 5

µs delay between two changes. For example to switch from 4.2 MHz to 32 MHz, you can switch from 4.2

MHz to 16 MHz, wait 5 µs, then switch from 16 MHz to 32 MHz.</li>

2. To be USB compliant from the I/O voltage standpoint, the minimum  $V_{\text{DD\_USB}}$  is 3.0 V.

#### Table 4. CPU frequency range depending on dynamic voltage scaling

| CPU frequency range                              | Dynamic voltage scaling range |

|--------------------------------------------------|-------------------------------|

| 16 MHz to 32 MHz (1ws)<br>32 kHz to 16 MHz (0ws) | Range 1                       |

| 8 MHz to 16 MHz (1ws)<br>32 kHz to 8 MHz (0ws)   | Range 2                       |

| 32 kHz to 4.2 MHz (0ws)                          | Range 3                       |

### 3.4.3 Voltage regulator

The regulator has three operation modes: main (MR), low power (LPR) and power down.

- MR is used in Run mode (nominal regulation)

- LPR is used in the Low-power run, Low-power sleep and Stop modes

- Power down is used in Standby mode. The regulator output is high impedance, the kernel circuitry is powered down, inducing zero consumption but the contents of the registers and RAM are lost except for the standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE crystal 32 KHz oscillator, RCC\_CSR).

# 3.5 Clock management

The clock controller distributes the clocks coming from different oscillators to the core and the peripherals. It also manages clock gating for low-power modes and ensures clock robustness. It features:

Clock prescaler

To get the best trade-off between speed and current consumption, the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler.

#### • Safe clock switching

Clock sources can be changed safely on the fly in Run mode through a configuration register.

#### Clock management

To reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

#### System clock source

Three different clock sources can be used to drive the master clock SYSCLK:

- 1-25 MHz high-speed external crystal (HSE), that can supply a PLL

- 16 MHz high-speed internal RC oscillator (HSI), trimmable by software, that can supply a PLLMultispeed internal RC oscillator (MSI), trimmable by software, able to generate 7 frequencies (65 kHz, 131 kHz, 262 kHz, 524 kHz, 1.05 MHz, 2.1 MHz, 4.2 MHz). When a 32.768 kHz clock source is available in the system (LSE), the MSI frequency can be trimmed by software down to a ±0.5% accuracy.

#### • Auxiliary clock source

Two ultra-low-power clock sources that can be used to drive the LCD controller and the real-time clock:

- 32.768 kHz low-speed external crystal (LSE)

- 37 kHz low-speed internal RC (LSI), also used to drive the independent watchdog. The LSI clock can be measured using the high-speed internal RC oscillator for greater precision.

#### • RTC and LCD clock source

The LSI, LSE or HSE sources can be chosen to clock the RTC and the LCD, whatever the system clock.

#### USB clock source

A 48 MHz clock trimmed through the USB SOF or LSE supplies the USB interface.

# 3.10 Direct memory access (DMA)

The flexible 7-channel, general-purpose DMA is able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. The DMA controller supports circular buffer management, avoiding the generation of interrupts when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with software trigger support for each channel. Configuration is done by software and transfer sizes between source and destination are independent.

The DMA can be used with the main peripherals: AES, SPI, I<sup>2</sup>C, USART, LPUART, general-purpose timers, DAC, and ADC.

# 3.11 Liquid crystal display (LCD)

The LCD drives up to 8 common terminals and 48 segment terminals to drive up to 384 pixels.

- Internal step-up converter to guarantee functionality and contrast control irrespective of V<sub>DD</sub>. This converter can be deactivated, in which case the V<sub>LCD</sub> pin is used to provide the voltage to the LCD

- Supports static, 1/2, 1/3, 1/4 and 1/8 duty

- Supports static, 1/2, 1/3 and 1/4 bias

- Phase inversion to reduce power consumption and EMI

- Up to 8 pixels can be programmed to blink

- Unneeded segments and common pins can be used as general I/O pins

- LCD RAM can be updated at any time owing to a double-buffer

- The LCD controller can operate in Stop mode

- V<sub>LCD</sub> rails decoupling capability

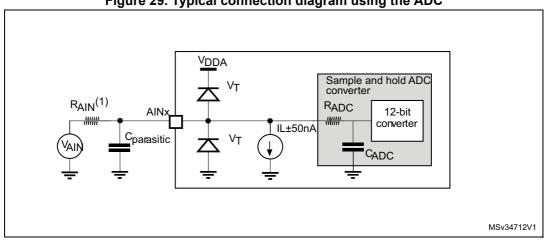

# 3.12 Analog-to-digital converter (ADC)

A native 12-bit, extended to 16-bit through hardware oversampling, analog-to-digital converter is embedded into STM32L083xx device. It has up to 16 external channels and 3 internal channels (temperature sensor, voltage reference,  $V_{LCD}$  voltage measurement). Three channels, PA0, PA4 and PA5, are fast channels, while the others are standard channels.

The ADC performs conversions in single-shot or scan mode. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC frequency is independent from the CPU frequency, allowing maximum sampling rate of 1.14 MSPS even with a low CPU speed. The ADC consumption is low at all frequencies (~25  $\mu$ A at 10 kSPS, ~240  $\mu$ A at 1MSPS). An auto-shutdown function guarantees that the ADC is powered off except during the active conversion phase.

The ADC can be served by the DMA controller. It can operate from a supply voltage down to 1.65 V.

The ADC features a hardware oversampler up to 256 samples, this improves the resolution to 16 bits (see AN2668).

DocID027070 Rev 3

| I2C features <sup>(1)</sup>                                  | I2C1 | I2C2             | I2C3 |

|--------------------------------------------------------------|------|------------------|------|

| Fast Mode Plus with 20 mA output drive I/Os (up to 1 Mbit/s) | х    | X <sup>(2)</sup> | х    |

| Independent clock                                            | Х    | -                | Х    |

| SMBus                                                        | Х    | -                | Х    |

| Wakeup from STOP                                             | Х    | -                | Х    |

Table 12. STM32L083xx I<sup>2</sup>C implementation (continued)

1. X = supported.

2. See Table 16: STM32L083xx pin definition on page 42 for the list of I/Os that feature Fast Mode Plus capability

### 3.19.2 Universal synchronous/asynchronous receiver transmitter (USART)

The four USART interfaces (USART1, USART2, USART4 and USART5) are able to communicate at speeds of up to 4 Mbit/s.

They provide hardware management of the CTS, RTS and RS485 driver enable (DE) signals, multiprocessor communication mode, master synchronous communication and single-wire half-duplex communication mode. USART1 and USART2 also support SmartCard communication (ISO 7816), IrDA SIR ENDEC, LIN Master/Slave capability, auto baud rate feature and has a clock domain independent from the CPU clock, allowing to wake up the MCU from Stop mode using baudrates up to 42 Kbaud.

All USART interfaces can be served by the DMA controller.

Table 13 for the supported modes and features of USART interfaces.

| USART modes/features <sup>(1)</sup>         | USART1 and USART2 | USART4 and USART5 |

|---------------------------------------------|-------------------|-------------------|

| Hardware flow control for modem             | Х                 | Х                 |

| Continuous communication using DMA          | Х                 | Х                 |

| Multiprocessor communication                | Х                 | Х                 |

| Synchronous mode <sup>(2)</sup>             | Х                 | Х                 |

| Smartcard mode                              | Х                 | -                 |

| Single-wire half-duplex communication       | Х                 | Х                 |

| IrDA SIR ENDEC block                        | Х                 | -                 |

| LIN mode                                    | Х                 | -                 |

| Dual clock domain and wakeup from Stop mode | Х                 | -                 |

| Receiver timeout interrupt                  | Х                 | -                 |

| Modbus communication                        | Х                 | -                 |

| Auto baud rate detection (4 modes)          | Х                 | -                 |

| Driver Enable                               | Х                 | Х                 |

| Table | 13. | USART | implementation |

|-------|-----|-------|----------------|

|-------|-----|-------|----------------|

1. X = supported.

2. This mode allows using the USART as an SPI master.

| 1             |                        |                            |                                         |  |  |  |  |  |

|---------------|------------------------|----------------------------|-----------------------------------------|--|--|--|--|--|

| Nar           | ne                     | Abbreviation               | Definition                              |  |  |  |  |  |

| Pin functions | Alternate<br>functions | Functions selected throug  | gh GPIOx_AFR registers                  |  |  |  |  |  |

|               | Additional functions   | Functions directly selecte | ed/enabled through peripheral registers |  |  |  |  |  |

Table 15. Legend/abbreviations used in the pinout table (continued)

|        | Pi     | n num   | ber     |          |                                       |          |               |      |                                   |                                    |

|--------|--------|---------|---------|----------|---------------------------------------|----------|---------------|------|-----------------------------------|------------------------------------|

| LQFP48 | LQFP64 | TFBGA64 | LQFP100 | UFBGA100 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Note | Alternate functions               | Additional functions               |

| -      | -      | -       | 1       | B2       | PE2                                   | I/O      | FT            | -    | LCD_SEG38, TIM3_ETR               | -                                  |

| -      | -      | -       | 2       | A1       | PE3                                   | I/O      | FT            | -    | TIM22_CH1, LCD_SEG39,<br>TIM3_CH1 | -                                  |

| -      | -      | -       | 3       | B1       | PE4                                   | I/O      | FT            | -    | TIM22_CH2, TIM3_CH2               | -                                  |

| -      | -      | -       | 4       | C2       | PE5                                   | I/O      | FT            | -    | TIM21_CH1, TIM3_CH3               | -                                  |

| -      | -      | -       | 5       | D2       | PE6                                   | I/O      | FT            | -    | TIM21_CH2, TIM3_CH4               | RTC_TAMP3/WKUP3                    |

| 1      | 1      | B2      | 6       | E2       | VLCD                                  | S        |               | -    | -                                 |                                    |

| 2      | 2      | A2      | 7       | C1       | PC13                                  | I/O      | FT            | -    | -                                 | RTC_TAMP1/RTC_TS/<br>RTC_OUT/WKUP2 |

| 3      | 3      | A1      | 8       | D1       | PC14-<br>OSC32_IN<br>(PC14)           | I/O      | FT            | -    | -                                 | OSC32_IN                           |

| 4      | 4      | B1      | 9       | E1       | PC15-<br>OSC32_OUT<br>(PC15)          | I/O      | тс            | -    | -                                 | OSC32_OUT                          |

| -      | -      | -       | 10      | F2       | PH9                                   | I/O      | FT            | 1    | -                                 | -                                  |

| -      | -      | -       | 11      | G2       | PH10                                  | I/O      | FT            | -    | -                                 | -                                  |

| 5      | 5      | C1      | 12      | F1       | PH0-OSC_IN<br>(PH0)                   | I/O      | тс            | -    | USB_CRS_SYNC                      | OSC_IN                             |

| 6      | 6      | D1      | 13      | G1       | PH1-<br>OSC_OUT<br>(PH1)              | I/O      | тс            | -    | -                                 | OSC_OUT                            |

| 7      | 7      | E1      | 14      | H2       | NRST                                  | I/O      | -             | -    | -                                 | -                                  |

#### Table 16. STM32L083xx pin definition

| Table 16. | STM32L | .083xx pi | n definition | (continued) |

|-----------|--------|-----------|--------------|-------------|

|-----------|--------|-----------|--------------|-------------|

|        | Pi     | n num   | ber     |          |                                       |          | -             |      |                                                                                      |                      |

|--------|--------|---------|---------|----------|---------------------------------------|----------|---------------|------|--------------------------------------------------------------------------------------|----------------------|

| LQFP48 | LQFP64 | TFBGA64 | LQFP100 | UFBGA100 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Note | Alternate functions                                                                  | Additional functions |

| 33     | 45     | B8      | 71      | A12      | PA12                                  | I/O      | FT            | (2)  | SPI1_MOSI, EVENTOUT,<br>TSC_G4_IO4,<br>USART1_RTS_DE,<br>COMP2_OUT                   | USB_DP               |

| 34     | 46     | A8      | 72      | A11      | PA13                                  | I/O      | FT            | -    | SWDIO, USB_OE,<br>LPUART1_RX                                                         | -                    |

| -      | -      | -       | 73      | C11      | VDD                                   | S        |               | -    | -                                                                                    | -                    |

| 35     | 47     | D5      | 74      | F11      | VSS                                   | S        |               | -    | -                                                                                    | -                    |

| 36     | 48     | E6      | 75      | G11      | VDD_USB                               | S        |               | -    | -                                                                                    | -                    |

| 37     | 49     | A7      | 76      | A10      | PA14                                  | I/O      | FT            | -    | SWCLK, USART2_TX,<br>LPUART1_TX                                                      | -                    |

| 38     | 50     | A6      | 77      | A9       | PA15                                  | I/O      | FT            | -    | SPI1_NSS, LCD_SEG17,<br>TIM2_ETR, EVENTOUT,<br>USART2_RX, TIM2_CH1,<br>USART4_RTS_DE | -                    |

| -      | 51     | B7      | 78      | B11      | PC10                                  | I/O      | FT            | -    | LPUART1_TX,<br>LCD_COM4/LCD_SEG28/<br>LCD_SEG48, USART4_TX                           | -                    |

| -      | 52     | B6      | 79      | C10      | PC11                                  | I/O      | FT            | -    | LPUART1_RX,<br>LCD_COM5/LCD_SEG29/<br>LCD_SEG49,<br>USART4_RX                        | -                    |

| -      | 53     | C5      | 80      | B10      | PC12                                  | I/O      | FT            | -    | LCD_COM6/LCD_SEG30/<br>LCD_SEG50,<br>USART5_TX,<br>USART4_CK                         | -                    |

| -      | -      | -       | 81      | C9       | PD0                                   | I/O      | FT            | -    | TIM21_CH1,<br>SPI2_NSS/I2S2_WS                                                       | -                    |

| -      | -      | -       | 82      | B9       | PD1                                   | I/O      | FT            | I    | SPI2_SCK/I2S2_CK                                                                     | -                    |

| -      | 54     | В5      | 83      | C8       | PD2                                   | I/O      | FT            | -    | LPUART1_RTS_DE,<br>LCD_COM7/LCD_SEG31/<br>LCD_SEG51, TIM3_ETR,<br>USART5_RX          | -                    |

| -      | -      | -       | 84      | B8       | PD3                                   | I/O      | FT            | -    | USART2_CTS,<br>LCD_SEG44,<br>SPI2_MISO/I2S2_MCK                                      | -                    |

DocID027070 Rev 3

| Table 16. | STM32L | .083xx | pin | definition | (continued) |

|-----------|--------|--------|-----|------------|-------------|

|-----------|--------|--------|-----|------------|-------------|

|        | Pi     | n num   | ber     |          |                                       |          | _             |      |                                                                                                                 |                      |

|--------|--------|---------|---------|----------|---------------------------------------|----------|---------------|------|-----------------------------------------------------------------------------------------------------------------|----------------------|

| LQFP48 | LQFP64 | TFBGA64 | LQFP100 | UFBGA100 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Note | Alternate functions                                                                                             | Additional functions |

| -      | -      | -       | 85      | B7       | PD4                                   | I/O      | FT            | -    | USART2_RTS_DE,<br>SPI2_MOSI/I2S2_SD                                                                             | -                    |

| -      | -      | -       | 86      | A6       | PD5                                   | I/O      | FT            | -    | USART2_TX                                                                                                       | -                    |

| -      | -      | -       | 87      | B6       | PD6                                   | I/O      | FT            | -    | USART2_RX                                                                                                       | -                    |

| -      | -      | -       | 88      | A5       | PD7                                   | I/O      | FT            | -    | USART2_CK, TIM21_CH2                                                                                            | -                    |

| 39     | 55     | A5      | 89      | A8       | PB3                                   | I/O      | FT            | -    | SPI1_SCK, LCD_SEG7,<br>TIM2_CH2, TSC_G5_IO1,<br>EVENTOUT,<br>USART1_RTS_DE,<br>USART5_TX                        | COMP2_INM            |

| 40     | 56     | A4      | 90      | A7       | PB4                                   | I/O      | FTf           | -    | SPI1_MISO, LCD_SEG8,<br>TIM3_CH1, TSC_G5_IO2,<br>TIM22_CH1,<br>USART1_CTS,<br>USART5_RX, I2C3_SDA               | COMP2_INP            |

| 41     | 57     | C4      | 91      | C5       | PB5                                   | I/O      | FT            | -    | SPI1_MOSI, LCD_SEG9,<br>LPTIM1_IN1, I2C1_SMBA,<br>TIM3_CH2/TIM22_CH2,<br>USART1_CK,<br>USART5_CK/USART5_<br>RTS | COMP2_INP            |

| 42     | 58     | D3      | 92      | B5       | PB6                                   | I/O      | FTf           | -    | USART1_TX, I2C1_SCL,<br>LPTIM1_ETR,<br>TSC_G5_IO3                                                               | COMP2_INP            |

| 43     | 59     | C3      | 93      | B4       | PB7                                   | I/O      | FTf           | -    | USART1_RX, I2C1_SDA,<br>LPTIM1_IN2,<br>TSC_G5_IO4,<br>USART4_CTS                                                | COMP2_INP, PVD_IN    |

| 44     | 60     | B4      | 94      | A4       | BOOT0                                 | Ι        |               | -    | -                                                                                                               | -                    |

| 45     | 61     | B3      | 95      | A3       | PB8                                   | I/O      | FTf           | -    | LCD_SEG16, TSC_SYNC,<br>I2C1_SCL                                                                                | -                    |

| 46     | 62     | A3      | 96      | В3       | PB9                                   | I/O      | FTf           | -    | LCD_COM3, EVENTOUT,<br>I2C1_SDA,<br>SPI2_NSS/I2S2_WS                                                            | -                    |

| -      | -      | -       | 97      | C3       | PE0                                   | I/O      | FT            | -    | LCD_SEG36, EVENTOUT                                                                                             | -                    |

| -      | -      | -       | 98      | A2       | PE1                                   | I/O      | FT            | -    | LCD_SEG37, EVENTOUT                                                                                             | -                    |

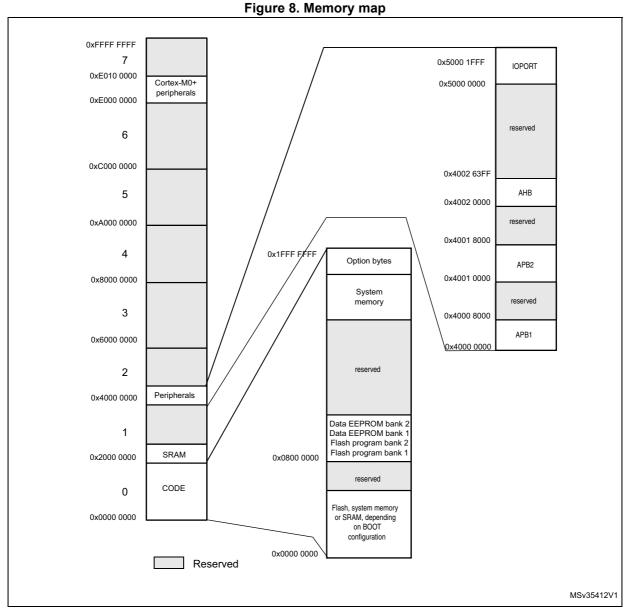

# 5 Memory mapping

1. Refer to the STM32L083xx reference manual for details on the Flash memory organization for each memory size.

| Symbol                            | Parameter                                                                             | Conditio                                                          | n                                     | f <sub>HCLK</sub><br>(MHz) | Тур  | Max <sup>(1)</sup> | Unit |

|-----------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------|----------------------------|------|--------------------|------|

|                                   |                                                                                       |                                                                   | Range3,                               | 1                          | 175  | 230                |      |

|                                   |                                                                                       |                                                                   | Vcore=1.2 V                           | 2                          | 315  | 360                | μA   |

| I <sub>DD</sub> (Run<br>from RAM) |                                                                                       |                                                                   | VOS[1:0]=11                           | 4                          | 570  | 630                |      |

|                                   |                                                                                       | f <sub>HSE</sub> = f <sub>HCLK</sub> up to                        | Range2,                               | 4                          | 0,71 | 0,78               |      |

|                                   |                                                                                       | 16 MHz included,<br>f <sub>HSE</sub> = f <sub>HCLK</sub> /2 above | Vcore=1.5 V                           | 8                          | 1,35 | 1,6                |      |

|                                   |                                                                                       | 16 MHz (PLL ON) <sup>(2)</sup>                                    | VOS[1:0]=10                           | 16                         | 2,7  | 3                  | mA   |

|                                   |                                                                                       |                                                                   | Range1,                               | 8                          | 1,7  | 1,9                |      |

|                                   | Supply current in Run<br>mode code executed<br>from RAM, Flash<br>memory switched off |                                                                   | Vcore=1.8 V<br>VOS[1:0]=01            | 16                         | 3,2  | 3,7                |      |

|                                   |                                                                                       |                                                                   |                                       | 32                         | 6,65 | 7,1                |      |

|                                   |                                                                                       | MSI clock                                                         | Range3,<br>Vcore=1.2 V                | 0,065                      | 38   | 98                 | μA   |

|                                   |                                                                                       |                                                                   |                                       | 0,524                      | 105  | 160                |      |

|                                   |                                                                                       |                                                                   | VOS[1:0]=11                           | 4,2                        | 615  | 710                |      |

|                                   |                                                                                       | HSI clock source                                                  | Range2,<br>Vcore=1.5 V<br>VOS[1:0]=10 | 16                         | 2,85 | 3                  | - mA |

|                                   |                                                                                       | (16 MHz)                                                          | Range1,<br>Vcore=1.8 V<br>VOS[1:0]=01 | 32                         | 6,85 | 7,3                |      |

#### Table 32. Current consumption in Run mode, code with data processing running from RAM

1. Guaranteed by characterization results at 125 °C, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

# Table 33. Current consumption in Run mode vs code type,code with data processing running from RAM<sup>(1)</sup>

| Symbol                       | Parameter |                                                                                | Conditions                                           |           | f <sub>HCLK</sub> | Тур  | Unit |

|------------------------------|-----------|--------------------------------------------------------------------------------|------------------------------------------------------|-----------|-------------------|------|------|

|                              |           |                                                                                |                                                      | Dhrystone |                   | 570  |      |

|                              |           |                                                                                | Range 3,                                             | CoreMark  |                   | 670  |      |

| from executed from 16 MHz in | f f unto  | 10001.01-11                                                                    | Fibonacci                                            | 4 MHz     | 410               | μA   |      |

|                              | ,         | $f_{HSE} = f_{HCLK}$ up to<br>16 MHz included,<br>$f_{HSE} = f_{HCLK}/2$ above |                                                      | while(1)  |                   | 375  |      |

|                              | ,         |                                                                                | Range 1,<br>V <sub>CORE</sub> =1.8 V,<br>VOS[1:0]=01 | Dhrystone |                   | 6,65 | mA   |

|                              |           |                                                                                |                                                      | CoreMark  | - 32 MHz          | 6,95 |      |

|                              |           |                                                                                |                                                      | Fibonacci |                   | 5,9  |      |

|                              |           |                                                                                |                                                      | while(1)  |                   | 5,2  |      |

1. Guaranteed by characterization results, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

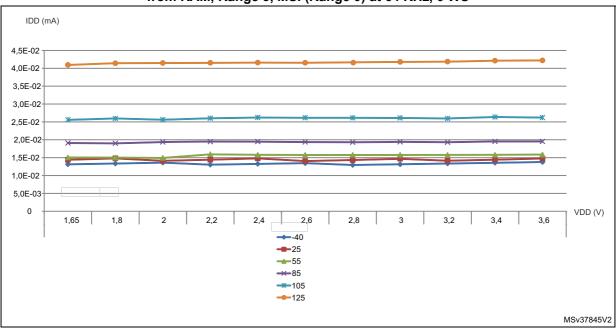

Figure 16. I<sub>DD</sub> vs V<sub>DD</sub>, at T<sub>A</sub>= 25 °C, Low-power run mode, code running from RAM, Range 3, MSI (Range 0) at 64 KHz, 0 WS

| Symbol     | Parameter                                    |                                                                                       | Condition                                                              |                              | Тур  | Max<br>(1) | Unit |

|------------|----------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------|------------------------------|------|------------|------|

|            |                                              |                                                                                       | MSI clock = 65 kHz,<br>f <sub>HCLK</sub> = 32 kHz,<br>Flash memory OFF | $T_A = -40$ to $25^{\circ}C$ | 4,7  | -          |      |

|            |                                              |                                                                                       |                                                                        | $T_A = -40$ to $25^{\circ}C$ | 17   | 24         | 1    |

| (LP Sleep) |                                              | ower sleep executed from MSL clock = $65 \text{ kHz}$ T <sub>A</sub> = $85^{\circ}$ C | MSI clock = 65 kHz,                                                    | T <sub>A</sub> = 85°C        | 19,5 | 30         | 1    |

|            |                                              |                                                                                       | T <sub>A</sub> = 105°C                                                 | 23                           | 47   |            |      |

|            | Supply current in<br>Low-power sleep<br>mode |                                                                                       |                                                                        | T <sub>A</sub> = 125°C       | 32,5 | 70         |      |

|            |                                              |                                                                                       | MSI clock = 65 kHz,<br>f <sub>HCLK</sub> = 65 kHz                      | $T_A = -40$ to $25^{\circ}C$ | 17   | 24         |      |

|            |                                              |                                                                                       |                                                                        | T <sub>A</sub> = 85°C        | 20   | 31         | μA   |

|            | mode                                         | Flash memory, V <sub>DD</sub><br>from 1.65 to 3.6 V                                   |                                                                        | T <sub>A</sub> = 105°C       | 23,5 | 47         | -    |

|            |                                              |                                                                                       |                                                                        | T <sub>A</sub> = 125°C       | 32,5 | 70         |      |

|            |                                              |                                                                                       |                                                                        | $T_A$ = - 40 to 25°C         | 19,5 | 27         |      |

|            |                                              |                                                                                       |                                                                        | T <sub>A</sub> = 55°C        | 20,5 | 28         |      |

|            |                                              |                                                                                       | MSI clock = 131kHz,<br>f <sub>HCLK</sub> = 131 kHz                     | T <sub>A</sub> = 85°C        | 22,5 | 33         |      |

|            |                                              |                                                                                       | HOLIX                                                                  | T <sub>A</sub> = 105°C       | 26   | 50         |      |

|            |                                              |                                                                                       |                                                                        | T <sub>A</sub> = 125°C       | 35   | 73         |      |

#### Table 36. Current consumption in Low-power sleep mode

1. Guaranteed by characterization results at 125 °C, unless otherwise specified.

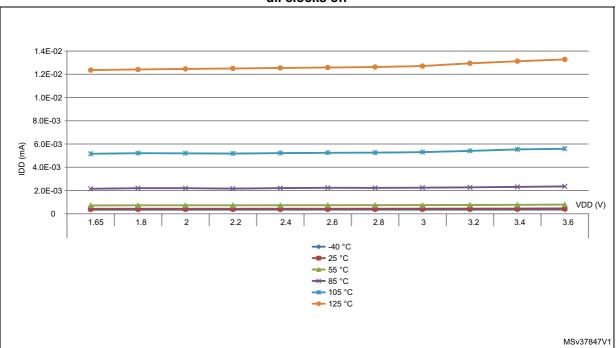

## Figure 18. $I_{DD}$ vs $V_{DD}$ , at $T_A$ = 25/55/85/105/125 °C, Stop mode with RTC disabled, all clocks off

| Table 38. Typical and maximum | current consum   | ptions in | Standby mode |

|-------------------------------|------------------|-----------|--------------|

| Tuble eel Typical and maximum | ourionit oonouni |           | otanaby moao |

| Symbol                                                      | Parameter                               | Conditi                             | Тур                                        | Max <sup>(1)</sup> | Unit |              |

|-------------------------------------------------------------|-----------------------------------------|-------------------------------------|--------------------------------------------|--------------------|------|--------------|

| I <sub>DD</sub> Supply current in Standby<br>(Standby) mode |                                         |                                     | $T_A = -40 \text{ to } 25^{\circ}\text{C}$ | 0,855              | 1,70 |              |

|                                                             |                                         |                                     | T <sub>A</sub> = 55 °C                     | -                  | 2,90 |              |

|                                                             | Independent watchdog<br>and LSI enabled | T <sub>A</sub> = 85 °C              | -                                          | 3,30               |      |              |

|                                                             |                                         |                                     | T <sub>A</sub> = 105 °C                    | -                  | 4,10 | - μΑ<br>- μΑ |

|                                                             | Supply current in Standby mode          |                                     | T <sub>A</sub> = 125 °C                    | -                  | 8,50 |              |

|                                                             |                                         |                                     | T <sub>A</sub> = − 40 to 25°C              | 0,29               | 0,60 |              |

|                                                             |                                         |                                     | T <sub>A</sub> = 55 °C                     | 0,32               | 1,20 |              |

|                                                             |                                         | Independent watchdog<br>and LSI off | T <sub>A</sub> = 85 °C                     | 0,5                | 2,30 |              |

|                                                             |                                         |                                     | T <sub>A</sub> = 105 °C                    | 0,94               | 3,00 |              |

|                                                             |                                         |                                     | T <sub>A</sub> = 125 °C                    | 2,6                | 7,00 |              |

1. Guaranteed by characterization results at 125 °C, unless otherwise specified

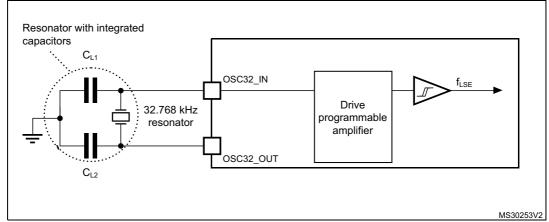

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 46*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                                    | Conditions <sup>(2)</sup>                          | Min <sup>(2)</sup> | Тур    | Max  | Unit |

|-------------------------------------|----------------------------------------------|----------------------------------------------------|--------------------|--------|------|------|

| f <sub>LSE</sub>                    | LSE oscillator frequency                     |                                                    | -                  | 32.768 | -    | kHz  |

|                                     |                                              | LSEDRV[1:0]=00<br>lower driving capability         | -                  | -      | 0.5  |      |

| Gm                                  | Maximum critical crystal<br>transconductance | LSEDRV[1:0]= 01<br>medium low driving capability   | -                  | -      | 0.75 | uA/V |

| G <sub>m</sub>                      |                                              | LSEDRV[1:0] = 10<br>medium high driving capability | -                  | -      | 1.7  | μΑνν |

|                                     |                                              | LSEDRV[1:0]=11<br>higher driving capability        | 2.7                |        |      |      |

| t <sub>SU(LSE)</sub> <sup>(3)</sup> | Startup time                                 | V <sub>DD</sub> is stabilized                      | -                  | 2      | -    | S    |

|  | Table 46. | LSE | oscillator | characteristics <sup>(1)</sup> |

|--|-----------|-----|------------|--------------------------------|

|--|-----------|-----|------------|--------------------------------|

1. Guaranteed by design.

2. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

3. Guaranteed by characterization results. t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer. To increase speed, address a lower-drive quartz with a high- driver mode.

# *Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

Note:

An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

## 6.3.11 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the ANSI/JEDEC standard.

| Symbol                | Ratings                                               | Conditions                                                     | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|----------------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)    | $T_A = +25 \text{ °C},$<br>conforming to<br>ANSI/JEDEC JS-001  | 2     | 2000                            | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model) | $T_A = +25 \text{ °C},$<br>conforming to<br>ANSI/ESD STM5.3.1. | C4    | 500                             | v    |

Table 57. ESD absolute maximum ratings

1. Guaranteed by characterization results.

#### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latch-up standard.

#### Table 58. Electrical sensitivities

| Symbol | Parameter             | Conditions                            | Class      |

|--------|-----------------------|---------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +125$ °C conforming to JESD78A | II level A |

#### **Output voltage levels**

Unless otherwise specified, the parameters given in *Table 61* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 26*. All I/Os are CMOS and TTL compliant.

| Symbol                               | Parameter                                | Conditions                                                                                                                                                   | Min                   | Max  | Unit |

|--------------------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------|------|

| V <sub>OL</sub> <sup>(1)</sup>       | Output low level voltage for an I/O pin  | CMOS port <sup>(2)</sup> ,<br>I <sub>IO</sub> = +8 mA                                                                                                        | -                     | 0.4  |      |

| V <sub>OH</sub> <sup>(3)</sup>       | Output high level voltage for an I/O pin | $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}$                                                                                                   | V <sub>DD</sub> -0.4  | -    |      |

| V <sub>OL</sub> <sup>(1)</sup>       | Output low level voltage for an I/O pin  | $\begin{array}{c} {\sf TTL \ port}^{(2)}, \\ {\sf I}_{IO} \ \mbox{=+ 8 mA} \\ {\sf 2.7 \ V} \le {\sf V}_{DD} \le \ \mbox{3.6 V} \end{array}$                 | -                     | 0.4  |      |

| V <sub>OH</sub> <sup>(3)(4)</sup>    | Output high level voltage for an I/O pin | $\begin{array}{c} {\sf TTL} \mbox{ port}^{(2)}, \\ {\sf I}_{IO} \mbox{=} \mbox{-}6\mbox{ mA} \\ 2.7\mbox{ V} \le {\sf V}_{DD} \le \mbox{ 3.6 V} \end{array}$ | 2.4                   | -    |      |

| V <sub>OL</sub> <sup>(1)(4)</sup>    | Output low level voltage for an I/O pin  | $\begin{array}{l} {I_{IO}} \mbox{ = +15 mA} \\ 2.7 \ V \le V_{DD} \le \ 3.6 \ V \end{array}$                                                                 | -                     | 1.3  | V    |

| V <sub>OH</sub> <sup>(3)(4)</sup>    | Output high level voltage for an I/O pin | $\begin{array}{l} \text{I}_{\text{IO}} \text{=} -15 \text{ mA} \\ \text{2.7 V} \leq \text{V}_{\text{DD}} \leq \ 3.6 \text{ V} \end{array}$                   | V <sub>DD</sub> -1.3  | -    |      |

| V <sub>OL</sub> <sup>(1)(4)</sup>    | Output low level voltage for an I/O pin  | $I_{IO}$ = +4 mA<br>1.65 V $\leq$ V <sub>DD</sub> < 3.6 V                                                                                                    | -                     | 0.45 |      |

| V <sub>OH</sub> <sup>(3)(4)</sup>    | Output high level voltage for an I/O pin | $\begin{array}{l} \text{I}_{IO} = \text{-4 mA} \\ 1.65 \text{ V} \leq \text{V}_{DD} \leq \ 3.6 \text{ V} \end{array}$                                        | V <sub>DD</sub> -0.45 | -    |      |

| V <sub>OLFM+</sub> <sup>(1)(4)</sup> | Output low level voltage for an FTf      | $\begin{array}{l} \text{I}_{\text{IO}} = 20 \text{ mA} \\ 2.7 \text{ V} \leq \text{V}_{DD} \leq \ 3.6 \text{ V} \end{array}$                                 | -                     | 0.4  |      |

| VOLFM+                               | I/O pin in Fm+ mode                      | $\begin{array}{l} {\sf I}_{IO} \mbox{=} \ 10 \ mA \\ 1.65 \ V \le V_{DD} \le \ 3.6 \ V \end{array}$                                                          | -                     | 0.4  |      |

The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 24*. The sum of the currents sunk by all the I/Os (I/O ports and control pins) must always be respected and must not exceed ΣI<sub>IO(PIN)</sub>.

2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in Table 24. The sum of the currents sourced by all the I/Os (I/O ports and control pins) must always be respected and must not exceed  $\Sigma I_{IO(PIN)}$ .

4. Guaranteed by characterization results.

| Symbol | Parameter                    | Conditions                                                                | Min  | Тур  | Мах | Unit |

|--------|------------------------------|---------------------------------------------------------------------------|------|------|-----|------|

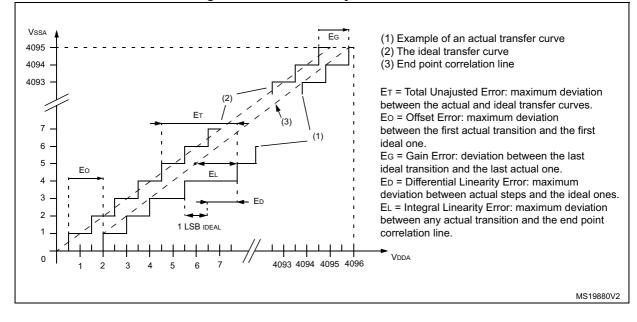

| ET     | Total unadjusted error       | 1.65 V < V <sub>REF+</sub> <v<sub>DDA &lt; 3.6 V,<br/>range 1/2/3</v<sub> | -    | 2    | 5   | -    |

| EO     | Offset error                 |                                                                           | -    | 1    | 2.5 |      |

| EG     | Gain error                   |                                                                           | -    | 1    | 2   | LSB  |

| EL     | Integral linearity error     |                                                                           | -    | 1.5  | 3   |      |

| ED     | Differential linearity error |                                                                           | -    | 1    | 2   |      |

| ENOB   | Effective number of bits     |                                                                           | 10.0 | 11.0 | -   | bits |

| SINAD  | Signal-to-noise distortion   |                                                                           | 62   | 69   | -   |      |

| SNR    | Signal-to-noise ratio        |                                                                           | 61   | 69   | -   | dB   |

| THD    | Total harmonic distortion    |                                                                           | -    | -85  | -65 |      |

## Table 66. ADC accuracy<sup>(1)(2)(3)</sup> (continued)

1. ADC DC accuracy values are measured after internal calibration.

ADC Accuracy vs. Negative Injection Current: Injecting negative current on any of the standard (non-robust) analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to standard analog pins which may potentially inject negative current.

Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 6.3.12 does not affect the ADC accuracy.

3. Better performance may be achieved in restricted V<sub>DDA</sub>, frequency and temperature ranges.

4. This number is obtained by the test board without additional noise, resulting in non-optimized value for oversampling mode.

#### Figure 28. ADC accuracy characteristics

- 1. Refer to Table 64: ADC characteristics for the values of RAIN, RADC and CADC.

- $C_{parasitic}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high  $C_{parasitic}$  value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced. 2.

#### **General PCB design guidelines**

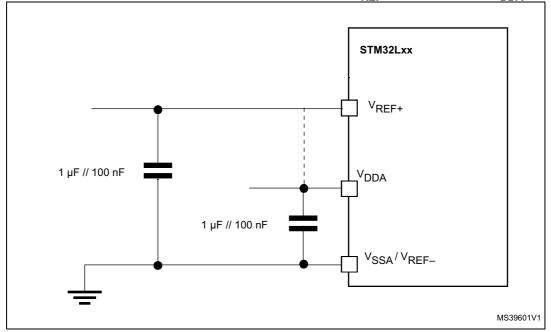

Power supply decoupling should be performed as shown in Figure 30 or Figure 31, depending on whether  $V_{\text{REF+}}$  is connected to  $V_{\text{DDA}}$  or not. The 10 nF capacitors should be ceramic (good quality). They should be placed as close as possible to the chip.

Figure 30. Power supply and reference decoupling (V<sub>REF+</sub> not connected to V<sub>DDA</sub>)

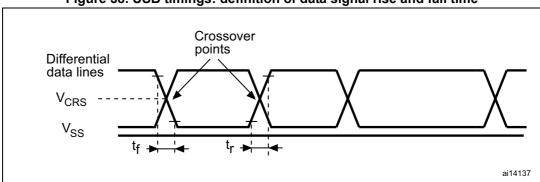

Figure 38. USB timings: definition of data signal rise and fall time

| Driver characteristics <sup>(1)</sup> |                                 |                                |     |     |      |

|---------------------------------------|---------------------------------|--------------------------------|-----|-----|------|

| Symbol                                | Parameter                       | Conditions                     | Min | Max | Unit |

| t <sub>r</sub>                        | Rise time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |

| t <sub>f</sub>                        | Fall Time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |

| t <sub>rfm</sub>                      | Rise/ fall time matching        | t <sub>r</sub> /t <sub>f</sub> | 90  | 110 | %    |

| V <sub>CRS</sub>                      | Output signal crossover voltage |                                | 1.3 | 2.0 | V    |

1. Guaranteed by design.

2. Measured from 10% to 90% of the data signal. For more detailed informations, please refer to USB Specification - Chapter 7 (version 2.0).

## 6.3.21 LCD controller

The devices embed a built-in step-up converter to provide a constant LCD reference voltage independently from the  $V_{DD}$  voltage. An external capacitor  $C_{ext}$  must be connected to the  $V_{LCD}$  pin to decouple this converter.

| Symbol            | Parameter                             | Min | Тур  | Max | Unit |

|-------------------|---------------------------------------|-----|------|-----|------|

| V <sub>LCD</sub>  | LCD external voltage                  | -   | -    | 3.6 |      |

| V <sub>LCD0</sub> | LCD internal reference voltage 0      | -   | 2.6  | -   |      |

| V <sub>LCD1</sub> | LCD internal reference voltage 1      | -   | 2.73 | -   |      |

| V <sub>LCD2</sub> | LCD internal reference voltage 2      | -   | 2.86 | -   |      |

| V <sub>LCD3</sub> | LCD internal reference voltage 3      | -   | 2.98 | -   | V    |

| V <sub>LCD4</sub> | LCD internal reference voltage 4      | -   | 3.12 | -   |      |

| V <sub>LCD5</sub> | LCD internal reference voltage 5      | -   | 3.26 | -   |      |

| V <sub>LCD6</sub> | LCD internal reference voltage 6 -    |     | 3.4  | -   |      |

| V <sub>LCD7</sub> | LCD internal reference voltage 7      | -   | 3.55 | -   |      |

| C <sub>ext</sub>  | V <sub>LCD</sub> external capacitance | 0.1 | -    | 2   | μF   |

Table 82. LCD controller characteristics

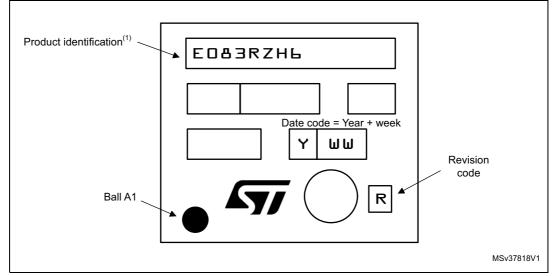

#### **Device marking for TFBGA64**

The following figure gives an example of topside marking versus ball A 1 position identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22-Mar-2016 | 3        | Updated number of SPIs on cover page and in <i>Table 2: Ultra-low-power STM32L083xxx device features and peripheral counts.</i><br>Changed minimum comparator supply voltage to 1.65 V on cover page. Added minimum DAC supply voltage on cover page.<br>Added number of fast and standard channels in <i>Section 3.12:</i><br><i>Analog-to-digital converter (ADC).</i><br>Updated <i>Section 3.19.2: Universal synchronous/asynchronous receiver transmitter (USART)</i> and <i>Section 3.19.4: Serial peripheral interface (SPI)/Inter-integrated sound (I2S)</i> to mention the fact that USARTs with synchronous mode feature can be used as SPI master interfaces.<br>Added baudrate allowing to wake up the MCU from Stop mode in <i>Section 3.19.2: Universal synchronous receiver transmitter (USART)</i> and <i>Section 3.19.3: Low-power universal asynchronous receiver transmitter (USART)</i> and <i>Section 3.19.3: Low-power universal asynchronous receiver transmitter (USART)</i> and <i>Section 3.19.3: Low-power universal asynchronous receiver transmitter (LPUART)</i> .<br><i>Section 6.3.15: 12-bit ADC characteristics:</i><br>- <i>Table 64: ADC characteristics:</i><br>Distinction made between V <sub>DDA</sub> for fast and standard channels; added note 1.<br>Added note 4. related to R <sub>ADC</sub> .<br>Updated f <sub>TRIG</sub> .<br>Updated f <sub>S</sub> and t <sub>CONV</sub> .<br>- Updated equation 1 description.<br>- Updated <i>Table 65: RAIN max for fADC = 16 MHz</i> for f <sub>ADC</sub> = 16 MHz and distinction made between fast and standard channels.<br>Updated R <sub>Q</sub> and added Note 2. in <i>Table 67: DAC characteristics</i> .<br>Added <i>Table 74: USART/LPUART characteristics</i> . |

Table 92. Document revision history