Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Product Status             | Active                                                                |  |

|----------------------------|-----------------------------------------------------------------------|--|

| Core Processor             | ARM® Cortex®-M0+                                                      |  |

| Core Size                  | 32-Bit Single-Core                                                    |  |

| Speed                      | 32MHz                                                                 |  |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                  |  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT     |  |

| Number of I/O              | 51                                                                    |  |

| Program Memory Size        | 192KB (192K x 8)                                                      |  |

| Program Memory Type        | FLASH                                                                 |  |

| EEPROM Size                | 6K x 8                                                                |  |

| RAM Size                   | 20K x 8                                                               |  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                           |  |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                 |  |

| Oscillator Type            | Internal                                                              |  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |  |

| Mounting Type              | Surface Mount                                                         |  |

| Package / Case             | 64-TFBGA                                                              |  |

| Supplier Device Package    | 64-TFBGA (5x5)                                                        |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l083rzh6 |  |

STM32L083xx Contents

|          |       | 3.18.3    | Basic timer (TIM6, TIM7)                                       | 32    |

|----------|-------|-----------|----------------------------------------------------------------|-------|

|          |       | 3.18.4    | SysTick timer                                                  | 32    |

|          |       | 3.18.5    | Independent watchdog (IWDG)                                    | 32    |

|          |       | 3.18.6    | Window watchdog (WWDG)                                         | 33    |

|          | 3.19  | Comm      | unication interfaces                                           | 33    |

|          |       | 3.19.1    | I2C bus                                                        | 33    |

|          |       | 3.19.2    | Universal synchronous/asynchronous receiver transmitter (USAF  | RT)34 |

|          |       | 3.19.3    | Low-power universal asynchronous receiver transmitter (LPUAR   | T) 35 |

|          |       | 3.19.4    | Serial peripheral interface (SPI)/Inter-integrated sound (I2S) | 35    |

|          |       | 3.19.5    | Universal serial bus (USB)                                     | 36    |

|          | 3.20  | Clock r   | recovery system (CRS)                                          | 36    |

|          | 3.21  | Cyclic    | redundancy check (CRC) calculation unit                        | 36    |

|          | 3.22  | Serial    | wire debug port (SW-DP)                                        | 36    |

| 4        | Pin d | lascrint  | ions                                                           | 37    |

| •        | 0     | icocript  |                                                                | 07    |

| 5        | Mem   | ory ma    | pping                                                          | 56    |

| 6        | Elect | trical ch | naracteristics                                                 | 57    |

|          | 6.1   | Param     | eter conditions                                                | 57    |

|          |       | 6.1.1     | Minimum and maximum values                                     | 57    |

|          |       | 6.1.2     | Typical values                                                 | 57    |

|          |       | 6.1.3     | Typical curves                                                 | 57    |

|          |       | 6.1.4     | Loading capacitor                                              | 57    |

|          |       | 6.1.5     | Pin input voltage                                              | 57    |

|          |       | 6.1.6     | Power supply scheme                                            | 58    |

|          |       | 6.1.7     | Optional LCD power supply scheme                               | 59    |

|          |       | 6.1.8     | Current consumption measurement                                | 59    |

|          | 6.2   | Absolu    | te maximum ratings                                             | 60    |

|          | 6.3   | Operat    | ing conditions                                                 | 62    |

|          |       | 6.3.1     | General operating conditions                                   | 62    |

|          |       | 6.3.2     | Embedded reset and power control block characteristics         | 64    |

|          |       | 6.3.3     | Embedded internal reference voltage                            | 65    |

|          |       | 6.3.4     | Supply current characteristics                                 | 66    |

|          |       | 6.3.5     | Wakeup time from low-power mode                                | 78    |

|          |       | 6.3.6     | External clock source characteristics                          | 80    |

|          |       | 6.3.7     | Internal clock source characteristics                          | 84    |

| <b>\</b> |       |           | DocID027070 Rev 3                                              | 3/139 |

|   |       | 6.3.8    | DLL pharacteristics 97                 |

|---|-------|----------|----------------------------------------|

|   |       |          | PLL characteristics                    |

|   |       | 6.3.9    | Memory characteristics                 |

|   |       | 6.3.10   | EMC characteristics                    |

|   |       | 6.3.11   | Electrical sensitivity characteristics |

|   |       | 6.3.12   | I/O current injection characteristics  |

|   |       | 6.3.13   | I/O port characteristics               |

|   |       | 6.3.14   | NRST pin characteristics               |

|   |       | 6.3.15   | 12-bit ADC characteristics             |

|   |       | 6.3.16   | DAC electrical specifications          |

|   |       | 6.3.17   | Temperature sensor characteristics     |

|   |       | 6.3.18   | Comparators                            |

|   |       | 6.3.19   | Timer characteristics                  |

|   |       | 6.3.20   | Communications interfaces              |

|   |       | 6.3.21   | LCD controller                         |

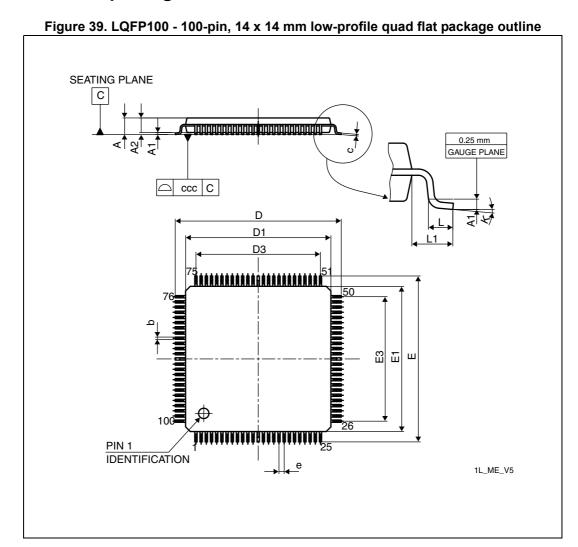

| 7 | Pack  | age info | ormation                               |

|   | 7.1   | LQFP1    | 00 package information                 |

|   | 7.2   | UFBGA    | A100 package information               |

|   | 7.3   | LQFP6    | 4 package information                  |

|   | 7.4   | TFBGA    | A64 package information                |

|   | 7.5   | LQFP4    | 8 package information                  |

|   | 7.6   | Therma   | al characteristics                     |

|   |       | 7.6.1    | Reference document                     |

| 8 | Part  | number   | ring                                   |

| • | Da:-! | alam b!- | 407                                    |

| 9 | Kevi  | sion nis | tory                                   |

STM32L083xx List of figures

# List of figures

| Figure 1.  | STM32L083xx block diagram                                                                    | 12  |

|------------|----------------------------------------------------------------------------------------------|-----|

| Figure 2.  | Clock tree                                                                                   | 24  |

| Figure 3.  | STM32L083xx LQFP100 pinout - 14 x 14 mm                                                      | 37  |

| Figure 4.  | STM32L083xx UFBGA100 ballout - 7x 7 mm                                                       | 38  |

| Figure 5.  | STM32L083xx LQFP64 pinout - 10 x 10 mm                                                       | 39  |

| Figure 6.  | STM32L083xx TFBGA64 ballout - 5x 5 mm                                                        | 40  |

| Figure 7.  | STM32L083xx LQFP48 pinout - 7 x 7 mm                                                         | 41  |

| Figure 8.  | Memory map                                                                                   | 56  |

| Figure 9.  | Pin loading conditions                                                                       | 57  |

| Figure 10. | Pin input voltage                                                                            | 57  |

| Figure 11. | Power supply scheme                                                                          | 58  |

| Figure 12. | Optional LCD power supply scheme                                                             |     |

| Figure 13. | Current consumption measurement scheme                                                       |     |

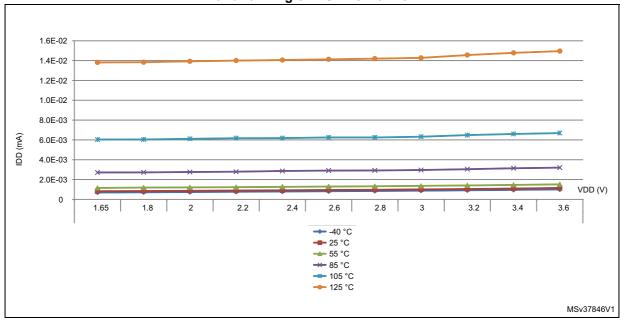

| Figure 14. | IDD vs VDD, at TA= 25/55/85/105 °C, Run mode, code running from                              |     |

| Ü          | Flash memory, Range 2, HSE, 1WS                                                              | 68  |

| Figure 15. | IDD vs VDD, at TA= 25/55/85/105 °C, Run mode, code running from                              |     |

| Ü          | Flash memory, Range 2, HSI16, 1WS                                                            | 68  |

| Figure 16. | IDD vs VDD, at TA= 25 °C, Low-power run mode, code running                                   |     |

| Ü          | from RAM, Range 3, MSI (Range 0) at 64 KHz, 0 WS                                             | 72  |

| Figure 17. | IDD vs VDD, at TA= 25/55/ 85/105/125 °C, Stop mode with RTC enabled                          |     |

| J          | and running on LSE Low drive                                                                 | 73  |

| Figure 18. | IDD vs VDD, at TA= 25/55/85/105/125 °C, Stop mode with RTC disabled,                         |     |

| Ü          | all clocks off                                                                               | 74  |

| Figure 19. | High-speed external clock source AC timing diagram                                           | 80  |

| Figure 20. | Low-speed external clock source AC timing diagram                                            |     |

| Figure 21. | HSE oscillator circuit diagram                                                               |     |

| Figure 22. | Typical application with a 32.768 kHz crystal                                                |     |

| Figure 23. | HSI16 minimum and maximum value versus temperature                                           |     |

| Figure 24. | VIH/VIL versus VDD (CMOS I/Os)                                                               |     |

| Figure 25. | VIH/VIL versus VDD (TTL I/Os)                                                                |     |

| Figure 26. | I/O AC characteristics definition                                                            |     |

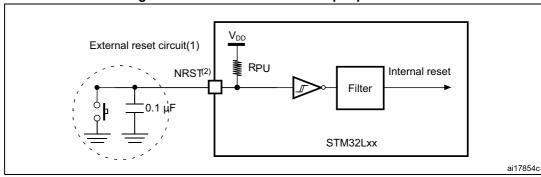

| Figure 27. | Recommended NRST pin protection                                                              | 98  |

| Figure 28. | ADC accuracy characteristics                                                                 |     |

| Figure 29. | Typical connection diagram using the ADC                                                     |     |

| Figure 30. | Power supply and reference decoupling (V <sub>REF+</sub> not connected to V <sub>DDA</sub> ) |     |

| Figure 31. | Power supply and reference decoupling (V <sub>REF+</sub> connected to V <sub>DDA</sub> )     |     |

| Figure 32. | 12-bit buffered/non-buffered DAC                                                             |     |

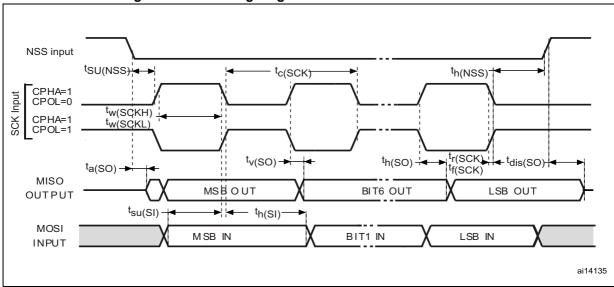

| Figure 33. | SPI timing diagram - slave mode and CPHA = 0                                                 | 112 |

| Figure 34. | SPI timing diagram - slave mode and CPHA = 1 <sup>(1)</sup>                                  | 113 |

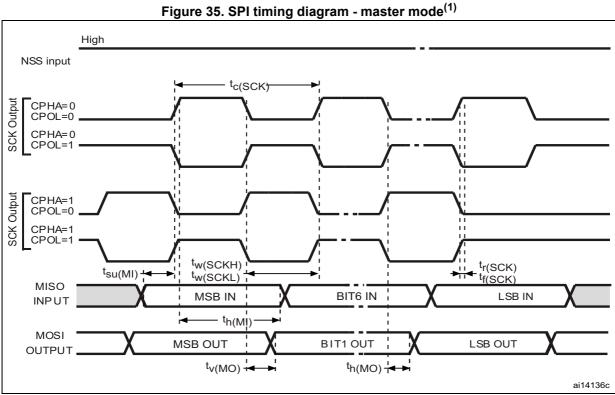

| Figure 35. | SPI timing diagram - master mode <sup>(1)</sup>                                              | 113 |

| Figure 36. | I <sup>2</sup> S slave timing diagram (Philips protocol) <sup>(1)</sup>                      | 115 |

| Figure 37. | I <sup>2</sup> S master timing diagram (Philips protocol) <sup>(1)</sup>                     | 115 |

| Figure 38. | USB timings: definition of data signal rise and fall time                                    | 117 |

| Figure 39. | LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat package outline                          |     |

| Figure 40. | LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat                                          |     |

| -          | recommended footprint                                                                        | 121 |

| Figure 41. | LQFP100 marking example (package top view)                                                   | 121 |

| Figure 42. | UFBGA100 - 100-pin, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball                           |     |

|            |                                                                                              |     |

Functional overview STM32L083xx

## 3 Functional overview

## 3.1 Low-power modes

The ultra-low-power STM32L083xx support dynamic voltage scaling to optimize its power consumption in Run mode. The voltage from the internal low-drop regulator that supplies the logic can be adjusted according to the system's maximum operating frequency and the external voltage supply.

There are three power consumption ranges:

- Range 1 (V<sub>DD</sub> range limited to 1.71-3.6 V), with the CPU running at up to 32 MHz

- Range 2 (full V<sub>DD</sub> range), with a maximum CPU frequency of 16 MHz

- Range 3 (full V<sub>DD</sub> range), with a maximum CPU frequency limited to 4.2 MHz

Seven low-power modes are provided to achieve the best compromise between low-power consumption, short startup time and available wakeup sources:

### Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs. Sleep mode power consumption at 16 MHz is about 1 mA with all peripherals off.

#### Low-power run mode

This mode is achieved with the multispeed internal (MSI) RC oscillator set to the low-speed clock (max 131 kHz), execution from SRAM or Flash memory, and internal regulator in low-power mode to minimize the regulator's operating current. In Low-power run mode, the clock frequency and the number of enabled peripherals are both limited.

### • Low-power sleep mode

This mode is achieved by entering Sleep mode with the internal voltage regulator in low-power mode to minimize the regulator's operating current. In Low-power sleep mode, both the clock frequency and the number of enabled peripherals are limited; a typical example would be to have a timer running at 32 kHz.

When wakeup is triggered by an event or an interrupt, the system reverts to the Run mode with the regulator on.

### Stop mode with RTC

The Stop mode achieves the lowest power consumption while retaining the RAM and register contents and real time clock. All clocks in the  $V_{CORE}$  domain are stopped, the PLL, MSI RC, HSE crystal and HSI RC oscillators are disabled. The LSE or LSI is still running. The voltage regulator is in the low-power mode.

Some peripherals featuring wakeup capability can enable the HSI RC during Stop mode to detect their wakeup condition.

The device can be woken up from Stop mode by any of the EXTI line, in 3.5 µs, the processor can serve the interrupt or resume the code. The EXTI line source can be any GPIO. It can be the PVD output, the comparator 1 event or comparator 2 event (if internal reference voltage is on), it can be the RTC alarm/tamper/timestamp/wakeup events, the USB/USART/I2C/LPUART/LPTIMER wakeup events.

14/139 DocID027070 Rev 3

Functional overview STM32L083xx

### 3.4.3 Voltage regulator

The regulator has three operation modes: main (MR), low power (LPR) and power down.

- MR is used in Run mode (nominal regulation)

- LPR is used in the Low-power run, Low-power sleep and Stop modes

- Power down is used in Standby mode. The regulator output is high impedance, the kernel circuitry is powered down, inducing zero consumption but the contents of the registers and RAM are lost except for the standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE crystal 32 KHz oscillator, RCC CSR).

## 3.5 Clock management

The clock controller distributes the clocks coming from different oscillators to the core and the peripherals. It also manages clock gating for low-power modes and ensures clock robustness. It features:

### • Clock prescaler

To get the best trade-off between speed and current consumption, the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler.

### Safe clock switching

Clock sources can be changed safely on the fly in Run mode through a configuration register.

### • Clock management

To reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

### System clock source

Three different clock sources can be used to drive the master clock SYSCLK:

- 1-25 MHz high-speed external crystal (HSE), that can supply a PLL

- 16 MHz high-speed internal RC oscillator (HSI), trimmable by software, that can supply a PLLMultispeed internal RC oscillator (MSI), trimmable by software, able to generate 7 frequencies (65 kHz, 131 kHz, 262 kHz, 524 kHz, 1.05 MHz, 2.1 MHz, 4.2 MHz). When a 32.768 kHz clock source is available in the system (LSE), the MSI frequency can be trimmed by software down to a ±0.5% accuracy.

### Auxiliary clock source

Two ultra-low-power clock sources that can be used to drive the LCD controller and the real-time clock:

- 32.768 kHz low-speed external crystal (LSE)

- 37 kHz low-speed internal RC (LSI), also used to drive the independent watchdog.

The LSI clock can be measured using the high-speed internal RC oscillator for greater precision.

#### RTC and LCD clock source

The LSI, LSE or HSE sources can be chosen to clock the RTC and the LCD, whatever the system clock.

#### USB clock source

A 48 MHz clock trimmed through the USB SOF or LSE supplies the USB interface.

577

22/139 DocID027070 Rev 3

STM32L083xx Functional overview

## 3.6 Low-power real-time clock and backup registers

The real time clock (RTC) and the 5 backup registers are supplied in all modes including standby mode. The backup registers are five 32-bit registers used to store 20 bytes of user application data. They are not reset by a system reset, or when the device wakes up from Standby mode.

The RTC is an independent BCD timer/counter. Its main features are the following:

- Calendar with subsecond, seconds, minutes, hours (12 or 24 format), week day, date, month, year, in BCD (binary-coded decimal) format

- Automatically correction for 28, 29 (leap year), 30, and 31 day of the month

- Two programmable alarms with wake up from Stop and Standby mode capability

- Periodic wakeup from Stop and Standby with programmable resolution and period

- On-the-fly correction from 1 to 32767 RTC clock pulses. This can be used to synchronize it with a master clock.

- Reference clock detection: a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar precision.

- Digital calibration circuit with 1 ppm resolution, to compensate for quartz crystal inaccuracy

- 2 anti-tamper detection pins with programmable filter. The MCU can be woken up from Stop and Standby modes on tamper event detection.

- Timestamp feature which can be used to save the calendar content. This function can be triggered by an event on the timestamp pin, or by a tamper event. The MCU can be woken up from Stop and Standby modes on timestamp event detection.

The RTC clock sources can be:

- A 32.768 kHz external crystal

- A resonator or oscillator

- The internal low-power RC oscillator (typical frequency of 37 kHz)

- The high-speed external clock

## 3.7 General-purpose inputs/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions, and can be individually remapped using dedicated alternate function registers. All GPIOs are high current capable. Each GPIO output, speed can be slowed (40 MHz, 10 MHz, 2 MHz, 400 kHz). The alternate function configuration of I/Os can be locked if needed following a specific sequence in order to avoid spurious writing to the I/O registers. The I/O controller is connected to a dedicated IO bus with a toggling speed of up to 32 MHz.

### **Extended interrupt/event controller (EXTI)**

The extended interrupt/event controller consists of 29 edge detector lines used to generate interrupt/event requests. Each line can be individually configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 84 GPIOs can be connected to the 16 configurable interrupt/event lines. The 13 other lines are connected to PVD, RTC, USB, USARTs, I2C, LPUART, LPTIMER or comparator events.

STM32L083xx Functional overview

### 3.19.3 Low-power universal asynchronous receiver transmitter (LPUART)

The devices embed one Low-power UART. The LPUART supports asynchronous serial communication with minimum power consumption. It supports half duplex single wire communication and modem operations (CTS/RTS). It allows multiprocessor communication.

The LPUART has a clock domain independent from the CPU clock. It can wake up the system from Stop mode using baudrates up to 46 Kbaud. The Wakeup events from Stop mode are programmable and can be:

- Start bit detection

- Or any received data frame

- Or a specific programmed data frame

Only a 32.768 kHz clock (LSE) is needed to allow LPUART communication up to 9600 baud. Therefore, even in Stop mode, the LPUART can wait for an incoming frame while having an extremely low energy consumption. Higher speed clock can be used to reach higher baudrates.

LPUART interface can be served by the DMA controller.

## 3.19.4 Serial peripheral interface (SPI)/Inter-integrated sound (I2S)

Up to two SPIs are able to communicate at up to 16 Mbits/s in slave and master modes in full-duplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes.

The USARTs with synchronous capability can also be used as SPI master.

One standard I2S interfaces (multiplexed with SPI2) is available. It can operate in master or slave mode, and can be configured to operate with a 16-/32-bit resolution as input or output channels. Audio sampling frequencies from 8 kHz up to 192 kHz are supported. When the I2S interfaces is configured in master mode, the master clock can be output to the external DAC/CODEC at 256 times the sampling frequency.

The SPIs can be served by the DMA controller.

Refer to Table 14 for the differences between SPI1 and SPI2.

Table 14. SPI/I2S implementation

| SPI features <sup>(1)</sup> | SPI1 | SPI2 |

|-----------------------------|------|------|

| Hardware CRC calculation    | Х    | Х    |

| I2S mode                    | -    | Х    |

| TI mode                     | Х    | Х    |

<sup>1.</sup> X = supported.

|      |      |                                                                                                   |                                         | Table 19. Alter                                                                 | nate function         | ns port C                                          |                                              |                                                             |                                   |

|------|------|---------------------------------------------------------------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------|-----------------------|----------------------------------------------------|----------------------------------------------|-------------------------------------------------------------|-----------------------------------|

|      |      | AF0                                                                                               | AF1                                     | AF2                                                                             | AF3                   | AF4                                                | AF5                                          | AF6                                                         | AF7                               |

|      | Port | SPI1/SPI2/I2S2/<br>USART1/2/<br>LPUART1/USB/<br>LPTIM1/TSC/<br>TIM2/21/22/<br>EVENTOUT/<br>SYS_AF | SPI1/SPI2/I2S2/I2C1/<br>LCD/<br>TIM2/21 | SPI1/SPI2/I2S2/<br>LPUART1/<br>USART5/USB/<br>LPTIM1/TIM2/3<br>/EVENTOUT/SYS_AF | I2C1/TSC/<br>EVENTOUT | I2C1/USART1/2/<br>LPUART1/<br>TIM3/22/<br>EVENTOUT | SPI2/I2S2<br>/I2C2/<br>USART1/<br>TIM2/21/22 | I2C1/2/<br>LPUART1/<br>USART4/<br>UASRT5/TIM21/E<br>VENTOUT | I2C3/LPUART1/<br>COMP1/2/<br>TIM3 |

|      | PC0  | LPTIM1_IN1                                                                                        | LCD_SEG18                               | EVENTOUT                                                                        | TSC_G7_IO1            |                                                    |                                              | LPUART1_RX                                                  | I2C3_SCL                          |

|      | PC1  | LPTIM1_OUT                                                                                        | LCD_SEG19                               | EVENTOUT                                                                        | TSC_G7_IO2            |                                                    |                                              | LPUART1_TX                                                  | I2C3_SDA                          |

|      | PC2  | LPTIM1_IN2                                                                                        | LCD_SEG20                               | SPI2_MISO/<br>I2S2_MCK                                                          | TSC_G7_IO3            |                                                    |                                              |                                                             |                                   |

|      | PC3  | LPTIM1_ETR                                                                                        | LCD_SEG21                               | SPI2_MOSI/<br>I2S2_SD                                                           | TSC_G7_IO4            |                                                    |                                              |                                                             |                                   |

|      | PC4  | EVENTOUT                                                                                          | LCD_SEG22                               | LPUART1_TX                                                                      |                       |                                                    |                                              |                                                             |                                   |

|      | PC5  |                                                                                                   | LCD_SEG23                               | LPUART1_RX                                                                      | TSC_G3_IO1            |                                                    |                                              |                                                             |                                   |

|      | PC6  | TIM22_CH1                                                                                         | LCD_SEG24                               | TIM3_CH1                                                                        | TSC_G8_IO1            |                                                    |                                              |                                                             |                                   |

| ٠    | PC7  | TIM22_CH2                                                                                         | LCD_SEG25                               | TIM3_CH2                                                                        | TSC_G8_IO2            |                                                    |                                              |                                                             |                                   |

| Port | PC8  | TIM22_ETR                                                                                         | LCD_SEG26                               | TIM3_CH3                                                                        | TSC_G8_IO3            |                                                    |                                              |                                                             |                                   |

|      | PC9  | TIM21_ETR                                                                                         | LCD_SEG27                               | USB_OE/TIM3_CH4                                                                 | TSC_G8_IO4            |                                                    |                                              |                                                             | I2C3_SDA                          |

|      | PC10 | LPUART1_TX                                                                                        | LCD_COM4/LCD_SEG<br>28/LCD_SEG48        |                                                                                 |                       |                                                    |                                              | USART4_TX                                                   |                                   |

|      | PC11 | LPUART1_RX                                                                                        | LCD_COM5/LCD_SEG<br>29/LCD_SEG49        |                                                                                 |                       |                                                    |                                              | USART4_RX                                                   |                                   |

|      | PC12 |                                                                                                   | LCD_COM6/LCD_SEG<br>30/LCD_SEG50        | USART5_TX                                                                       |                       |                                                    |                                              | USART4_CK                                                   |                                   |

|      | PC13 |                                                                                                   |                                         |                                                                                 |                       |                                                    |                                              |                                                             |                                   |

|      | PC14 |                                                                                                   |                                         |                                                                                 |                       |                                                    |                                              |                                                             |                                   |

|      | PC15 |                                                                                                   |                                         |                                                                                 |                       |                                                    |                                              |                                                             |                                   |

|        | Table 21. Alternate functions port E |                                                                                                   |                                     |                                                                                     |                       |                                                    |                                              |                                                             |                               |

|--------|--------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------|-----------------------|----------------------------------------------------|----------------------------------------------|-------------------------------------------------------------|-------------------------------|

|        |                                      | AF0                                                                                               | AF1                                 | AF2                                                                                 | AF3                   | AF4                                                | AF5                                          | AF6                                                         | AF7                           |

| Port   |                                      | SPI1/SPI2/I2S2/<br>USART1/2/<br>LPUART1/USB/<br>LPTIM1/TSC/<br>TIM2/21/22/<br>EVENTOUT/<br>SYS_AF | SPI1/SPI2/I2S2/I2C1<br>/LCD/TIM2/21 | SPI1/SPI2/I2S2/<br>LPUART1/<br>USART5/USB/<br>LPTIM1/TIM2/3<br>/EVENTOUT/<br>SYS_AF | I2C1/TSC/<br>EVENTOUT | I2C1/USART1/2/<br>LPUART1/<br>TIM3/22/<br>EVENTOUT | SPI2/I2S2<br>/I2C2/<br>USART1/<br>TIM2/21/22 | I2C1/2/<br>LPUART1/<br>USART4/<br>UASRT5/TIM21/<br>EVENTOUT | I2C3/LPUART1/<br>COMP1/2/TIM3 |

|        | PE0                                  | -                                                                                                 | LCD_SEG36                           | EVENTOUT                                                                            | -                     | -                                                  | -                                            | -                                                           | -                             |

|        | PE1                                  | -                                                                                                 | LCD_SEG37                           | EVENTOUT                                                                            | -                     | -                                                  | -                                            | -                                                           | -                             |

|        | PE2                                  | -                                                                                                 | LCD_SEG38                           | TIM3_ETR                                                                            | -                     | -                                                  | -                                            | -                                                           | -                             |

|        | PE3                                  | TIM22_CH1                                                                                         | LCD_SEG39                           | TIM3_CH1                                                                            | -                     | -                                                  | -                                            | -                                                           | -                             |

|        | PE4                                  | TIM22_CH2                                                                                         | -                                   | TIM3_CH2                                                                            | -                     | -                                                  | -                                            | -                                                           | -                             |

|        | PE5                                  | TIM21_CH1                                                                                         | -                                   | TIM3_CH3                                                                            | -                     | -                                                  | -                                            | -                                                           | -                             |

|        | PE6                                  | TIM21_CH2                                                                                         | -                                   | TIM3_CH4                                                                            | -                     | -                                                  | -                                            | -                                                           | -                             |

| Port E | PE7                                  | -                                                                                                 | LCD_SEG45                           | -                                                                                   | -                     | -                                                  | -                                            | USART5_CK/U<br>SART5_RTS_D<br>E                             | -                             |

| _      | PE8                                  | -                                                                                                 | LCD_SEG46                           | -                                                                                   | -                     | -                                                  | -                                            | USART4_TX                                                   | -                             |

|        | PE9                                  | TIM2_CH1                                                                                          | LCD_SEG47                           | TIM2_ETR                                                                            | -                     | -                                                  | -                                            | USART4_RX                                                   | -                             |

|        | PE10                                 | TIM2_CH2                                                                                          | LCD_SEG40                           | -                                                                                   | -                     | -                                                  | -                                            | USART5_TX                                                   | -                             |

|        | PE11                                 | TIM2_CH3                                                                                          | -                                   | -                                                                                   | -                     | -                                                  | -                                            | USART5_RX                                                   | -                             |

|        | PE12                                 | TIM2_CH4                                                                                          | -                                   | SPI1_NSS                                                                            | -                     | -                                                  | -                                            | -                                                           | -                             |

|        | PE13                                 | -                                                                                                 | LCD_SEG41                           | SPI1_SCK                                                                            | -                     | -                                                  | -                                            | -                                                           | -                             |

|        | PE14                                 | -                                                                                                 | LCD_SEG42                           | SPI1_MISO                                                                           | -                     | -                                                  | -                                            | -                                                           | -                             |

|        | PE15                                 | -                                                                                                 | LCD_SEG43                           | SPI1_MOSI                                                                           | -                     | -                                                  | -                                            | -                                                           | -                             |

Electrical characteristics STM32L083xx

## 6.1.6 Power supply scheme

Standby-power circuitry (OSC32,RTC,Wake-up logic, RTC backup registers) Ю GP I/Os Logic Kernel logic (CPU, Digital & Memories) Regulator N × 100 nF + 1 × 10 µF  $V_{\text{DDA}}$ V<sub>REF</sub> 100 nF + 1 μF Analog: RC,PLL,COMP, ADC/ 100 nF  $V_{\mathsf{REF}}$ DAC  $V_{SSA}$  $V_{\text{LCD}} \ V_{\text{SS}}$ LCD  $V_{\text{SS}}$ USB  $V_{DD\_USB} \big[$ transceiver MSv33790V1

Figure 11. Power supply scheme

Table 37. Typical and maximum current consumptions in Stop mode

| Symbol                 | Parameter                   | Conditions                                 | Тур   | Max <sup>(1)</sup> | Unit |

|------------------------|-----------------------------|--------------------------------------------|-------|--------------------|------|

|                        | Supply current in Stop mode | $T_A = -40 \text{ to } 25^{\circ}\text{C}$ | 0,43  | 1,00               |      |

|                        |                             | T <sub>A</sub> = 55°C                      | 0,735 | 2,50               |      |

| I <sub>DD</sub> (Stop) |                             | T <sub>A</sub> = 85°C                      | 2,25  | 4,90               | μΑ   |

|                        |                             | T <sub>A</sub> = 105°C                     | 5,3   | 13,00              |      |

|                        |                             | T <sub>A</sub> = 125°C                     | 12,5  | 28,00              |      |

<sup>1.</sup> Guaranteed by characterization results at 125 °C, unless otherwise specified.

Figure 17.  $I_{DD}$  vs  $V_{DD}$ , at  $T_A$ = 25/55/ 85/105/125 °C, Stop mode with RTC enabled and running on LSE Low drive

### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 46*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                   | Parameter                                 | Conditions <sup>(2)</sup>                       | Min <sup>(2)</sup> | Тур    | Max  | Unit |

|--------------------------|-------------------------------------------|-------------------------------------------------|--------------------|--------|------|------|

| f <sub>LSE</sub>         | LSE oscillator frequency                  |                                                 | -                  | 32.768 | -    | kHz  |

| G <sub>m</sub>           |                                           | LSEDRV[1:0]=00 lower driving capability         | -                  | -      | 0.5  |      |

|                          | Maximum critical crystal transconductance | LSEDRV[1:0]= 01 medium low driving capability   | -                  | -      | 0.75 | µA/V |

|                          |                                           | LSEDRV[1:0] = 10 medium high driving capability | -                  | -      | 1.7  | μΑνν |

|                          |                                           | LSEDRV[1:0]=11 higher driving capability        | -                  | -      | 2.7  |      |

| t <sub>SU(LSE)</sub> (3) | Startup time                              | V <sub>DD</sub> is stabilized                   | -                  | 2      | -    | S    |

Table 46. LSE oscillator characteristics<sup>(1)</sup>

For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

Resonator with integrated capacitors

CL1

OSC32\_IN

Drive programmable amplifier

OSC32\_OUT

OSC32\_OUT

MS30253V2

Figure 22. Typical application with a 32.768 kHz crystal

Note:

Note:

An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

<sup>1.</sup> Guaranteed by design.

Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

Guaranteed by characterization results. t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer. To increase speed, address a lower-drive quartz with a high- driver mode.

| Symbol                                | Parameter                          | Condition                                | Тур | Max | Unit  |

|---------------------------------------|------------------------------------|------------------------------------------|-----|-----|-------|

|                                       |                                    | MSI range 0                              | -   | 40  |       |

|                                       |                                    | MSI range 1                              | -   | 20  |       |

|                                       |                                    | MSI range 2                              | -   | 10  |       |

|                                       |                                    | MSI range 3                              | -   | 4   |       |

| t(2)                                  | MSI oscillator stabilization time  | MSI range 4                              | -   | 2.5 | μs    |

| t <sub>STAB(MSI)</sub> <sup>(2)</sup> |                                    | MSI range 5                              | -   | 2   |       |

|                                       |                                    | MSI range 6,<br>Voltage range 1<br>and 2 | -   | 2   |       |

|                                       |                                    | MSI range 3,<br>Voltage range 3          | -   | 3   |       |

| forman                                | MSI oscillator frequency overshoot | Any range to range 5                     | -   | 4   | MHz   |

| f <sub>OVER(MSI)</sub>                | The resonator requeries eversions  | Any range to range 6                     | -   | 6   | IVIMZ |

Table 50. MSI oscillator characteristics (continued)

### 6.3.8 PLL characteristics

t<sub>LOCK</sub>

Jitter

I<sub>DDA</sub>(PLL)

I<sub>DD</sub>(PLL)

The parameters given in *Table 51* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 26*.

Value **Symbol Parameter** Max<sup>(1)</sup> Min Typ PLL input clock<sup>(2)</sup> 2 24 f<sub>PLL IN</sub> PLL input clock duty cycle 45 55 2 32 PLL output clock f<sub>PLL\_OUT</sub> PLL input = 16 MHz

Table 51. PLL characteristics

115

220

120

160

$\pm\,600$

450

150

PLL VCO = 96 MHz

Cycle-to-cycle jitter

Current consumption on V<sub>DDA</sub>

Current consumption on  $V_{\mbox{\scriptsize DD}}$

Unit

MHz

%

MHz

μs

ps

μΑ

<sup>1.</sup> This is a deviation for an individual part, once the initial frequency has been measured.

<sup>2.</sup> Guaranteed by characterization results.

<sup>1.</sup> Guaranteed by characterization results.

<sup>2.</sup> Take care of using the appropriate multiplier factors so as to have PLL input clock values compatible with the range defined by  $f_{\text{PLL\_OUT}}$ .

Electrical characteristics STM32L083xx

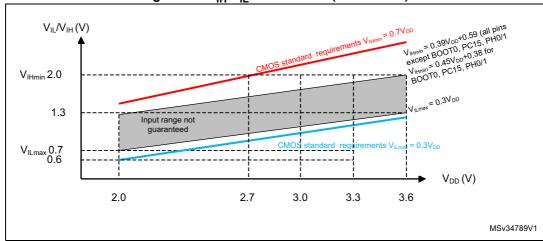

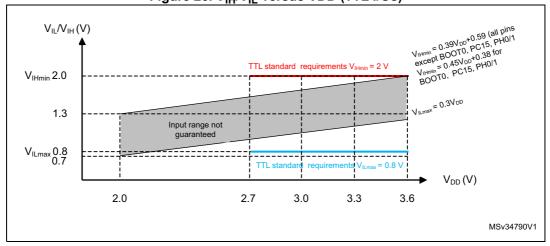

Figure 24. V<sub>IH</sub>/V<sub>IL</sub> versus VDD (CMOS I/Os)

Figure 25. V<sub>IH</sub>/V<sub>IL</sub> versus VDD (TTL I/Os)

### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to  $\pm 8$  mA, and sink or source up to  $\pm 15$  mA with the non-standard  $V_{OL}/V_{OH}$  specifications given in *Table 61*.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 6.2*:

- The sum of the currents sourced by all the I/Os on  $V_{DD}$ , plus the maximum Run consumption of the MCU sourced on  $V_{DD}$ , cannot exceed the absolute maximum rating  $I_{VDD(\Sigma)}$  (see *Table 24*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating I<sub>VSS(Σ)</sub> (see *Table 24*).

57

Electrical characteristics STM32L083xx

Figure 27. Recommended NRST pin protection

- 1. The reset network protects the device against parasitic resets.

- 2. The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in *Table 63*. Otherwise the reset will not be taken into account by the device.

### 6.3.15 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 64* are derived from tests performed under ambient temperature, f<sub>PCLK</sub> frequency and V<sub>DDA</sub> supply voltage conditions summarized in *Table 26: General operating conditions*.

Note: It is recommended to perform a calibration after each power-up.

**Table 64. ADC characteristics**

| Symbol                             | Parameter                             | Conditions                                      | Min                 | Тур | Max               | Unit               |

|------------------------------------|---------------------------------------|-------------------------------------------------|---------------------|-----|-------------------|--------------------|

| V                                  | Analog supply voltage for             | Fast channel                                    | 1.65                | -   | 3.6               | V                  |

| $V_{DDA}$                          | ADC on                                | Standard channel                                | 1.75 <sup>(1)</sup> | -   | 3.6               | ]                  |

| V <sub>REF+</sub>                  | Positive reference voltage            | -                                               | 1.65                |     | $V_{DDA}$         | V                  |

| V <sub>REF-</sub>                  | Negative reference voltage            | -                                               | -                   | 0   | -                 |                    |

|                                    | Current consumption of the            | 1.14 Msps                                       | -                   | 200 | -                 |                    |

|                                    | ADC on $V_{DDA}$ and $V_{REF+}$       | 10 ksps                                         | -                   | 40  | -                 | ] <u>,</u>         |

| I <sub>DDA</sub> (ADC)             | Current consumption of the            | 1.14 Msps                                       | -                   | 70  | -                 | - μΑ               |

|                                    | ADC on V <sub>DD</sub> <sup>(2)</sup> | 10 ksps                                         | -                   | 1   | -                 |                    |

|                                    |                                       | Voltage scaling Range 1                         | 0.14                | -   | 16                |                    |

| $f_{ADC}$                          | ADC clock frequency                   | Voltage scaling Range 2                         | 0.14                | -   | 8                 | MHz                |

|                                    |                                       | Voltage scaling Range 3                         | 0.14                | -   | 4                 |                    |

| f <sub>S</sub> <sup>(3)</sup>      | Sampling rate                         | 12-bit resolution                               | 0.01                | -   | 1.14              | MHz                |

| f <sub>TRIG</sub> <sup>(3)</sup>   | External trigger frequency            | f <sub>ADC</sub> = 16 MHz,<br>12-bit resolution | -                   | -   | 941               | kHz                |

|                                    |                                       | -                                               | -                   | -   | 17                | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub>                   | Conversion voltage range              | -                                               | 0                   | -   | V <sub>REF+</sub> | V                  |

| R <sub>AIN</sub> <sup>(3)</sup>    | External input impedance              | See Equation 1 and Table 65 for details         | -                   | -   | 50                | kΩ                 |

| R <sub>ADC</sub> <sup>(3)(4)</sup> | Sampling switch resistance            | -                                               | -                   | -   | 1                 | kΩ                 |

98/139 DocID027070 Rev 3

Table 76. SPI characteristics in voltage Range 2 (1)

| Symbol                                    | Parameter                         | Conditions                                               | Min     | Тур   | Max              | Unit |

|-------------------------------------------|-----------------------------------|----------------------------------------------------------|---------|-------|------------------|------|

|                                           |                                   | Master mode                                              |         |       | 8                |      |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub> | SPI clock frequency               | Slave mode Transmitter<br>1.65 <v<sub>DD&lt;3.6V</v<sub> | _       | -     | 8                | MHz  |

| (SCK)                                     |                                   | Slave mode Transmitter 2.7 <v<sub>DD&lt;3.6V</v<sub>     |         |       | 8 <sup>(2)</sup> |      |

| Duty <sub>(SCK)</sub>                     | Duty cycle of SPI clock frequency | Slave mode                                               | 30      | 50    | 70               | %    |

| t <sub>su(NSS)</sub>                      | NSS setup time                    | Slave mode, SPI presc = 2                                | 4*Tpclk | -     | -                |      |

| t <sub>h(NSS)</sub>                       | NSS hold time                     | Slave mode, SPI presc = 2                                | 2*Tpclk | -     | -                |      |

| $t_{w(SCKH)}$ $t_{w(SCKL)}$               | SCK high and low time             | Master mode                                              | Tpclk-2 | Tpclk | Tpclk+2          |      |

| t <sub>su(MI)</sub>                       | Data input setup time             | Master mode                                              | 0       | -     | -                |      |

| t <sub>su(SI)</sub>                       | Data input setup time             | Slave mode                                               | 3       | -     | -                |      |

| t <sub>h(MI)</sub>                        | Data input hold time              | Master mode                                              | 11      | -     | -                |      |

| t <sub>h(SI)</sub>                        | Data input noid time              | Slave mode                                               | 4.5     | -     | -                | ns   |

| t <sub>a(SO</sub>                         | Data output access time           | Slave mode                                               | 18      | -     | 52               |      |

| t <sub>dis(SO)</sub>                      | Data output disable time          | Slave mode                                               | 12      | -     | 42               |      |

| t <sub>v(SO)</sub>                        | Data output valid time            | Slave mode                                               | -       | 20    | 56.5             |      |

| t <sub>v(MO)</sub>                        |                                   | Master mode                                              | -       | 5     | 9                |      |

| t <sub>h(SO)</sub>                        | Data output hold time             | Slave mode                                               | 13      | -     | -                |      |

| t <sub>h(MO)</sub>                        | Data output noid time             | Master mode                                              | 3       | -     | -                |      |

<sup>1.</sup> Guaranteed by characterization results.

<sup>2.</sup> The maximum SPI clock frequency in slave transmitter mode is determined by the sum of  $t_{v(SO)}$  and  $t_{su(MI)}$  which has to fit into SCK low or high phase preceding the SCK sampling edge. This value can be achieved when the SPI communicates with a master having  $t_{su(MI)} = 0$  while Duty<sub>(SCK)</sub> = 50%.

Figure 34. SPI timing diagram - slave mode and CPHA =  $1^{(1)}$

1. Measurement points are done at CMOS levels:  $0.3V_{DD}$  and  $0.7V_{DD}$ .

1. Measurement points are done at CMOS levels:  $0.3V_{DD}$  and  $0.7V_{DD}$ .

## 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status *are available at www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

## 7.1 LQFP100 package information

1. Drawing is not to scale. Dimensions are in millimeters.

Package information STM32L083xx

## 7.6 Thermal characteristics

The maximum chip-junction temperature,  $T_J$  max, in degrees Celsius, may be calculated using the following equation:

$T_J \max = T_A \max + (P_D \max \times \Theta_{JA})$

### Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- Θ<sub>JA</sub> is the package junction-to-ambient thermal resistance, in °C/W,

- $P_D$  max is the sum of  $P_{INT}$  max and  $P_{I/O}$  max ( $P_D$  max =  $P_{INT}$  max +  $P_{I/O}$ max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

P<sub>I/O</sub> max represents the maximum power dissipation on output pins where:

$$\mathsf{P}_\mathsf{I/O} \; \mathsf{max} = \Sigma \; (\mathsf{V}_\mathsf{OL} \times \mathsf{I}_\mathsf{OL}) + \Sigma ((\mathsf{V}_\mathsf{DD} - \mathsf{V}_\mathsf{OH}) \times \mathsf{I}_\mathsf{OH}),$$

taking into account the actual  $V_{OL}$  /  $I_{OL}$  and  $V_{OH}$  /  $I_{OH}$  of the I/Os at low and high level in the application.

| Symbol        | Parameter                                                                  | Value | Unit |

|---------------|----------------------------------------------------------------------------|-------|------|

| $\Theta_{JA}$ | Thermal resistance junction-ambient<br>LQFP48 - 7 x 7 mm / 0.5 mm pitch    | 54    |      |

|               | Thermal resistance junction-ambient LQFP64 - 10 x 10 mm / 0.5 mm pitch     | 46    |      |

|               | Thermal resistance junction-ambient TFBGA64 - 5 x 5 mm / 0.5 mm pitch      | 64    | °C/W |

|               | Thermal resistance junction-ambient<br>LQFP100 - 14 x 14 mm / 0.5 mm pitch | 41    |      |

|               | Thermal resistance junction-ambient UFBGA100 - 7 x 7 mm / 0.5 mm pitch     | 57    |      |

Table 90. Thermal characteristics

STM32L083xx Revision history

# 9 Revision history

Table 92. Document revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 03-Aug-2015 | 1        | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 26-Oct-2015 | 2        | Added UFBGA100 package. Changed confidentiality level to public. Updated datasheet status to "production data". Modified ultra-low-power platform features on cover page. Changed LCD_VLCD1 into LCD_VLCD2 in Section 3.13.2: VLCD voltage monitoring. In Section 6: Electrical characteristics, updated notes related to values guaranteed by characterization. Updated $ \Delta V_{SS} $ definition to include $V_{REF-}$ in Table 23: Voltage characteristics. Added $\Sigma V_{DD_USB}$ and updated $\Sigma I_{IO(PIN)}$ in Figure 24: Current characteristics. Updated Table 56: EMI characteristics. Updated $T_{RIG}$ and $V_{AIN}$ maximum value, added $V_{REF+}$ and $V_{REF-}$ in Table 64: ADC characteristics. Updated Figure 53: LQFP48 marking example (package top view). |