Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 32MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT     |

| Number of I/O              | 84                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 3K x 8                                                                |

| RAM Size                   | 20K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                           |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 100-LQFP                                                              |

| Supplier Device Package    | 100-LQFP (14x14)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l083v8t6 |

Contents STM32L083xx

# **Contents**

| 1 | Intro | duction                                                     | . 9 |

|---|-------|-------------------------------------------------------------|-----|

| 2 | Desc  | cription                                                    | 10  |

|   | 2.1   | Device overview                                             | .11 |

|   | 2.2   | Ultra-low-power device continuum                            | 13  |

| 3 | Fund  | ctional overview                                            | 14  |

|   | 3.1   | Low-power modes                                             | 14  |

|   | 3.2   | Interconnect matrix                                         | 19  |

|   | 3.3   | ARM® Cortex®-M0+ core with MPU                              | 20  |

|   | 3.4   | Reset and supply management                                 | 21  |

|   |       | 3.4.1 Power supply schemes                                  | 21  |

|   |       | 3.4.2 Power supply supervisor                               | 21  |

|   |       | 3.4.3 Voltage regulator                                     | 22  |

|   | 3.5   | Clock management                                            | 22  |

|   | 3.6   | Low-power real-time clock and backup registers              | 25  |

|   | 3.7   | General-purpose inputs/outputs (GPIOs)                      | 25  |

|   | 3.8   | Memories                                                    | 26  |

|   | 3.9   | Boot modes                                                  | 26  |

|   | 3.10  | Direct memory access (DMA)                                  | 27  |

|   | 3.11  | Liquid crystal display (LCD)                                | 27  |

|   | 3.12  | Analog-to-digital converter (ADC)                           | 27  |

|   | 3.13  | Temperature sensor                                          | 28  |

|   |       | 3.13.1 Internal voltage reference (V <sub>REFINT</sub> )    | 28  |

|   |       | 3.13.2 V <sub>LCD</sub> voltage monitoring                  | 29  |

|   | 3.14  | Digital-to-analog converter (DAC)                           | 29  |

|   | 3.15  | Ultra-low-power comparators and reference voltage           | 29  |

|   | 3.16  | Touch sensing controller (TSC)                              | 30  |

|   | 3.17  | AES                                                         | 31  |

|   | 3.18  | Timers and watchdogs                                        | 31  |

|   |       | 3.18.1 General-purpose timers (TIM2, TIM3, TIM21 and TIM22) | 31  |

|   |       | 3.18.2 Low-power Timer (LPTIM)                              | 32  |

STM32L083xx List of tables

# List of tables

| Table 1.  | Device summary                                                              | 1  |

|-----------|-----------------------------------------------------------------------------|----|

| Table 2.  | Ultra-low-power STM32L083xxx device features and peripheral counts          | 11 |

| Table 3.  | Functionalities depending on the operating power supply range               | 16 |

| Table 4.  | CPU frequency range depending on dynamic voltage scaling                    | 16 |

| Table 5.  | Functionalities depending on the working mode                               |    |

|           | (from Run/active down to standby)                                           | 17 |

| Table 6.  | STM32L0xx peripherals interconnect matrix                                   | 19 |

| Table 7.  | Temperature sensor calibration values                                       | 28 |

| Table 8.  | Internal voltage reference measured values                                  | 28 |

| Table 9.  | Capacitive sensing GPIOs available on STM32L083xx devices                   | 30 |

| Table 10. | Timer feature comparison                                                    | 31 |

| Table 11. | Comparison of I2C analog and digital filters                                |    |

| Table 12. | STM32L083xx I <sup>2</sup> C implementation                                 | 33 |

| Table 13. | USART implementation                                                        |    |

| Table 14. | SPI/I2S implementation                                                      | 35 |

| Table 15. | Legend/abbreviations used in the pinout table                               |    |

| Table 16. | STM32L083xx pin definition                                                  |    |

| Table 17. | Alternate functions port A                                                  | 50 |

| Table 18. | Alternate functions port B                                                  |    |

| Table 19. | Alternate functions port C                                                  |    |

| Table 20. | Alternate functions port D                                                  |    |

| Table 21. | Alternate functions port E                                                  |    |

| Table 22. | Alternate functions port H                                                  |    |

| Table 23. | Voltage characteristics                                                     |    |

| Table 24. | Current characteristics                                                     |    |

| Table 25. | Thermal characteristics                                                     |    |

| Table 26. | General operating conditions                                                |    |

| Table 27. | Embedded reset and power control block characteristics                      |    |

| Table 28. | Embedded internal reference voltage calibration values                      |    |

| Table 29. | Embedded internal reference voltage                                         | 65 |

| Table 30. | Current consumption in Run mode, code with data processing running from     |    |

|           | Flash memory                                                                | 67 |

| Table 31. | Current consumption in Run mode vs code type,                               |    |

|           | code with data processing running from Flash memory                         |    |

| Table 32. | Current consumption in Run mode, code with data processing running from RAM | 69 |

| Table 33. | Current consumption in Run mode vs code type,                               |    |

|           | code with data processing running from RAM                                  |    |

| Table 34. | Current consumption in Sleep mode                                           |    |

| Table 35. | Current consumption in Low-power run mode                                   |    |

| Table 36. | Current consumption in Low-power sleep mode                                 |    |

| Table 37. | Typical and maximum current consumptions in Stop mode                       |    |

| Table 38. | Typical and maximum current consumptions in Standby mode                    |    |

| Table 39. | Average current consumption during Wakeup                                   |    |

| Table 40. | Peripheral current consumption in Run or Sleep mode                         |    |

| Table 41. | Peripheral current consumption in Stop and Standby mode                     |    |

| Table 42. | Low-power mode wakeup timings                                               |    |

| Table 43. | High-speed external user clock characteristics                              |    |

| Table 44. | Low-speed external user clock characteristics                               | 81 |

Description STM32L083xx

## 2 Description

The ultra-low-power STM32L083xx microcontrollers incorporate the connectivity power of the universal serial bus (USB 2.0 crystal-less) with the high-performance ARM® Cortex®-M0+ 32-bit RISC core operating at a 32 MHz frequency, a memory protection unit (MPU), high-speed embedded memories (up to 192 Kbytes of Flash program memory, 6 Kbytes of data EEPROM and 20 Kbytes of RAM) plus an extensive range of enhanced I/Os and peripherals.

The STM32L083xx device provide high power efficiency for a wide range of performance. It is achieved with a large choice of internal and external clock sources, an internal voltage adaptation and several low-power modes.

The STM32L083xx device offer several analog features, one 12-bit ADC with hardware oversampling, two DACs, two ultra-low-power comparators, AES, several timers, one low-power timer (LPTIM), four general-purpose 16-bit timers and two basic timer, one RTC and one SysTick which can be used as timebases. They also feature two watchdogs, one watchdog with independent clock and window capability and one window watchdog based on bus clock.

Moreover, the STM32L083xx devices embed standard and advanced communication interfaces: up to three I2Cs, two SPIs, one I2S, four USARTs, a low-power UART (LPUART), and a crystal-less USB. The devices offer up to 24 capacitive sensing channels to simply add touch sensing functionality to any application.

The STM32L083xx also include a real-time clock and a set of backup registers that remain powered in Standby mode.

Finally, their integrated LCD controller has a built-in LCD voltage generator that allows to drive up to 8 multiplexed LCDs with contrast independent of the supply voltage.

The ultra-low-power STM32L083xx devices operate from a 1.8 to 3.6 V power supply (down to 1.65 V at power down) with BOR and from a 1.65 to 3.6 V power supply without BOR option. They are available in the -40 to +125 °C temperature range. A comprehensive set of power-saving modes allows the design of low-power applications.

10/139 DocID027070 Rev 3

STM32L083xx Description

### 2.1 Device overview

Table 2. Ultra-low-power STM32L083xxx device features and peripheral counts

| Peripheral                  |                       | STM32L083<br>V8      | STM32L083<br>CB                 | STM32L083<br>VB      | STM32L083<br>RB                  | STM32L083<br>CZ  | STM32L083<br>VZ      | STM32L083<br>RZ                     |

|-----------------------------|-----------------------|----------------------|---------------------------------|----------------------|----------------------------------|------------------|----------------------|-------------------------------------|

| Flash mem                   | ory (Kbytes)          | 64 Kbytes            | 64 Kbytes 128 Kbytes 192 Kbytes |                      |                                  |                  |                      |                                     |

| Data EEPR                   | OM (Kbytes)           | 3 Kbytes             |                                 |                      | 6 Kb                             | ytes             |                      |                                     |

| RAM (Kbyt                   | es)                   |                      |                                 |                      | 20 Kbytes                        |                  |                      |                                     |

| AES                         |                       |                      |                                 |                      | 1                                |                  |                      |                                     |

|                             | General-<br>purpose   |                      |                                 |                      | 4                                |                  |                      |                                     |

| Timers                      | Basic                 |                      |                                 |                      | 2                                |                  |                      |                                     |

|                             | LPTIMER               |                      |                                 |                      | 1                                |                  |                      |                                     |

| RTC/SYST                    | CK/IWDG/WWDG          |                      |                                 |                      | 1/1/1/1                          |                  |                      |                                     |

|                             | SPI/I2S               |                      |                                 |                      | 6(4) <sup>(1)</sup> /1           |                  |                      |                                     |

| Commu-                      | I <sup>2</sup> C      |                      |                                 |                      | 3                                |                  |                      |                                     |

| nication                    | USART                 |                      |                                 |                      | 4                                |                  |                      |                                     |

| interfaces                  | LPUART                |                      | 1                               |                      |                                  |                  |                      |                                     |

|                             | USB/(VDD_USB)         |                      |                                 |                      | 1/(1)                            |                  |                      |                                     |

| GPIOs                       |                       | 84                   | 40                              | 84                   | 51                               | 40               | 84                   | 51                                  |

| Clocks:<br>HSE/LSE/H        | SI/MSI/LSI            | 1/1/1/1              |                                 |                      |                                  |                  |                      |                                     |

| 12-bit synd<br>Number of    | hronized ADC channels | 1<br>16              | 1<br>10                         |                      | 1<br>6                           | 1<br>10          |                      | 1<br>6                              |

| 12-bit DAC<br>Number of     | channels              |                      |                                 |                      | 2<br>2                           |                  |                      |                                     |

| LCD<br>COM x SEC            | 3                     | 1<br>4x52 or<br>8x48 | 1<br>4x18                       | 1<br>4x52 or<br>8x48 | 1<br>4x32 or 8x28                | 1<br>4x18        | 1<br>4x52 or<br>8x48 | 1<br>4x32 or<br>8x28 <sup>(2)</sup> |

| Comparato                   | rs                    |                      |                                 |                      | 2                                |                  |                      |                                     |

| Capacitive sensing channels |                       | 24                   | 17                              | 24                   | 24                               | 17               | 24                   | 24                                  |

| Max. CPU frequency          |                       |                      |                                 |                      | 32 MHz                           |                  |                      |                                     |

| Operating                   | voltage               | 1.8 V to 3.6         | V (down to 1.6                  | 55 V at power-o      | lown) with BOF                   | R option 1.65 to | 3.6 V without        | BOR option                          |

| Operating                   | temperatures          |                      |                                 |                      | mperature: –40<br>mperature: –40 |                  |                      |                                     |

| Packages                    |                       | LQFP100<br>UFBGA100  | LQFP48                          | LQFP100<br>UFBGA100  | LQFP64                           | LQFP48           | LQFP100<br>UFBGA100  | LQFP64<br>TFBGA64                   |

<sup>1. 4</sup> SPI interfaces are USARTs operating in SPI master mode.

<sup>2.</sup> On TFBGA64, only 4x31 or 8x27 COMxSEG are available.

STM32L083xx Functional overview

### 3.4 Reset and supply management

### 3.4.1 Power supply schemes

•  $V_{DD}$  = 1.65 to 3.6 V: external power supply for I/Os and the internal regulator. Provided externally through  $V_{DD}$  pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 1.65 to 3.6 V: external analog power supplies for ADC reset blocks, RCs and PLL. V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively.

- V<sub>DD\_USB</sub> = 1.65 to 3.6V: external power supply for USB transceiver, USB\_DM (PA11) and USB\_DP (PA12). To guarantee a correct voltage level for USB communication V<sub>DD\_USB</sub> must be above 3.0V. If USB is not used this pin must be tied to V<sub>DD</sub>.

### 3.4.2 Power supply supervisor

The devices have an integrated ZEROPOWER power-on reset (POR)/power-down reset (PDR) that can be coupled with a brownout reset (BOR) circuitry.

Two versions are available:

- The version with BOR activated at power-on operates between 1.8 V and 3.6 V.

- The other version without BOR operates between 1.65 V and 3.6 V.

After the  $V_{DD}$  threshold is reached (1.65 V or 1.8 V depending on the BOR which is active or not at power-on), the option byte loading process starts, either to confirm or modify default thresholds, or to disable the BOR permanently: in this case, the VDD min value becomes 1.65 V (whatever the version, BOR active or not, at power-on).

When BOR is active at power-on, it ensures proper operation starting from 1.8 V whatever the power ramp-up phase before it reaches 1.8 V. When BOR is not active at power-up, the power ramp-up should guarantee that 1.65 V is reached on  $V_{DD}$  at least 1 ms after it exits the POR area.

Five BOR thresholds are available through option bytes, starting from 1.8 V to 3 V. To reduce the power consumption in Stop mode, it is possible to automatically switch off the internal reference voltage ( $V_{REFINT}$ ) in Stop mode. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for any external reset circuit.

Note:

The start-up time at power-on is typically 3.3 ms when BOR is active at power-up, the start-up time at power-on can be decreased down to 1 ms typically for devices with BOR inactive at power-up.

The devices feature an embedded programmable voltage detector (PVD) that monitors the  $V_{DD/VDDA}$  power supply and compares it to the  $V_{PVD}$  threshold. This PVD offers 7 different levels between 1.85 V and 3.05 V, chosen by software, with a step around 200 mV. An interrupt can be generated when  $V_{DD/VDDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD/VDDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

Functional overview STM32L083xx

### 3.8 Memories

The STM32L083xx devices have the following features:

• 20 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states. With the enhanced bus matrix, operating the RAM does not lead to any performance penalty during accesses to the system bus (AHB and APB buses).

- The non-volatile memory is divided into three arrays:

- 64, 128 or 192 Kbytes of embedded Flash program memory

- 6 Kbytes of data EEPROM

- Information block containing 32 user and factory options bytes plus Kbytes of system memory

Flash program and data EEPROM are divided into two banks. This allows writing in one bank while running code or reading data from the other bank.

The user options bytes are used to write-protect or read-out protect the memory (with 4 Kbyte granularity) and/or readout-protect the whole memory with the following options:

- Level 0: no protection

- Level 1: memory readout protected.

- The Flash memory cannot be read from or written to if either debug features are connected or boot in RAM is selected

- Level 2: chip readout protected, debug features (Cortex-M0+ serial wire) and boot in RAM selection disabled (debugline fuse)

The firewall protects parts of code/data from access by the rest of the code that is executed outside of the protected area. The granularity of the protected code segment or the non-volatile data segment is 256 bytes (Flash memory or EEPROM) against 64 bytes for the volatile data segment (RAM).

The whole non-volatile memory embeds the error correction code (ECC) feature.

### 3.9 Boot modes

At startup, BOOT0 pin and nBOOT1 option bit are used to select one of three boot options:

- Boot from Flash memory

- Boot from System memory

- Boot from embedded RAM

The boot loader is located in System memory. It is used to reprogram the Flash memory by using USB (PA11, PA12), USART1(PA9, PA10) or USART2(PA2, PA3). See STM32<sup>™</sup> microcontroller system memory boot mode AN2606 for details.

26/139 DocID027070 Rev 3

Functional overview STM32L083xx

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all scanned channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

The events generated by the general-purpose timers (TIMx) can be internally connected to the ADC start triggers, to allow the application to synchronize A/D conversions and timers.

### 3.13 Temperature sensor

The temperature sensor ( $T_{SENSE}$ ) generates a voltage  $V_{SENSE}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN18 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode.

| Calibration value name | Description                                                              | Memory address            |

|------------------------|--------------------------------------------------------------------------|---------------------------|

| TSENSE_CAL1            | TS ADC raw data acquired at temperature of 30 °C, V <sub>DDA</sub> = 3 V | 0x1FF8 007A - 0x1FF8 007B |

| TSENSE_CAL2            | TS ADC raw data acquired at temperature of 130 °C V <sub>DDA</sub> = 3 V | 0x1FF8 007E - 0x1FF8 007F |

Table 7. Temperature sensor calibration values

## 3.13.1 Internal voltage reference (V<sub>REFINT</sub>)

28/139

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC and Comparators.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. It enables accurate monitoring of the  $V_{DD}$  value (when no external voltage,  $V_{REF+}$ , is available for ADC). The precise voltage of  $V_{REFINT}$  is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode.

| Table 8. Internal voltage | reference measured values |

|---------------------------|---------------------------|

|---------------------------|---------------------------|

| Calibration value name | Description                                                            | Memory address            |

|------------------------|------------------------------------------------------------------------|---------------------------|

| VREFINT_CAL            | Raw data acquired at<br>temperature of 25 °C<br>V <sub>DDA</sub> = 3 V | 0x1FF8 0078 - 0x1FF8 0079 |

STM32L083xx Functional overview

### 3.18.6 Window watchdog (WWDG)

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

### 3.19 Communication interfaces

### 3.19.1 I<sup>2</sup>C bus

Up to three I<sup>2</sup>C interfaces (I2C1 and I2C3) can operate in multimaster or slave modes.

Each I<sup>2</sup>C interface can support Standard mode (Sm, up to 100 kbit/s), Fast mode (Fm, up to 400 kbit/s) and Fast Mode Plus (Fm+, up to 1 Mbit/s) with 20 mA output drive on some I/Os.

7-bit and 10-bit addressing modes, multiple 7-bit slave addresses (2 addresses, 1 with configurable mask) are also supported as well as programmable analog and digital noise filters.

|                                  | Analog filter                                         | Digital filter                                                                     |

|----------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------|

| Pulse width of suppressed spikes | ≥ 50 ns                                               | Programmable length from 1 to 15 I2C peripheral clocks                             |

| Benefits                         | Available in Stop mode                                | Extra filtering capability vs. standard requirements.     Stable length            |

| Drawbacks                        | Variations depending on temperature, voltage, process | Wakeup from Stop on address match is not available when digital filter is enabled. |

Table 11. Comparison of I2C analog and digital filters

In addition, I2C1 and I2C3 provide hardware support for SMBus 2.0 and PMBus 1.1: ARP capability, Host notify protocol, hardware CRC (PEC) generation/verification, timeouts verifications and ALERT protocol management. I2C1/I2C3 also have a clock domain independent from the CPU clock, allowing the I2C1/I2C3 to wake up the MCU from Stop mode on address match.

Each I2C interface can be served by the DMA controller.

Refer to Table 12 for an overview of I2C interface features.

Table 12. STM32L083xx I<sup>2</sup>C implementation

| I2C features <sup>(1)</sup>      | I2C1 | I2C2 | I2C3 |

|----------------------------------|------|------|------|

| 7-bit addressing mode            | Х    | Х    | Х    |

| 10-bit addressing mode           | Х    | Х    | Х    |

| Standard mode (up to 100 kbit/s) | Х    | Х    | Х    |

| Fast mode (up to 400 kbit/s)     | Х    | Х    | Х    |

STM32L083xx Pin descriptions

## 4 Pin descriptions

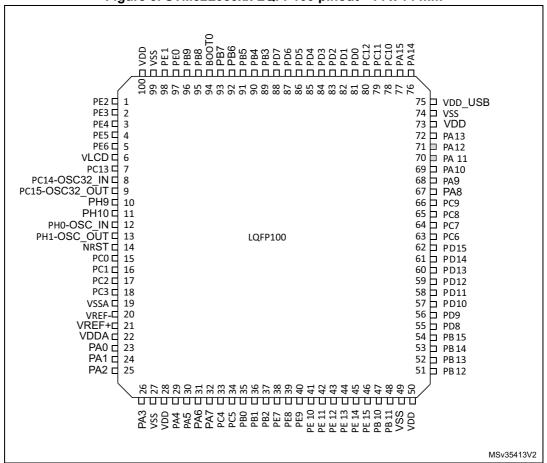

Figure 3. STM32L083xx LQFP100 pinout - 14 x 14 mm

- 1. The above figure shows the package top view.

- 2. I/O pin supplied by VDD\_USB.

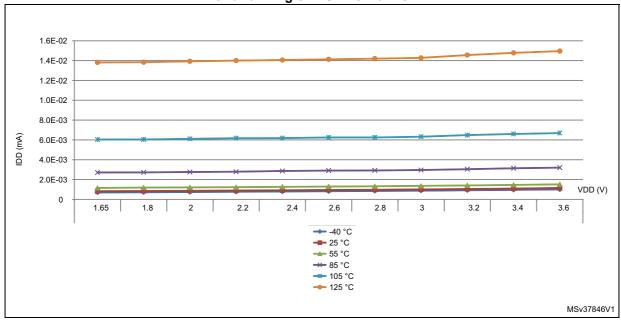

Table 37. Typical and maximum current consumptions in Stop mode

| Symbol                 | Parameter                   | Conditions                                 | Тур   | Max <sup>(1)</sup> | Unit |

|------------------------|-----------------------------|--------------------------------------------|-------|--------------------|------|

| I <sub>DD</sub> (Stop) | Supply current in Stop mode | $T_A = -40 \text{ to } 25^{\circ}\text{C}$ | 0,43  | 1,00               |      |

|                        |                             | T <sub>A</sub> = 55°C                      | 0,735 | 2,50               |      |

|                        |                             | T <sub>A</sub> = 85°C                      | 2,25  | 4,90               | μΑ   |

|                        |                             | T <sub>A</sub> = 105°C                     | 5,3   | 13,00              |      |

|                        |                             | T <sub>A</sub> = 125°C                     | 12,5  | 28,00              |      |

<sup>1.</sup> Guaranteed by characterization results at 125 °C, unless otherwise specified.

Figure 17.  $I_{DD}$  vs  $V_{DD}$ , at  $T_A$ = 25/55/ 85/105/125 °C, Stop mode with RTC enabled and running on LSE Low drive

### High-speed internal 48 MHz (HSI48) RC oscillator

Table 48. HSI48 oscillator characteristics<sup>(1)</sup>

| Symbol                  | Parameter                                                                    | Conditions             | Min                 | Тур  | Max                | Unit |

|-------------------------|------------------------------------------------------------------------------|------------------------|---------------------|------|--------------------|------|

| f <sub>HSI48</sub>      | Frequency                                                                    |                        | -                   | 48   | -                  | MHz  |

| TRIM                    | HSI48 user-trimming step                                                     |                        | 0.09 <sup>(2)</sup> | 0.14 | 0.2 <sup>(2)</sup> | %    |

| DuCy <sub>(HSI48)</sub> | Duty cycle                                                                   |                        | 45 <sup>(2)</sup>   | -    | 55 <sup>(2)</sup>  | %    |

| ACC <sub>HSI48</sub>    | Accuracy of the HSI48 oscillator (factory calibrated before CRS calibration) | T <sub>A</sub> = 25 °C | -4 <sup>(3)</sup>   | -    | 4 <sup>(3)</sup>   | %    |

| t <sub>su(HSI48)</sub>  | HSI48 oscillator startup time                                                |                        | -                   | -    | 6 <sup>(2)</sup>   | μs   |

| I <sub>DDA(HSI48)</sub> | HSI48 oscillator power consumption                                           |                        | -                   | 330  | 380 <sup>(2)</sup> | μΑ   |

- 1.  $V_{DDA}$  = 3.3 V,  $T_{A}$  = -40 to 125 °C unless otherwise specified.

- 2. Guaranteed by design.

- 3. Guaranteed by characterization results.

### Low-speed internal (LSI) RC oscillator

Table 49. LSI oscillator characteristics

| Symbol                              | Parameter                                                           | Min | Тур | Max | Unit |

|-------------------------------------|---------------------------------------------------------------------|-----|-----|-----|------|

| f <sub>LSI</sub> <sup>(1)</sup>     | LSI frequency                                                       | 26  | 38  | 56  | kHz  |

| D <sub>LSI</sub> <sup>(2)</sup>     | LSI oscillator frequency drift $0^{\circ}C \le T_A \le 85^{\circ}C$ | -10 | -   | 4   | %    |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time                                         | -   | -   | 200 | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption                                    | -   | 400 | 510 | nA   |

- 1. Guaranteed by test in production.

- 2. This is a deviation for an individual part, once the initial frequency has been measured.

- 3. Guaranteed by design.

### Multi-speed internal (MSI) RC oscillator

Table 50. MSI oscillator characteristics

| Symbol           | Parameter                                                                       | Condition   | Тур  | Max | Unit |

|------------------|---------------------------------------------------------------------------------|-------------|------|-----|------|

|                  | Frequency after factory calibration, done at $V_{DD}$ = 3.3 V and $T_A$ = 25 °C | MSI range 0 | 65.5 | -   |      |

|                  |                                                                                 | MSI range 1 | 131  | -   | kHz  |

|                  |                                                                                 | MSI range 2 | 262  | -   |      |

| f <sub>MSI</sub> |                                                                                 | MSI range 3 | 524  | -   |      |

|                  |                                                                                 | MSI range 4 | 1.05 | -   |      |

|                  |                                                                                 | MSI range 5 | 2.1  | -   | MHz  |

|                  |                                                                                 | MSI range 6 | 4.2  | -   |      |

Electrical characteristics STM32L083xx

### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

Max vs. Monitored frequency **Parameter Conditions** Unit **Symbol** frequency band range at 32 MHz 0.1 to 30 MHz -7  $V_{DD} = 3.6 \text{ V},$ 30 to 130 MHz 14  $dB\mu V$  $T_A = 25$  °C, Peak level S<sub>EMI</sub> LQFP100 package 130 MHz to 1 GHz 9 compliant with IEC 61967-2 EMI Level 2

Table 56. EMI characteristics

**Electrical characteristics** STM32L083xx

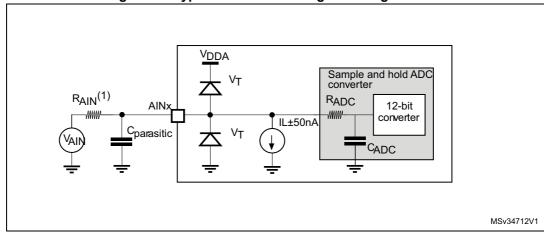

Figure 29. Typical connection diagram using the ADC

- 1. Refer to Table 64: ADC characteristics for the values of RAIN, RADC and CADC.

- $C_{parasitic}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high  $C_{parasitic}$  value will downgrade conversion accuracy. To remedy this,  $f_{ADC}$  should be reduced.

### General PCB design guidelines

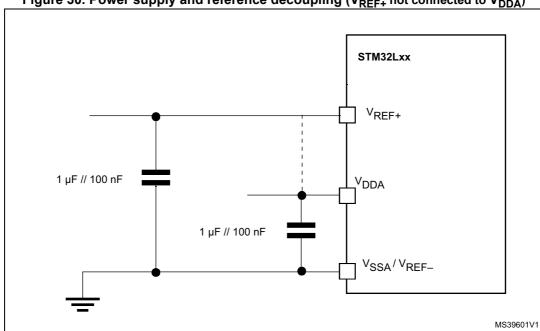

Power supply decoupling should be performed as shown in Figure 30 or Figure 31, depending on whether  $V_{\text{REF+}}$  is connected to  $V_{\text{DDA}}$  or not. The 10 nF capacitors should be ceramic (good quality). They should be placed as close as possible to the chip.

Figure 30. Power supply and reference decoupling ( $V_{REF+}$  not connected to  $V_{DDA}$ )

Electrical characteristics STM32L083xx

## 6.3.16 DAC electrical specifications

Data guaranteed by design, not tested in production, unless otherwise specified.

Table 67. DAC characteristics

| Symbol                              | Parameter                                       | Conditions                                                                                                             | Min | Тур       | Max                         | Unit |  |

|-------------------------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----|-----------|-----------------------------|------|--|

| $V_{DDA}$                           | Analog supply voltage                           | -                                                                                                                      | 1.8 | -         | 3.6                         | V    |  |

| V <sub>REF+</sub>                   | Reference supply voltage                        | V <sub>REF+</sub> must always be below V <sub>DDA</sub>                                                                | 1.8 | -         | 3.6                         | V    |  |

| V <sub>REF-</sub>                   | Lower reference voltage                         | -                                                                                                                      |     | $V_{SSA}$ | •                           | V    |  |

| (1)                                 | Current consumption on V <sub>REF+</sub> supply | No load, middle code (0x800)                                                                                           | -   | 130       | 220                         | μΑ   |  |

| I <sub>DDVREF+</sub> <sup>(1)</sup> | V <sub>REF+</sub> = 3.3 V                       | No load, worst code (0x000)                                                                                            | -   | 220       | 350                         |      |  |

| (2)                                 | Current consumption on V <sub>DDA</sub>         | No load, middle code (0x800)                                                                                           | -   | 210       | 320                         |      |  |

| I <sub>DDA</sub> <sup>(2)</sup>     | supply,<br>V <sub>DDA</sub> = 3.3 V             | No load, worst code (0xF1C)                                                                                            | -   | 320       | 520                         | μΑ   |  |

| R <sub>L</sub> <sup>(3)</sup>       | Resistive load                                  | DAC output buffer on                                                                                                   | 5   | -         | -                           | kΩ   |  |

| C <sub>L</sub> <sup>(3)</sup>       | Capacitive load                                 | DAC output buller on                                                                                                   | -   | -         | 50                          | pF   |  |

| R <sub>O</sub>                      | Output impedance                                | DAC output buffer off                                                                                                  | 12  | 16        | 20                          | kΩ   |  |

| V <sub>DAC_OUT</sub>                |                                                 | DAC output buffer ON                                                                                                   | 0.2 | -         | V <sub>DDA</sub> – 0.2      | V    |  |

|                                     | Voltage on DAC_OUT output                       | DAC output buffer OFF                                                                                                  | 0.5 | -         | V <sub>REF+</sub> –<br>1LSB | mV   |  |

| DNL <sup>(2)</sup>                  | Differential non linearity <sup>(4)</sup>       | $C_L \leq 50$ pF, $R_L \geq 5$ k $\Omega$ DAC output buffer on                                                         | -   | 1.5       | 3                           |      |  |

|                                     |                                                 | No $R_{LOAD}$ , $C_{L} \le 50 pF$<br>DAC output buffer off                                                             | -   | 1.5       | 3                           |      |  |

| INL <sup>(2)</sup>                  | Integral man line seit (5)                      | $C_L \le 50$ pF, $R_L \ge 5$ k $\Omega$ DAC output buffer on                                                           | -   | 2         | 4                           |      |  |

|                                     | Integral non linearity <sup>(5)</sup>           | No $R_{LOAD}$ , $C_{L} \le 50 pF$<br>DAC output buffer off                                                             | -   | 2         | 4                           | LSB  |  |

| Offset <sup>(2)</sup>               | Offset error at code 0x800 (6)                  | $\begin{array}{l} C_L \leq \ 50 \ \text{pF}, \ R_L \geq 5 \ \text{k}\Omega \\ \text{DAC output buffer on} \end{array}$ | -   | ±10       | ±25                         |      |  |

|                                     | Oliset entor at code 0x800 (6)                  | No $R_{LOAD}$ , $C_{L} \le 50 pF$<br>DAC output buffer off                                                             | -   | ±5        | ±8                          |      |  |

| Offset1 <sup>(2)</sup>              | Offset error at code 0x001 <sup>(7)</sup>       | No $R_{LOAD}$ , $C_{L} \le 50 pF$<br>DAC output buffer off                                                             | -   | ±1.5      | ±5                          |      |  |

### **SPI** characteristics

Unless otherwise specified, the parameters given in the following tables are derived from tests performed under ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 26*.

Refer to Section 6.3.12: I/O current injection characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

Table 75. SPI characteristics in voltage Range 1 (1)

| Symbol                                    | Parameter                         | Conditions                                                  | Min     | Тур   | Max               | Unit |

|-------------------------------------------|-----------------------------------|-------------------------------------------------------------|---------|-------|-------------------|------|

|                                           |                                   | Master mode                                                 |         | -     | 16                |      |

|                                           |                                   | Slave mode receiver                                         | -       |       | 16                |      |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub> | SPI clock frequency               | Slave mode<br>Transmitter<br>1.71 <v<sub>DD&lt;3.6V</v<sub> | -       | ı     | 12 <sup>(2)</sup> | MHz  |

|                                           |                                   | Slave mode<br>Transmitter<br>2.7 <v<sub>DD&lt;3.6V</v<sub>  | -       | ı     | 16 <sup>(2)</sup> |      |

| Duty <sub>(SCK)</sub>                     | Duty cycle of SPI clock frequency | Slave mode                                                  | 30      | 50    | 70                | %    |

| t <sub>su(NSS)</sub>                      | NSS setup time                    | Slave mode, SPI<br>presc = 2                                |         |       | -                 |      |

| t <sub>h(NSS)</sub>                       | NSS hold time                     | Slave mode, SPI<br>presc = 2                                | 2*Tpclk | -     | -                 |      |

| t <sub>w(SCKH)</sub>                      | SCK high and low time             | Master mode                                                 | Tpclk-2 | Tpclk | Tpclk+            |      |

| t <sub>su(MI)</sub>                       | Data input setup time             | Master mode                                                 | 0       | -     | -                 |      |

| t <sub>su(SI)</sub>                       | Data input setup time             | Slave mode                                                  | 3       | -     | -                 |      |

| t <sub>h(MI)</sub>                        | Data input hold time              | Master mode                                                 | 7       | -     | -                 |      |

| t <sub>h(SI)</sub>                        | Data input noid time              | Slave mode                                                  | 3.5     | ı     | -                 | ns   |

| t <sub>a(SO</sub>                         | Data output access time           | Slave mode                                                  | 15      | ı     | 36                |      |

| t <sub>dis(SO)</sub>                      | Data output disable time          | Slave mode                                                  | 10      | -     | 30                |      |

| t <sub>v(SO)</sub>                        |                                   | Slave mode<br>1.65 V <v<sub>DD&lt;3.6 V</v<sub>             | -       | 18    | 41                |      |

|                                           | Data output valid time            | Slave mode<br>2.7 V <v<sub>DD&lt;3.6 V</v<sub>              | -       | 18    | 25                |      |

| t <sub>v(MO)</sub>                        |                                   | Master mode                                                 | -       | 4     | 7                 |      |

| t <sub>h(SO)</sub>                        | Data output hold time             | Slave mode                                                  | 10      | -     | -                 |      |

| t <sub>h(MO)</sub>                        | Data output noid time             | Master mode                                                 | 0       | -     | -                 |      |

<sup>1.</sup> Guaranteed by characterization results.

110/139 DocID027070 Rev 3

<sup>2.</sup> The maximum SPI clock frequency in slave transmitter mode is determined by the sum of  $t_{v(SO)}$  and  $t_{su(MI)}$  which has to fit into SCK low or high phase preceding the SCK sampling edge. This value can be achieved when the SPI communicates with a master having  $t_{su(MI)} = 0$  while Duty<sub>(SCK)</sub> = 50%.

Electrical characteristics STM32L083xx

Table 82. LCD controller characteristics (continued)

| Symbol                           | Parameter                                                        | Min  | Тур                  | Max              | Unit |

|----------------------------------|------------------------------------------------------------------|------|----------------------|------------------|------|

| I <sub>LCD</sub> <sup>(1)</sup>  | Supply current at V <sub>DD</sub> = 2.2 V                        |      | 3.3                  | -                |      |

| 'LCD`                            | Supply current at V <sub>DD</sub> = 3.0 V                        | -    | 3.1                  | -                | μΑ   |

| R <sub>Htot</sub> <sup>(2)</sup> | Low drive resistive network overall value                        | 5.28 | 6.6                  | 7.92             | МΩ   |

| R <sub>L</sub> <sup>(2)</sup>    | High drive resistive network total value                         | 192  | 240                  | 288              | kΩ   |

| V <sub>44</sub>                  | Segment/Common highest level voltage                             | -    | -                    | V <sub>LCD</sub> | V    |

| V <sub>34</sub>                  | Segment/Common 3/4 level voltage                                 | -    | 3/4 V <sub>LCD</sub> | -                |      |

| V <sub>23</sub>                  | Segment/Common 2/3 level voltage                                 | -    | 2/3 V <sub>LCD</sub> | -                |      |

| V <sub>12</sub>                  | Segment/Common 1/2 level voltage                                 | -    | 1/2 V <sub>LCD</sub> | -                | V    |

| V <sub>13</sub>                  | Segment/Common 1/3 level voltage                                 | -    | 1/3 V <sub>LCD</sub> | -                | V    |

| V <sub>14</sub>                  | Segment/Common 1/4 level voltage                                 | -    | 1/4 V <sub>LCD</sub> | -                |      |

| V <sub>0</sub>                   | Segment/Common lowest level voltage                              | 0    | -                    | -                |      |

| ΔVxx <sup>(3)</sup>              | Segment/Common level voltage error T <sub>A</sub> = -40 to 85 °C | -    | -                    | ± 50             | mV   |

LCD enabled with 3 V internal step-up active, 1/8 duty, 1/4 bias, division ratio= 64, all pixels active, no LCD connected.

<sup>2.</sup> Guaranteed by design.

<sup>3.</sup> Guaranteed by characterization results.

Package information STM32L083xx

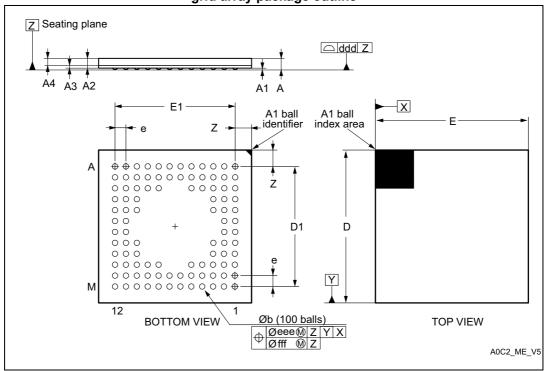

### 7.2 UFBGA100 package information

Figure 42. UFBGA100 - 100-pin, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball grid array package outline

1. Drawing is not to scale.

Table 84. UFBGA100 - 100-pin, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball grid array package mechanical data

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|-------|-------|-----------------------|--------|--------|--|

| Symbol | Min.        | Тур.  | Max.  | Min.                  | Тур.   | Max.   |  |

| Α      | -           | -     | 0.600 | -                     | -      | 0.0236 |  |

| A1     | -           | -     | 0.110 | -                     | -      | 0.0043 |  |

| A2     | -           | 0.450 | -     | -                     | 0.0177 | -      |  |

| A3     | -           | 0.130 | -     | -                     | 0.0051 | 0.0094 |  |

| A4     | -           | 0.320 | -     | -                     | 0.0126 | -      |  |

| b      | 0.240       | 0.290 | 0.340 | 0.0094                | 0.0114 | 0.0134 |  |

| D      | 6.850       | 7.000 | 7.150 | 0.2697                | 0.2756 | 0.2815 |  |

| D1     | -           | 5.500 | -     | -                     | 0.2165 | -      |  |

| Е      | 6.850       | 7.000 | 7.150 | 0.2697                | 0.2756 | 0.2815 |  |

| E1     | -           | 5.500 | -     | -                     | 0.2165 | -      |  |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |  |

| Z      | -           | 0.750 | -     | -                     | 0.0295 | -      |  |

Package information STM32L083xx

Table 86. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package mechanical data (continued)

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|-------|-------|-----------------------|--------|--------|--|

| Symbol | Min         | Тур   | Max   | Min                   | Тур    | Max    |  |

| E3     | -           | 7.500 | -     | -                     | 0.2953 | -      |  |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |  |

| K      | 0°          | 3.5°  | 7°    | 0°                    | 3.5°   | 7°     |  |

| L      | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |  |

| L1     | -           | 1.000 | -     | -                     | 0.0394 | -      |  |

| ccc    | -           | -     | 0.080 | -                     | -      | 0.0031 |  |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

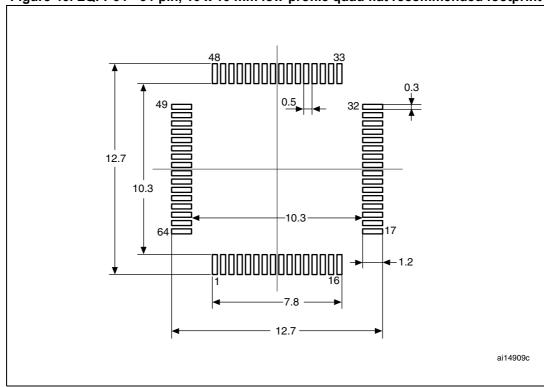

Figure 46. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat recommended footprint

1. Dimensions are expressed in millimeters.

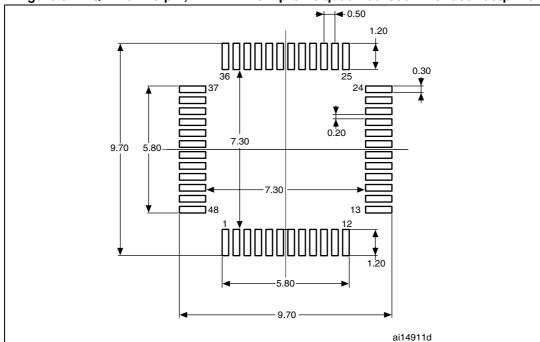

Figure 52. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat recommended footprint

1. Dimensions are expressed in millimeters.

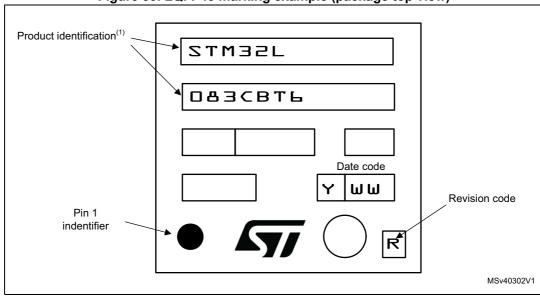

### **Device marking for LQFP48**

The following figure gives an example of topside marking versus pin 1 position identifier location.

Figure 53. LQFP48 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

Revision history STM32L083xx

Table 92. Document revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22-Mar-2016 | 3        | Updated number of SPIs on cover page and in <i>Table 2: Ultra-low-power STM32L083xxx device features and peripheral counts.</i> Changed minimum comparator supply voltage to 1.65 V on cover page. Added minimum DAC supply voltage on cover page. Added number of fast and standard channels in <i>Section 3.12: Analog-to-digital converter (ADC).</i> Updated <i>Section 3.19.2: Universal synchronous/asynchronous receiver transmitter (USART)</i> and <i>Section 3.19.4: Serial peripheral interface (SPI)/Inter-integrated sound (I2S)</i> to mention the fact that USARTs with synchronous mode feature can be used as SPI master interfaces. Added baudrate allowing to wake up the MCU from Stop mode in <i>Section 3.19.2: Universal synchronous/asynchronous receiver transmitter (USART)</i> and <i>Section 3.19.3: Low-power universal asynchronous receiver transmitter (USART)</i> and <i>Section 3.19.3: Low-power universal asynchronous receiver transmitter (LPUART)</i> . Section 6.3.15: 12-bit ADC characteristics:  — Table 64: ADC characteristics:  Distinction made between V <sub>DDA</sub> for fast and standard channels; added note 4. related to R <sub>ADC</sub> .  Updated f <sub>TRIG</sub> .  Updated equation 1 description.  — Updated Table 65: RAIN max for fADC = 16 MHz for f <sub>ADC</sub> = 16 MHz and distinction made between fast and standard channels.  Updated R <sub>O</sub> and added Note 2. in <i>Table 67: DAC characteristics</i> . Added <i>Table 74: USART/LPUART characteristics</i> . |