Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 32MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT     |

| Number of I/O              | 84                                                                    |

| Program Memory Size        | 192KB (192K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 3K x 8                                                                |

| RAM Size                   | 20K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                           |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 100-UFBGA                                                             |

| Supplier Device Package    | 100-UFBGA (7x7)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l083vzi6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Contents STM32L083xx

## **Contents**

| 1 | Intro | duction                                                     | . 9 |

|---|-------|-------------------------------------------------------------|-----|

| 2 | Desc  | cription                                                    | 10  |

|   | 2.1   | Device overview                                             | .11 |

|   | 2.2   | Ultra-low-power device continuum                            | 13  |

| 3 | Fund  | ctional overview                                            | 14  |

|   | 3.1   | Low-power modes                                             | 14  |

|   | 3.2   | Interconnect matrix                                         | 19  |

|   | 3.3   | ARM® Cortex®-M0+ core with MPU                              | 20  |

|   | 3.4   | Reset and supply management                                 | 21  |

|   |       | 3.4.1 Power supply schemes                                  | 21  |

|   |       | 3.4.2 Power supply supervisor                               | 21  |

|   |       | 3.4.3 Voltage regulator                                     | 22  |

|   | 3.5   | Clock management                                            | 22  |

|   | 3.6   | Low-power real-time clock and backup registers              | 25  |

|   | 3.7   | General-purpose inputs/outputs (GPIOs)                      | 25  |

|   | 3.8   | Memories                                                    | 26  |

|   | 3.9   | Boot modes                                                  | 26  |

|   | 3.10  | Direct memory access (DMA)                                  | 27  |

|   | 3.11  | Liquid crystal display (LCD)                                | 27  |

|   | 3.12  | Analog-to-digital converter (ADC)                           | 27  |

|   | 3.13  | Temperature sensor                                          | 28  |

|   |       | 3.13.1 Internal voltage reference (V <sub>REFINT</sub> )    | 28  |

|   |       | 3.13.2 V <sub>LCD</sub> voltage monitoring                  | 29  |

|   | 3.14  | Digital-to-analog converter (DAC)                           | 29  |

|   | 3.15  | Ultra-low-power comparators and reference voltage           | 29  |

|   | 3.16  | Touch sensing controller (TSC)                              | 30  |

|   | 3.17  | AES                                                         | 31  |

|   | 3.18  | Timers and watchdogs                                        | 31  |

|   |       | 3.18.1 General-purpose timers (TIM2, TIM3, TIM21 and TIM22) | 31  |

|   |       | 3.18.2 Low-power Timer (LPTIM)                              | 32  |

STM32L083xx Contents

|          |       | 3.18.3    | Basic timer (TIM6, TIM7)                                       | 32    |

|----------|-------|-----------|----------------------------------------------------------------|-------|

|          |       | 3.18.4    | SysTick timer                                                  | 32    |

|          |       | 3.18.5    | Independent watchdog (IWDG)                                    | 32    |

|          |       | 3.18.6    | Window watchdog (WWDG)                                         | 33    |

|          | 3.19  | Comm      | unication interfaces                                           | 33    |

|          |       | 3.19.1    | I2C bus                                                        | 33    |

|          |       | 3.19.2    | Universal synchronous/asynchronous receiver transmitter (USAF  | RT)34 |

|          |       | 3.19.3    | Low-power universal asynchronous receiver transmitter (LPUAR   | T) 35 |

|          |       | 3.19.4    | Serial peripheral interface (SPI)/Inter-integrated sound (I2S) | 35    |

|          |       | 3.19.5    | Universal serial bus (USB)                                     | 36    |

|          | 3.20  | Clock r   | recovery system (CRS)                                          | 36    |

|          | 3.21  | Cyclic    | redundancy check (CRC) calculation unit                        | 36    |

|          | 3.22  | Serial    | wire debug port (SW-DP)                                        | 36    |

| 4        | Pin d | lascrint  | ions                                                           | 37    |

| •        | 0     | icocript  |                                                                | 07    |

| 5        | Mem   | ory ma    | pping                                                          | 56    |

| 6        | Elect | trical ch | naracteristics                                                 | 57    |

|          | 6.1   | Param     | eter conditions                                                | 57    |

|          |       | 6.1.1     | Minimum and maximum values                                     | 57    |

|          |       | 6.1.2     | Typical values                                                 | 57    |

|          |       | 6.1.3     | Typical curves                                                 | 57    |

|          |       | 6.1.4     | Loading capacitor                                              | 57    |

|          |       | 6.1.5     | Pin input voltage                                              | 57    |

|          |       | 6.1.6     | Power supply scheme                                            | 58    |

|          |       | 6.1.7     | Optional LCD power supply scheme                               | 59    |

|          |       | 6.1.8     | Current consumption measurement                                | 59    |

|          | 6.2   | Absolu    | te maximum ratings                                             | 60    |

|          | 6.3   | Operat    | ing conditions                                                 | 62    |

|          |       | 6.3.1     | General operating conditions                                   | 62    |

|          |       | 6.3.2     | Embedded reset and power control block characteristics         | 64    |

|          |       | 6.3.3     | Embedded internal reference voltage                            | 65    |

|          |       | 6.3.4     | Supply current characteristics                                 | 66    |

|          |       | 6.3.5     | Wakeup time from low-power mode                                | 78    |

|          |       | 6.3.6     | External clock source characteristics                          | 80    |

|          |       | 6.3.7     | Internal clock source characteristics                          | 84    |

| <b>\</b> |       |           | DocID027070 Rev 3                                              | 3/139 |

|   |       | 6.3.8    | DLL pharacteristics 97                 |

|---|-------|----------|----------------------------------------|

|   |       |          | PLL characteristics                    |

|   |       | 6.3.9    | Memory characteristics                 |

|   |       | 6.3.10   | EMC characteristics                    |

|   |       | 6.3.11   | Electrical sensitivity characteristics |

|   |       | 6.3.12   | I/O current injection characteristics  |

|   |       | 6.3.13   | I/O port characteristics               |

|   |       | 6.3.14   | NRST pin characteristics               |

|   |       | 6.3.15   | 12-bit ADC characteristics             |

|   |       | 6.3.16   | DAC electrical specifications          |

|   |       | 6.3.17   | Temperature sensor characteristics     |

|   |       | 6.3.18   | Comparators                            |

|   |       | 6.3.19   | Timer characteristics                  |

|   |       | 6.3.20   | Communications interfaces              |

|   |       | 6.3.21   | LCD controller                         |

| 7 | Pack  | age info | ormation                               |

|   | 7.1   | LQFP1    | 00 package information                 |

|   | 7.2   | UFBGA    | A100 package information               |

|   | 7.3   | LQFP6    | 4 package information                  |

|   | 7.4   | TFBGA    | A64 package information                |

|   | 7.5   | LQFP4    | 8 package information                  |

|   | 7.6   | Therma   | al characteristics                     |

|   |       | 7.6.1    | Reference document                     |

| 8 | Part  | number   | ring                                   |

| • | Da:-! | alam b!- | 407                                    |

| 9 | Kevi  | sion nis | tory                                   |

STM32L083xx List of figures

# List of figures

| Figure 1.  | STM32L083xx block diagram                                                                    | 12  |

|------------|----------------------------------------------------------------------------------------------|-----|

| Figure 2.  | Clock tree                                                                                   | 24  |

| Figure 3.  | STM32L083xx LQFP100 pinout - 14 x 14 mm                                                      | 37  |

| Figure 4.  | STM32L083xx UFBGA100 ballout - 7x 7 mm                                                       | 38  |

| Figure 5.  | STM32L083xx LQFP64 pinout - 10 x 10 mm                                                       | 39  |

| Figure 6.  | STM32L083xx TFBGA64 ballout - 5x 5 mm                                                        | 40  |

| Figure 7.  | STM32L083xx LQFP48 pinout - 7 x 7 mm                                                         | 41  |

| Figure 8.  | Memory map                                                                                   | 56  |

| Figure 9.  | Pin loading conditions                                                                       | 57  |

| Figure 10. | Pin input voltage                                                                            | 57  |

| Figure 11. | Power supply scheme                                                                          | 58  |

| Figure 12. | Optional LCD power supply scheme                                                             |     |

| Figure 13. | Current consumption measurement scheme                                                       |     |

| Figure 14. | IDD vs VDD, at TA= 25/55/85/105 °C, Run mode, code running from                              |     |

| Ü          | Flash memory, Range 2, HSE, 1WS                                                              | 68  |

| Figure 15. | IDD vs VDD, at TA= 25/55/85/105 °C, Run mode, code running from                              |     |

| Ü          | Flash memory, Range 2, HSI16, 1WS                                                            | 68  |

| Figure 16. | IDD vs VDD, at TA= 25 °C, Low-power run mode, code running                                   |     |

| Ü          | from RAM, Range 3, MSI (Range 0) at 64 KHz, 0 WS                                             | 72  |

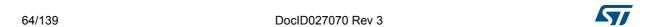

| Figure 17. | IDD vs VDD, at TA= 25/55/ 85/105/125 °C, Stop mode with RTC enabled                          |     |

| J          | and running on LSE Low drive                                                                 | 73  |

| Figure 18. | IDD vs VDD, at TA= 25/55/85/105/125 °C, Stop mode with RTC disabled,                         |     |

| Ü          | all clocks off                                                                               | 74  |

| Figure 19. | High-speed external clock source AC timing diagram                                           | 80  |

| Figure 20. | Low-speed external clock source AC timing diagram                                            |     |

| Figure 21. | HSE oscillator circuit diagram                                                               |     |

| Figure 22. | Typical application with a 32.768 kHz crystal                                                |     |

| Figure 23. | HSI16 minimum and maximum value versus temperature                                           |     |

| Figure 24. | VIH/VIL versus VDD (CMOS I/Os)                                                               |     |

| Figure 25. | VIH/VIL versus VDD (TTL I/Os)                                                                |     |

| Figure 26. | I/O AC characteristics definition                                                            |     |

| Figure 27. | Recommended NRST pin protection                                                              | 98  |

| Figure 28. | ADC accuracy characteristics                                                                 |     |

| Figure 29. | Typical connection diagram using the ADC                                                     |     |

| Figure 30. | Power supply and reference decoupling (V <sub>REF+</sub> not connected to V <sub>DDA</sub> ) |     |

| Figure 31. | Power supply and reference decoupling (V <sub>REF+</sub> connected to V <sub>DDA</sub> )     |     |

| Figure 32. | 12-bit buffered/non-buffered DAC                                                             |     |

| Figure 33. | SPI timing diagram - slave mode and CPHA = 0                                                 | 112 |

| Figure 34. | SPI timing diagram - slave mode and CPHA = 1 <sup>(1)</sup>                                  | 113 |

| Figure 35. | SPI timing diagram - master mode <sup>(1)</sup>                                              | 113 |

| Figure 36. | I <sup>2</sup> S slave timing diagram (Philips protocol) <sup>(1)</sup>                      | 115 |

| Figure 37. | I <sup>2</sup> S master timing diagram (Philips protocol) <sup>(1)</sup>                     | 115 |

| Figure 38. | USB timings: definition of data signal rise and fall time                                    | 117 |

| Figure 39. | LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat package outline                          |     |

| Figure 40. | LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat                                          |     |

| -          | recommended footprint                                                                        | 121 |

| Figure 41. | LQFP100 marking example (package top view)                                                   | 121 |

| Figure 42. | UFBGA100 - 100-pin, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball                           |     |

|            |                                                                                              |     |

STM32L083xx Description

## 2.2 Ultra-low-power device continuum

The ultra-low-power family offers a large choice of core and features, from 8-bit proprietary core up to ARM® Cortex®-M4, including ARM® Cortex®-M3 and ARM® Cortex®-M0+. The STM32Lx series are the best choice to answer your needs in terms of ultra-low-power features. The STM32 ultra-low-power series are the best solution for applications such as gaz/water meter, keyboard/mouse or fitness and healthcare application. Several built-in features like LCD drivers, dual-bank memory, low-power run mode, operational amplifiers, 128-bit AES, DAC, crystal-less USB and many other definitely help you building a highly cost optimized application by reducing BOM cost. STMicroelectronics, as a reliable and long-term manufacturer, ensures as much as possible pin-to-pin compatibility between all STM8Lx and STM32Lx on one hand, and between all STM32Lx and STM32Fx on the other hand. Thanks to this unprecedented scalability, your legacy application can be upgraded to respond to the latest market feature and efficiency requirements.

Functional overview STM32L083xx

Table 3. Functionalities depending on the operating power supply range

|                                                | Functionalities depending on the operating power supply range |                                     |                            |                           |  |

|------------------------------------------------|---------------------------------------------------------------|-------------------------------------|----------------------------|---------------------------|--|

| Operating power supply range                   | DAC and ADC operation                                         | Dynamic<br>voltage scaling<br>range | I/O operation              | USB                       |  |

| V <sub>DD</sub> = 1.65 to 1.71 V               | ADC only,<br>conversion time<br>up to 570 ksps                | Range 2 or range 3                  | Degraded speed performance | Not functional            |  |

| V <sub>DD</sub> = 1.71 to 1.8 V <sup>(1)</sup> | ADC only,<br>conversion time<br>up to 1.14 Msps               | Range 1, range 2<br>or range 3      | Degraded speed performance | Functional <sup>(2)</sup> |  |

| $V_{DD}$ = 1.8 to 2.0 $V^{(1)}$                | Conversion time up to 1.14 Msps                               | Range1, range 2<br>or range 3       | Degraded speed performance | Functional <sup>(2)</sup> |  |

| V <sub>DD</sub> = 2.0 to 2.4 V                 | Conversion time<br>up to<br>1.14 Msps                         | Range 1, range 2<br>or range 3      | Full speed operation       | Functional <sup>(2)</sup> |  |

| V <sub>DD</sub> = 2.4 to 3.6 V                 | Conversion time<br>up to<br>1.14 Msps                         | Range 1, range 2<br>or range 3      | Full speed operation       | Functional <sup>(2)</sup> |  |

<sup>1.</sup> CPU frequency changes from initial to final must respect "fcpu initial <4\*fcpu final". It must also respect 5  $\mu s$  delay between two changes. For example to switch from 4.2 MHz to 32 MHz, you can switch from 4.2 MHz to 16 MHz, wait 5  $\mu s$ , then switch from 16 MHz to 32 MHz.

Table 4. CPU frequency range depending on dynamic voltage scaling

| CPU frequency range                              | Dynamic voltage scaling range |

|--------------------------------------------------|-------------------------------|

| 16 MHz to 32 MHz (1ws)<br>32 kHz to 16 MHz (0ws) | Range 1                       |

| 8 MHz to 16 MHz (1ws)<br>32 kHz to 8 MHz (0ws)   | Range 2                       |

| 32 kHz to 4.2 MHz (0ws)                          | Range 3                       |

<sup>2.</sup> To be USB compliant from the I/O voltage standpoint, the minimum  $\rm V_{\rm DD\_USB}$  is 3.0 V.

Functional overview STM32L083xx

## 3.3 ARM® Cortex®-M0+ core with MPU

The Cortex-M0+ processor is an entry-level 32-bit ARM Cortex processor designed for a broad range of embedded applications. It offers significant benefits to developers, including:

- a simple architecture that is easy to learn and program

- ultra-low power, energy-efficient operation

- excellent code density

- deterministic, high-performance interrupt handling

- upward compatibility with Cortex-M processor family

- platform security robustness, with integrated Memory Protection Unit (MPU).

The Cortex-M0+ processor is built on a highly area and power optimized 32-bit processor core, with a 2-stage pipeline Von Neumann architecture. The processor delivers exceptional energy efficiency through a small but powerful instruction set and extensively optimized design, providing high-end processing hardware including a single-cycle multiplier.

The Cortex-M0+ processor provides the exceptional performance expected of a modern 32-bit architecture, with a higher code density than other 8-bit and 16-bit microcontrollers.

Owing to its embedded ARM core, the STM32L083xx are compatible with all ARM tools and software.

### **Nested vectored interrupt controller (NVIC)**

The ultra-low-power STM32L083xx embed a nested vectored interrupt controller able to handle up to 32 maskable interrupt channels and 4 priority levels.

The Cortex-M0+ processor closely integrates a configurable Nested Vectored Interrupt Controller (NVIC), to deliver industry-leading interrupt performance. The NVIC:

- includes a Non-Maskable Interrupt (NMI)

- provides zero jitter interrupt option

- provides four interrupt priority levels

The tight integration of the processor core and NVIC provides fast execution of Interrupt Service Routines (ISRs), dramatically reducing the interrupt latency. This is achieved through the hardware stacking of registers, and the ability to abandon and restart load-multiple and store-multiple operations. Interrupt handlers do not require any assembler wrapper code, removing any code overhead from the ISRs. Tail-chaining optimization also significantly reduces the overhead when switching from one ISR to another.

To optimize low-power designs, the NVIC integrates with the sleep modes, that include a deep sleep function that enables the entire device to enter rapidly stop or standby mode.

This hardware block provides flexible interrupt management features with minimal interrupt latency.

STM32L083xx Functional overview

### 3.4 Reset and supply management

### 3.4.1 Power supply schemes

•  $V_{DD}$  = 1.65 to 3.6 V: external power supply for I/Os and the internal regulator. Provided externally through  $V_{DD}$  pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 1.65 to 3.6 V: external analog power supplies for ADC reset blocks, RCs and PLL. V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively.

- V<sub>DD\_USB</sub> = 1.65 to 3.6V: external power supply for USB transceiver, USB\_DM (PA11) and USB\_DP (PA12). To guarantee a correct voltage level for USB communication V<sub>DD\_USB</sub> must be above 3.0V. If USB is not used this pin must be tied to V<sub>DD</sub>.

### 3.4.2 Power supply supervisor

The devices have an integrated ZEROPOWER power-on reset (POR)/power-down reset (PDR) that can be coupled with a brownout reset (BOR) circuitry.

Two versions are available:

- The version with BOR activated at power-on operates between 1.8 V and 3.6 V.

- The other version without BOR operates between 1.65 V and 3.6 V.

After the  $V_{DD}$  threshold is reached (1.65 V or 1.8 V depending on the BOR which is active or not at power-on), the option byte loading process starts, either to confirm or modify default thresholds, or to disable the BOR permanently: in this case, the VDD min value becomes 1.65 V (whatever the version, BOR active or not, at power-on).

When BOR is active at power-on, it ensures proper operation starting from 1.8 V whatever the power ramp-up phase before it reaches 1.8 V. When BOR is not active at power-up, the power ramp-up should guarantee that 1.65 V is reached on  $V_{DD}$  at least 1 ms after it exits the POR area.

Five BOR thresholds are available through option bytes, starting from 1.8 V to 3 V. To reduce the power consumption in Stop mode, it is possible to automatically switch off the internal reference voltage ( $V_{REFINT}$ ) in Stop mode. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for any external reset circuit.

Note:

The start-up time at power-on is typically 3.3 ms when BOR is active at power-up, the start-up time at power-on can be decreased down to 1 ms typically for devices with BOR inactive at power-up.

The devices feature an embedded programmable voltage detector (PVD) that monitors the  $V_{DD/VDDA}$  power supply and compares it to the  $V_{PVD}$  threshold. This PVD offers 7 different levels between 1.85 V and 3.05 V, chosen by software, with a step around 200 mV. An interrupt can be generated when  $V_{DD/VDDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD/VDDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

STM32L083xx Functional overview

### 3.19.3 Low-power universal asynchronous receiver transmitter (LPUART)

The devices embed one Low-power UART. The LPUART supports asynchronous serial communication with minimum power consumption. It supports half duplex single wire communication and modem operations (CTS/RTS). It allows multiprocessor communication.

The LPUART has a clock domain independent from the CPU clock. It can wake up the system from Stop mode using baudrates up to 46 Kbaud. The Wakeup events from Stop mode are programmable and can be:

- Start bit detection

- Or any received data frame

- Or a specific programmed data frame

Only a 32.768 kHz clock (LSE) is needed to allow LPUART communication up to 9600 baud. Therefore, even in Stop mode, the LPUART can wait for an incoming frame while having an extremely low energy consumption. Higher speed clock can be used to reach higher baudrates.

LPUART interface can be served by the DMA controller.

### 3.19.4 Serial peripheral interface (SPI)/Inter-integrated sound (I2S)

Up to two SPIs are able to communicate at up to 16 Mbits/s in slave and master modes in full-duplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes.

The USARTs with synchronous capability can also be used as SPI master.

One standard I2S interfaces (multiplexed with SPI2) is available. It can operate in master or slave mode, and can be configured to operate with a 16-/32-bit resolution as input or output channels. Audio sampling frequencies from 8 kHz up to 192 kHz are supported. When the I2S interfaces is configured in master mode, the master clock can be output to the external DAC/CODEC at 256 times the sampling frequency.

The SPIs can be served by the DMA controller.

Refer to Table 14 for the differences between SPI1 and SPI2.

Table 14. SPI/I2S implementation

| SPI features <sup>(1)</sup> | SPI1 | SPI2 |

|-----------------------------|------|------|

| Hardware CRC calculation    | Х    | Х    |

| I2S mode                    | -    | Х    |

| TI mode                     | Х    | Х    |

<sup>1.</sup> X = supported.

## 6.1.7 Optional LCD power supply scheme

Figure 12. Optional LCD power supply scheme

- 1. Option 1: LCD power supply is provided by a dedicated VLCD supply source, VSEL switch is open.

- Option 2: LCD power supply is provided by the internal step-up converter, VSEL switch is closed, an external capacitance is needed for correct behavior of this converter.

### 6.1.8 Current consumption measurement

N × 100 nF + 1 × 10 μF NxVSS

Figure 13. Current consumption measurement scheme

## 6.3 Operating conditions

## 6.3.1 General operating conditions

Table 26. General operating conditions

| Symbol             | Parameter                                                                         | Conditions                                           | Min  | Max                  | Unit  |

|--------------------|-----------------------------------------------------------------------------------|------------------------------------------------------|------|----------------------|-------|

| $f_{HCLK}$         | Internal AHB clock frequency                                                      | -                                                    | 0    | 32                   |       |

| f <sub>PCLK1</sub> | Internal APB1 clock frequency                                                     | -                                                    | 0    | 32                   | MHz   |

| f <sub>PCLK2</sub> | Internal APB2 clock frequency                                                     | -                                                    | 0    | 32                   |       |

|                    |                                                                                   | BOR detector disabled                                | 1.65 | 3.6                  |       |

| $V_{DD}$           | Standard operating voltage                                                        | BOR detector enabled, at power on                    | 1.8  | 3.6                  | V     |

|                    |                                                                                   | BOR detector disabled, after power on                | 1.65 | 3.6                  |       |

| $V_{DDA}$          | Analog operating voltage (DAC not used)                                           | Must be the same voltage as $V_{DD}^{(1)}$           | 1.65 | 3.6                  | ٧     |

| $V_{DDA}$          | Analog operating voltage (all features)                                           | Must be the same voltage as $V_{DD}^{(1)}$           | 1.8  | 3.6                  | ٧     |

| V <sub>DD US</sub> | Standard operating voltage, USB                                                   | USB peripheral used                                  | 3.0  | 3.6                  | V     |

| В                  | domain <sup>(2)</sup>                                                             | USB peripheral not used                              | 1.65 | 3.6                  |       |

|                    | Input voltage on FT, FTf and RST pins <sup>(3)</sup>                              | $2.0~V \leq V_{DD} \leq 3.6~V$                       | -0.3 | 5.5                  | V     |

| V                  | input voltage on F1, F11 and R51 pinston                                          | $1.65 \text{ V} \le \text{V}_{DD} \le 2.0 \text{ V}$ | -0.3 | 5.2                  |       |

| $V_{IN}$           | Input voltage on BOOT0 pin                                                        | -                                                    | 0    | 5.5                  |       |

|                    | Input voltage on TC pin                                                           | -                                                    | -0.3 | V <sub>DD</sub> +0.3 |       |

|                    |                                                                                   | UFBGA100 package                                     | -    | 351                  |       |

|                    |                                                                                   | LQFP100 package                                      | -    | 488                  |       |

|                    | Power dissipation at $T_A = 85$ °C (range 6) or $T_A = 105$ °C (range 7) $^{(4)}$ | TFBGA64 package                                      | -    | 313                  | 1     |

|                    | and a constant                                                                    | LQFP64 package                                       | -    | 435                  |       |

| В                  |                                                                                   | LQFP48 package                                       | -    | 370                  | mW    |

| $P_D$              |                                                                                   | UFBGA100 package                                     | -    | 88                   | IIIVV |

|                    |                                                                                   | LQFP100 package                                      | -    | 122                  |       |

|                    | Power dissipation at $T_A = 125$ °C (range 3) $^{(4)}$                            | TFBGA64 package                                      | -    | 78                   |       |

|                    |                                                                                   | LQFP64 package                                       | -    | 109                  |       |

|                    |                                                                                   | LQFP48 package                                       |      | 93                   |       |

## 6.3.2 Embedded reset and power control block characteristics

The parameters given in the following table are derived from the tests performed under the ambient temperature condition summarized in *Table 26*.

Table 27. Embedded reset and power control block characteristics

| Symbol                               | Parameter                      | Conditions                                          | Min  | Тур  | Max      | Unit |

|--------------------------------------|--------------------------------|-----------------------------------------------------|------|------|----------|------|

|                                      | V via time vata                | BOR detector enabled                                | 0    | -    | $\infty$ |      |

| <b>.</b> (1)                         | V <sub>DD</sub> rise time rate | BOR detector disabled                               | 0    | -    | 1000     | µs/V |

| t <sub>VDD</sub> <sup>(1)</sup>      |                                | BOR detector enabled                                | 20   | -    | $\infty$ |      |

|                                      | V <sub>DD</sub> fall time rate | BOR detector disabled                               | 0    | -    | 1000     |      |

| T <sub>RSTTEMPO</sub> <sup>(1)</sup> | Dogat tomporization            | V <sub>DD</sub> rising, BOR enabled                 | -    | 2    | 3.3      | ma   |

|                                      | Reset temporization            | V <sub>DD</sub> rising, BOR disabled <sup>(2)</sup> | 0.4  | 0.7  | 1.6      | ms   |

| V                                    | Power on/power down reset      | Falling edge                                        | 1    | 1.5  | 1.65     |      |

| V <sub>POR/PDR</sub>                 | threshold                      | Rising edge                                         | 1.3  | 1.5  | 1.65     |      |

| M                                    | Drawn aut roast throabald 0    | Falling edge                                        | 1.67 | 1.7  | 1.74     |      |

| $V_{BOR0}$                           | Brown-out reset threshold 0    | Rising edge                                         | 1.69 | 1.76 | 1.8      |      |

| \/                                   |                                | Falling edge                                        | 1.87 | 1.93 | 1.97     |      |

| V <sub>BOR1</sub>                    | Brown-out reset threshold 1    | Rising edge                                         | 1.96 | 2.03 | 2.07     |      |

| M                                    | Brown-out reset threshold 2    | Falling edge                                        | 2.22 | 2.30 | 2.35     |      |

| $V_{BOR2}$                           |                                | Rising edge                                         | 2.31 | 2.41 | 2.44     |      |

| M                                    | Brown-out reset threshold 3    | Falling edge                                        | 2.45 | 2.55 | 2.6      |      |

| $V_{BOR3}$                           |                                | Rising edge                                         | 2.54 | 2.66 | 2.7      |      |

| V                                    | Drawn aut roast throabald 4    | Falling edge                                        | 2.68 | 2.8  | 2.85     |      |

| $V_{BOR4}$                           | Brown-out reset threshold 4    | Rising edge                                         | 2.78 | 2.9  | 2.95     | .,   |

| 1/                                   | Programmable voltage detector  | Falling edge                                        | 1.8  | 1.85 | 1.88     | V    |

| $V_{PVD0}$                           | threshold 0                    | Rising edge                                         | 1.88 | 1.94 | 1.99     |      |

|                                      | DVD three-bald 4               | Falling edge                                        | 1.98 | 2.04 | 2.09     |      |

| $V_{PVD1}$                           | PVD threshold 1                | Rising edge                                         | 2.08 | 2.14 | 2.18     |      |

| .,                                   | DVD the sector LLO             | Falling edge                                        | 2.20 | 2.24 | 2.28     |      |

| $V_{PVD2}$                           | PVD threshold 2                | Rising edge                                         | 2.28 | 2.34 | 2.38     |      |

|                                      | DVD the sector LLO             | Falling edge                                        | 2.39 | 2.44 | 2.48     |      |

| $V_{PVD3}$                           | PVD threshold 3                | Rising edge                                         | 2.47 | 2.54 | 2.58     |      |

|                                      | DVD the select A               | Falling edge                                        | 2.57 | 2.64 | 2.69     |      |

| $V_{PVD4}$                           | PVD threshold 4                | Rising edge                                         | 2.68 | 2.74 | 2.79     |      |

| .,                                   | 5)(5)                          | Falling edge                                        | 2.77 | 2.83 | 2.88     |      |

| $V_{PVD5}$                           | PVD threshold 5                | Rising edge                                         | 2.87 | 2.94 | 2.99     |      |

| Symbol                                  | Parameter                                                     | Conditions | Min | Тур | Max  | Unit                     |

|-----------------------------------------|---------------------------------------------------------------|------------|-----|-----|------|--------------------------|

| I <sub>LPBUF</sub> <sup>(4)</sup>       | Consumption of reference voltage buffer for VREF_OUT and COMP | -          | -   | 730 | 1200 | nA                       |

| V <sub>REFINT_DIV1</sub> <sup>(4)</sup> | 1/4 reference voltage                                         | -          | 24  | 25  | 26   |                          |

| V <sub>REFINT_DIV2</sub> <sup>(4)</sup> | 1/2 reference voltage                                         | -          | 49  | 50  | 51   | %<br>V <sub>REFINT</sub> |

| V <sub>REFINT_DIV3</sub> <sup>(4)</sup> | 3/4 reference voltage                                         | -          | 74  | 75  | 76   | INEI IIVI                |

Table 29. Embedded internal reference voltage<sup>(1)</sup> (continued)

- Refer to Table 41: Peripheral current consumption in Stop and Standby mode for the value of the internal reference current consumption (I<sub>REFINT</sub>).

- 2. Guaranteed by test in production.

- 3. The internal V<sub>REF</sub> value is individually measured in production and stored in dedicated EEPROM bytes.

- 4. Guaranteed by design.

- 5. Shortest sampling time can be determined in the application by multiple iterations.

- 6. To guarantee less than 1% VREF\_OUT deviation.

### 6.3.4 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code. The current consumption is measured as described in *Figure 13: Current consumption measurement scheme*.

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to Dhrystone 2.1 code if not specified otherwise.

The current consumption values are derived from the tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 26: General operating conditions* unless otherwise specified.

The MCU is placed under the following conditions:

- All I/O pins are configured in analog input mode

- All peripherals are disabled except when explicitly mentioned

- The Flash memory access time and prefetch is adjusted depending on fHCLK frequency and voltage range to provide the best CPU performance unless otherwise specified.

- When the peripherals are enabled f<sub>APB1</sub> = f<sub>APB2</sub> = f<sub>APB</sub>

- When PLL is on, the PLL inputs are equal to HSI = 16 MHz (if internal clock is used) or HSE = 16 MHz (if HSE bypass mode is used)

- The HSE user clock applied to OSCI\_IN input follows the characteristic specified in Table 43: High-speed external user clock characteristics

- For maximum current consumption V<sub>DD</sub> = V<sub>DDA</sub> = 3.6 V is applied to all supply pins

- For typical current consumption V<sub>DD</sub> = V<sub>DDA</sub> = 3.0 V is applied to all supply pins if not specified otherwise

The parameters given in *Table 51*, *Table 26* and *Table 27* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 26*.

Table 37. Typical and maximum current consumptions in Stop mode

| Symbol                 | Parameter                   | Conditions                                 | Тур   | Max <sup>(1)</sup> | Unit |

|------------------------|-----------------------------|--------------------------------------------|-------|--------------------|------|

| I <sub>DD</sub> (Stop) | Supply current in Stop mode | $T_A = -40 \text{ to } 25^{\circ}\text{C}$ | 0,43  | 1,00               |      |

|                        |                             | T <sub>A</sub> = 55°C                      | 0,735 | 2,50               |      |

|                        |                             | T <sub>A</sub> = 85°C                      | 2,25  | 4,90               | μΑ   |

|                        |                             | T <sub>A</sub> = 105°C                     | 5,3   | 13,00              |      |

|                        |                             | T <sub>A</sub> = 125°C                     | 12,5  | 28,00              |      |

<sup>1.</sup> Guaranteed by characterization results at 125 °C, unless otherwise specified.

Figure 17.  $I_{DD}$  vs  $V_{DD}$ , at  $T_A$ = 25/55/ 85/105/125 °C, Stop mode with RTC enabled and running on LSE Low drive

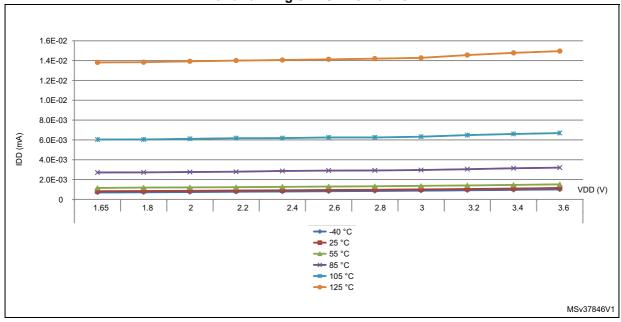

#### 6.3.6 **External clock source characteristics**

### High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO. The external clock signal has to respect the I/O characteristics in Section 6.3.12. However, the recommended clock input waveform is shown in Figure 19.

Table 43. High-speed external user clock characteristics<sup>(1)</sup>

| Symbol                    | Parameter                           | Conditions                       | Min                | Тур | Max                | Unit |

|---------------------------|-------------------------------------|----------------------------------|--------------------|-----|--------------------|------|

| f                         | User external clock source          | CSS is on or<br>PLL is used      | 1                  | 8   | 32                 | MHz  |

| f <sub>HSE_ext</sub>      | frequency                           | CSS is off, PLL not used         | 0                  | 8   | 32                 | MHz  |

| V <sub>HSEH</sub>         | OSC_IN input pin high level voltage |                                  | 0.7V <sub>DD</sub> | -   | $V_{DD}$           | V    |

| V <sub>HSEL</sub>         | OSC_IN input pin low level voltage  |                                  | $V_{SS}$           | ı   | 0.3V <sub>DD</sub> | V    |

| $t_{w(HSE)} \ t_{w(HSE)}$ | OSC_IN high or low time             |                                  | 12                 | ı   | -                  | ns   |

| t <sub>r(HSE)</sub>       | OSC_IN rise or fall time            |                                  | -                  | -   | 20                 | 115  |

| C <sub>in(HSE)</sub>      | OSC_IN input capacitance            |                                  | -                  | 2.6 | -                  | pF   |

| DuCy <sub>(HSE)</sub>     | Duty cycle                          |                                  | 45                 | -   | 55                 | %    |

| IL                        | OSC_IN Input leakage current        | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                  | ı   | ±1                 | μΑ   |

<sup>1.</sup> Guaranteed by design.

Figure 19. High-speed external clock source AC timing diagram

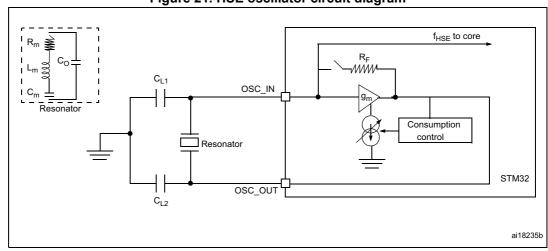

### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 1 to 25 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 45*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol               | Parameter Conditions                      |                               | Min | Тур | Max | Unit     |

|----------------------|-------------------------------------------|-------------------------------|-----|-----|-----|----------|

| f <sub>OSC_IN</sub>  | Oscillator frequency                      | -                             | 1   |     | 25  | MHz      |

| R <sub>F</sub>       | Feedback resistor                         | -                             | -   | 200 | -   | kΩ       |

| G <sub>m</sub>       | Maximum critical crystal transconductance | Startup                       | -   | -   | 700 | μA<br>/V |

| t <sub>SU(HSE)</sub> | Startup time                              | V <sub>DD</sub> is stabilized | -   | 2   | -   | ms       |

Table 45. HSE oscillator characteristics<sup>(1)</sup>

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 21*).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ . Refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website *www.st.com*.

Figure 21. HSE oscillator circuit diagram

4

<sup>1.</sup> Guaranteed by design.

Guaranteed by characterization results. t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

| Symbol                          | Parameter                                                                                             | Conditions                 | Value              | Unit  |

|---------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------|--------------------|-------|

|                                 | raiailletei                                                                                           | Conditions                 | Min <sup>(1)</sup> | Offic |

|                                 | Data retention (program memory) after 10 kcycles at T <sub>A</sub> = 85 °C  T <sub>RET</sub> = +85 °C | 30                         |                    |       |

|                                 | Data retention (EEPROM data memory) after 100 kcycles at T <sub>A</sub> = 85 °C                       | 1 RET - +03 C              | 30                 |       |

| t <sub>RET</sub> <sup>(2)</sup> | Data retention (program memory) after 10 kcycles at T <sub>A</sub> = 105 °C                           | T <sub>RET</sub> = +105 °C | 10                 | years |

| 'RET`                           | Data retention (EEPROM data memory) after 100 kcycles at T <sub>A</sub> = 105 °C                      | 1 RET - +103 G             |                    |       |

|                                 | Data retention (program memory) after 200 cycles at T <sub>A</sub> = 125 °C                           | T <sub>RFT</sub> = +125 °C | 10                 |       |

|                                 | Data retention (EEPROM data memory) after 2 kcycles at T <sub>A</sub> = 125 °C                        | RET - 1125 G               |                    |       |

Table 54. Flash memory and data EEPROM endurance and retention (continued)

#### 6.3.10 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- **Electrostatic discharge (ESD)** (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 55*. They are based on the EMS levels and classes defined in application note AN1709.

**Table 55. EMS characteristics**

| Symbol            | Parameter                                                                                                                                       | Conditions                                                                                                                  | Level/<br>Class |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                                  | $V_{DD} = 3.3 \text{ V, LQFP100, T}_{A} = +25 \text{ °C,} \\ f_{HCLK} = 32 \text{ MHz} \\ \text{conforms to IEC 61000-4-2}$ | 3B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on V <sub>DD</sub> and V <sub>SS</sub> pins to induce a functional disturbance | $V_{DD}$ = 3.3 V, LQFP100, $T_{A}$ = +25 °C, $f_{HCLK}$ = 32 MHz conforms to IEC 61000-4-4                                  | 4A              |

<sup>1.</sup> Guaranteed by characterization results.

<sup>2.</sup> Characterization is done according to JEDEC JESD22-A117.

### Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 26* and *Table 62*, respectively.

Unless otherwise specified, the parameters given in *Table 62* are derived from tests performed under ambient temperature and V<sub>DD</sub> supply voltage conditions summarized in *Table 26*.

Table 62. I/O AC characteristics<sup>(1)</sup>

| OSPEEDRx[1:0]<br>bit value <sup>(1)</sup> | Symbol                  | Parameter                                                       | Conditions                                                       | Min | Max <sup>(2)</sup> | Unit    |  |

|-------------------------------------------|-------------------------|-----------------------------------------------------------------|------------------------------------------------------------------|-----|--------------------|---------|--|

| 00                                        | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup>                                | $C_L = 50 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$  | -   | 400                | kHz     |  |

|                                           |                         |                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.65 V to 2.7 V        | -   | 100                | KIIZ    |  |

| 00                                        | t <sub>f(IO)out</sub>   | Output rise and fall time                                       | $C_L = 50 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$  | -   | 125                | ns      |  |

|                                           | t <sub>r(IO)out</sub>   |                                                                 | $C_L = 50 \text{ pF}, V_{DD} = 1.65 \text{ V to } 2.7 \text{ V}$ | -   | 320                |         |  |

|                                           | f                       | Maximum frequency <sup>(3)</sup>                                | $C_L = 50 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$  | -   | 2                  | MHz     |  |

| 01                                        | f <sub>max(IO)out</sub> | waximum nequency                                                | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.65 V to 2.7 V        | -   | 0.6                | IVIIIZ  |  |

| 01                                        | t <sub>f(IO)out</sub>   | Output vice and fall times                                      | $C_L = 50 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$  | -   | 30                 | - ns    |  |

|                                           | t <sub>r(IO)out</sub>   | Output rise and fall time                                       | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.65 V to 2.7 V        | -   | 65                 |         |  |

|                                           | F                       | Maximum fraguancy(3)                                            | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2.7 V to 3.6 V         | -   | 10                 | N 41 1- |  |

| 10                                        | F <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup>                                | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.65 V to 2.7 V        | -   | 2                  | MHz     |  |

| 10                                        | t <sub>f(IO)out</sub>   | Output rise and fall time                                       | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2.7 V to 3.6 V         | -   | 13                 | ne      |  |

|                                           | t <sub>r(IO)out</sub>   |                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.65 V to 2.7 V        | -   | 28                 | ns      |  |

|                                           | Е                       | Maximum frequency <sup>(3)</sup>                                | $C_L = 30 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$  | -   | 35                 | MHz     |  |

| 11                                        | F <sub>max(IO)out</sub> |                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.65 V to 2.7 V        | -   | 10                 |         |  |

| 11                                        | t <sub>f(IO)out</sub>   | Outrot vice and fall time                                       | C <sub>L</sub> = 30 pF, V <sub>DD</sub> = 2.7 V to 3.6 V         | -   | 6                  | no      |  |

|                                           | t <sub>r(IO)out</sub>   | Output rise and fall time                                       | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.65 V to 2.7 V        | -   | 17                 | ns      |  |

|                                           | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup>                                |                                                                  | -   | 1                  | MHz     |  |

|                                           | t <sub>f(IO)out</sub>   | Output fall time                                                | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2.5 V to 3.6 V         | -   | 10                 | no      |  |

| Fm+                                       | t <sub>r(IO)out</sub>   | Output rise time                                                | 1                                                                |     | 30                 | ns      |  |

| configuration <sup>(4)</sup>              | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup>                                |                                                                  | -   | 350                | KHz     |  |

|                                           | t <sub>f(IO)out</sub>   | Output fall time                                                | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.65 V to 3.6 V        |     | 15                 |         |  |

|                                           | t <sub>r(IO)out</sub>   | Output rise time                                                |                                                                  | -   | 60                 | ns      |  |

| -                                         | t <sub>EXTIpw</sub>     | Pulse width of external signals detected by the EXTI controller | -                                                                | 8   | -                  | ns      |  |

<sup>1.</sup> The I/O speed is configured using the OSPEEDRx[1:0] bits. Refer to the line reference manual for a description of GPIO Port configuration register.

<sup>2.</sup> Guaranteed by design.

<sup>3.</sup> The maximum frequency is defined in Figure 26.

<sup>4.</sup> When Fm+ configuration is set, the I/O speed control is bypassed. Refer to the line reference manual for a detailed description of Fm+ I/O configuration.

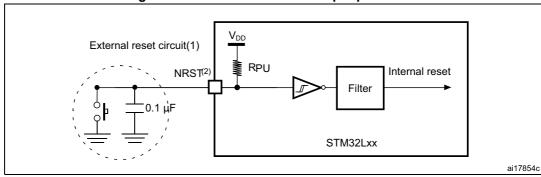

Figure 27. Recommended NRST pin protection

- 1. The reset network protects the device against parasitic resets.

- 2. The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in *Table 63*. Otherwise the reset will not be taken into account by the device.

### 6.3.15 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 64* are derived from tests performed under ambient temperature, f<sub>PCLK</sub> frequency and V<sub>DDA</sub> supply voltage conditions summarized in *Table 26: General operating conditions*.

Note: It is recommended to perform a calibration after each power-up.

**Table 64. ADC characteristics**

| Symbol                             | Parameter                                                        | Conditions                                      | Min                 | Тур | Max               | Unit               |

|------------------------------------|------------------------------------------------------------------|-------------------------------------------------|---------------------|-----|-------------------|--------------------|

| $V_{DDA}$                          | Analog supply voltage for                                        | Fast channel                                    | 1.65                | -   | 3.6               | V                  |

|                                    | ADC on                                                           | Standard channel                                | 1.75 <sup>(1)</sup> | -   | 3.6               | ]                  |

| V <sub>REF+</sub>                  | Positive reference voltage                                       | -                                               | 1.65                |     | $V_{DDA}$         | V                  |

| V <sub>REF-</sub>                  | Negative reference voltage                                       | -                                               | -                   | 0   | -                 |                    |

|                                    | Current consumption of the                                       | 1.14 Msps                                       | -                   | 200 | -                 |                    |

|                                    | ADC on $V_{DDA}$ and $V_{REF+}$                                  | 10 ksps                                         | -                   | 40  | -                 | ] <u>,</u>         |

| I <sub>DDA</sub> (ADC)             | Current consumption of the ADC on V <sub>DD</sub> <sup>(2)</sup> | 1.14 Msps                                       | -                   | 70  | -                 | - μΑ               |

|                                    |                                                                  | 10 ksps                                         | -                   | 1   | -                 |                    |

|                                    | ADC clock frequency                                              | Voltage scaling Range 1                         | 0.14                | -   | 16                |                    |

| $f_{ADC}$                          |                                                                  | Voltage scaling Range 2                         | 0.14                | -   | 8                 | MHz                |

|                                    |                                                                  | Voltage scaling Range 3                         | 0.14                | -   | 4                 |                    |

| f <sub>S</sub> <sup>(3)</sup>      | Sampling rate                                                    | 12-bit resolution                               | 0.01                | -   | 1.14              | MHz                |

| f <sub>TRIG</sub> <sup>(3)</sup>   | External trigger frequency                                       | f <sub>ADC</sub> = 16 MHz,<br>12-bit resolution | -                   | -   | 941               | kHz                |

|                                    |                                                                  | -                                               | -                   | -   | 17                | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub>                   | Conversion voltage range                                         | -                                               | 0                   | -   | V <sub>REF+</sub> | V                  |

| R <sub>AIN</sub> <sup>(3)</sup>    | External input impedance                                         | See Equation 1 and Table 65 for details         | -                   | -   | 50                | kΩ                 |

| R <sub>ADC</sub> <sup>(3)(4)</sup> | Sampling switch resistance                                       | -                                               | -                   | -   | 1                 | kΩ                 |

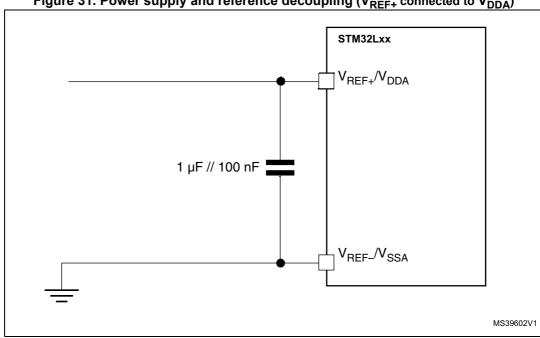

Figure 31. Power supply and reference decoupling ( $V_{REF+}$  connected to  $V_{DDA}$ )