# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Core ProcessorARM® Cortex®-M0+Core Size32-Bit Single-CoreSpeed32MHzConnectivityI²C, IrDA, LINbus, SPI, UART/USART, USBPeripheralsBrown-out Detect/Reset, DMA, I²S, LCD, POR, PWM, WDTNumber of I/O84Program Memory Size192KB (192K x 8)Program Memory TypeFLASHEEPROM Size3K x 8RAM Size20K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 16x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LOFP (14x14) |                            |                                                                       |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------------------------------|--|--|

| Core Size32-Bit Single-CoreSpeed32MHzConnectivityP'C, IrDA, LINbus, SPI, UART/USART, USBPeripheralsBrown-out Detect/Reset, DMA, I'S, LCD, POR, PWM, WDTNumber of I/O84Program Memory Size192KB (192K x 8)Program Memory TypeFLASHEEPROM Size3K x 8RAM Size20K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 16x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP (14x14)                               | Product Status             | Active                                                                |  |  |

| Speed32MHzConnectivityI²C, IrDA, LINbus, SPI, UART/USART, USBPeripheralsBrown-out Detect/Reset, DMA, I²S, LCD, POR, PWM, WDTNumber of I/O84Program Memory Size192KB (192K x 8)Program Memory TypeFLASHEEPROM Size3K x 8RAM Size20K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 16x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP (14x14)                                                          | Core Processor             | ARM® Cortex®-M0+                                                      |  |  |

| ProductivityP²C, IrDA, LINbus, SPI, UART/USART, USBPeripheralsBrown-out Detect/Reset, DMA, I²S, LCD, POR, PWM, WDTNumber of I/O84Program Memory Size192KB (192K x 8)Program Memory TypeFLASHEEPROM Size3K x 8RAM Size20K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 16x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP (14x14)                                                                    | Core Size                  | 32-Bit Single-Core                                                    |  |  |

| PeripheralsBrown-out Detect/Reset, DMA, I²S, LCD, POR, PWM, WDTNumber of I/O84Program Memory Size192KB (192K x 8)Program Memory TypeFLASHEEPROM Size3K x 8RAM Size20K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 16x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP (14x14)                                                                                                                       | Speed                      | 32MHz                                                                 |  |  |

| Number of I/O84Program Memory Size192KB (192K x 8)Program Memory TypeFLASHEEPROM Size3K x 8RAM Size20K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 16x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP (14x14)                                                                                                                                                                                      | Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                  |  |  |

| Program Memory Size192KB (192K x 8)Program Memory TypeFLASHEEPROM Size3K x 8RAM Size20K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 16x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP (14x14)                                                                                                                                                                                                     | Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT     |  |  |

| Program Memory TypeFLASHEEPROM Size3K x 8RAM Size20K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 16x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP (14x14)                                                                                                                                                                                                                                        | Number of I/O              | 84                                                                    |  |  |

| EEPROM Size3K x 8RAM Size20K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 16x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP (14x14)                                                                                                                                                                                                                                                                | Program Memory Size        | 192КВ (192К х 8)                                                      |  |  |

| RAM Size20K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 16x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LQFPSupplier Device Package100-LQFP (14x14)                                                                                                                                                                                                                                                  | Program Memory Type        | FLASH                                                                 |  |  |

| Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 16x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LQFPSupplier Device Package100-LQFP (14x14)                                                                                                                                                                                                                                                                 | EEPROM Size                | 3K x 8                                                                |  |  |

| Data ConvertersA/D 16x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LQFPSupplier Device Package100-LQFP (14x14)                                                                                                                                                                                                                                                                                                      | RAM Size                   | 20K x 8                                                               |  |  |

| Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LQFPSupplier Device Package100-LQFP (14x14)                                                                                                                                                                                                                                                                                                                                          | Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                           |  |  |

| Operating Temperature     -40°C ~ 85°C (TA)       Mounting Type     Surface Mount       Package / Case     100-LQFP       Supplier Device Package     100-LQFP (14x14)                                                                                                                                                                                                                                                                                                                        | Data Converters            | A/D 16x12b; D/A 2x12b                                                 |  |  |

| Mounting Type     Surface Mount       Package / Case     100-LQFP       Supplier Device Package     100-LQFP (14x14)                                                                                                                                                                                                                                                                                                                                                                          | Oscillator Type            | Internal                                                              |  |  |

| Package / Case     100-LQFP       Supplier Device Package     100-LQFP (14x14)                                                                                                                                                                                                                                                                                                                                                                                                                | Operating Temperature      | -40°C ~ 85°C (TA)                                                     |  |  |

| Supplier Device Package     100-LQFP (14x14)                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Mounting Type              | Surface Mount                                                         |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Package / Case             | 100-LQFP                                                              |  |  |

| Purchase URL https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l083vzt6                                                                                                                                                                                                                                                                                                                                                                                                            | Supplier Device Package    | 100-LQFP (14x14)                                                      |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l083vzt6 |  |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                | Functionalitie                                               | tionalities depending on the operating power supply range |                            |                           |  |  |

|------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------|----------------------------|---------------------------|--|--|

| Operating power<br>supply range                | DAC and ADC<br>operation Dynamic<br>voltage scaling<br>range |                                                           | I/O operation              | USB                       |  |  |

| V <sub>DD</sub> = 1.65 to 1.71 V               | ADC only,<br>conversion time<br>up to 570 ksps               | conversion time Range 2 or                                |                            | Not functional            |  |  |

| V <sub>DD</sub> = 1.71 to 1.8 V <sup>(1)</sup> | ADC only,<br>conversion time<br>up to 1.14 Msps              | Range 1, range 2<br>or range 3                            | Degraded speed performance | Functional <sup>(2)</sup> |  |  |

| $V_{DD}$ = 1.8 to 2.0 V <sup>(1)</sup>         | Conversion time<br>up to 1.14 Msps                           | Range1, range 2<br>or range 3                             | Degraded speed performance | Functional <sup>(2)</sup> |  |  |

| V <sub>DD</sub> = 2.0 to 2.4 V                 | Conversion time<br>up to<br>1.14 Msps                        | Range 1, range 2<br>or range 3                            | Full speed operation       | Functional <sup>(2)</sup> |  |  |

| V <sub>DD</sub> = 2.4 to 3.6 V                 | Conversion time<br>up to<br>1.14 Msps                        | Range 1, range 2<br>or range 3                            | Full speed operation       | Functional <sup>(2)</sup> |  |  |

| Table 3. Functionalities | depending on the operating | g power supply range |

|--------------------------|----------------------------|----------------------|

CPU frequency changes from initial to final must respect "fcpu initial <4\*fcpu final". It must also respect 5

µs delay between two changes. For example to switch from 4.2 MHz to 32 MHz, you can switch from 4.2

MHz to 16 MHz, wait 5 µs, then switch from 16 MHz to 32 MHz.</li>

2. To be USB compliant from the I/O voltage standpoint, the minimum  $V_{\text{DD\_USB}}$  is 3.0 V.

#### Table 4. CPU frequency range depending on dynamic voltage scaling

| CPU frequency range                              | Dynamic voltage scaling range |

|--------------------------------------------------|-------------------------------|

| 16 MHz to 32 MHz (1ws)<br>32 kHz to 16 MHz (0ws) | Range 1                       |

| 8 MHz to 16 MHz (1ws)<br>32 kHz to 8 MHz (0ws)   | Range 2                       |

| 32 kHz to 4.2 MHz (0ws) Range 3                  |                               |

#### • Startup clock

After reset, the microcontroller restarts by default with an internal 2.1 MHz clock (MSI). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

#### • Clock security system (CSS)

This feature can be enabled by software. If an HSE clock failure occurs, the master clock is automatically switched to HSI and a software interrupt is generated if enabled.

Another clock security system can be enabled, in case of failure of the LSE it provides an interrupt or wakeup event which is generated if enabled.

#### • Clock-out capability (MCO: microcontroller clock output)

It outputs one of the internal clocks for external use by the application.

Several prescalers allow the configuration of the AHB frequency, each APB (APB1 and APB2) domains. The maximum frequency of the AHB and the APB domains is 32 MHz. See *Figure 2* for details on the clock tree.

## 3.17 AES

The AES Hardware Accelerator can be used to encrypt and decrypt data using the AES algorithm (compatible with FIPS PUB 197, 2001 Nov 26).

- Key scheduler

- Key derivation for decryption

- 128-bit data block processed

- 128-bit key length

- 213 clock cycles to encrypt/decrypt one 128-bit block

- Electronic codebook (ECB), cypher block chaining (CBC), and counter mode (CTR) supported by hardware.

The AES can be served by the DMA controller.

### 3.18 Timers and watchdogs

The ultra-low-power STM32L083xx devices include three general-purpose timers, one low-power timer (LPTIM), one basic timer, two watchdog timers and the SysTick timer.

*Table 10* compares the features of the general-purpose and basic timers.

| Timer           | Counter resolution | Counter type         | Prescaler factor                   | DMA<br>request<br>generation | Capture/compare<br>channels | Complementary<br>outputs |

|-----------------|--------------------|----------------------|------------------------------------|------------------------------|-----------------------------|--------------------------|

| TIM2,<br>TIM3   | 16-bit             | Up, down,<br>up/down | Any integer between<br>1 and 65536 | Yes                          | 4                           | No                       |

| TIM21,<br>TIM22 | 16-bit             | Up, down,<br>up/down | Any integer between<br>1 and 65536 | No                           | 2                           | No                       |

| TIM6,<br>TIM7   | 16-bit             | Up                   | Any integer between<br>1 and 65536 | Yes                          | 0                           | No                       |

Table 10. Timer feature comparison

#### 3.18.1 General-purpose timers (TIM2, TIM3, TIM21 and TIM22)

There are four synchronizable general-purpose timers embedded in the STM32L083xx device (see *Table 10* for differences).

#### TIM2, TIM3

TIM2 and TIM3 are based on 16-bit auto-reload up/down counter. It includes a 16-bit prescaler. It features four independent channels each for input capture/output compare, PWM or one-pulse mode output.

The TIM2/TIM3 general-purpose timers can work together or with the TIM21 and TIM22 general-purpose timers via the Timer Link feature for synchronization or event chaining. Their counter can be frozen in debug mode. Any of the general-purpose timers can be used to generate PWM outputs.

TIM2/TIM3 have independent DMA request generation.

DocID027070 Rev 3

#### 3.18.6 Window watchdog (WWDG)

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

## 3.19 Communication interfaces

## 3.19.1 I<sup>2</sup>C bus

Up to three I<sup>2</sup>C interfaces (I2C1 and I2C3) can operate in multimaster or slave modes.

Each I<sup>2</sup>C interface can support Standard mode (Sm, up to 100 kbit/s), Fast mode (Fm, up to 400 kbit/s) and Fast Mode Plus (Fm+, up to 1 Mbit/s) with 20 mA output drive on some I/Os.

7-bit and 10-bit addressing modes, multiple 7-bit slave addresses (2 addresses, 1 with configurable mask) are also supported as well as programmable analog and digital noise filters.

|                                     | Analog filter                                         | Digital filter                                                                                       |

|-------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Pulse width of<br>suppressed spikes | ≥ 50 ns                                               | Programmable length from 1 to 15<br>I2C peripheral clocks                                            |

| Benefits                            | Available in Stop mode                                | <ol> <li>Extra filtering capability vs.<br/>standard requirements.</li> <li>Stable length</li> </ol> |

| Drawbacks                           | Variations depending on temperature, voltage, process | Wakeup from Stop on address<br>match is not available when digital<br>filter is enabled.             |

Table 11. Comparison of I2C analog and digital filters

In addition, I2C1 and I2C3 provide hardware support for SMBus 2.0 and PMBus 1.1: ARP capability, Host notify protocol, hardware CRC (PEC) generation/verification, timeouts verifications and ALERT protocol management. I2C1/I2C3 also have a clock domain independent from the CPU clock, allowing the I2C1/I2C3 to wake up the MCU from Stop mode on address match.

Each I2C interface can be served by the DMA controller.

Refer to Table 12 for an overview of I2C interface features.

| Table 12. STM32L083xx I <sup>2</sup> C i | implementation |

|------------------------------------------|----------------|

|------------------------------------------|----------------|

| I2C features <sup>(1)</sup>      | I2C1 | I2C2 | I2C3 |

|----------------------------------|------|------|------|

| 7-bit addressing mode            | Х    | Х    | Х    |

| 10-bit addressing mode           | Х    | Х    | Х    |

| Standard mode (up to 100 kbit/s) | Х    | Х    | Х    |

| Fast mode (up to 400 kbit/s)     | Х    | Х    | Х    |

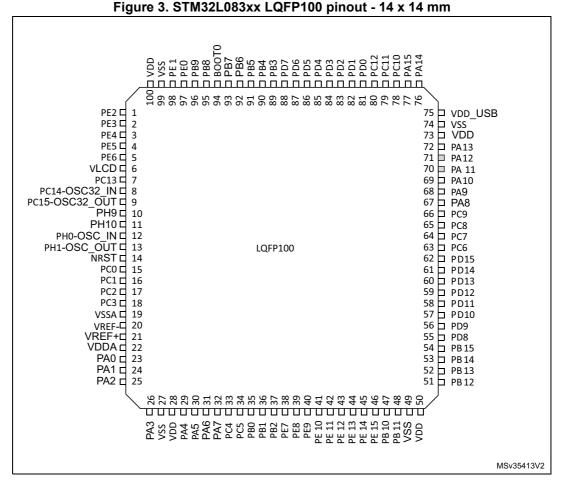

## 4 Pin descriptions

1. The above figure shows the package top view.

2. I/O pin supplied by VDD\_USB.

|                   |        |      |                                                                                                   |                                      | Table 20. A                                                                         | Iternate func         | tions port D                                       |                                              |                                                             |                               |

|-------------------|--------|------|---------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------------------------------------------------------|-----------------------|----------------------------------------------------|----------------------------------------------|-------------------------------------------------------------|-------------------------------|

|                   |        |      | AF0                                                                                               | AF1                                  | AF2                                                                                 | AF3                   | AF4                                                | AF5                                          | AF6                                                         | AF7                           |

|                   |        | Port | SPI1/SPI2/I2S2/<br>USART1/2/<br>LPUART1/USB/<br>LPTIM1/TSC/<br>TIM2/21/22/<br>EVENTOUT/<br>SYS_AF | SPI1/SPI2/I2S2/I2C1/<br>LCD/TIM2/21  | SPI1/SPI2/I2S2/<br>LPUART1/<br>USART5/USB/<br>LPTIM1/TIM2/3<br>/EVENTOUT/<br>SYS_AF | I2C1/TSC/<br>EVENTOUT | I2C1/USART1/2/<br>LPUART1/<br>TIM3/22/<br>EVENTOUT | SPI2/I2S2<br>/I2C2/<br>USART1/<br>TIM2/21/22 | I2C1/2/<br>LPUART1/<br>USART4/<br>UASRT5/TIM21/E<br>VENTOUT | I2C3/LPUART1/<br>COMP1/2/TIM3 |

|                   |        | PD0  | TIM21_CH1                                                                                         | SPI2_NSS/I2S2_WS                     | -                                                                                   | -                     | -                                                  | -                                            | -                                                           | -                             |

|                   |        | PD1  | -                                                                                                 | SPI2_SCK/I2S2_CK                     | -                                                                                   | -                     | -                                                  | -                                            | -                                                           | -                             |

|                   |        | PD2  | LPUART1_RTS_<br>DE                                                                                | LCD_COM7/<br>LCD_SEG31/<br>LCD_SEG51 | TIM3_ETR                                                                            | -                     | -                                                  | -                                            | USART5_RX                                                   | -                             |

| Doc               |        | PD3  | USART2_CTS                                                                                        | LCD_SEG44                            | SPI2_MISO/<br>I2S2_MCK                                                              | -                     | -                                                  | -                                            | -                                                           | -                             |

| DocID027070 Rev 3 |        | PD4  | USART2_RTS_D<br>E                                                                                 | SPI2_MOSI/I2S2_SD                    | -                                                                                   | -                     | -                                                  | -                                            | -                                                           | -                             |

| 070               |        | PD5  | USART2_TX                                                                                         | -                                    | -                                                                                   | -                     | -                                                  | -                                            | -                                                           | -                             |

| 10<br>P<br>V      | t D    | PD6  | USART2_RX                                                                                         | -                                    | -                                                                                   | -                     | -                                                  | -                                            | -                                                           | -                             |

| <del>در</del>     | Port D | PD7  | USART2_CK                                                                                         | TIM21_CH2                            | -                                                                                   | -                     | -                                                  | -                                            | -                                                           | -                             |

|                   |        | PD8  | LPUART1_TX                                                                                        | LCD_SEG28                            | -                                                                                   | -                     | -                                                  | -                                            | -                                                           | -                             |

|                   |        | PD9  | LPUART1_RX                                                                                        | LCD_SEG29                            | -                                                                                   | -                     | -                                                  | -                                            | -                                                           | -                             |

|                   |        | PD10 | -                                                                                                 | LCD_SEG30                            | -                                                                                   | -                     | -                                                  | -                                            | -                                                           | -                             |

|                   |        | PD11 | LPUART1_CTS                                                                                       | LCD_SEG31                            | -                                                                                   | -                     | -                                                  | -                                            | -                                                           | -                             |

|                   |        | PD12 | LPUART1_RTS_<br>DE                                                                                | LCD_SEG32                            | -                                                                                   | -                     | -                                                  | -                                            | -                                                           | -                             |

|                   |        | PD13 | -                                                                                                 | LCD_SEG33                            | -                                                                                   | -                     | -                                                  | -                                            | -                                                           | -                             |

|                   |        | PD14 | -                                                                                                 | LCD_SEG34                            | -                                                                                   | -                     | -                                                  | -                                            | -                                                           | -                             |

|                   |        | PD15 | USB_CRS_SYNC                                                                                      | LCD_SEG35                            | -                                                                                   | -                     | -                                                  | -                                            | -                                                           | -                             |

STM32L083xx

53/139

Pin descriptions

| Symbol            | Parameter          | Conditions                                | Min  | Тур  | Max  | Unit |  |

|-------------------|--------------------|-------------------------------------------|------|------|------|------|--|

| V                 | PVD threshold 6    | Falling edge                              | 2.97 | 3.05 | 3.09 | V    |  |

| V <sub>PVD6</sub> | PVD threshold o    | Rising edge                               | 3.08 | 3.15 | 3.20 | v    |  |

|                   |                    | BOR0 threshold                            | -    | 40   | -    |      |  |

| V <sub>hyst</sub> | Hysteresis voltage | All BOR and PVD thresholds excepting BOR0 | -    | 100  | -    | mV   |  |

Table 27. Embedded reset and power control block characteristics (continued)

1. Guaranteed by characterization results.

2. Valid for device version without BOR at power up. Please see option "D" in Ordering information scheme for more details.

### 6.3.3 Embedded internal reference voltage

The parameters given in *Table 29* are based on characterization results, unless otherwise specified.

| Table 28. Embedde | d internal reference voltage calibration | values |

|-------------------|------------------------------------------|--------|

|                   |                                          |        |

| Calibration value name | Description                                                            | Memory address            |

|------------------------|------------------------------------------------------------------------|---------------------------|

| VREFINT_CAL            | Raw data acquired at<br>temperature of 25 °C<br>V <sub>DDA</sub> = 3 V | 0x1FF8 0078 - 0x1FF8 0079 |

| Symbol                                   | Parameter                                                                                    | Conditions                                                                              | Min   | Тур   | Max   | Unit   |

|------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------|-------|-------|--------|

| V <sub>REFINT out</sub> <sup>(2)</sup>   | Internal reference voltage                                                                   | – 40 °C < T <sub>J</sub> < +125 °C                                                      | 1.202 | 1.224 | 1.242 | V      |

| T <sub>VREFINT</sub>                     | Internal reference startup time                                                              | -                                                                                       | -     | 2     | 3     | ms     |

| V <sub>VREF_MEAS</sub>                   | V <sub>DDA</sub> and V <sub>REF+</sub> voltage during<br>V <sub>REFINT</sub> factory measure | -                                                                                       | 2.99  | 3     | 3.01  | V      |

| A <sub>VREF_MEAS</sub>                   | Accuracy of factory-measured $V_{REFINT}$ value <sup>(3)</sup>                               | Including uncertainties<br>due to ADC and<br>V <sub>DDA</sub> /V <sub>REF+</sub> values | -     | -     | ±5    | mV     |

| T <sub>Coeff</sub> <sup>(4)</sup>        | Temperature coefficient                                                                      | –40 °C < T <sub>J</sub> < +125 °C                                                       | -     | 25    | 100   | ppm/°C |

| A <sub>Coeff</sub> <sup>(4)</sup>        | Long-term stability                                                                          | 1000 hours, T= 25 °C                                                                    | -     | -     | 1000  | ppm    |

| V <sub>DDCoeff</sub> <sup>(4)</sup>      | Voltage coefficient                                                                          | 3.0 V < V <sub>DDA</sub> < 3.6 V                                                        | -     | -     | 2000  | ppm/V  |

| T <sub>S_vrefint</sub> <sup>(4)(5)</sup> | ADC sampling time when reading the internal reference voltage                                | -                                                                                       | 5     | 10    | -     | μs     |

| T <sub>ADC_BUF</sub> <sup>(4)</sup>      | Startup time of reference voltage buffer for ADC                                             | -                                                                                       | -     | -     | 10    | μs     |

| I <sub>BUF_ADC</sub> <sup>(4)</sup>      | Consumption of reference voltage buffer for ADC                                              | -                                                                                       | -     | 13.5  | 25    | μA     |

| I <sub>VREF_OUT</sub> <sup>(4)</sup>     | VREF_OUT output current <sup>(6)</sup>                                                       | -                                                                                       | -     | -     | 1     | μA     |

| C <sub>VREF_OUT</sub> <sup>(4)</sup>     | VREF_OUT output load                                                                         | -                                                                                       | -     | -     | 50    | pF     |

#### Table 29. Embedded internal reference voltage<sup>(1)</sup>

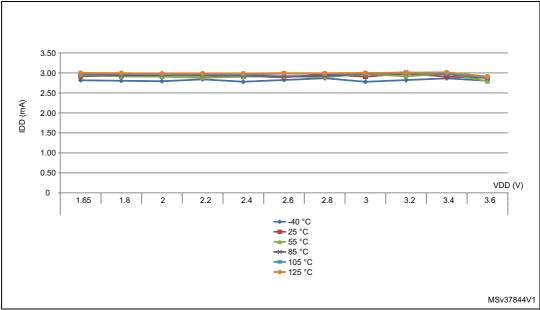

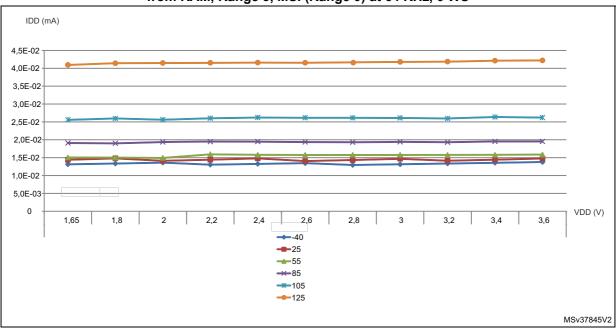

Figure 16. I<sub>DD</sub> vs V<sub>DD</sub>, at T<sub>A</sub>= 25 °C, Low-power run mode, code running from RAM, Range 3, MSI (Range 0) at 64 KHz, 0 WS

| Symbol                        | Parameter                                    |  | Condition                                                              |                              | Тур  | Max<br>(1) | Unit |

|-------------------------------|----------------------------------------------|--|------------------------------------------------------------------------|------------------------------|------|------------|------|

|                               |                                              |  | MSI clock = 65 kHz,<br>f <sub>HCLK</sub> = 32 kHz,<br>Flash memory OFF | $T_A = -40$ to $25^{\circ}C$ | 4,7  | -          |      |

|                               |                                              |  |                                                                        | $T_A = -40$ to $25^{\circ}C$ | 17   | 24         | 1    |

| . Su                          |                                              |  | MSI clock = 65 kHz,                                                    | T <sub>A</sub> = 85°C        | 19,5 | 30         | 1    |

|                               | Supply current in<br>Low-power sleep<br>mode |  | f <sub>HCLK</sub> = 32 kHz                                             | T <sub>A</sub> = 105°C       | 23   | 47         | -    |

|                               |                                              |  |                                                                        | T <sub>A</sub> = 125°C       | 32,5 | 70         |      |

|                               |                                              |  | MSI clock = 65 kHz,<br>f <sub>HCLK</sub> = 65 kHz                      | $T_A = -40$ to $25^{\circ}C$ | 17   | 24         | ]    |

| I <sub>DD</sub><br>(LP Sleep) |                                              |  |                                                                        | T <sub>A</sub> = 85°C        | 20   | 31         | μA   |

|                               | mode                                         |  |                                                                        | T <sub>A</sub> = 105°C       | 23,5 | 47         |      |

|                               |                                              |  |                                                                        | T <sub>A</sub> = 125°C       | 32,5 | 70         |      |

|                               |                                              |  |                                                                        | $T_A$ = - 40 to 25°C         | 19,5 | 27         |      |

|                               |                                              |  |                                                                        | T <sub>A</sub> = 55°C        | 20,5 | 28         |      |

|                               |                                              |  | MSI clock = 131kHz,<br>f <sub>HCLK</sub> = 131 kHz                     | T <sub>A</sub> = 85°C        | 22,5 | 33         | ]    |

|                               |                                              |  | HULK TOT KIZ                                                           | T <sub>A</sub> = 105°C       | 26   | 50         |      |

|                               |                                              |  |                                                                        | T <sub>A</sub> = 125°C       | 35   | 73         |      |

#### Table 36. Current consumption in Low-power sleep mode

1. Guaranteed by characterization results at 125 °C, unless otherwise specified.

|                     |                     | / <sub>DD</sub> = 3.0 V, T <sub>A</sub> =             | 25 °C                                                 |                                                       |                               |                                |

|---------------------|---------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------|--------------------------------|

| Peripheral          |                     | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | Range 3,<br>V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | Low-power<br>sleep and<br>run | Unit                           |

|                     | ADC1 <sup>(2)</sup> | 5.5                                                   | 5                                                     | 3.5                                                   | 4                             |                                |

|                     | SPI1                | 4                                                     | 3                                                     | 3                                                     | 2.5                           |                                |

|                     | USART1              | 14.5                                                  | 11.5                                                  | 9.5                                                   | 12                            |                                |

| APB2                | TIM21               | 7.5                                                   | 6                                                     | 5                                                     | 5.5                           | µA/MHz                         |

| APDZ                | TIM22               | 7                                                     | 6                                                     | 5                                                     | 6                             | (f <sub>HCLK</sub> )           |

|                     | FIREWALL            | 1.5                                                   | 1                                                     | 1                                                     | 0.5                           |                                |

|                     | DBGMCU              | 1.5                                                   | 1                                                     | 1                                                     | 0.5                           |                                |

|                     | SYSCFG              | 2.5                                                   | 2                                                     | 2                                                     | 1.5                           |                                |

|                     | GPIOA               | 3.5                                                   | 3                                                     | 2.5                                                   | 2.5                           | μA/MHz                         |

|                     | GPIOB               | 3.5                                                   | 2.5                                                   | 2                                                     | 2.5                           |                                |

| Cortex-<br>M0+ core | GPIOC               | 8.5                                                   | 6.5                                                   | 5.5                                                   | 7                             |                                |

| I/O port            | GPIOD               | 1                                                     | 0.5                                                   | 0.5                                                   | 0.5                           | (f <sub>HCLK</sub> )           |

|                     | GPIOE               | 8                                                     | 6                                                     | 5                                                     | 6                             |                                |

|                     | GPIOH               | 1.5                                                   | 1                                                     | 1                                                     | 0.5                           |                                |

|                     | CRC                 | 1.5                                                   | 1                                                     | 1                                                     | 1                             |                                |

|                     | FLASH               | 0 <sup>(3)</sup>                                      | 0 <sup>(3)</sup>                                      | 0 <sup>(3)</sup>                                      | 0 <sup>(3)</sup>              |                                |

| AHB                 | DMA1                | 10                                                    | 8                                                     | 6.5                                                   | 8.5                           | µA/MHz                         |

| АПБ                 | RNG                 | 5.5                                                   | 1                                                     | 0.5                                                   | 0.5                           | (f <sub>HCLK</sub> )           |

|                     | TSC                 | 3                                                     | 2.5                                                   | 2                                                     | 3                             |                                |

|                     | AES                 | 0 <sup>(3)</sup>                                      | 0 <sup>(3)</sup>                                      | 0 <sup>(3)</sup>                                      | 0 <sup>(3)</sup>              |                                |

| All e               | enabled             | 204                                                   | 162                                                   | 130                                                   | 202                           | µA/MHz<br>(f <sub>HCLK</sub> ) |

| PWR                 |                     | 2.5                                                   | 2                                                     | 2                                                     | 1                             | µA/MHz<br>(f <sub>HCLK</sub> ) |

| Table 40. Peripheral current consumption in Run or Sleep mode <sup>(1)</sup> (continued) |

|------------------------------------------------------------------------------------------|

|------------------------------------------------------------------------------------------|

Data based on differential I<sub>DD</sub> measurement between all peripherals off an one peripheral with clock enabled, in the following conditions: f<sub>HCLK</sub> = 32 MHz (range 1), f<sub>HCLK</sub> = 16 MHz (range 2), f<sub>HCLK</sub> = 4 MHz (range 3), f<sub>HCLK</sub> = 64kHz (Low-power run/sleep), f<sub>APB1</sub> = f<sub>HCLK</sub>, f<sub>APB2</sub> = f<sub>HCLK</sub>, default prescaler value for each peripheral. The CPU is in Sleep mode in both cases. No I/O pins toggling. Not tested in production.

2. HSI oscillator is off for this measure.

3. Current consumption is negligible and close to 0  $\mu$ A.

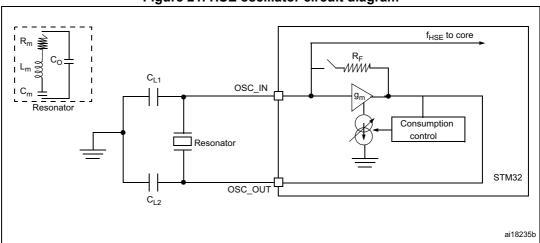

#### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 1 to 25 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 45*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol               | Parameter                                 | Conditions                    | Min | Тур | Max | Unit     |  |  |

|----------------------|-------------------------------------------|-------------------------------|-----|-----|-----|----------|--|--|

| f <sub>OSC_IN</sub>  | Oscillator frequency                      | -                             | 1   |     | 25  | MHz      |  |  |

| R <sub>F</sub>       | Feedback resistor                         | -                             | -   | 200 | -   | kΩ       |  |  |

| G <sub>m</sub>       | Maximum critical crystal transconductance | Startup                       | -   | -   | 700 | μΑ<br>/V |  |  |

| t <sub>SU(HSE)</sub> | Startup time                              | $V_{\text{DD}}$ is stabilized | -   | 2   | -   | ms       |  |  |

Table 45. HSE oscillator characteristics<sup>(1)</sup>

1. Guaranteed by design.

2. Guaranteed by characterization results. t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 21*).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ . Refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website *www.st.com*.

Figure 21. HSE oscillator circuit diagram

## 6.3.9 Memory characteristics

### **RAM** memory

| Symbol | Parameter                          | Conditions           | Min  | Тур | Max | Unit |

|--------|------------------------------------|----------------------|------|-----|-----|------|

| VRM    | Data retention mode <sup>(1)</sup> | STOP mode (or RESET) | 1.65 | -   | -   | V    |

Table 52. RAM and hardware registers

1. Minimum supply voltage without losing data stored in RAM (in Stop mode or under Reset) or in hardware registers (only in Stop mode).

#### Flash memory and data EEPROM

| Symbol                                                                                                                                                 | Parameter                                 | Conditions                                      | Min  | Тур  | Max <sup>(1)</sup> | Unit |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------------|------|------|--------------------|------|--|

| V <sub>DD</sub>                                                                                                                                        | Operating voltage<br>Read / Write / Erase | -                                               | 1.65 | -    | 3.6                | V    |  |

| t <sub>prog</sub>                                                                                                                                      | Programming time for word or half-page    | Erasing                                         | -    | 3.28 | 3.94               | me   |  |

|                                                                                                                                                        |                                           | Programming                                     | -    | 3.28 | 3.94               | ms   |  |

| Average current during<br>the whole programming /<br>erase operation<br>Maximum current (peak)<br>during the whole<br>programming / erase<br>operation |                                           | -                                               | 500  | 700  | μA                 |      |  |

|                                                                                                                                                        | during the whole programming / erase      | T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 3.6 V | -    | 1.5  | 2.5                | mA   |  |

#### Table 53. Flash memory and data EEPROM characteristics

1. Guaranteed by design.

| Table 54. Flash memory | and data EEPROM endurance and retention |  |

|------------------------|-----------------------------------------|--|

|                        |                                         |  |

| Symbol                          | Parameter                                     | Conditions                       | Value              | Unit      |  |

|---------------------------------|-----------------------------------------------|----------------------------------|--------------------|-----------|--|

| Symbol                          | Falameter                                     | Conditions                       | Min <sup>(1)</sup> | Unit      |  |

| N <sub>CYC</sub> <sup>(2)</sup> | Cycling (erase / write)<br>Program memory     | T 40°C to 105 °C                 | 10                 | - kcycles |  |

|                                 | Cycling (erase / write)<br>EEPROM data memory | T <sub>A</sub> = -40°C to 105 °C | 100                |           |  |

|                                 | Cycling (erase / write)<br>Program memory     | T 40°C to 125 °C                 | 0.2                |           |  |

|                                 | Cycling (erase / write)<br>EEPROM data memory | T <sub>A</sub> = -40°C to 125 °C | 2                  |           |  |

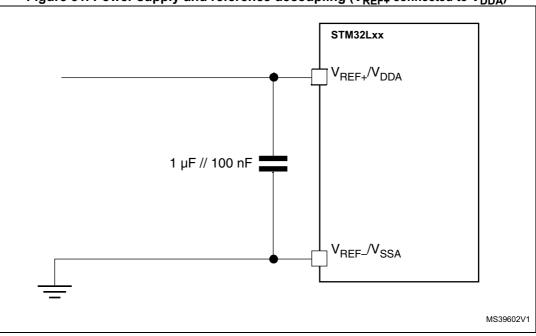

Figure 31. Power supply and reference decoupling ( $V_{REF+}$  connected to  $V_{DDA}$ )

| Symbol                                       | Parameter                            | Conditions                                               | Min     | Тур   | Max              | Unit |

|----------------------------------------------|--------------------------------------|----------------------------------------------------------|---------|-------|------------------|------|

|                                              |                                      | Master mode                                              |         |       | 8                |      |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>    | SPI clock frequency                  | Slave mode Transmitter<br>1.65 <v<sub>DD&lt;3.6V</v<sub> | -       | -     | 8                | MHz  |

|                                              |                                      | Slave mode Transmitter<br>2.7 <v<sub>DD&lt;3.6V</v<sub>  |         |       | 8 <sup>(2)</sup> |      |

| Duty <sub>(SCK)</sub>                        | Duty cycle of SPI clock<br>frequency | Slave mode                                               | 30      | 50    | 70               | %    |

| t <sub>su(NSS)</sub>                         | NSS setup time                       | Slave mode, SPI presc = 2                                | 4*Tpclk | -     | -                |      |

| t <sub>h(NSS)</sub>                          | NSS hold time                        | Slave mode, SPI presc = 2                                | 2*Tpclk | -     | -                |      |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time                | Master mode                                              | Tpclk-2 | Tpclk | Tpclk+2          |      |

| t <sub>su(MI)</sub>                          | Data input actus time                | Master mode                                              | 0       | -     | -                |      |

| t <sub>su(SI)</sub>                          | Data input setup time                | Slave mode                                               | 3       | -     | -                |      |

| t <sub>h(MI)</sub>                           | Data input hold time                 | Master mode                                              | 11      | -     | -                |      |

| t <sub>h(SI)</sub>                           |                                      | Slave mode                                               | 4.5     | -     | -                | ns   |

| t <sub>a(SO</sub>                            | Data output access time              | Slave mode                                               | 18      | -     | 52               |      |

| t <sub>dis(SO)</sub>                         | Data output disable time             | Slave mode                                               | 12      | -     | 42               |      |

| t <sub>v(SO)</sub>                           | Data output valid time               | Slave mode                                               | -       | 20    | 56.5             |      |

| t <sub>v(MO)</sub>                           |                                      | Master mode                                              | -       | 5     | 9                |      |

| t <sub>h(SO)</sub>                           | Data output hold time                | Slave mode                                               | 13      | -     | -                |      |

| t <sub>h(MO)</sub>                           |                                      | Master mode                                              | 3       | -     | -                |      |

| Table 76. SPI characteristics in vo | oltage Range 2 <sup>(1)</sup> |

|-------------------------------------|-------------------------------|

|-------------------------------------|-------------------------------|

1. Guaranteed by characterization results.

2. The maximum SPI clock frequency in slave transmitter mode is determined by the sum of  $t_{v(SO)}$  and  $t_{su(MI)}$  which has to fit into SCK low or high phase preceding the SCK sampling edge. This value can be achieved when the SPI communicates with a master having  $t_{su(MI)} = 0$  while Duty<sub>(SCK)</sub> = 50%.

#### **I2S** characteristics

| Symbol                 | Parameter                      | Conditions                             | Min      | Max                   | Unit  |

|------------------------|--------------------------------|----------------------------------------|----------|-----------------------|-------|

| f <sub>MCK</sub>       | I2S Main clock output          | -                                      | 256 x 8K | 256xFs <sup>(2)</sup> | MHz   |

| £                      | 125 alook froguopov            | Master data: 32 bits                   | -        | 64xFs                 | MHz   |

| f <sub>СК</sub>        | I2S clock frequency            | Slave data: 32 bits                    | -        | 64xFs                 | IVITZ |

| D <sub>CK</sub>        | I2S clock frequency duty cycle | Slave receiver                         | 30       | 70                    | %     |

| t <sub>v(WS)</sub>     | WS valid time                  | Master mode                            | -        | 15                    |       |

| t <sub>h(WS)</sub>     | WS hold time                   | Master mode                            | 11       | -                     |       |

| t <sub>su(WS)</sub>    | WS setup time                  | Slave mode                             | 6        | -                     |       |

| t <sub>h(WS)</sub>     | WS hold time                   | Slave mode                             | 2        | -                     |       |

| t <sub>su(SD_MR)</sub> | Data input setup time          | Master receiver                        | 0        | -                     |       |

| t <sub>su(SD_SR)</sub> | Data input setup time          | Slave receiver                         | 6.5      | -                     | ns    |

| t <sub>h(SD_MR)</sub>  | Data input hold time           | Master receiver                        | 18       | -                     | 115   |

| t <sub>h(SD_SR)</sub>  | Data Input noid time           | Slave receiver                         | 15.5     | -                     |       |

| t <sub>v(SD_ST)</sub>  | Data output valid time         | Slave transmitter (after enable edge)  | -        | 77                    |       |

| t <sub>v(SD_MT)</sub>  |                                | Master transmitter (after enable edge) | -        | 8                     |       |

| t <sub>h(SD_ST)</sub>  | Data output hold time          | Slave transmitter (after enable edge)  | 18       | -                     |       |

| t <sub>h(SD_MT)</sub>  | Data output hold time          | Master transmitter (after enable edge) | 1.5      | -                     |       |

#### Table 78. I2S characteristics<sup>(1)</sup>

1. Guaranteed by characterization results.

2. 256xFs maximum value is equal to the maximum clock frequency.

Note: Refer to the I2S section of the product reference manual for more details about the sampling frequency (Fs),  $f_{MCK}$ ,  $f_{CK}$  and  $D_{CK}$  values. These values reflect only the digital peripheral behavior, source clock precision might slightly change them. DCK depends mainly on the ODD bit value, digital contribution leads to a min of (I2SDIV/(2\*I2SDIV+ODD) and a max of (I2SDIV+ODD)/(2\*I2SDIV+ODD). Fs max is supported for each mode/condition.

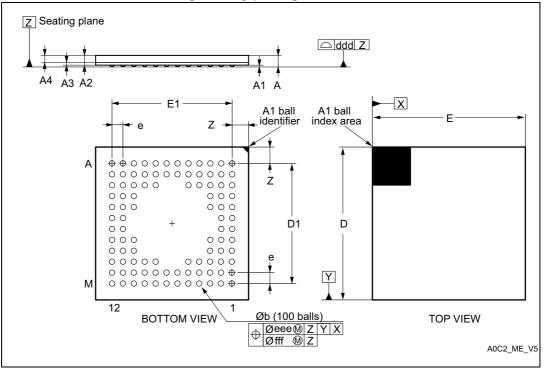

## 7.2 UFBGA100 package information

Figure 42. UFBGA100 - 100-pin, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball grid array package outline

1. Drawing is not to scale.

## Table 84. UFBGA100 - 100-pin, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball grid array package mechanical data

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

|        | Min.        | Тур.  | Max.  | Min.                  | Тур.   | Max.   |

| А      | -           | -     | 0.600 | -                     | -      | 0.0236 |

| A1     | -           | -     | 0.110 | -                     | -      | 0.0043 |

| A2     | -           | 0.450 | -     | -                     | 0.0177 | -      |

| A3     | -           | 0.130 | -     | -                     | 0.0051 | 0.0094 |

| A4     | -           | 0.320 | -     | -                     | 0.0126 | -      |

| b      | 0.240       | 0.290 | 0.340 | 0.0094                | 0.0114 | 0.0134 |

| D      | 6.850       | 7.000 | 7.150 | 0.2697                | 0.2756 | 0.2815 |

| D1     | -           | 5.500 | -     | -                     | 0.2165 | -      |

| E      | 6.850       | 7.000 | 7.150 | 0.2697                | 0.2756 | 0.2815 |

| E1     | -           | 5.500 | -     | -                     | 0.2165 | -      |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |

| Z      | -           | 0.750 | -     | -                     | 0.0295 | -      |

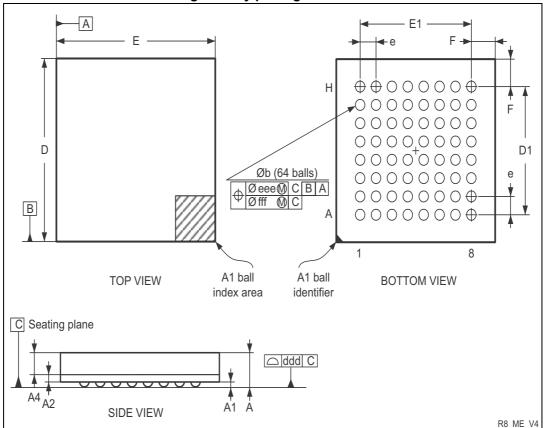

## 7.4 **TFBGA64** package information

Figure 48. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch thin profile fine pitch ball grid array package outline

1. Drawing is not to scale.

| Table 87. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ball |  |  |  |  |

|-----------------------------------------------------------------------------------|--|--|--|--|

| grid array package mechanical data                                                |  |  |  |  |

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

|        | Min         | Тур   | Мах   | Min                   | Тур    | Max    |

| А      | -           | -     | 1.200 | -                     | -      | 0.0472 |

| A1     | 0.150       | -     | -     | 0.0059                | -      | -      |

| A2     | -           | 0.200 | -     | -                     | 0.0079 | -      |

| A4     | -           | -     | 0.600 | -                     | -      | 0.0236 |

| b      | 0.250       | 0.300 | 0.350 | 0.0098                | 0.0118 | 0.0138 |

| D      | 4.850       | 5.000 | 5.150 | 0.1909                | 0.1969 | 0.2028 |

| D1     | -           | 3.500 | -     | -                     | 0.1378 | -      |

| E      | 4.850       | 5.000 | 5.150 | 0.1909                | 0.1969 | 0.2028 |

| E1     | -           | 3.500 | -     | -                     | 0.1378 | -      |

# Table 87. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ballgrid array package mechanical data (continued)

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

|        | Min         | Тур   | Мах   | Min                   | Тур    | Мах    |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |

| F      | -           | 0.750 | -     | -                     | 0.0295 | -      |

| ddd    | -           | -     | 0.080 | -                     | -      | 0.0031 |

| eee    | -           | -     | 0.150 | -                     | -      | 0.0059 |

| fff    | -           | -     | 0.050 | -                     | -      | 0.0020 |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

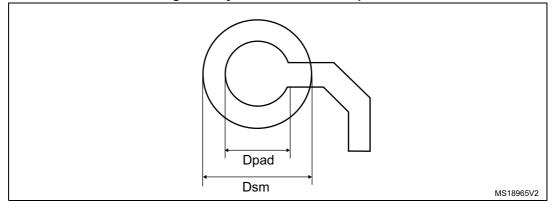

## Figure 49. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ball ,grid array recommended footprint

#### Table 88. TFBGA64 recommended PCB design rules (0.5 mm pitch BGA)

| Dimension    | Recommended values                                              |  |  |

|--------------|-----------------------------------------------------------------|--|--|

| Pitch        | 0.5                                                             |  |  |

| Dpad         | 0.27 mm                                                         |  |  |

| Dsm          | 0.35 mm typ. (depends on the soldermask registration tolerance) |  |  |

| Solder paste | 0.27 mm aperture diameter.                                      |  |  |

Note:Non solder mask defined (NSMD) pads are recommended.4 to 6 mils solder paste screen printing process.

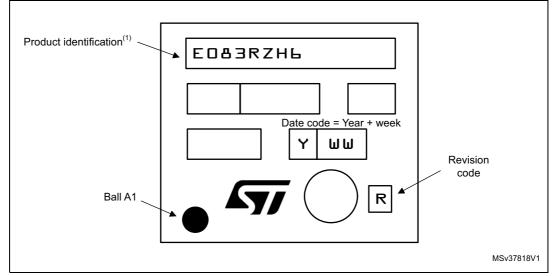

#### **Device marking for TFBGA64**

The following figure gives an example of topside marking versus ball A 1 position identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

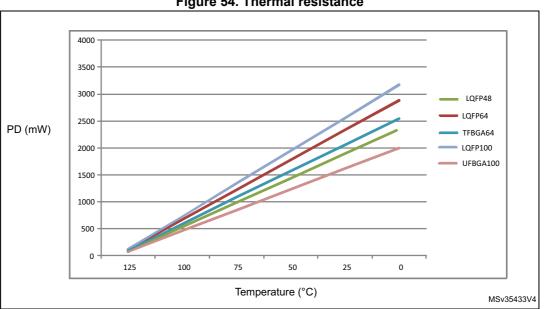

Figure 54. Thermal resistance

#### 7.6.1 **Reference document**

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org.