#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Last Time Buy                                                                  |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | M16C/60                                                                        |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 15MHz                                                                          |

| Connectivity               | I²C, SIO, UART/USART                                                           |

| Peripherals                | DMA, WDT                                                                       |

| Number of I/O              | 20                                                                             |

| Program Memory Size        | 96KB (96K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 24K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | -                                                                              |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-LQFP                                                                        |

| Supplier Device Package    | 64-LFQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/m306s0fagp-u3 |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Pin Configuration

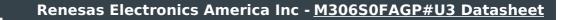

Figures 1.1.4 show the pin configurations (top view).

Figure 1.1.4. Pin Configuration (Top View)

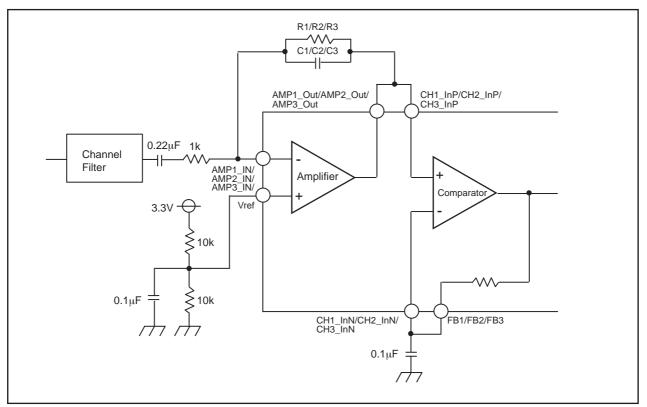

| Pin name | I/O type | Function                                                                         |

|----------|----------|----------------------------------------------------------------------------------|

| PRE-BOUT | Output   | This is a pre-amp buffer output.                                                 |

| PRE-INN  | Input    | This is a pre-amp differential signal input.                                     |

| PRE-INP  | Input    | This is a pre-amp differential signal input.                                     |

| VREF     | Input    | This is the reference voltage input of amplifier common to channels 1, 2, and 3. |

| VDCCN    | Input    | This is a pin for a test. Usually, please carry out a pull-up.                   |

| AMP1-IN  | Input    | This is a channel 1 amplifier input.                                             |

| AMP1-OUT | Output   | This is a channel 1 amplifier output.                                            |

| AMP2-IN  | Input    | This is a channel 2 amplifier input.                                             |

| AMP2-OUT | Output   | This is a channel 2 amplifier output.                                            |

| AMP3-IN  | Input    | This is a channel 3 amplifier input.                                             |

| AMP3-OUT | Output   | This is a channel 3 amplifier output.                                            |

| CHI-INP  | Input    | This is a channel 1 comparator differential input.                               |

| CHI-INN  | Input    | This is a channel 1 comparator differential input.                               |

| FB1      | Output   | This is a channel 1 comparator feedback output.                                  |

| CH2-INP  | Input    | This is a channel 2 comparator differential input.                               |

| CH2-INN  | Input    | This is a channel 2 comparator differential input.                               |

| FB2      | Output   | This is a channel 2 comparator feedback output.                                  |

| CH3-INP  | Input    | This is a channel 3 comparator differential input.                               |

| CH3-INN  | Input    | This is a channel 3 comparator differential input.                               |

| FB3      | Output   | This is a channel 3 comparator feedback output.                                  |

| IOUTC    | Output   | This is the differential current output of DAC.                                  |

| IOUT     | Output   | This is the differential current output of DAC.                                  |

| REXT     | Input    | This is for external reference resistor of DAC.                                  |

| IFLT     | Input    | This is the pin for low path filters of PLL.                                     |

### Table 1.1.8 Pin Description (2) (Analog pin)

| Address           | Dogistor                                  | Symbol | After recet  |

|-------------------|-------------------------------------------|--------|--------------|

| Address<br>008016 | Register                                  | Symbol | After reset  |

| 008016            |                                           |        |              |

| 008116            |                                           |        |              |

| 008316            |                                           |        |              |

| 008416            |                                           |        |              |

| 008516            |                                           |        |              |

| 008616            |                                           |        |              |

|                   |                                           |        |              |

| ≈                 |                                           |        | ≈            |

| 01B016            |                                           |        |              |

| 01B116            |                                           |        |              |

| 01B216            |                                           |        |              |

| 01B316            |                                           |        |              |

| 01B416            |                                           |        |              |

| 01B516            | Flash memory control register 1           | FMR1   | 0?00??0?2    |

| 01B616            | Electronic control as also a              |        | 00000001-    |

| 01B716            | Flash memory control register 0           | FMR0   | ??0000012    |

| 01B816            | Address match interrupt register 2        | RMAD2  | 0016         |

| 01B916            |                                           |        | 0016         |

| 01BA16            | Address motob interrupt anoble register 0 |        | X016         |

| 01BB16<br>01BC16  | Address match interrupt enable register 2 | AIER2  | XXXXXX002    |

| 01BC16<br>01BD16  | Address match interrupt register 3        | RMAD3  | 0016         |

| 01BD16<br>01BE16  |                                           |        | 0016<br>X016 |

| 01BE16            |                                           |        | Λυιο         |

| 5.5110            |                                           |        |              |

| ≈                 |                                           |        | ~            |

| ĩ                 |                                           |        | ~            |

| 025016            |                                           |        |              |

| 025116            |                                           |        |              |

| 025216            |                                           |        |              |

| 025316            |                                           |        |              |

| 025416            |                                           |        |              |

| 025516            |                                           |        |              |

| 025616            |                                           |        |              |

| 025716            |                                           |        |              |

| 025816            |                                           |        |              |

| 025916            |                                           |        |              |

| 025A16            |                                           |        |              |

| 025B16            |                                           |        |              |

| 025C16            |                                           |        |              |

| 025D16            |                                           |        |              |

| 025E16            | Peripheral clock select register          | PCLKR  | 000000112    |

| 025F16            |                                           |        |              |

| ≈                 |                                           |        | ~            |

|                   |                                           |        | ~            |

| 033016            |                                           |        |              |

| 033016            |                                           |        |              |

| 033116            |                                           |        |              |

| 033316            |                                           |        |              |

| 033416            |                                           |        |              |

| 033516            |                                           |        |              |

| 033616            |                                           |        |              |

| 033716            |                                           |        |              |

| 033816            |                                           |        |              |

| 033916            |                                           |        |              |

| 033A16            |                                           |        |              |

| 033B16            |                                           |        |              |

| 033C16            |                                           |        |              |

| 033D16            |                                           |        |              |

| 033E16            |                                           |        |              |

| 033F16            |                                           |        |              |

|                   |                                           |        |              |

Note 1: The blank areas are reserved and cannot be used by users.

X : Nothing is mapped to this bit ? : Undefined

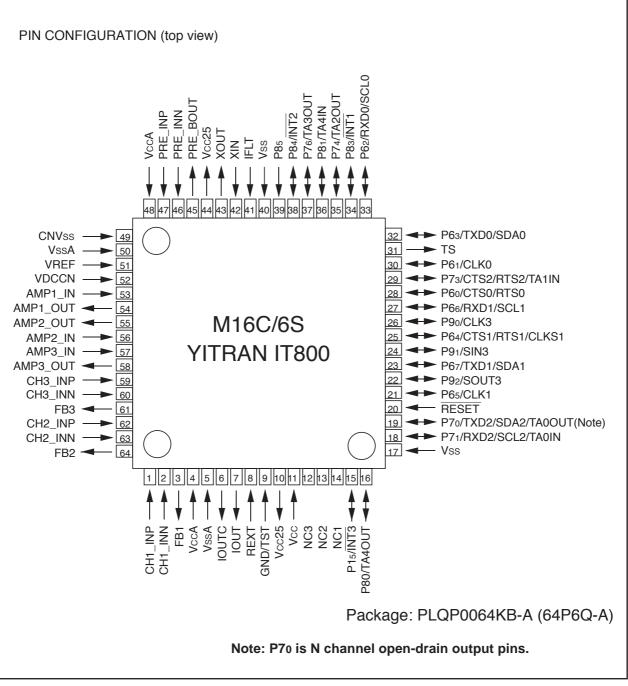

### (2) Setting PLC Mode

PLC mode is simply set by putting P15 High level during RESET.

Figure 1.6.1. PLC mode by P15 simply setting

|    |      | 10 1110 |     |

|----|------|---------|-----|

|    | min  | typ     | max |

| TR | 40us |         |     |

|    |      |         |     |

5us

5us

#### Table 1.6.3. RESET and P15 Input

Tset up

THOLD

#### Table 1.7.3. Pin Status During Wait Mode

| Pin       | Status                          |  |  |

|-----------|---------------------------------|--|--|

| I/O ports | Retains status before wait mode |  |  |

#### Table 1.7.4. Interrupts to Exit Wait Mode

| Interrupt            | CM02=0                                                     | CM02=1                                         |

|----------------------|------------------------------------------------------------|------------------------------------------------|

| Serial I/O interrupt | Can be used when operating with internal or external clock | Can be used when operating with external clock |

| Timer A interrupt    | Can be used in all modes                                   | Can be used in event counter mode              |

| INT interrupt        | Can be used                                                | Can be used                                    |

If the microcomputer is to be moved out of wait mode by a peripheral function interrupt, set up the following before executing the WAIT instruction.

In the ILVL2 to ILVL0 bits of interrupt control register, set the interrupt priority level of the periph eral function interrupt to be used to exit wait mode.

Also, for all of the peripheral function interrupts not used to exit wait mode, set the ILVL2 to ILVL0

bits to "0002" (interrupt disable).

- 2. Set the I flag to "1".

- 3. Enable the peripheral function whose interrupt is to be used to exit wait mode.

In this case, when an interrupt request is generated and the CPU clock is thereby turned on, an interrupt routine is executed.

The CPU clock turned on when exiting wait mode by a peripheral function interrupt is the same CPU clock that was on when the WAIT instruction was executed.

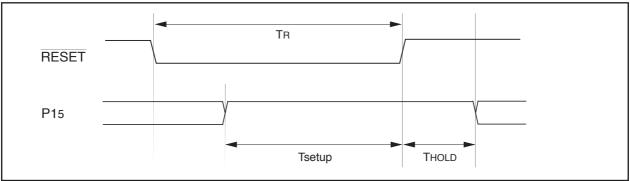

Figure 1.7.7 shows the state transition from normal operation mode to stop mode and wait mode.

Figure 1.7.7. State Transition to Stop Mode and Wait Mode

#### Interrupts and Interrupt Vector

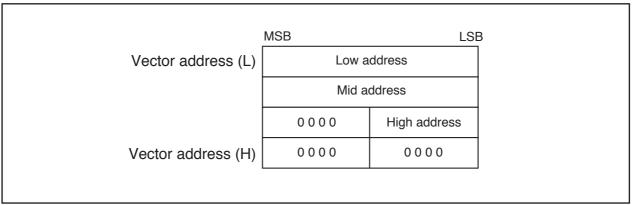

One interrupt vector consists of 4 bytes. Set the start address of each interrupt routine in the respective interrupt vectors. When an interrupt request is accepted, the CPU branches to the address set in the corresponding interrupt vector. Figure 1.9.2 shows the interrupt vector.

Figure 1.9.2. Interrupt Vector

#### • Fixed Vector Tables

The fixed vector tables are allocated to the addresses from FFFDC16 to FFFFF16. Table 1.9.1 lists the fixed vector tables. In the flash memory version of microcomputer, the vector addresses (H) of fixed vectors are used by the ID code check function. For details, refer to the section "flash memory rewrite disabling function".

Table 1.9.1. Fixed Vector Tables

| Interrupt source                       | Vector table addresses     | Remarks                                                                                                                                                  | Reference                |

|----------------------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

|                                        | Address (L) to address (H) |                                                                                                                                                          |                          |

| Undefined instruction                  | FFFDC16 to FFFDF16         | Interrupt on UND instruction                                                                                                                             | M16C/60, M16C/20         |

| Overflow                               | FFFE016 to FFFE316         | Interrupt on INTO instruction                                                                                                                            | series software          |

| BRK instruction                        | FFFE416 to FFFE716         | If the contents of address<br>FFFE716 is FF16, program ex-<br>ecution starts from the address<br>shown by the vector in the<br>relocatable vector table. | manual                   |

| Address match                          | FFFE816 to FFFEB16         |                                                                                                                                                          | Address match interrupt  |

| Single step (Note)                     | FFFEC16 to FFFEF16         |                                                                                                                                                          |                          |

| Watchdog timer<br>Oscillation stop and | FFFF016 to FFFF316         |                                                                                                                                                          | Watchdog timer           |

| re-oscillation detection               |                            |                                                                                                                                                          | Clock generating circuit |

| DBC (Note)                             | FFFF416 to FFFF716         |                                                                                                                                                          |                          |

| (Reserved)                             | FFFF816 to FFFFB16         |                                                                                                                                                          |                          |

| Reset                                  | FFFFC16 to FFFFF16         |                                                                                                                                                          | Reset                    |

Note: Do not normally use this interrupt because it is provided exclusively for use by development support tools.

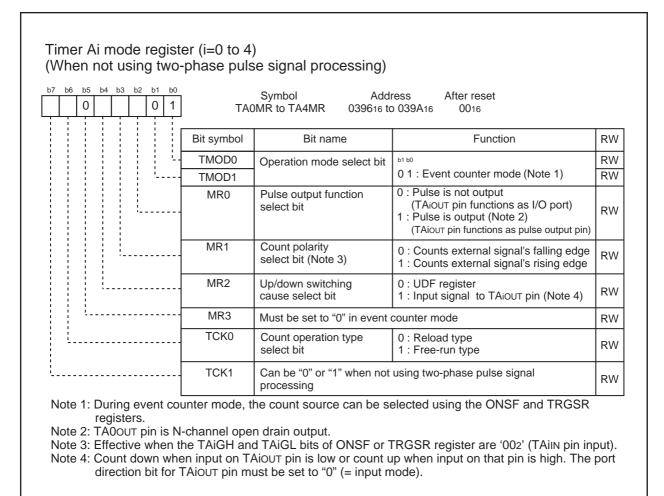

Figure 1.12.7. TAiMR Register in Event Counter Mode (when not using two-phase pulse signal processing)

#### **Counter Measure for Communication Error Occurs**

If a communication error occurs while transmitting or receiving in clock synchronous serial I/O mode, follow the procedures below.

- Resetting the UiRB register (i=0 to 2)

- (1) Set the RE bit in the UiC1 register to "0" (reception disabled)

- (2) Set the SMD2 to SMD0 bits in the UiMR register to "000b" (Serial I/O disabled)

- (3) Set the SMD2 to SMD0 bits in the UiMR register to "001b" (Clock synchronous serial I/O mode)

- (4) Set the RE bit in the UiC1 register to "1" (reception enabled)

• Resetting the UiTB register (i=0 to 2)

- (1) Set the SMD2 to SMD0 bits in the UiMR register "000b" (Serial I/O disabled)

- (2) Set the SMD2 to SMD0 bits in the UiMR register "001b" (Clock synchronous serial I/O mode)

- (3) "1" is written to RE bit in the UiC1 register (reception enabled), regardless of the TE bit in the UiCi register

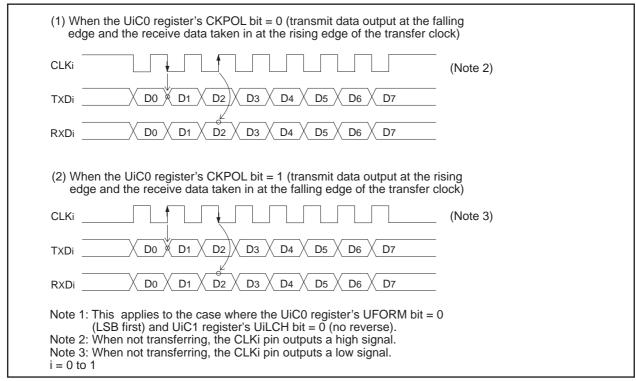

#### (a) CLK Polarity Select Function

Use the UiC0 register (i = 0 to 1)'s CKPOL bit to select the transfer clock polarity. Figure 1.14.2 shows the polarity of the transfer clock.

Figure 1.14.2. Transfer Clock Polarity

Table 1.15.3 lists the functions of the input/output pins during UART mode. Table 1.15.4 lists the P64 pin functions during UART mode. Note that for a period from when the UARTi operation mode is selected to when transfer starts, the TxDi pin outputs an "H". (If the N-channel open-drain output is selected, this pin is in a high-impedance state.)

| Pin name                                 | Function             | Method of selection                                                                                                                  |  |

|------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|

| TxDi (i = 0 to 2)<br>(P63, P67, P70)     | Serial data output   | (Outputs dummy data when performing reception only)                                                                                  |  |

| RxDi<br>(P62, P66, P71)                  | Serial data input    | PD6 register's PD6_2 bit=0, PD6_6 bit=0, PD7 register's PD7_1 bit=0 (Can be used as an input port when performing transmission only) |  |

| CLKi                                     | Input/output port    | UiMR register's CKDIR bit=0                                                                                                          |  |

| (P61, P65)                               | Transfer clock input | UiMR register's CKDIR bit=1<br>PD6 register's PD6_1 bit=0, PD6_5 bit=0, PD7 register's PD7_2 bit=0                                   |  |

| (P60, P64, P73) UiC0 register's CRS bit= |                      | UiC0 register's CRD bit=0<br>UiC0 register's CRS bit=0<br>PD6 register's PD6_0 bit=0, PD6_4 bit=0, PD7 register's PD7_3 bit=0        |  |

|                                          | RTS output           | UiC0 register's CRD bit=0<br>UiC0 register's CRS bit=1                                                                               |  |

|                                          | Input/output port    | UiC0 register's CRD bit=1                                                                                                            |  |

Table 1.15.3. I/O Pin Functions

Table 1.15.4. P64 Pin Functions

| Pin function            | Bit set value |     |               |        |                     |  |

|-------------------------|---------------|-----|---------------|--------|---------------------|--|

|                         | U1C0 register |     | UCON register |        | PD6 register        |  |

|                         | CRD           | CRS | RCSP          | CLKMD1 | PD6_4               |  |

| P64                     | 1             |     | 0             | 0      | Input: 0, Output: 1 |  |

| CTS1                    | 0             | 0   | 0             | 0      | 0                   |  |

| RTS1                    | 0             | 1   | 0             | 0      |                     |  |

| CTS <sub>0</sub> (Note) | 0             | 0   | 1             | 0      | 0                   |  |

Note: In addition to this, set the U0C0 register's CRD bit to "0" (CTS0/RTS0 enabled) and the U0C0 register's CRS bit to "1" (RTS0 selected).

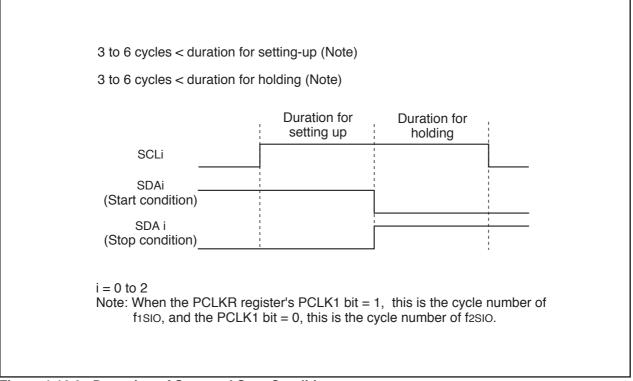

#### • Detection of Start and Stop Condition

Whether a start or a stop condition has been detected is determined.

A start condition-detected interrupt request is generated when the SDAi pin changes state from high to low while the SCLi pin is in the high state. A stop condition-detected interrupt request is generated when the SDAi pin changes state from low to high while the SCLi pin is in the high state.

Because the start and stop condition-detected interrupts share the interrupt control register and vector, check the UiSMR register's BBS bit to determine which interrupt source is requesting the interrupt.

Figure 1.16.3. Detection of Start and Stop Condition

#### • Output of Start and Stop Condition

A start condition is generated by setting the STAREQ bit in the UiSMR4 register (i = 0 to 2) to "1" (start).

A restart condition is generated by setting the RSTAREQ bit in the UiSMR4 register to "1" (start). A stop condition is generated by setting the STPREQ bit in the UiSMR4 register to "1" (start).

The output procedure is described below.

(1) Set the STAREQ bit, RSTAREQ bit or STPREQ bit to "1" (start).

(2) Set the STSPSEL bit in the UiSMR4 register to "1" (output).

The function of the STSPSEL bit is shown in Table 1.16.5 and Figure 1.16.4.

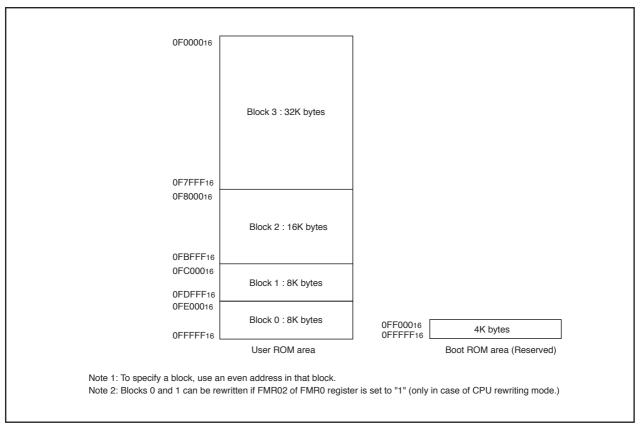

|                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Symbol<br>PUR0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Address<br>03FC16                                                                                                                                                                                                                                                       | After reset<br>0016                                                                                                                                                                                                                          |                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

|                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Bit symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Bit name                                                                                                                                                                                                                                                                | Function                                                                                                                                                                                                                                     | R                       |

|                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | (b2-b0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Nothing is assigned. When When read, its content is inde                                                                                                                                                                                                                |                                                                                                                                                                                                                                              | -                       |

|                                                                                                                                                                                   | !                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PU03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | P14 to P17 pull-up                                                                                                                                                                                                                                                      | 0 : Not pulled high<br>1 : Pulled high (Note 2)                                                                                                                                                                                              | R١                      |

|                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | (b7-b4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Nothing is assigned. When When read, its content is inde                                                                                                                                                                                                                |                                                                                                                                                                                                                                              | -                       |

|                                                                                                                                                                                   | in for which                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | his bit is "1" (pu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | an be modified.<br>Illed high) and the direction b                                                                                                                                                                                                                      | it is "0" (input mode) is pulled high.                                                                                                                                                                                                       |                         |

| •                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Symbol<br>PUR1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Address<br>03FD16                                                                                                                                                                                                                                                       | After reset(Note 5)<br>00000002<br>000000102                                                                                                                                                                                                 |                         |

|                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Bit symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Bit name                                                                                                                                                                                                                                                                | Function                                                                                                                                                                                                                                     | R١                      |

|                                                                                                                                                                                   | i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (b3-b0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Nothing is assigned. When When read, its content is inde                                                                                                                                                                                                                |                                                                                                                                                                                                                                              |                         |