#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Active                                                                       |

|---------------------------------|------------------------------------------------------------------------------|

| Core Processor                  | ARM926EJ-S                                                                   |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                               |

| Speed                           | 400MHz                                                                       |

| Co-Processors/DSP               | -                                                                            |

| RAM Controllers                 | DDR2, SDRAM, SRAM                                                            |

| Graphics Acceleration           | No                                                                           |

| Display & Interface Controllers | -                                                                            |

| Ethernet                        | 10/100Mbps                                                                   |

| SATA                            | -                                                                            |

| USB                             | USB 2.0 (3)                                                                  |

| Voltage - I/O                   | 1.8V, 3.3V                                                                   |

| Operating Temperature           | -40°C ~ 85°C (TA)                                                            |

| Security Features               | -                                                                            |

| Package / Case                  | 217-LFBGA                                                                    |

| Supplier Device Package         | 217-LFBGA (15x15)                                                            |

| Purchase URL                    | https://www.e-xfl.com/product-detail/microchip-technology/at91sam9g25-cu-999 |

|                                 |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Mode commands:

- Normal mode configures SAM-BA Monitor to send / receive data in binary format,

- Terminal mode configures SAM-BA Monitor to send / receive data in ascii format.

- Write commands: Write a byte (**O**), a halfword (**H**) or a word (**W**) to the target.

- Address: Address in hexadecimal.

- *Value*: Byte, halfword or word to write in hexadecimal.

- Output: '>'

- Read commands: Read a byte (o), a halfword (h) or a word (w) from the target.

- Address: Address in hexadecimal.

- Output: The byte, halfword or word read in hexadecimal followed by '>'

- Send a file (S): Send a file to a specified address.

- *Address*: Address in hexadecimal.

- Output: '>'

- Note: There is a time-out on this command which is reached when the prompt '>' appears before the end of the command execution.

- Receive a file (R): Receive data into a file from a specified address

- *Address*: Address in hexadecimal.

- *NbOfBytes*: Number of bytes in hexadecimal to receive.

- Output: '>'

- Go (G): Jump to a specified address and execute the code.

- Address: Address to jump in hexadecimal.

- Output: '>'once returned from the program execution. If the executed program does not handle the link

register at its entry and does not return, the prompt will not be displayed.

- Get Version (V): Return the Boot Program version.

- Output: version, date and time of ROM code followed by '>'.

# 10.5.2 DBGU Serial Port

Communication is performed through the DBGU serial port initialized to 115,200 baud, 8 bits of data, no parity, 1 stop bit.

# 10.5.2.1 Supported External Crystal/External Clocks

The SAM-BA monitor supports a frequency of 12 MHz to allow DBGU communication for both external crystal and external clock.

# 10.5.2.2 Xmodem Protocol

The Send and Receive File commands use the Xmodem protocol to communicate. Any terminal performing this protocol can be used to send the application file to the target. The size of the binary file to send depends on the SRAM size embedded in the product. In all cases, the size of the binary file must be lower than the SRAM size because the Xmodem protocol requires some SRAM memory in order to work.

The Xmodem protocol supported is the 128-byte length block. This protocol uses a two-character CRC16 to guarantee detection of a maximum bit error.

# 12.9.2 AIC Source Vector Register

| Name:<br>Address: | AIC_SVR0AIC_<br>0xFFFFF080 | _SVR31 |     |     |    |    |    |

|-------------------|----------------------------|--------|-----|-----|----|----|----|

| Access:           | Read/Write                 |        |     |     |    |    |    |

| Reset:            | 0x0                        |        |     |     |    |    |    |

| 31                | 30                         | 29     | 28  | 27  | 26 | 25 | 24 |

|                   |                            |        | VEC | TOR |    |    |    |

| 23                | 22                         | 21     | 20  | 19  | 18 | 17 | 16 |

|                   |                            |        | VEC | TOR |    |    |    |

| 15                | 14                         | 13     | 12  | 11  | 10 | 9  | 8  |

|                   | VECTOR                     |        |     |     |    |    |    |

| 7                 | 6                          | 5      | 4   | 3   | 2  | 1  | 0  |

|                   |                            |        | VEC | TOR |    |    |    |

This register can only be written if the WPEN bit is cleared in the AIC Write Protection Mode Register.

# • VECTOR: Source Vector

The user may store in these registers the addresses of the corresponding handler for each interrupt source.

### 14.6.4 RTC Calendar Register

| Name:    | RTC_CALR   |    |    |      |       |    |    |

|----------|------------|----|----|------|-------|----|----|

| Address: | 0xFFFFFEBC |    |    |      |       |    |    |

| Access:  | Read/Write |    |    |      |       |    |    |

| 31       | 30         | 29 | 28 | 27   | 26    | 25 | 24 |

| -        | -          |    |    | DA   | ATE   |    |    |

| 23       | 22         | 21 | 20 | 19   | 18    | 17 | 16 |

|          | DAY        |    |    |      | MONTH |    |    |

| 15       | 14         | 13 | 12 | 11   | 10    | 9  | 8  |

|          |            |    | YE | AR   |       |    |    |

| 7        | 6          | 5  | 4  | 3    | 2     | 1  | 0  |

| _        |            |    |    | CENT |       |    |    |

### • CENT: Current Century

Only the BCD value 20 can be configured.

The lowest four bits encode the units. The higher bits encode the tens.

### • YEAR: Current Year

The range that can be set is 00–99 (BCD).

The lowest four bits encode the units. The higher bits encode the tens.

### • MONTH: Current Month

The range that can be set is 01–12 (BCD).

The lowest four bits encode the units. The higher bits encode the tens.

# • DAY: Current Day in Current Week

The range that can be set is 1–7 (BCD).

The coding of the number (which number represents which day) is user-defined as it has no effect on the date counter.

# • DATE: Current Day in Current Month

The range that can be set is 01–31 (BCD).

The lowest four bits encode the units. The higher bits encode the tens.

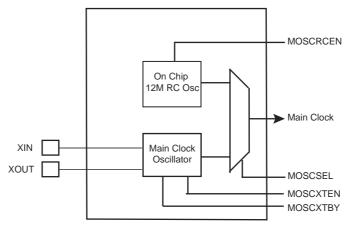

### 20.5.2 12 to 16 MHz Crystal Oscillator

After reset, the 12 to 16 MHz crystal oscillator is disabled and is not selected as the source of MAINCK.

As the source of MAINCK, the 12 to 16 MHz crystal oscillator provides an accurate frequency. The software enables or disables this oscillator in order to reduce power consumption via CKGR\_MOR.MOSCXTEN.

When disabling this oscillator by clearing the CKGR\_MOR.MOSCXTEN bit, the PMC\_SR.MOSCXTS bit is automatically cleared, indicating the 12 to 16 MHz crystal oscillator is off.

When enabling this oscillator, the user must initiate the startup time counter. This startup time depends on the characteristics of the external device connected to this oscillator. Refer to the section "Electrical Characteristics" for the startup time.

When CKGR\_MOR.MOSCXTEN and CKGR\_MOR.MOSCXTST are written to enable this oscillator, the PMC\_SR.MOSCXTS bit is cleared and the counter starts counting down on the slow clock divided by 8 from the MOSCXTST value. When the counter reaches 0, the PMC\_SR.MOSCXTS is set, indicating that the 12 to 16 MHz crystal oscillator is stabilized. Setting PMC\_IMR.MOSCXTS triggers an interrupt to the processor.

### 20.5.3 Main Clock Source Selection

The main clock is generated by the 12 to 16 MHz crystal oscillator, or by the embedded 12 MHz RC oscillator.

The selection is made by writing CKGR\_MOR.MOSCSEL. The switch of the main clock source is glitch-free, so there is no need to run out of SLCK or PLLACK in order to change the selection. PMC\_SR.MOSCSELS indicates when the switch sequence is done.

Setting PMC\_IMR.MOSCSELS triggers an interrupt to the processor.

The 12 to 16 MHz crystal oscillator can be bypassed by setting the MOSCXTBY bit in the CKGR\_MOR to accept an external main clock on XIN (refer to Section 20.5.4 "Bypassing the 12 to 16 MHz Crystal Oscillator").

### Figure 20-4. Main Clock Source Selection

MOSCRCEN, MOSCXTEN, MOSCSEL and MOSCXTBY bits are located in the PMC Clock Generator Main Oscillator Register (CKGR\_MOR).

After a VDDBU power-on reset, the default configuration is MOSCRCEN = 1, MOSCXTEN = 0 and MOSCSEL = 0, allowing the 12 MHz RC oscillator to start as Main clock.

# Atmel

# 21.16.10 PMC Clock Generator PLLA Register

| Name:    | CKGR_PLLAR |           |         |         |    |    |    |

|----------|------------|-----------|---------|---------|----|----|----|

| Address: | 0xFFFFFC28 |           |         |         |    |    |    |

| Access:  | Read/Write |           |         |         |    |    |    |

| 31       | 30         | 29        | 28      | 27      | 26 | 25 | 24 |

| -        | -          | ONE       | -       | -       | -  | _  | -  |

| 23       | 22         | 21        | 20      | 19      | 18 | 17 | 16 |

|          |            |           | MU      | JLA     |    |    |    |

| 15       | 14         | 13        | 12      | 11      | 10 | 9  | 8  |

|          | OUTA       | PLLACOUNT |         |         |    |    |    |

| 7        | 6          | 5         | 4<br>DI | 3<br>VA | 2  | 1  | 0  |

This register can only be written if the WPEN bit is cleared in the PMC Write Protection Mode Register.

Possible limitations on PLL input frequencies and multiplier factors should be checked before using the PMC.

### • DIVA: Divider A

| Value | Name   | Description                                           |

|-------|--------|-------------------------------------------------------|

| 0     | 0      | Divider output is 0                                   |

| 1     | BYPASS | Divider is bypassed                                   |

| 2–255 | -      | Divider output is the selected clock divided by DIVA. |

# PLLACOUNT: PLLA Counter

Specifies the number of slow clock cycles before the LOCKA bit is set in PMC\_SR after CKGR\_PLLAR is written.

### OUTA: PLLA Clock Frequency Range

To optimize clock performance, this field must be programmed as specified in "PLL Characteristics" in the Electrical Characteristics section of the product datasheet.

### • MULA: PLLA Multiplier

0: The PLLA is deactivated.

1–254: The PLLA Clock frequency is the PLLA input frequency multiplied by MULA + 1.

### • ONE: Must Be Set to 1

Bit 29 must always be set to 1 when programming the CKGR\_PLLAR.

### 22.5.15 Register Write Protection

To prevent any single software error from corrupting PIO behavior, certain registers in the address space can be write-protected by setting the WPEN bit in the PIO Write Protection Mode Register (PIO\_WPMR).

If a write access to a write-protected register is detected, the WPVS flag in the PIO Write Protection Status Register (PIO\_WPSR) is set and the field WPVSRC indicates the register in which the write access has been attempted.

The WPVS bit is automatically cleared after reading the PIO\_WPSR.

The following registers can be write-protected:

- PIO Enable Register

- PIO Disable Register

- PIO Output Enable Register

- PIO Output Disable Register

- PIO Input Filter Enable Register

- PIO Input Filter Disable Register

- PIO Multi-driver Enable Register

- PIO Multi-driver Disable Register

- PIO Pull-Up Disable Register

- PIO Pull-Up Enable Register

- PIO Peripheral ABCD Select Register 1

- PIO Peripheral ABCD Select Register 2

- PIO Output Write Enable Register

- PIO Output Write Disable Register

- PIO Pad Pull-Down Disable Register

- PIO Pad Pull-Down Enable Register

# 27.5.4 Error Location Disable Register

| Name:    | PMERRLOC_ELDIS |    |    |    |    |    |     |  |

|----------|----------------|----|----|----|----|----|-----|--|

| Address: | 0xFFFFE60C     |    |    |    |    |    |     |  |

| Access:  | Read-write     |    |    |    |    |    |     |  |

| Reset:   | 0x00000000     |    |    |    |    |    |     |  |

| 31       | 30             | 29 | 28 | 27 | 26 | 25 | 24  |  |

| -        | -              | -  | -  | -  | -  | _  | -   |  |

| 23       | 22             | 21 | 20 | 19 | 18 | 17 | 16  |  |

| -        | -              | -  | _  | -  | —  | _  | -   |  |

| 15       | 14             | 13 | 12 | 11 | 10 | 9  | 8   |  |

| -        | -              | -  | -  | -  | -  | _  | -   |  |

| 7        | 6              | 5  | 4  | 3  | 2  | 1  | 0   |  |

| _        | -              | —  | _  | —  | -  | _  | DIS |  |

• DIS: Disable Error Location Engine

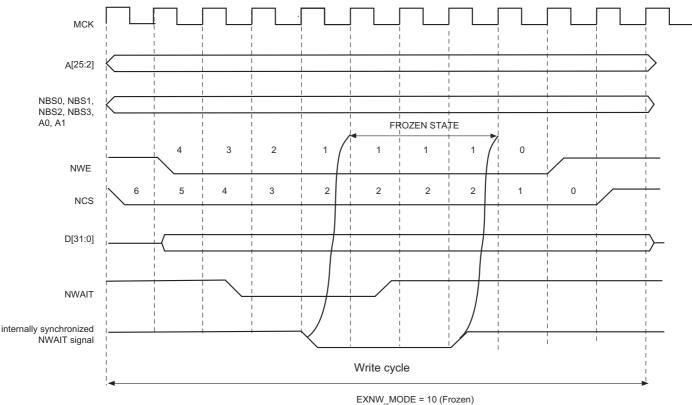

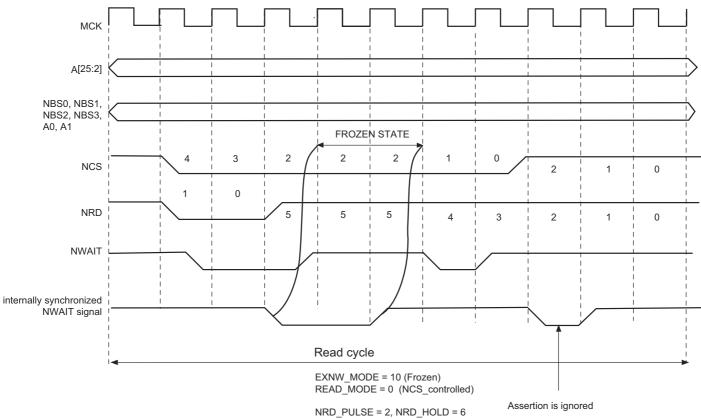

### 28.12.2 Frozen Mode

When the external device asserts the NWAIT signal (active low), and after internal synchronization of this signal, the SMC state is frozen, i.e., SMC internal counters are frozen, and all control signals remain unchanged. When the resynchronized NWAIT signal is deasserted, the SMC completes the access, resuming the access from the point where it was stopped. See Figure 28-26. This mode must be selected when the external device uses the NWAIT signal to delay the access and to freeze the SMC.

The assertion of the NWAIT signal outside the expected period is ignored as illustrated in Figure 28-27.

Figure 28-26. Write Access with NWAIT Assertion in Frozen Mode (EXNW\_MODE = 10)

EXNW\_MODE = 10 (Frozen) WRITE\_MODE = 1 (NWE\_controlled)

NWE\_PULSE = 5 NCS\_WR\_PULSE = 7

NRD\_PULSE = 2, NRD\_HOLD = 6 NCS\_RD\_PULSE =5, NCS\_RD\_HOLD =3

414 SAM9G25 [DATASHEET] Atmel-11032G-ATARM-SAM9G25-Datasheet\_31-Aug-15

Atmel

# 30.8.21 DMAC Write Protection Mode Register

| Name:    | DMAC_WPMR     |              |       |     |    |    |      |

|----------|---------------|--------------|-------|-----|----|----|------|

| Address: | 0xFFFFEDE4 (0 | ), 0xFFFFEFE | 4 (1) |     |    |    |      |

| Access:  | Read/Write    |              |       |     |    |    |      |

| 31       | 30            | 29           | 28    | 27  | 26 | 25 | 24   |

|          |               |              | WP    | KEY |    |    |      |

| 23       | 22            | 21           | 20    | 19  | 18 | 17 | 16   |

|          |               |              | WP    | KEY |    |    |      |

| 15       | 14            | 13           | 12    | 11  | 10 | 9  | 8    |

|          |               |              | WP    | KEY |    |    |      |

| 7        | 6             | 5            | 4     | 3   | 2  | 1  | 0    |

| _        | _             | _            | _     | _   | _  | _  | WPEN |

# • WPEN: Write Protection Enable

0: Disables the Write Protection if WPKEY corresponds to 0x444D41 ("DMA" in ASCII).

1: Enables the Write Protection if WPKEY corresponds to 0x444D41 ("DMA" in ASCII).

See Section 30.6.7 "Register Write Protection" for the list of registers that can be write-protected.

### • WPKEY: Write Protection Key

| Value    | Name   | Description                                                                       |

|----------|--------|-----------------------------------------------------------------------------------|

| 0x444D41 | PASSWD | Writing any other value in this field aborts the write operation of the WPEN bit. |

| 08444041 | PASSWD | Always reads as 0.                                                                |

# 31.7.17 UDPHS Endpoint Clear Status Register (Control, Bulk, Interrupt Endpoints)

Name: UDPHS\_EPTCLRSTAx [x=0..6]

Address: 0xF803C118 [0], 0xF803C138 [1], 0xF803C158 [2], 0xF803C178 [3], 0xF803C198 [4], 0xF803C1B8 [5], 0xF803C1D8 [6]

# Access: Write-only

| 31      | 30       | 29        | 28       | 27 | 26        | 25         | 24 |

|---------|----------|-----------|----------|----|-----------|------------|----|

| -       | -        | —         | _        | -  | -         | —          | _  |

| 23      | 22       | 21        | 20       | 19 | 18        | 17         | 16 |

| -       | -        | -         | -        | -  | -         | -          | -  |

| 15      | 14       | 13        | 12       | 11 | 10        | 9          | 8  |

| NAK_OUT | NAK_IN   | STALL_SNT | RX_SETUP | -  | TX_COMPLT | RXRDY_TXKL | -  |

| 7       | 6        | 5         | 4        | 3  | 2         | 1          | 0  |

| -       | TOGGLESQ | FRCESTALL | _        | _  | _         | -          | _  |

This register view is relevant only if EPT\_TYPE = 0x0, 0x2 or 0x3 in "UDPHS Endpoint Configuration Register" .

For additional information, see "UDPHS Endpoint Status Register (Control, Bulk, Interrupt Endpoints)" .

# • FRCESTALL: Stall Handshake Request Clear

0: No effect.

1: Clear the STALL request. The next packets from host will not be STALLed.

# • TOGGLESQ: Data Toggle Clear

0: No effect.

1: Clear the PID data of the current bank

For OUT endpoints, the next received packet should be a DATA0.

For IN endpoints, the next packet will be sent with a DATA0 PID.

# • RXRDY\_TXKL: Received OUT Data Clear

0: No effect.

1: Clear the RXRDY\_TXKL flag of UDPHS\_EPTSTAx.

# • TX\_COMPLT: Transmitted IN Data Complete Clear

0: No effect.

1: Clear the TX\_COMPLT flag of UDPHS\_EPTSTAx.

# • RX\_SETUP: Received SETUP Clear

0: No effect.

1: Clear the RX\_SETUP flags of UDPHS\_EPTSTAx.

# STALL\_SNT: Stall Sent Clear

0: No effect.

1: Clear the STALL\_SNT flags of UDPHS\_EPTSTAx.

### 33.8.2 Data Transfer Operation

The High Speed MultiMedia Card allows several read/write operations (single block, multiple blocks, stream, etc.). These kinds of transfer can be selected setting the Transfer Type (TRTYP) field in the HSMCI Command Register (HSMCI\_CMDR).

These operations can be done using the features of the DMA Controller.

In all cases, the block length (BLKLEN field) must be defined either in the HSMCI Mode Register (HSMCI\_MR) or in the HSMCI Block Register (HSMCI\_BLKR). This field determines the size of the data block.

Consequent to MMC Specification 3.1, two types of multiple block read (or write) transactions are defined (the host can use either one at any time):

• Open-ended/Infinite Multiple block read (or write):

The number of blocks for the read (or write) multiple block operation is not defined. The card will continuously transfer (or program) data blocks until a stop transmission command is received.

• Multiple block read (or write) with predefined block count (since version 3.1 and higher):

The card will transfer (or program) the requested number of data blocks and terminate the transaction. The stop command is not required at the end of this type of multiple block read (or write), unless terminated with an error. In order to start a multiple block read (or write) with predefined block count, the host must correctly program the HSMCI Block Register (HSMCI\_BLKR). Otherwise the card will start an open-ended multiple block read. The BCNT field of the HSMCI\_BLKR defines the number of blocks to transfer (from 1 to 65535 blocks). Programming the value 0 in the BCNT field corresponds to an infinite block transfer.

# 33.8.3 Read Operation

The following flowchart (Figure 33-8) shows how to read a single block with or without use of DMAC facilities. In this example, a polling method is used to wait for the end of read. Similarly, the user can configure the HSMCI Interrupt Enable Register (HSMCI\_IER) to trigger an interrupt at the end of read.

PCS and LASTXFER fields in the MSBs. However, the SPI still controls the number of bits (8 to 16) to be transferred through MISO and MOSI lines with the chip select configuration registers. This is not the optimal means in terms of memory size for the buffers, but it provides a very effective means to exchange data with several peripherals without any intervention of the processor.

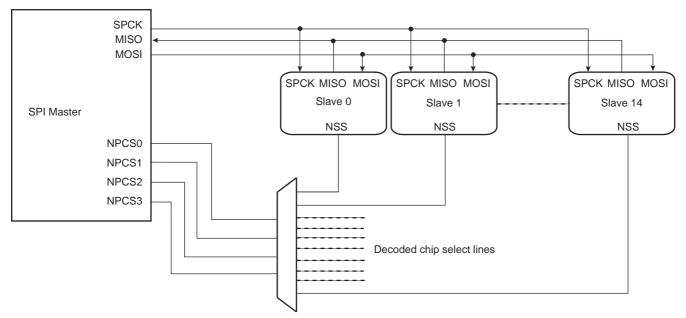

### 34.7.3.7 Peripheral Chip Select Decoding

The user can program the SPI to operate with up to 15 slave peripherals by decoding the four chip select lines, NPCS0 to NPCS3 with an external decoder/demultiplexer (refer to Figure 34-10). This can be enabled by setting the PCSDEC bit in the SPI\_MR.

When operating without decoding, the SPI makes sure that in any case only one chip select line is activated, i.e., one NPCS line driven low at a time. If two bits are defined low in a PCS field, only the lowest numbered chip select is driven low.

When operating with decoding, the SPI directly outputs the value defined by the PCS field on the NPCS lines of either SPI\_MR or SPI\_TDR (depending on PS).

As the SPI sets a default value of 0xF on the chip select lines (i.e., all chip select lines at 1) when not processing any transfer, only 15 peripherals can be decoded.

The SPI has four chip select registers (SPI\_CSR0...SPI\_CSR3). As a result, when external decoding is activated, each NPCS chip select defines the characteristics of up to four peripherals. As an example, SPI\_CRS0 defines the characteristics of the externally decoded peripherals 0 to 3, corresponding to the PCS values 0x0 to 0x3. Consequently, the user has to make sure to connect compatible peripherals on the decoded chip select lines 0 to 3, 4 to 7, 8 to 11 and 12 to 14. Figure 34-10 shows this type of implementation.

If the CSAAT bit is used, with or without the DMAC, the Mode Fault detection for NPCS0 line must be disabled. This is not needed for all other chip select lines since Mode Fault detection is only on NPCS0.

Figure 34-10. Chip Select Decoding Application Block Diagram: Single Master/Multiple Slave Implementation

External 1-of-n Decoder/Demultiplexer

### 34.7.3.8 Peripheral Deselection without DMA

During a transfer of more than one unit of data on a chip select without the DMA, the SPI\_TDR is loaded by the processor, the TDRE flag rises as soon as the content of the SPI\_TDR is transferred into the internal Shift register. When this flag is detected high, the SPI\_TDR can be reloaded. If this reload by the processor occurs before the

### 35.6.12 External Event/Trigger Conditions

An external event can be programmed to be detected on one of the clock sources (XC0, XC1, XC2) or TIOB. The external event selected can then be used as a trigger.

The EEVT parameter in TC\_CMR selects the external trigger. The EEVTEDG parameter defines the trigger edge for each of the possible external triggers (rising, falling or both). If EEVTEDG is cleared (none), no external event is defined.

If TIOB is defined as an external event signal (EEVT = 0), TIOB is no longer used as an output and the compare register B is not used to generate waveforms and subsequently no IRQs. In this case the TC channel can only generate a waveform on TIOA.

When an external event is defined, it can be used as a trigger by setting bit ENETRG in the TC\_CMR.

As in Capture mode, the SYNC signal and the software trigger are also available as triggers. RC Compare can also be used as a trigger depending on the parameter WAVSEL.

### 35.6.13 Output Controller

The output controller defines the output level changes on TIOA and TIOB following an event. TIOB control is used only if TIOB is defined as output (not as an external event).

The following events control TIOA and TIOB: software trigger, external event and RC compare. RA compare controls TIOA and RB compare controls TIOB. Each of these events can be programmed to set, clear or toggle the output as defined in the corresponding parameter in TC\_CMR.

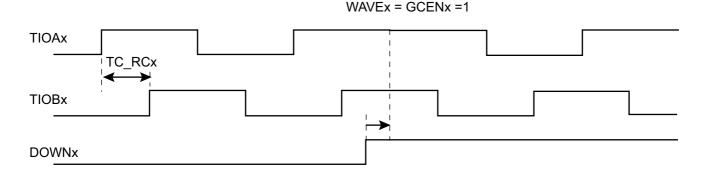

### 35.6.14 2-bit Gray Up/Down Counter for Stepper Motor

Each channel can be independently configured to generate a 2-bit gray count waveform on corresponding TIOA, TIOB outputs by means of the GCEN bit in TC\_SMMRx.

Up or Down count can be defined by writing bit DOWN in TC\_SMMRx.

It is mandatory to configure the channel in Waveform mode in the TC\_CMR.

The period of the counters can be programmed in TC\_RCx.

### Figure 35-15. 2-bit Gray Up/Down Counter

# 35.7.1 TC Channel Control Register

Name: TC\_CCRx [x=0..2]

Address: 0xF8008000 (0)[0], 0xF8008040 (0)[1], 0xF8008080 (0)[2], 0xF800C000 (1)[0], 0xF800C040 (1)[1], 0xF800C080 (1)[2]

# Access: Write-only

| 31 | 30 | 29 | 28 | 27 | 26    | 25     | 24    |

|----|----|----|----|----|-------|--------|-------|

| -  | -  | _  | _  | _  | -     | -      | _     |

| 23 | 22 | 21 | 20 | 19 | 18    | 17     | 16    |

| -  | -  | -  | -  | -  | -     | -      | -     |

| 15 | 14 | 13 | 12 | 11 | 10    | 9      | 8     |

| -  | -  | -  | -  | -  | -     | -      | -     |

| 7  | 6  | 5  | 4  | 3  | 2     | 1      | 0     |

| —  | -  | -  | -  | -  | SWTRG | CLKDIS | CLKEN |

### • CLKEN: Counter Clock Enable Command

0: No effect.

1: Enables the clock if CLKDIS is not 1.

# • CLKDIS: Counter Clock Disable Command

0: No effect.

1: Disables the clock.

# • SWTRG: Software Trigger Command

0: No effect.

1: A software trigger is performed: the counter is reset and the clock is started.

# 37.8 Two-wire Interface (TWI) User Interface

| Offset    | Register                          | Name     | Access     | Reset      |

|-----------|-----------------------------------|----------|------------|------------|

| 0x00      | Control Register                  | TWI_CR   | Write-only | _          |

| 0x04      | Master Mode Register              | TWI_MMR  | Read/Write | 0x0000000  |

| 0x08      | Slave Mode Register               | TWI_SMR  | Read/Write | 0x0000000  |

| 0x0C      | Internal Address Register         | TWI_IADR | Read/Write | 0x0000000  |

| 0x10      | Clock Waveform Generator Register | TWI_CWGR | Read/Write | 0x0000000  |

| 0x14-0x1C | Reserved                          | -        | _          | _          |

| 0x20      | Status Register                   | TWI_SR   | Read-only  | 0x0000F009 |

| 0x24      | Interrupt Enable Register         | TWI_IER  | Write-only | _          |

| 0x28      | Interrupt Disable Register        | TWI_IDR  | Write-only | _          |

| 0x2C      | Interrupt Mask Register           | TWI_IMR  | Read-only  | 0x0000000  |

| 0x30      | Receive Holding Register          | TWI_RHR  | Read-only  | 0x0000000  |

| 0x34      | Transmit Holding Register         | TWI_THR  | Write-only | _          |

| 0x38-0xE0 | Reserved                          | -        | _          | _          |

| 0xE4      | Write Protection Mode Register    | TWI_WPMR | Read/Write | 0x0000000  |

| 0xE8      | Write Protection Status Register  | TWI_WPSR | Read-only  | 0x0000000  |

| 0xEC-0xFC | Reserved                          | -        | _          | -          |

### Table 37-7. Register Mapping

Note: All unlisted offset values are considered as "reserved".

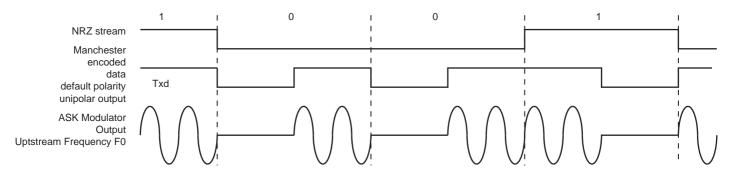

### Figure 38-17. ASK Modulator Output

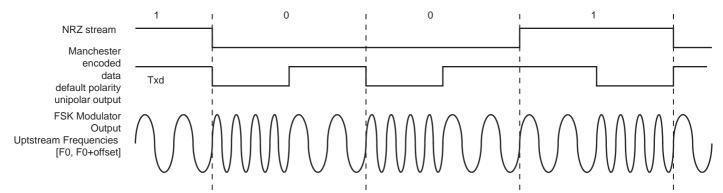

### Figure 38-18. FSK Modulator Output

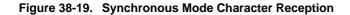

#### 38.6.3.6 Synchronous Receiver

In Synchronous mode (SYNC = 1), the receiver samples the RXD signal on each rising edge of the baud rate clock. If a low level is detected, it is considered as a start. All data bits, the parity bit and the stop bits are sampled and the receiver waits for the next start bit. Synchronous mode operations provide a high-speed transfer capability.

Configuration fields and bits are the same as in Asynchronous mode.

Figure 38-19 illustrates a character reception in Synchronous mode.

### 38.6.3.7 Receiver Operations

When a character reception is completed, it is transferred to the Receive Holding register (US\_RHR) and the RXRDY bit in US\_CSR rises. If a character is completed while the RXRDY is set, the OVRE (Overrun Error) bit is set. The last character is transferred into US\_RHR and overwrites the previous one. The OVRE bit is cleared by writing a 1 to the RSTSTA (Reset Status) bit in the US\_CR.

# Atmel

| 44.6.16 Spe | 44.6.16 Specific Address 1 Bottom Register |    |    |    |    |    |    |  |  |  |

|-------------|--------------------------------------------|----|----|----|----|----|----|--|--|--|

| Name:       | EMAC_SA1B                                  |    |    |    |    |    |    |  |  |  |

| Address:    | 0xF802C098                                 |    |    |    |    |    |    |  |  |  |

| Access:     | Read-write                                 |    |    |    |    |    |    |  |  |  |

| 31          | 30                                         | 29 | 28 | 27 | 26 | 25 | 24 |  |  |  |

|             |                                            |    | AD | DR |    |    |    |  |  |  |

| 23          | 22                                         | 21 | 20 | 19 | 18 | 17 | 16 |  |  |  |

|             |                                            |    | AD | DR |    |    |    |  |  |  |

| 15          | 14                                         | 13 | 12 | 11 | 10 | 9  | 8  |  |  |  |

|             | ADDR                                       |    |    |    |    |    |    |  |  |  |

| 7           | 6                                          | 5  | 4  | 3  | 2  | 1  | 0  |  |  |  |

|             |                                            |    | AD | DR |    |    |    |  |  |  |

# ADDR: Specific Address 1 Bottom

Least significant bits of the destination address. Bit zero indicates whether the address is multicast or unicast and corresponds to the least significant bit of the first byte received.

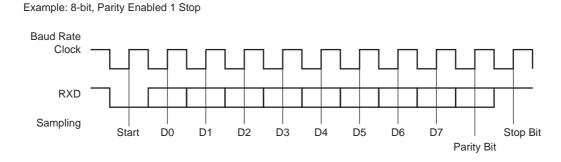

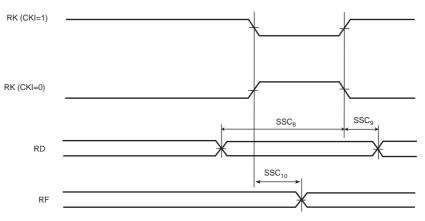

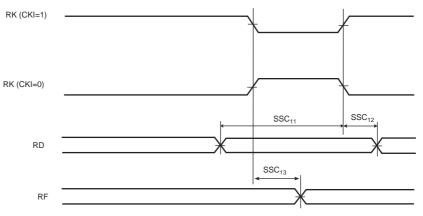

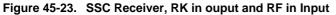

### Figure 45-21. SSC Receiver, RK in Input and RF in Output

### Figure 45-22. SSC Receiver, RK and RF in Output

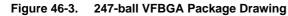

### 46.2.2 247-ball VFBGA package

|                              |    |                  | Common Dimensions |       |      |  |

|------------------------------|----|------------------|-------------------|-------|------|--|

|                              |    | Symbol           | MIN.              | NOM.  | MAX. |  |

| Package :                    |    | VFBGA            |                   |       |      |  |

| Body Size:                   | E  | 10.000<br>10.000 |                   |       |      |  |

| Ball Pitch :                 |    | e                | 0.500             |       |      |  |

| Total Thickness :            |    | A                | 1                 |       |      |  |

| Mold Thickness :             |    | м                | 0.450 Ref.        |       |      |  |

| Substrate Thickness :        |    | s                | 0.260 Ref.        |       |      |  |

| Ball Diameter :              |    |                  | 0.300             |       |      |  |

| Stand Off :                  | A1 | 0.160            | -                 | 0.260 |      |  |

| Ball Width :                 |    | b                | 0.270 - 0         |       |      |  |

| Package Edge Tolerance :     |    | 000              | 0.100             |       |      |  |

| Mold Flatness :              |    | bbb              | 0.100             |       |      |  |

| Coplanarity:                 |    | ddd              | 0.080             |       |      |  |

| Ball Offset (Package) :      |    | eee              | eee 0.150         |       |      |  |

| Ball Offset (Ball) :         |    | fff              | iff 0.080         |       |      |  |

| Ball Count :                 |    | n                | 247               |       |      |  |

| Edge Ball Center to Center : | X  | E1<br>D1         |                   | 9.00  |      |  |

|             | TITLE          | Low profile | Fine Pitc | h Ball Grid Array | GPC:   | СВQ     |

|-------------|----------------|-------------|-----------|-------------------|--------|---------|

| BOTTOM VIEW | Pins:          | 247         |           | Drawing No.:      | R-VFB  | GA247_A |

|             | Body:          | 10x10x1.0   | mm        | REV.:             | В      |         |

|             | Ball Pitch:    | 0.5         | mm        | Date:             | 8/7/2  | 012     |

|             | Ball Diameter: | 0.3         | mm        | Jedec Code:       | Not Je | dec     |

### Table 46-11. Package Information

| BGA Substrate Ball Land | 0.25 mm +/- 0.05  |

|-------------------------|-------------------|

| Solder Mask Opening     | 0.275 mm +/- 0.05 |

### Table 46-12. Device and 247-ball BGA Package Maximum Weight

| 177 | mg |

|-----|----|

|     |    |

# Table 46-13. 247-ball BGA Package Characteristics

| Moisture Sensitivity Level | 3 |

|----------------------------|---|

|----------------------------|---|

# Table 46-14. Package Reference

| JEDEC Drawing Reference | none |

|-------------------------|------|

| JESD97 Classification   | e8   |

### Table 46-10. Ball Information

| Ball Pitch    | 0.5 mm +/- 0.05 |

|---------------|-----------------|

| Ball Diameter | 0.3 mm +/- 0.05 |