## E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ST7                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                             |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 48                                                                     |

| Program Memory Size        | 32KB (32K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 1K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                            |

| Data Converters            | A/D 16x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-LQFP                                                                |

| Supplier Device Package    | -                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f321ar6tae |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|      | 22.1.7    | SCI wrong break duration                  | 239 |

|------|-----------|-------------------------------------------|-----|

|      | 22.1.8    | 16-bit timer PWM mode                     | 239 |

|      | 22.1.9    | TIMD set simultaneously with OC interrupt | 240 |

|      | 22.1.10   | I <sup>2</sup> C multimaster              | 240 |

|      | 22.1.11   | Readout protection with LVD               | 240 |

| 22.2 | All Flas  | h devices                                 | 240 |

|      | 22.2.1    | Internal RC oscillator with LVD           | 240 |

| 22.3 | Limitatio | ons specific to ROM devices               | 240 |

|      | 22.3.1    | LVD operation                             | 240 |

|      | 22.3.2    | LVD startup behavior                      | 241 |

|      | 22.3.3    | AVD not supported                         | 241 |

|      | 22.3.4    | Internal RC oscillator operation          | 241 |

|      | 22.3.5    | External clock source with PLL            | 241 |

|      | 22.3.6    | Pull-up not present on PE2                | 241 |

|      | 22.3.7    | Readout protection with LVD               | 2/1 |

23

## List of figures

| Figure 1.  | Device block diagram                                             | . 19 |

|------------|------------------------------------------------------------------|------|

| Figure 2.  | 64-pin LQFP 14x14 and 10x10 package pinout                       | . 20 |

| Figure 3.  | 44-pin LQFP package pinout                                       | . 21 |

| Figure 4.  | Memory map                                                       | . 26 |

| Figure 5.  | Memory map and sector address                                    | . 30 |

| Figure 6.  | Typical ICC interface                                            | . 31 |

| Figure 7.  | CPU registers                                                    | . 33 |

| Figure 8.  | Stack manipulation example                                       | . 36 |

| Figure 9.  | Clock, reset and supply block diagram                            | . 37 |

| Figure 10. | PLL block diagram                                                | . 38 |

| Figure 11. | Reset block diagram                                              | . 40 |

| Figure 12. | RESET sequence phases                                            |      |

| Figure 13. | RESET sequences                                                  |      |

| Figure 14. | Low voltage detector versus reset                                |      |

| Figure 15. | Using the AVD to monitor $V_{DD}$ (AVDS bit = 0)                 |      |

| Figure 16. | Using the voltage detector to monitor the EVD pin (AVDS bit = 1) |      |

| Figure 17. | Interrupt processing flowchart                                   |      |

| Figure 18. | Priority decision process flowchart                              |      |

| Figure 19. | Concurrent interrupt management                                  |      |

| Figure 20. | Nested interrupt management                                      |      |

| Figure 21. | External interrupt control bits                                  |      |

| Figure 22. | Power saving mode transitions.                                   |      |

| Figure 23. | Slow mode clock transitions                                      |      |

| Figure 24. | Wait mode flowchart                                              |      |

| Figure 25. | Active Halt timing overview                                      |      |

| Figure 26. | Active Halt mode flowchart                                       |      |

| Figure 27. | Halt timing overview                                             |      |

| Figure 28. | Halt mode flowchart                                              |      |

| Figure 29. | I/O port general block diagram                                   |      |

| Figure 30. | Interrupt I/O port state transitions                             |      |

| Figure 31. | Watchdog block diagram                                           |      |

| Figure 32. | Approximate timeout duration.                                    |      |

| Figure 33. | Exact timeout duration (t <sub>min</sub> and t <sub>max</sub> ). |      |

| Figure 34. | Main clock controller (MCC/RTC) block diagram                    |      |

| Figure 35. | PWM auto-reload timer block diagram                              |      |

| Figure 36. | Output compare control                                           |      |

| Figure 37. | PWM auto-reload timer function                                   |      |

| Figure 38. | PWM signal from 0% to 100% duty cycle                            |      |

| Figure 39. | External event detector example (3 counts)                       |      |

| Figure 40. | Input capture timing diagram                                     |      |

| Figure 41. | Timer block diagram                                              |      |

| Figure 42. | 16-bit read sequence                                             |      |

| Figure 43. | Counter timing diagram, internal clock divided by 2              |      |

| •          | Counter timing diagram, internal clock divided by 2              |      |

| Figure 44. |                                                                  |      |

| Figure 45. | Counter timing diagram, internal clock divided by 8              |      |

| Figure 46. | Input capture block diagram                                      |      |

| Figure 47. | Input capture timing diagram                                     |      |

| Figure 48. | Output compare block diagram                                     | 107  |

#### Halt mode recommendations

- Make sure that an external event is available to wake up the microcontroller from Halt mode.

- When using an external interrupt to wake up the microcontroller, re-initialize the corresponding I/O as "Input Pull-up with Interrupt" before executing the HALT instruction. The main reason for this is that the I/O may be wrongly configured due to external interference or by an unforeseen logical condition.

- For the same reason, reinitialize the level sensitiveness of each external interrupt as a precautionary measure.

- The opcode for the HALT instruction is 0x8E. To avoid an unexpected HALT instruction due to a program counter failure, it is advised to clear all occurrences of the data value 0x8E from memory. For example, avoid defining a constant in ROM with the value 0x8E.

- As the HALT instruction clears the interrupt mask in the CC register to allow interrupts, the user may choose to clear all pending interrupt bits before executing the HALT instruction. This avoids entering other peripheral interrupt routines after executing the external interrupt routine corresponding to the wake-up event (reset or external interrupt).

#### **Related documentation**

ST7 Keypad Decoding Techniques, Implementing Wake-Up on Keystroke (AN 980) How to Minimize the ST7 Power Consumption (AN1014) Using an active RC to wake up the ST7LITE0 from power saving mode (AN1605)

| Address (Hex.)                        | Register label | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|---------------------------------------|----------------|-----|---|---|---|---|---|---|-----|

| Reset value of all I/O port registers |                | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0   |

| 0003h                                 | PBDR           |     |   |   |   |   |   |   |     |

| 0004h                                 | PBDDR          | MSB |   |   |   |   |   |   | LSB |

| 0005h                                 | PBOR           |     |   |   |   |   |   |   |     |

| 0006h                                 | PCDR           |     |   |   |   |   |   |   |     |

| 0007h                                 | PCDDR          | MSB |   |   |   |   |   |   | LSB |

| 0008h                                 | PCOR           |     |   |   |   |   |   |   |     |

| 0009h                                 | PDDR           |     |   |   |   |   |   |   |     |

| 000Ah                                 | PDDDR          | MSB |   |   |   |   |   |   | LSB |

| 000Bh                                 | PDOR           |     |   |   |   |   |   |   |     |

| 000Ch                                 | PEDR           |     |   |   |   |   |   |   |     |

| 000Dh                                 | PEDDR          | MSB |   |   |   |   |   |   | LSB |

| 000Eh                                 | PEOR           |     |   |   |   |   |   |   |     |

| 000Fh                                 | PFDR           |     |   |   |   |   |   |   |     |

| 0010h                                 | PFDDR          | MSB |   |   |   |   |   |   | LSB |

| 0011h                                 | PFOR           |     |   |   |   |   |   |   |     |

Table 34. I/O port register map and reset values (continued)

#### **Related documentation**

SPI Communication between ST7 and EEPROM (AN 970)

S/W implementation of I2C bus master (AN1045)

Software LCD driver (AN1048)

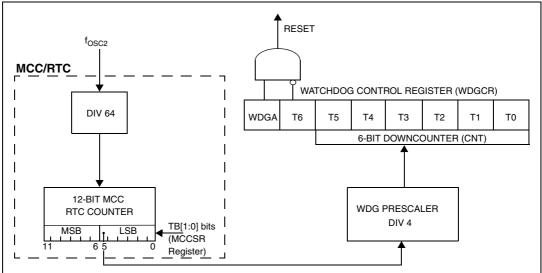

Figure 31. Watchdog block diagram

## **10.4** How to program the watchdog timeout

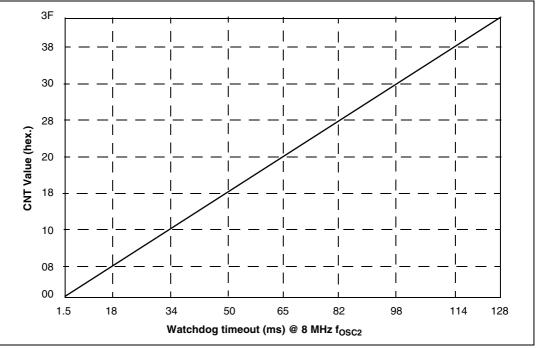

*Figure 32* shows the linear relationship between the 6-bit value to be loaded in the Watchdog Counter (CNT) and the resulting timeout duration in milliseconds. This can be used for a quick calculation without taking the timing variations into account. If more precision is needed, use the formulae in *Figure 33*.

**Caution:** When writing to the WDGCR register, always write 1 in the T6 bit to avoid generating an immediate reset.

Figure 32. Approximate timeout duration

# 11 Main clock controller with real-time clock and beeper (MCC/RTC)

## 11.1 Introduction

The Main Clock Controller consists of three different functions:

- a programmable CPU clock prescaler

- a clock-out signal to supply external devices

- a real-time clock timer with interrupt capability

Each function can be used independently and simultaneously.

## 11.2 **Programmable CPU clock prescaler**

The programmable CPU clock prescaler supplies the clock for the ST7 CPU and its internal peripherals. It manages Slow power saving mode (see *Section 8.2: Slow mode on page 62* for more details).

The prescaler selects the  $f_{CPU}$  main clock frequency and is controlled by three bits in the MCCSR register: CP[1:0] and SMS.

## 11.3 Clock-out capability

The clock-out capability is an alternate function of an I/O port pin that outputs a  $f_{CPU}$  clock to drive external devices. It is controlled by the MCO bit in the MCCSR register.

**Caution:** When selected, the clock out pin suspends the clock during Active Halt mode.

## **11.4** Real-time clock timer (RTC)

The counter of the real-time clock timer allows an interrupt to be generated based on an accurate real-time clock. Four different time bases depending directly on  $f_{OSC2}$  are available. The whole functionality is controlled by four bits of the MCCSR register: TB[1:0], OIE and OIF.

When the RTC interrupt is enabled (OIE bit set), the ST7 enters Active Halt mode when the HALT instruction is executed. See *Section 8.4: Active Halt and Halt modes on page 65* for more details.

## 11.5 Beeper

The beep function is controlled by the MCCBCR register. It can output three selectable frequencies on the BEEP pin (I/O port alternate function).

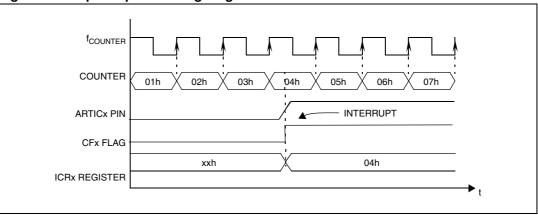

#### 12.2.9 External interrupt capability

This mode allows the input capture capabilities to be used as external interrupt sources. The interrupts are generated on the edge of the ARTICx signal.

The edge sensitivity of the external interrupts is programmable (CSx bit of ARTICCSR register) and they are independently enabled through CIEx bits of the ARTICCSR register. After fetching the interrupt vector, the CFx flags can be read to identify the interrupt source.

During Halt mode, the external interrupts can be used to wake up the micro (if the CIEx bit is set).

Figure 40. Input capture timing diagram

#### 12.3.5 Duty cycle registers (PWMDCRx)

| PWMDCRx Reset value: 00 |   |   |   |   |   | et value: 0000 | 0000 (00h) |

|-------------------------|---|---|---|---|---|----------------|------------|

| 7                       | 6 | 5 | 4 | 3 | 2 | 1              | 0          |

| DC[7:0]                 |   |   |   |   |   |                |            |

| RW                      |   |   |   |   |   |                |            |

Table 52. PWMDCRx register description

| Bit | Name    | Function                                                       |

|-----|---------|----------------------------------------------------------------|

| 7:0 | DC[7:0] | Duty Cycle Data<br>These bits are set and cleared by software. |

A PWMDCRx register is associated with the OCRx register of each PWM channel to determine the second edge location of the PWM signal (the first edge location is common to all channels and given by the ARTARR register). These PWMDCR registers allow the duty cycle to be set independently for each PWM channel.

#### 12.3.6 Input capture control / status register (ARTICCSR)

| ARTICCSR Reset value: 0000 0000 (00h) |                  |   |          |   |         |   |   |

|---------------------------------------|------------------|---|----------|---|---------|---|---|

| 7                                     | 6                | 5 | 4        | 3 | 2       | 1 | 0 |

| Rese                                  | Reserved CS[2:1] |   | CIE[2:1] |   | CF[2:1] |   |   |

| -                                     | - BW             |   | R\       | N | F       | W |   |

#### Table 53. ARTICCSR register description

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                           |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | -        | Reserved, always read as 0.                                                                                                                                                                                                                                                                                        |

| 5:4 | CS[2:1]  | <ul> <li>Capture Sensitivity</li> <li>These bits are set and cleared by software. They determine the trigger event polarity on the corresponding input capture channel.</li> <li>0: Falling edge triggers capture on channel x</li> <li>1: Rising edge triggers capture on channel x</li> </ul>                    |

| 3:2 | CIE[2:1] | <ul> <li>Capture Interrupt Enable</li> <li>These bits are set and cleared by software. They enable or disable the Input capture channel interrupts independently.</li> <li>0: Input capture channel x interrupt disabled</li> <li>1: Input capture channel x interrupt enabled</li> </ul>                          |

| 1:0 | CF[2:1]  | <ul> <li><i>Capture Flag</i></li> <li>These bits are set by hardware and cleared by software reading the corresponding ARTICRx register. Each CFx bit indicates that an input capture x has occurred.</li> <li>0: No input capture on channel x</li> <li>1: An input capture has occurred on channel x.</li> </ul> |

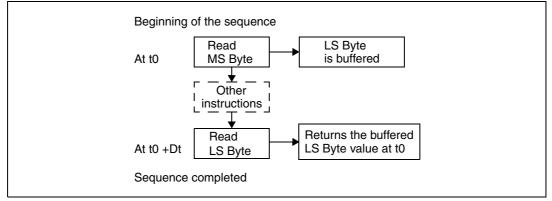

#### 16-bit read sequence

The 16-bit read sequence (from either the Counter Register or the Alternate Counter Register) is illustrated in *Figure 42*.

Figure 42. 16-bit read sequence

The user must read the MS Byte first; the LS Byte value is then buffered automatically.

This buffered value remains unchanged until the 16-bit read sequence is completed, even if the user reads the MS Byte several times.

After a complete reading sequence, if only the CLR register or ACLR register are read, they return the LS Byte of the count value at the time of the read.

Whatever timer mode is used (input capture, output compare, one pulse mode or PWM mode) an overflow occurs when the counter rolls over from FFFFh to 0000h, after which

- the TOF bit of the SR register is set

- a timer interrupt is generated if

- the TOIE bit of the CR1 register is set and

- the I bit of the CC register is cleared

If one of these conditions is false, the interrupt remains pending to be issued as soon as they are both true.

Clearing the overflow interrupt request is done in two steps:

- 1. Reading the SR register while the TOF bit is set

- 2. An access (read or write) to the CLR register

Note: The TOF bit is not cleared by accesses to ACLR register. The advantage of accessing the ACLR register rather than the CLR register is that it allows simultaneous use of the overflow function and reading the free running counter at random times (for example, to measure elapsed time) without the risk of clearing the TOF bit erroneously.

The timer is not affected by Wait mode.

In Halt mode, the counter stops counting until the mode is exited. Counting then resumes from the previous count (MCU awakened by an interrupt) or from the reset count (MCU awakened by a Reset).

The SPIF bit can be cleared during a second transmission; however, it must be cleared before the second SPIF bit in order to prevent an Overrun condition (see *Overrun condition* (*OVR*) on page 128).

## 14.4 Clock phase and clock polarity

Four possible timing relationships may be chosen by software, using the CPOL and CPHA bits (see *Figure 59*).

Note: The idle state of SCK must correspond to the polarity selected in the SPICSR register (by pulling up SCK if CPOL = 1 or pulling down SCK if CPOL = 0).

The combination of the CPOL clock polarity and CPHA (clock phase) bits selects the data capture clock edge

*Figure 59* shows an SPI transfer with the four combinations of the CPHA and CPOL bits. The diagram may be interpreted as a master or slave timing diagram where the SCK pin, the MISO pin, the MOSI pin are directly connected between the master and the slave device.

*Note:* If CPOL is changed at the communication byte boundaries, the SPI must be disabled by resetting the SPE bit.

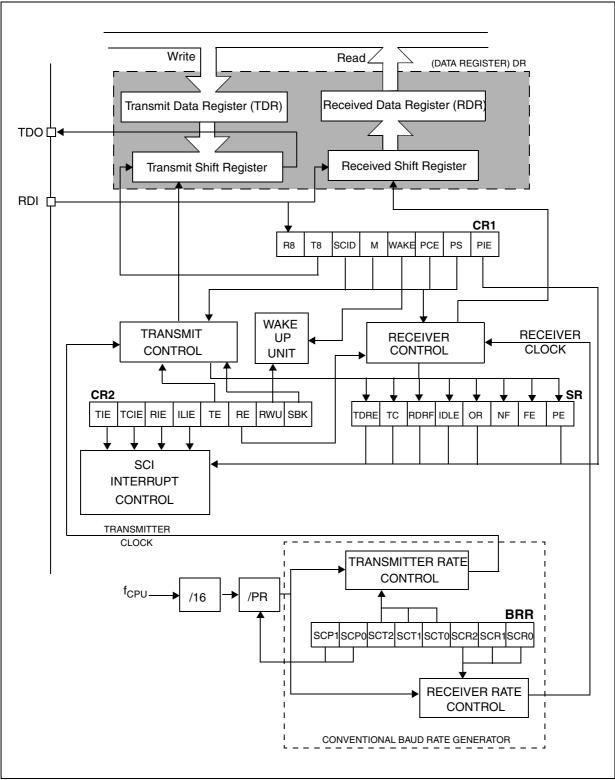

#### Figure 62. SCI block diagram

A receiver wakes up by Idle Line detection when the Receive line has recognized an Idle Frame. Then the RWU bit is reset by hardware but the IDLE bit is not set.

Receiver wakes up by Address Mark detection when it received a '1' as the most significant bit of a word, thus indicating that the message is an address. The reception of this particular word wakes up the receiver, resets the RWU bit and sets the RDRF bit, which allows the receiver to receive this word normally and to use it as an address word.

**Caution:** In Mute mode, do not write to the SCICR2 register. If the SCI is in Mute mode during the read operation (RWU = 1) and a address mark wake-up event occurs (RWU is reset) before the write operation, the RWU bit is set again by this write operation. Consequently the address byte is lost and the SCI is not woken up from Mute mode.

#### **Parity control**

Parity control (generation of parity bit in transmission and parity checking in reception) can be enabled by setting the PCE bit in the SCICR1 register. Depending on the frame length defined by the M bit, the possible SCI frame formats are as listed in *Table 70*.

| M bit | PCE bit | SCI frame                  |

|-------|---------|----------------------------|

| 0     | 0       | SB   8 bit data   STB      |

| 0     | 1       | SB   7-bit data   PB   STB |

| 1     | 0       | SB   9-bit data   STB      |

| 1     | 1       | SB   8-bit data PB   STB   |

Table 70.Frame formats

Legend: SB = Start Bit, STB = Stop Bit, PB = Parity Bit

Note:

In case of wake-up by an address mark, the MSB bit of the data is taken into account and not the parity bit

**Even parity:** the parity bit is calculated to obtain an even number of '1's inside the frame made of the 7 or 8 LSB bits (depending on whether M is equal to 0 or 1) and the parity bit.

Example: data = 00110101; 4 bits set => parity bit is 0 if even parity is selected (PS bit = 0).

**Odd parity:** the parity bit is calculated to obtain an odd number of '1's inside the frame made of the 7 or 8 LSB bits (depending on whether M is equal to 0 or 1) and the parity bit.

Example: data = 00110101; 4 bits set => parity bit is 1 if odd parity is selected (PS bit = 1).

**Transmission mode:** If the PCE bit is set then the MSB bit of the data written in the data register is not transmitted but is changed by the parity bit.

**Reception mode:** If the PCE bit is set then the interface checks if the received data byte has an even number of '1's if even parity is selected (PS = 0) or an odd number of '1's if odd parity is selected (PS = 1). If the parity check fails, the PE flag is set in the SCISR register and an interrupt is generated if PIE is set in the SCICR1 register.

#### SCI clock tolerance

During reception, each bit is sampled 16 times. The majority of the 8th, 9th and 10th samples is considered as the bit value. For a valid bit detection, all the three samples should have the same value otherwise the noise flag (NF) is set. For example: If the 8th, 9th and 10th samples are 0, 1 and 1 respectively, then the bit value is '1', but the Noise Flag bit is set because the three samples values are not the same.

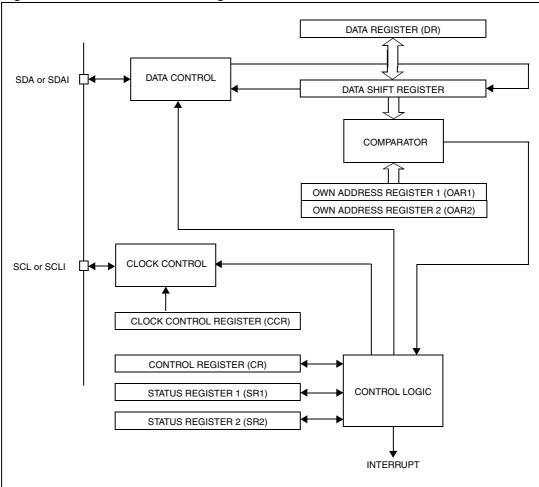

#### 16.3.3 SDA/SCL line control

#### Transmitter mode

The interface holds the clock line low before transmission to wait for the microcontroller to write the byte in the data register.

#### **Receiver mode**

The interface holds the clock line low after reception to wait for the microcontroller to read the byte in the data register.

The SCL frequency ( $f_{SCL}$ ) is controlled by a programmable clock divider which depends on the  $I^2C$  bus mode.

When the I<sup>2</sup>C cell is enabled, the SDA and SCL ports must be configured as floating inputs. In this case, the value of the external pull-up resistor used depends on the application.

When the I<sup>2</sup>C cell is disabled, the SDA and SCL ports revert to being standard I/O port pins.

Figure 67. I<sup>2</sup>C interface block diagram

#### 19.4.3 On-chip peripherals

Measured on LQFP64 generic board  $T_A = 25^{\circ}C$ ,  $f_{CPU} = 4$  MHz.

Table 113.

On-chip peripherals current consumption

| Symbol               | Parameter                                         | Conditions             | Тур | Unit |

|----------------------|---------------------------------------------------|------------------------|-----|------|

| I <sub>DD(TIM)</sub> | 16-bit timer supply current <sup>(1)</sup>        | $V_{DD} = 5.0V$        | 50  | μA   |

| I <sub>DD(ART)</sub> | ART PWM supply current <sup>(2)</sup>             | $V_{DD} = 5.0V$        | 75  | μA   |

| I <sub>DD(SPI)</sub> | SPI supply current <sup>(3)</sup>                 | V - 5 0V               | 400 |      |

| I <sub>DD(SCI)</sub> | SCI supply current <sup>(4)</sup>                 | V <sub>DD</sub> = 5.0V | 400 | μA   |

| I <sub>DD(I2C)</sub> | I2C supply current <sup>(5)</sup>                 | $V_{DD} = 5.0V$        | 175 | μA   |

| I <sub>DD(ADC)</sub> | ADC supply current when converting <sup>(6)</sup> | $V_{DD} = 5.0V$        | 400 | μA   |

1. Data based on a differential I<sub>DD</sub> measurement between reset configuration (timer counter running at  $f_{CPU}/4$ ) and timer counter stopped (only TIMD bit set). Data valid for one timer.

2. Data based on a differential  $I_{DD}$  measurement between reset configuration (timer stopped) and timer counter enabled (only TCE bit set).

Data based on a differential I<sub>DD</sub> measurement between reset configuration (SPI disabled) and a permanent SPI master communication at maximum speed (data sent equal to 55h). This measurement includes the pad toggling consumption.

4. Data based on a differential  $I_{DD}$  measurement between SCI low power state (SCID = 1) and a permanent SCI data transmit sequence.

Data based on a differential I<sub>DD</sub> measurement between reset configuration (I2C disabled) and a permanent I2C master communication at 100 kHz (data sent equal to 55h). This measurement includes the pad toggling consumption (27k ohm external pull-up on clock and data lines).

6. Data based on a differential  ${\rm I}_{\rm DD}$  measurement between reset configuration and continuous A/D conversions.

|          |                        | Typical ceramic resonators <sup>(1)</sup> |                                                  |  |  |  |

|----------|------------------------|-------------------------------------------|--------------------------------------------------|--|--|--|

| Supplier | f <sub>OSC</sub> (MHz) | Reference                                 | Recommended OSCRANGE option bit<br>configuration |  |  |  |

|          | 2                      | CSTCC2M00G56A-R0                          | MP mode <sup>(2)</sup>                           |  |  |  |

| Murata   | 4                      | CSTCR4M00G55B-R0                          | MS mode                                          |  |  |  |

| Wulata   | 8                      | CSTCE8M00G55A-R0                          | HS mode                                          |  |  |  |

|          | 16                     | CSTCE16M0G53A-R0                          | TIS mode                                         |  |  |  |

Table 117. OSCRANGE selection for typical resonators

1. Resonator characteristics given by the ceramic resonator manufacturer. For more information on these resonators, please consult www.murata.com.

2. LP mode is not recommended for 2 MHz resonator because the peak to peak amplitude is too small (> 0.8V).

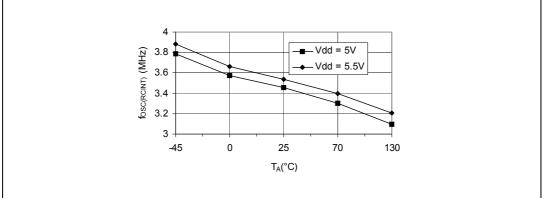

#### 19.5.4 RC oscillators

#### Table 118. RC oscillator characteristics

| Symbol      | Parameter                                                | Conditions                         | Min | Тур | Max | Unit |

|-------------|----------------------------------------------------------|------------------------------------|-----|-----|-----|------|

| fosc(rcint) | Internal RC oscillator frequency (see <i>Figure 80</i> ) | $T_{A} = 25^{\circ}C, V_{DD} = 5V$ | 2   | 3.5 | 5.6 | MHz  |

## Figure 80. Typical f<sub>OSC(RCINT)</sub> versus T<sub>A</sub>

Note: To reduce disturbance to the RC oscillator, it is recommended to place decoupling capacitors between  $V_{DD}$  and  $V_{SS}$  as shown in Figure 100.

## 20.1 Thermal characteristics

#### Table 139. Thermal characteristics

| Symbol            | Ratings                                                                                          | Value          | Unit |

|-------------------|--------------------------------------------------------------------------------------------------|----------------|------|

| R <sub>thJA</sub> | Package thermal resistance (junction to ambient)<br>LQFP64 14x14<br>LQFP64 10x10<br>LQFP44 10x10 | 47<br>50<br>52 | °C/W |

| PD                | Power dissipation <sup>(1)</sup>                                                                 | 500            | mW   |

| T <sub>Jmax</sub> | Maximum junction temperature <sup>(2)</sup>                                                      | 150            | °C   |

1. The maximum power dissipation is obtained from the formula  $P_D = (T_J - T_A) / R_{thJA}$ . The power dissipation of an application can be defined by the user with the formula:  $P_D = P_{INT} + P_{PORT}$  where  $P_{INT}$  is the chip internal power ( $I_{DD} \times V_{DD}$ ) and  $P_{PORT}$  is the port power dissipation depending on the ports used in the application.

2. The maximum chip-junction temperature is based on technology characteristics.

## 20.2 Ecopack information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

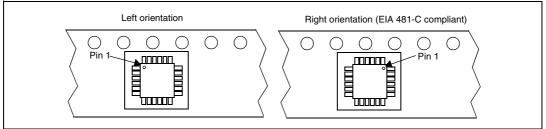

## 20.3 Packaging for automatic handling

The devices can be supplied in trays or with tape and reel conditioning.

Tape and reel conditioning can be ordered with pin 1 left-oriented or right-oriented when facing the tape sprocket holes as shown in *Figure 104*.

#### Figure 104. Pin 1 orientation in tape and reel conditioning

See also Section Figure 105.: ST72F321xxx-Auto Flash commercial product structure on page 226 and Figure 106: ST72P321xxx-Auto FastROM commercial product structure on page 228.

### 21.1.2 Flash ordering information

The following *Figure 105* serves as a guide for ordering.

#### Figure 105. ST72F321xxx-Auto Flash commercial product structure

| Example:                              |            | ST72       | F        | 321   | R | 9 | Т | А | х |

|---------------------------------------|------------|------------|----------|-------|---|---|---|---|---|

| Product class                         |            |            |          |       |   |   |   |   |   |

| ST72 microcontroller                  |            |            |          |       |   |   |   |   |   |

| ST72 microcontroller                  |            |            |          |       |   |   |   |   |   |

| Family type                           |            |            |          |       |   |   |   |   |   |

| F = Flash                             |            |            |          |       |   |   |   |   |   |

| Sub-family type                       |            |            |          |       |   |   |   |   |   |

|                                       |            |            |          |       |   |   |   |   |   |

| 321 = 321 sub-family                  |            |            |          |       |   |   |   |   |   |

| Pin count                             |            |            |          |       |   |   |   |   |   |

| AR = 64 pins 10 x 10 mm               |            |            |          |       |   |   |   |   |   |

| R = 64 pins 14 x 14 mm                |            |            |          |       |   |   |   |   |   |

| J = 44 pins 10 x 10 mm                |            |            |          |       |   |   |   |   |   |

|                                       |            |            |          |       |   |   |   |   |   |

| Program memory size                   |            |            |          |       |   |   |   |   |   |

| 6 = 32 Kbytes                         |            |            |          |       |   |   |   |   |   |

| 7 = 48 Kbytes                         |            |            |          |       |   |   |   |   |   |

| 9 = 60 Kbytes                         |            |            |          |       |   |   |   |   |   |

|                                       |            |            |          |       |   |   |   |   |   |

| Package type                          |            |            |          |       |   |   |   |   |   |

| T = LQFP                              |            |            |          |       |   |   |   |   |   |

|                                       |            |            |          |       |   |   |   |   |   |

| Temperature range                     |            |            |          |       |   |   |   |   |   |

| A = -40 °C to 85 °C                   |            |            |          |       |   |   |   |   |   |

| C = -40 °C to 125 °C                  |            |            |          |       |   |   |   |   |   |

| Tape and Reel conditioning            | options (  | left blank | t if Tra | ay) — |   |   |   |   |   |

| TR or R = Pin 1 left-oriented         | - •        |            |          |       |   |   |   |   |   |

| TX or X = Pin 1 right-oriented        | (EIA 481-  | C complia  | ant)     |       |   |   |   |   |   |

| ECOPACK/Fab code                      |            |            |          |       |   |   |   |   |   |

| Blank or E = Lead-free ECOP           |            |            |          |       |   |   |   |   |   |

|                                       |            |            | )        |       |   |   |   |   |   |

| S = Lead-free ECOPACK <sup>®</sup> Ca | atania Fab | )          |          |       |   |   |   |   |   |

For a list of available options (e.g. memory size, package) and orderable part numbers or for further information on any aspect of this device, please go to <u>www.st.com</u> or contact the ST Sales Office nearest to you.

|                          | Emulation         |                      |                    |                            | Programming                |  |

|--------------------------|-------------------|----------------------|--------------------|----------------------------|----------------------------|--|

| Supported                | ST7 DVP3 series   |                      | ST7 EMU            | ICC socket                 |                            |  |

| products                 | Emulator          | Connection kit       | Emulator           | Active probe<br>and T.E.B. | board                      |  |

| ST72521M,<br>ST72F521M   |                   | ST7MDT20-<br>T80/DVP |                    |                            |                            |  |

| ST72521R,<br>ST72F521R   | ST7MDT20-<br>DVP3 | ST7MDT20-<br>T64/DVP | ST7MDT20M-<br>EMU3 | ST7MDT20M-<br>TEB          | ST7SB20M/xx <sup>(1)</sup> |  |

| ST72521AR,<br>ST72F521AR |                   | ST7MDT20-<br>T6A/DVP |                    |                            |                            |  |

| ST72321AR,<br>ST72F321AR |                   | ST7MDT20-<br>T6A/DVP | ST7MDT20M-         | ST7MDT20M-                 | ST7SB20M/xx <sup>(2)</sup> |  |

| ST72321R,<br>ST72F321R   | ST7MDT20-<br>DVP3 | ST7MDT20-<br>T64/DVP | EMU3               | TEB                        | 5175B20W/XX <sup>(-)</sup> |  |

| ST72321J,<br>ST72F321J   |                   | ST7MDT20-<br>T44/DVP | ST7MDT20J-<br>EMU3 | ST7MDT20J-<br>TEB          | ST7SB20J/xx <sup>(2)</sup> |  |

Table 144. STMicroelectronics development tools

1. Add suffix /EU, /UK, /US for the power supply of your region.

2. Add suffix /EU, /UK, /US for the power supply of your region.

#### Table 145. Suggested list of socket types

| Device         | Socket<br>(supplied with ST7MDT20M-EMU3) | Emulator adapter<br>(supplied with ST7MDT20M-EMU3) |

|----------------|------------------------------------------|----------------------------------------------------|

| LQFP80 14 X 14 | YAMAICHI IC149-080-*51-*5                | YAMAICHI ICP-080-7                                 |

| LQFP64 14 x14  | CAB 3303262                              | CAB 3303351                                        |

| LQFP64 10 x10  | YAMAICHI IC149-064-*75-*5                | YAMAICHI ICP-064-6                                 |

| LQFP44 10 x10  | YAMAICHI IC149-044-*52-*5                | YAMAICHI ICP-044-5                                 |

#### 21.3.5 Socket and emulator adapter information

For information on the type of socket that is supplied with the emulator, refer to the suggested list of sockets in *Table 145*.

Note: Before designing the board layout, it is recommended to check the overall dimensions of the socket as they may be greater than the dimensions of the device.

For footprint and other mechanical information about these sockets and adapters, refer to the manufacturer's datasheet.

#### **Related documentation**

ST7 Visual Develop Software Key Debugging Features (AN 978)

ST7 Visual Develop for ST7 Cosmic C toolset users (AN 1938)

ST7 Visual Develop for ST7 Assembler Linker toolset users (AN 1940)

## 21.4 ST7 application notes

All relevant ST7 application notes can be found on www.st.com.

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2010 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

Doc ID 13829 Rev 1