# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | ST7                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                              |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 48                                                                      |

| Program Memory Size        | 60KB (60K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 2K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                             |

| Data Converters            | A/D 16x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | -                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f321ar9tatr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 6.6 System integrity management (SI)

The System Integrity Management block contains the Low Voltage Detector (LVD) and Auxiliary Voltage Detector (AVD) functions. It is managed by the SICSR register.

#### 6.6.1 Low voltage detector (LVD)

The low voltage detector function (LVD) generates a static reset when the  $V_{DD}$  supply voltage is below a  $V_{IT}$  reference value. This means that it secures the power-up as well as the power-down keeping the ST7 in reset.

The V<sub>IT</sub> reference value for a voltage drop is lower than the V<sub>IT+</sub> reference value for poweron in order to avoid a parasitic reset when the MCU starts running and sinks current on the supply (hysteresis).

The LVD reset circuitry generates a reset when  $V_{DD}$  is below:

- V<sub>IT+</sub> when V<sub>DD</sub> is rising

- V<sub>IT</sub> when V<sub>DD</sub> is falling

The LVD function is illustrated in *Figure 14*.

The voltage threshold can be configured by option byte to be low, medium or high.

Provided the minimum  $V_{DD}$  value (guaranteed for the oscillator frequency) is above  $V_{IT-}$ , the MCU can only be in two modes:

- under full software control

- in static safe reset

In these conditions, secure operation is always ensured for the application without the need for external reset hardware.

During a low voltage detector reset, the **RESET** pin is held low, thus permitting the MCU to reset other devices.

Note: The LVD allows the device to be used without any external RESET circuitry.

If the medium or low thresholds are selected, the detection may occur outside the specified operating voltage range. Below 3.8V, device operation is not guaranteed.

The LVD is an optional function which can be selected by option byte.

It is recommended to make sure that the  $V_{DD}$  supply voltage rises monotonously when the device is exiting from Reset, to ensure the application functions properly.

## 9 I/O ports

## 9.1 Introduction

The I/O ports offer different functional modes:

• transfer of data through digital inputs and outputs

and for specific pins:

- external interrupt generation

- alternate signal input/output for the on-chip peripherals.

An I/O port contains up to eight pins. Each pin can be programmed independently as digital input (with or without interrupt generation) or digital output.

## 9.2 Functional description

Each port has two main registers:

- Data Register (DR)

- Data Direction Register (DDR)

and one optional register:

• Option Register (OR)

Each I/O pin may be programmed using the corresponding register bits in the DDR and OR registers (bit X corresponding to pin X of the port). The same correspondence is used for the DR register.

The following description takes into account the OR register (for specific ports which do not provide this register refer to *Section 9.3: I/O port implementation on page 74*). The generic I/O block diagram is shown in *Figure 29*.

#### 9.2.1 Input modes

The input configuration is selected by clearing the corresponding DDR register bit.

In this case, reading the DR register returns the digital value applied to the external I/O pin.

Different input modes can be selected by software through the OR register.

Note: 1 Writing the DR register modifies the latch value but does not affect the pin status.

- 2 When switching from input to output mode, the DR register has to be written first to drive the correct level on the pin as soon as the port is configured as an output.

- 3 Do not use read/modify/write instructions (BSET or BRES) to modify the DR register as this might corrupt the DR content for I/Os configured as input.

#### **External interrupt function**

When an I/O is configured as Input with Interrupt, an event on this I/O can generate an external interrupt request to the CPU.

Each pin can independently generate an interrupt request. The interrupt sensitivity is independently programmable using the sensitivity bits in the EICR register.

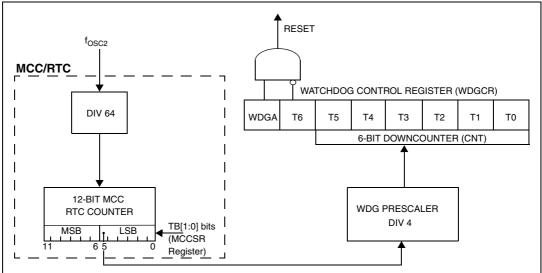

Figure 31. Watchdog block diagram

## **10.4** How to program the watchdog timeout

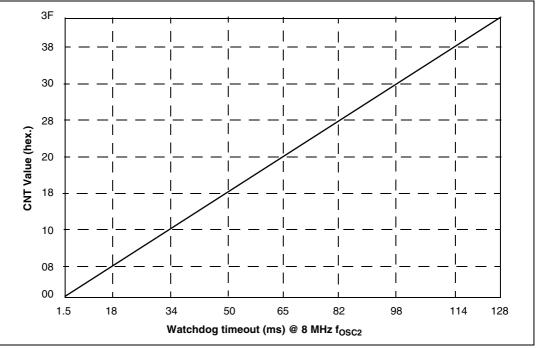

*Figure 32* shows the linear relationship between the 6-bit value to be loaded in the Watchdog Counter (CNT) and the resulting timeout duration in milliseconds. This can be used for a quick calculation without taking the timing variations into account. If more precision is needed, use the formulae in *Figure 33*.

**Caution:** When writing to the WDGCR register, always write 1 in the T6 bit to avoid generating an immediate reset.

Figure 32. Approximate timeout duration

# 11 Main clock controller with real-time clock and beeper (MCC/RTC)

## 11.1 Introduction

The Main Clock Controller consists of three different functions:

- a programmable CPU clock prescaler

- a clock-out signal to supply external devices

- a real-time clock timer with interrupt capability

Each function can be used independently and simultaneously.

## 11.2 **Programmable CPU clock prescaler**

The programmable CPU clock prescaler supplies the clock for the ST7 CPU and its internal peripherals. It manages Slow power saving mode (see *Section 8.2: Slow mode on page 62* for more details).

The prescaler selects the  $f_{CPU}$  main clock frequency and is controlled by three bits in the MCCSR register: CP[1:0] and SMS.

## 11.3 Clock-out capability

The clock-out capability is an alternate function of an I/O port pin that outputs a  $f_{CPU}$  clock to drive external devices. It is controlled by the MCO bit in the MCCSR register.

**Caution:** When selected, the clock out pin suspends the clock during Active Halt mode.

## 11.4 Real-time clock timer (RTC)

The counter of the real-time clock timer allows an interrupt to be generated based on an accurate real-time clock. Four different time bases depending directly on  $f_{OSC2}$  are available. The whole functionality is controlled by four bits of the MCCSR register: TB[1:0], OIE and OIF.

When the RTC interrupt is enabled (OIE bit set), the ST7 enters Active Halt mode when the HALT instruction is executed. See *Section 8.4: Active Halt and Halt modes on page 65* for more details.

## 11.5 Beeper

The beep function is controlled by the MCCBCR register. It can output three selectable frequencies on the BEEP pin (I/O port alternate function).

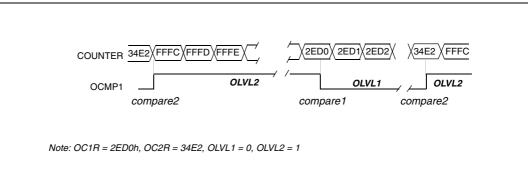

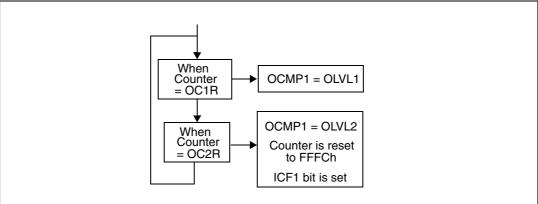

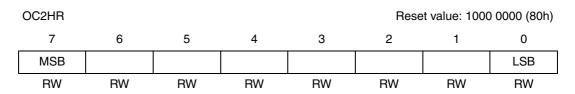

## Figure 53. Pulse width modulation mode timing example with 2 output compare functions

Note:

On timers with only one Output Compare register, a fixed frequency PWM signal can be generated using the output compare and the counter overflow to define the pulse length.

#### 13.3.7 Pulse width modulation mode

Pulse Width Modulation (PWM) mode enables the generation of a signal with a frequency and pulse length determined by the value of the OC1R and OC2R registers.

Pulse Width Modulation mode uses the complete Output Compare 1 function plus the OC2R register, and so this functionality cannot be used when PWM mode is activated.

In PWM mode, double buffering is implemented on the output compare registers. Any new values written in the OC1R and OC2R registers are taken into account only at the end of the PWM period (OC2) to avoid spikes on the PWM output pin (OCMP1).

#### Procedure

To use pulse width modulation mode:

- 1. Load the OC2R register with the value corresponding to the period of the signal using the appropriate formula below according to the timer clock source used.

- Load the OC1R register with the value corresponding to the period of the pulse if OLVL1 = 0 and OLVL2 = 1 using the appropriate formula below according to the timer clock source used.

- 3. Select the following in the CR1 register:

- Using the OLVL1 bit, select the level to be applied to the OCMP1 pin after a successful comparison with the OC1R register.

- Using the OLVL2 bit, select the level to be applied to the OCMP1 pin after a successful comparison with the OC2R register.

- 4. Select the following in the CR2 register:

- Set OC1E bit: the OCMP1 pin is then dedicated to the output compare 1 function.

- Set the PWM bit.

- Select the timer clock (CC[1:0]) (see Table 61: Timer clock selection).

If OLVL1 = 1 and OLVL2 = 0 the length of the positive pulse is the difference between the OC2R and OC1R registers.

If OLVL1 = OLVL2 a continuous signal will be seen on the OCMP1 pin.

The OC<sub>i</sub>R register value required for a specific timing application can be calculated using the following formula:

$$OCiR value = \frac{t \cdot f_{CPU} - 5}{PRESC}$$

Where:

t

= Signal or pulse period (in seconds)

$f_{CPU} = CPU \operatorname{clock} \operatorname{frequency} (\operatorname{in} \operatorname{hertz})$

PRESC = Timer prescaler factor (2, 4 or 8 depending on CC[1:0] bits; see *Table 61: Timer clock selection*)

If the timer clock is an external clock the formula is:

$$OCiR = t * f_{EXT} - 5$$

Where:

t

Signal or pulse period (in seconds)

f<sub>EXT</sub> = External timer clock frequency (in hertz)

The Output Compare 2 event causes the counter to be initialized to FFFCh (see Figure 53).

- Note: 1 After a write instruction to the OCiHR register, the output compare function is inhibited until the OCiLR register is also written.

- 2 The OCF1 and OCF2 bits cannot be set by hardware in PWM mode therefore the Output Compare interrupt is inhibited.

- 3 The ICF1 bit is set by hardware when the counter reaches the OC2R value and can produce a timer interrupt if the ICIE bit is set and the I bit is cleared.

- 4 In PWM mode the ICAP1 pin cannot be used to perform input capture because it is disconnected to the timer. The ICAP2 pin can be used to perform input capture (ICF2 can be set and IC2R can be loaded) but the user must take care that the counter is reset each period and ICF1 can also generates interrupt if ICIE is set.

- 5 When the Pulse Width Modulation (PWM) and One Pulse Mode (OPM) bits are both set, the PWM mode is the only active one.

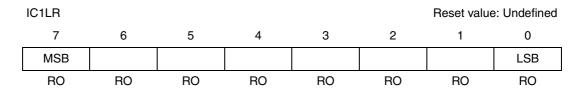

#### 13.7.5 Input capture 1 low register (IC1LR)

This is an 8-bit read only register that contains the low part of the counter value (transferred by the input capture 1 event).

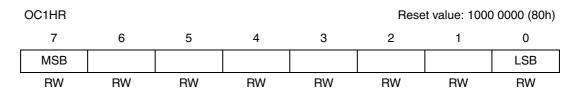

#### 13.7.6 Output compare 1 high register (OC1HR)

This is an 8-bit register that contains the high part of the value to be compared to the CHR register.

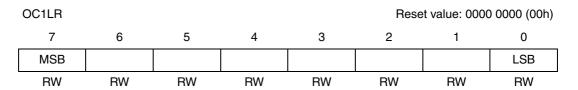

#### 13.7.7 Output compare 1 low register (OC1LR)

This is an 8-bit register that contains the low part of the value to be compared to the CLR register.

#### 13.7.8 Output compare 2 high register (OC2HR)

This is an 8-bit register that contains the high part of the value to be compared to the CHR register.

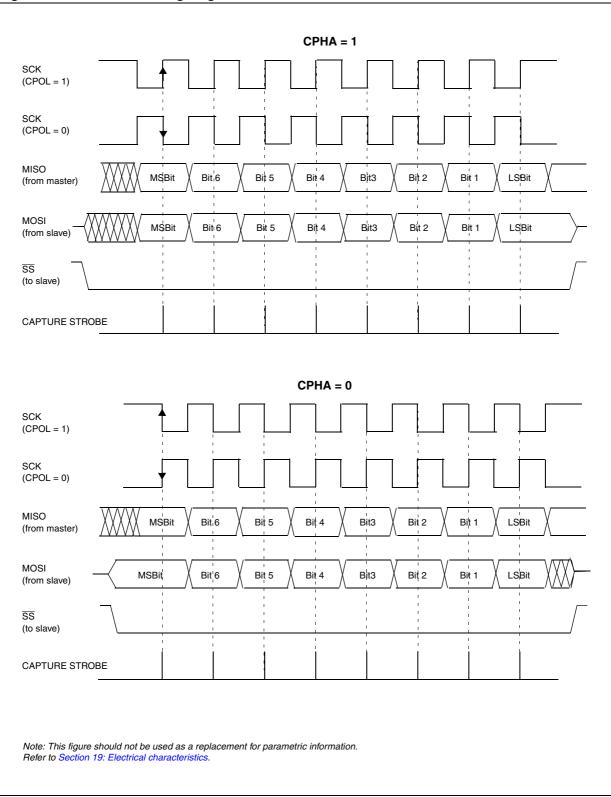

#### Figure 59. Data clock timing diagram

Doc ID 13829 Rev 1

## 15.3 General description

The interface is externally connected to another device by two pins (see *Figure 63*):

- TDO: Transmit Data Output. When the transmitter and the receiver are disabled, the output pin returns to its I/O port configuration. When the transmitter and/or the receiver are enabled and nothing is to be transmitted, the TDO pin is at high level.

- RDI: Receive Data Input is the serial data input. Oversampling techniques are used for data recovery by discriminating between valid incoming data and noise.

Through these pins, serial data is transmitted and received as frames comprising:

- An Idle Line prior to transmission or reception

- A start bit

- A data word (8 or 9 bits) least significant bit first

- A Stop bit indicating that the frame is complete

This interface uses two types of baud rate generator:

- A conventional type for commonly-used baud rates

- An extended type with a prescaler offering a very wide range of baud rates even with non-standard oscillator frequencies

## 15.4 Functional description

The block diagram of the Serial Control Interface, is shown in *Figure 62*. It contains six dedicated registers:

- 2 control registers (SCICR1 and SCICR2)

- a status register (SCISR)

- a baud rate register (SCIBRR)

- an extended prescaler receiver register (SCIERPR)

- an extended prescaler transmitter register (SCIETPR)

Refer to the register descriptions in Section 15.7 for the definitions of each bit.

#### 15.4.1 Serial data format

Word length may be selected as being either 8 or 9 bits by programming the M bit in the SCICR1 register (see *Figure 62*).

The TDO pin is in low state during the start bit.

The TDO pin is in high state during the stop bit.

An Idle character is interpreted as an entire frame of '1's followed by the start bit of the next frame which contains data.

A Break character is interpreted on receiving '0's for some multiple of the frame period. At the end of the last break frame the transmitter inserts an extra '1' bit to acknowledge the start bit.

Transmission and reception are driven by their own baud rate generator.

|   | 9-bit        | Word  | l leng |             | <b>l bit i</b><br>ta Fra | <b>s set)</b><br>ame     |       |        |       | F            | ossib<br>Parit<br>Bit | у           | N            | Ne<br>Jext                  | ext Dat      | a Frame |

|---|--------------|-------|--------|-------------|--------------------------|--------------------------|-------|--------|-------|--------------|-----------------------|-------------|--------------|-----------------------------|--------------|---------|

|   | Start<br>Bit | Bit   | ) В    | it1         | Bit2                     | Bit3                     | Bit4  | Bit5   | Bit6  | Bit7         | Bit8                  | B Sto       | op S         | Start<br>Bit                |              | -       |

|   | 8-b          | it Wo | ord le | Bre<br>ngth | -                        | <sup>me</sup><br>t is re | set)  |        |       | Possik       |                       |             | E            | Start<br>Bit<br>xtra<br>'1' | Start<br>Bit | rame    |

|   | C+/          |       |        | Da          | ta Fra                   | ame                      |       |        |       | Parit<br>Bit | t                     |             | Next         |                             |              |         |

|   | Sta<br>B     |       | Bit0   | Bit1        | Bit2                     | 2 Bit3                   | B Bit | 4 Bits | 5 Bit | 6 Bit        | 7 5                   | Stop<br>Bit | Start<br>Bit |                             |              |         |

| - | Idle Frame   |       |        |             |                          |                          |       |        |       | Start<br>Bit |                       |             |              |                             |              |         |

|   |              |       |        | Bre         | eak F                    | rame                     |       |        |       |              |                       |             | Extra<br>'1' | Star<br>Bit                 | t            | -       |

#### Figure 63. Word length programming

When an overrun error occurs:

- The OR bit is set.

- The RDR content is not lost.

- The shift register is overwritten.

- An interrupt is generated if the RIE bit is set and the I bit is cleared in the CCR register.

The OR bit is reset by an access to the SCISR register followed by a SCIDR register read operation.

#### Noise error

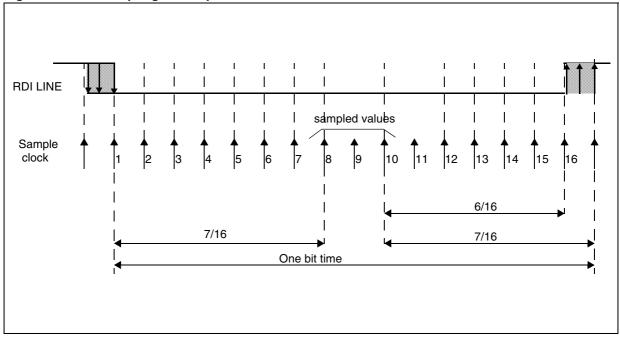

Oversampling techniques are used for data recovery by discriminating between valid incoming data and noise. Normal data bits are considered valid if three consecutive samples (8th, 9th, 10th) have the same bit value, otherwise the NF flag is set. In the case of start bit detection, the NF flag is set on the basis of an algorithm combining both valid edge detection and three samples (8th, 9th, 10th). Therefore, to prevent the NF flag getting set during start bit reception, there should be a valid edge detection as well as three valid samples.

When noise is detected in a frame:

- The NF flag is set at the rising edge of the RDRF bit.

- Data is transferred from the Shift register to the SCIDR register.

- No interrupt is generated. However this bit rises at the same time as the RDRF bit which itself generates an interrupt.

The NF flag is reset by a SCISR register read operation followed by a SCIDR register read operation.

During reception, if a false start bit is detected (for example, 8th, 9th, 10th samples are 011, 101, 110), the frame is discarded and the receiving sequence is not started for this frame. There is no RDRF bit set for this frame and the NF flag is set internally (not accessible to the user). This NF flag is accessible along with the RDRF bit when a next valid frame is received.

Note: If the application Start Bit is not long enough to match the above requirements, then the NF Flag may get set due to the short Start Bit. In this case, the NF flag may be ignored by the application software when the first valid byte is received.

See also Noise error causes on page 145.

#### Figure 65. Bit sampling in reception mode

## 15.5 Low power modes

#### Table 71. Effect of low power modes on SCI

| Mode | Effect                                                                                                     |

|------|------------------------------------------------------------------------------------------------------------|

| Wait | No effect on SCI.<br>SCI interrupts cause the device to exit from Wait mode.                               |

| Halt | SCI registers are frozen.<br>In Halt mode, the SCI stops transmitting/receiving until Halt mode is exited. |

## 15.6 Interrupts

The SCI interrupt events are connected to the same interrupt vector.

These events generate an interrupt if the corresponding Enable Control Bit is set and the interrupt mask in the CC register is reset (RIM instruction).

Table 72. SCI interrupt control/wake-up capability

| Interrupt event                | Event flag | Enable control<br>bit | Exit from<br>Wait | Exit from<br>Halt |

|--------------------------------|------------|-----------------------|-------------------|-------------------|

| Transmit Data Register Empty   | TDRE       | TIE                   | Yes               | No                |

| Transmission Complete          | TC         | TCIE                  | Yes               | No                |

| Received Data Ready to be Read | RDRF       | RIE                   | Yes               | No                |

| Overrun Error Detected         | OR         |                       | Yes               | No                |

| Address (Hex.) | Register label          | 7        | 6    | 5    | 4    | 3    | 2    | 1    | 0        |

|----------------|-------------------------|----------|------|------|------|------|------|------|----------|

| 0050h          | SCISR                   | TDRE     | TC   | RDRF | IDLE | OR   | NF   | FE   | PE       |

|                | Reset value             | 1        | 1    | 0    | 0    | 0    | 0    | 0    | 0        |

| 0051h          | SCIDR<br>Reset value    | MSB<br>x | x    | x    | x    | x    | x    | x    | LSB<br>x |

| 0052h          | SCIBRR                  | SCP1     | SCP0 | SCT2 | SCT1 | SCT0 | SCR2 | SCR1 | SCR0     |

|                | Reset value             | 0        | 0    | 0    | 0    | 0    | 0    | 0    | 0        |

| 0053h          | SCICR1                  | R8       | Т8   | SCID | M    | WAKE | PCE  | PS   | PIE      |

|                | Reset value             | x        | 0    | 0    | 0    | 0    | 0    | 0    | 0        |

| 0054h          | SCICR2                  | TIE      | TCIE | RIE  | ILIE | TE   | RE   | RWU  | SBK      |

|                | Reset value             | 0        | 0    | 0    | 0    | 0    | 0    | 0    | 0        |

| 0055h          | SCIERPR<br>Reset value  | MSB<br>0 | 0    | 0    | 0    | 0    | 0    | 0    | LSB<br>0 |

| 0057h          | SCIPETPR<br>Reset value | MSB<br>0 | 0    | 0    | 0    | 0    | 0    | 0    | LSB<br>0 |

Table 80.

SCI register map and reset values

## 16.4 Functional description

Refer to the CR, SR1 and SR2 registers in Section 16.7 for the bit definitions.

By default the I<sup>2</sup>C interface operates in Slave mode (M/SL bit is cleared) except when it initiates a transmit or receive sequence.

First the interface frequency must be configured using the FRi bits in the OAR2 register.

#### 16.4.1 Slave mode

As soon as a start condition is detected, the address is received from the SDA line and sent to the shift register; then it is compared with the address of the interface or the General Call address (if selected by software).

Note: In 10-bit addressing mode, the comparison includes the header sequence (11110xx0) and the two most significant bits of the address.

**Header matched** (10-bit mode only): The interface generates an acknowledge pulse if the ACK bit is set.

Address not matched: The interface ignores it and waits for another Start condition.

Address matched: The interface generates in sequence:

- an acknowledge pulse if the ACK bit is set

- EVF and ADSL bits are set with an interrupt if the ITE bit is set.

Then the interface waits for a read of the SR1 register, **holding the SCL line low** (see *Figure 68: Transfer sequencing* EV1).

Next, in 7-bit mode read the DR register to determine from the least significant bit (Data Direction Bit) if the slave must enter Receiver or Transmitter mode.

In 10-bit mode, after receiving the address sequence the slave is always in receive mode. It will enter transmit mode on receiving a repeated Start condition followed by the header sequence with matching address bits and the least significant bit set (11110xx1).

#### **Slave receiver**

Following the address reception and after the SR1 register has been read, the slave receives bytes from the SDA line into the DR register via the internal shift register. After each byte the interface generates in sequence:

- an acknowledge pulse if the ACK bit is set

- EVF and BTF bits are set with an interrupt if the ITE bit is set.

Then the interface waits for a read of the SR1 register followed by a read of the DR register, **holding the SCL line low** (see *Figure 68: Transfer sequencing* EV2).

#### Slave transmitter

Following the address reception and after SR1 register has been read, the slave sends bytes from the DR register to the SDA line via the internal shift register.

The slave waits for a read of the SR1 register followed by a write in the DR register, **holding the SCL line low** (see *Figure 68: Transfer sequencing* EV3).

When the acknowledge pulse is received:

• The EVF and BTF bits are set by hardware with an interrupt if the ITE bit is set.

## 16.7 Register description

## 16.7.1 I<sup>2</sup>C control register (CR)

| CR Reset value: 0000 0000 ( |          |   |    |      |       |     |      | 0000 (00h) 0000 |

|-----------------------------|----------|---|----|------|-------|-----|------|-----------------|

|                             | 7        | 6 | 5  | 4    | 3     | 2   | 1    | 0               |

|                             | Reserved |   | PE | ENGC | START | ACK | STOP | ITE             |

|                             | -        |   | RW | RW   | RW    | RW  | RW   | RW              |

Table 83. CR register description

| Bit | Name  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | -     | Reserved. Forced to 0 by hardware.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5   | PE    | <ul> <li>Peripheral enable</li> <li>This bit is set and cleared by software.</li> <li>0: Peripheral disabled</li> <li>1: Master/Slave capability</li> <li>Notes:</li> <li>When PE = 0, all the bits of the CR register and the SR register except the Stop bit are reset. All outputs are released while PE = 0</li> <li>When PE = 1, the corresponding I/O pins are selected by hardware as alternate functions.</li> <li>To enable the I<sup>2</sup>C interface, write the CR register TWICE with PE = 1 as the first write only activates the interface (only PE is set).</li> </ul> |

| 4   | ENGC  | <ul> <li>Enable General Call</li> <li>This bit is set and cleared by software. It is also cleared by hardware when the interface is disabled (PE = 0). The 00h General Call address is acknowledged (01h ignored).</li> <li>0: General Call disabled</li> <li>1: General Call enabled</li> <li>Note: In accordance with the I2C standard, when GCAL addressing is enabled, an I2C slave can only receive data. It will not transmit data to the master.</li> </ul>                                                                                                                      |

| 3   | START | <ul> <li>Generation of a Start condition</li> <li>This bit is set and cleared by software. It is also cleared by hardware when the interface is disabled (PE = 0) or when the Start condition is sent (with interrupt generation if ITE = 1).</li> <li>In Master mode</li> <li>0: No start generation</li> <li>1: Repeated start generation</li> <li>In Slave mode</li> <li>0: No start generation</li> <li>1: Start generation when the bus is free</li> </ul>                                                                                                                         |

| 2   | ACK   | <ul> <li>Acknowledge enable</li> <li>This bit is set and cleared by software. It is also cleared by hardware when the interface is disabled (PE = 0).</li> <li>0: No acknowledge returned</li> <li>1: Acknowledge returned after an address byte or a data byte is received</li> </ul>                                                                                                                                                                                                                                                                                                  |

|          | Mode     |          | Syntax              | Destination | Pointer<br>address<br>(Hex.) | Pointer<br>size<br>(Hex.) | Length<br>(bytes) |

|----------|----------|----------|---------------------|-------------|------------------------------|---------------------------|-------------------|

| Long     | Indirect | Indexed  | ld A,([\$10.w],X)   | 0000FFFF    | 00FF                         | word                      | + 2               |

| Relative | Direct   |          | jrne loop           | PC+/-127    |                              |                           | + 1               |

| Relative | Indirect |          | jrne [\$10]         | PC+/-127    | 00FF                         | byte                      | + 2               |

| Bit      | Direct   |          | bset \$10,#7        | 00FF        |                              |                           | + 1               |

| Bit      | Indirect |          | bset [\$10],#7      | 00FF        | 00FF                         | byte                      | + 2               |

| Bit      | Direct   | Relative | btjt \$10,#7,skip   | 00FF        |                              |                           | + 2               |

| Bit      | Indirect | Relative | btjt [\$10],#7,skip | 00FF        | 00FF                         | byte                      | + 3               |

Table 97. CPU addressing mode overview (continued)

#### 18.1.1 Inherent

All Inherent instructions consist of a single byte. The opcode fully specifies all the required information for the CPU to process the operation.

| Instruction             | Function                            |

|-------------------------|-------------------------------------|

| NOP                     | No operation                        |

| TRAP                    | S/W Interrupt                       |

| WFI                     | Wait For Interrupt (Low Power Mode) |

| HALT                    | Halt Oscillator (Lowest Power Mode) |

| RET                     | Sub-routine Return                  |

| IRET                    | Interrupt Sub-routine Return        |

| SIM                     | Set Interrupt Mask (level 3)        |

| RIM                     | Reset Interrupt Mask (level 0)      |

| SCF                     | Set Carry Flag                      |

| RCF                     | Reset Carry Flag                    |

| RSP                     | Reset Stack Pointer                 |

| LD                      | Load                                |

| CLR                     | Clear                               |

| PUSH/POP                | Push/Pop to/from the stack          |

| INC/DEC                 | Increment/Decrement                 |

| TNZ                     | Test Negative or Zero               |

| CPL, NEG                | 1 or 2 Complement                   |

| MUL                     | Byte Multiplication                 |

| SLL, SRL, SRA, RLC, RRC | Shift and Rotate Operations         |

| SWAP                    | Swap Nibbles                        |

## **19.3.2** Operating conditions with low voltage detector (LVD)

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$ .

| Symbol                | Parameter                                                       | Conditions                                    | Min                 | Тур  | Max                 | Unit |

|-----------------------|-----------------------------------------------------------------|-----------------------------------------------|---------------------|------|---------------------|------|

|                       |                                                                 | VD level = High in option byte                | 4.0 <sup>(1)</sup>  | 4.2  | 4.5                 |      |

| V <sub>IT+(LVD)</sub> | Reset release threshold<br>(V <sub>DD</sub> rise)               | VD level = Med. in option byte <sup>(2)</sup> | 3.55 <sup>(1)</sup> | 3.75 | 4.0 <sup>(1)</sup>  |      |

|                       |                                                                 | VD level = Low in option byte <sup>(2)</sup>  | 2.95 <sup>(1)</sup> | 3.15 | 3.35 <sup>(1)</sup> | v    |

| V <sub>IT-(LVD)</sub> |                                                                 | VD level = High in option byte                | 3.8                 | 4.0  | 4.25 <sup>(1)</sup> | v    |

|                       | Reset generation threshold<br>(V <sub>DD</sub> fall)            | VD level = Med. in option byte <sup>(2)</sup> | 3.35 <sup>(1)</sup> | 3.55 | 3.75 <sup>(1)</sup> |      |

|                       |                                                                 | VD level = Low in option byte <sup>(2)</sup>  | 2.8 <sup>(1)</sup>  | 3.0  | 3.15 <sup>(1)</sup> |      |

| V <sub>hys(LVD)</sub> | LVD voltage threshold<br>hysteresis                             | V <sub>IT+(LVD)</sub> -V <sub>IT-(LVD)</sub>  |                     | 200  |                     | mV   |

| Vt <sub>POR</sub>     | V <sub>DD</sub> rise time <sup>(2)(3)</sup>                     | LVD enabled                                   | 6µs/V               |      | 100ms/V             | -    |

| t <sub>g(VDD)</sub>   | $V_{DD}$ glitches filtered (not detected) by LVD <sup>(4)</sup> |                                               |                     |      | 40                  | ns   |

#### Table 108. Operating conditions with low voltage detector (LVD)

1. Data based on characterization results, tested in production for ROM devices only

2. Data based on characterization results, not tested in production

3. When  $Vt_{POR}$  is faster than 100µs/V, the Reset signal is released after a delay of maximum 42µs after  $V_{DD}$  crosses the  $V_{IT+(LVD)}$  threshold.

4. If the medium or low thresholds are selected, the detection may occur outside the specified operating voltage range. Below 3.8V, device operation is not guaranteed.

## 19.3.3 Auxiliary voltage detector (AVD) thresholds

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$ .

| Table 109. | Auxiliary voltage | e detector (AVD | ) thresholds |

|------------|-------------------|-----------------|--------------|

|------------|-------------------|-----------------|--------------|

| Symbol                | Parameter                                                 | Conditions                                      | Min                 | Тур  | Max                 | Unit |  |  |

|-----------------------|-----------------------------------------------------------|-------------------------------------------------|---------------------|------|---------------------|------|--|--|

| V <sub>IT+(AVD)</sub> | 1⇒0 AVDF flag toggle threshold ( $V_{DD}$ rise)           | VD level = High in option byte                  | 4.4 <sup>(1)</sup>  | 4.6  | 4.9 <sup>(1)</sup>  |      |  |  |

|                       |                                                           | VD level = Med. in option byte                  | 3.95 <sup>(1)</sup> | 4.15 | 4.4 <sup>(1)</sup>  |      |  |  |

|                       |                                                           | VD level = Low in option byte                   |                     | 3.6  | 3.8 <sup>(1)</sup>  | v    |  |  |

| V <sub>IT-(AVD)</sub> | 0⇒1 AVDF flag toggle threshold<br>(V <sub>DD</sub> fall)  | VD level = High in option byte                  | 4.2 <sup>(1)</sup>  | 4.4  | 4.65 <sup>(1)</sup> | V    |  |  |

|                       |                                                           | VD level = Med. in option byte                  | 3.75 <sup>(1)</sup> | 4.0  | 4.2 <sup>(1)</sup>  |      |  |  |

|                       |                                                           | VD level = Low in option byte                   | 3.2 <sup>(1)</sup>  | 3.4  | 3.6 <sup>(1)</sup>  |      |  |  |

| V <sub>hys(AVD)</sub> | AVD voltage threshold hysteresis                          | V <sub>IT+(AVD)</sub> -V <sub>IT-(AVD)</sub> 20 |                     | 200  |                     |      |  |  |

| ΔV <sub>IT-</sub>     | Voltage drop between AVD flag set and LVD reset activated | V <sub>IT-(AVD)</sub> -V <sub>IT-(LVD)</sub>    |                     | 450  |                     | mV   |  |  |

1. Data based on characterization results, tested in production for ROM devices only

#### **19.8.2** Output driving current

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$  unless otherwise specified.

#### Table 127. Output driving current

| Symbol                         | Parameter                                                                                                                             | Conditions           |                                                                     | Min                                            | Мах        | Unit |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------------------------------------------------------|------------------------------------------------|------------|------|

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for a standard I/O pin<br>when 8 pins are sunk at same time<br>(see <i>Figure 84</i> )                       | V <sub>DD</sub> = 5V | I <sub>IO</sub> = +5mA                                              |                                                | 1.2        | V    |

|                                |                                                                                                                                       |                      | $I_{IO} = +2mA$                                                     |                                                | 0.5        |      |

|                                | Output low level voltage for a high sink I/O pin<br>when 4 pins are sunk at same time<br>(see <i>Figure 85</i> and <i>Figure 87</i> ) |                      | $I_{IO} = +20mA,$<br>$T_A \le 85^{\circ}C$<br>$T_A \ge 85^{\circ}C$ |                                                | 1.3<br>1.5 |      |

|                                |                                                                                                                                       |                      | I <sub>IO</sub> = +8mA                                              |                                                | 0.6        |      |

| V <sub>OH</sub> <sup>(2)</sup> | Output high level voltage for an I/O pin<br>when 4 pins are sourced at same time<br>(see <i>Figure 86</i> and <i>Figure 89</i> )      |                      | $I_{IO} = -5mA,$<br>$T_A \le 85^{\circ}C$<br>$T_A \ge 85^{\circ}C$  | V <sub>DD</sub> - 1.4<br>V <sub>DD</sub> - 1.6 |            |      |

|                                |                                                                                                                                       |                      | I <sub>IO</sub> = -2mA                                              | V <sub>DD</sub> - 0.7                          |            |      |

1. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in Section 19.2.2 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. The I<sub>IO</sub> current sourced must always respect the absolute maximum rating specified in Section 19.2.2 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>. True open-drain I/O pins do not have V<sub>OH</sub>.

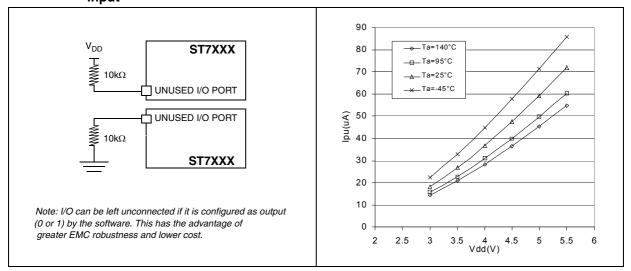

## Figure 83. Typical $I_{PU}$ vs $V_{DD}$ with $V_{IN} = V_{SS}$

ST72321xx-Auto

# 21.2 ROM device ordering information and transfer of customer code

Customer code is made up of the ROM/FASTROM contents and the list of the selected options (if any). The ROM/FASTROM contents are to be sent on diskette, or by electronic means, with the S19 hexadecimal file generated by the development tool. All unused bytes must be set to FFh.

Complete the appended **Option list** *on page 230* to communicate the selected options to STMicroelectronics and check for regular updates of the option list on the ST website or ask your ST representative.

Refer to application note AN1635 for information on the counter listing returned by ST after code has been transferred.

The following *Figure 106* and *Figure 107* serve as guides for ordering. The STMicroelectronics Sales Organization will be pleased to provide detailed information on contractual points.

**Caution:** The Readout Protection binary value is inverted between ROM and Flash products. The option byte checksum will differ between ROM and Flash.

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2010 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

Doc ID 13829 Rev 1