# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | I²C, SCI, SPI                                                        |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 32                                                                   |

| Program Memory Size        | 48KB (48K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 1.5K x 8                                                             |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                          |

| Data Converters            | A/D 16x10b                                                           |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 44-LQFP                                                              |

| Supplier Device Package    | -                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f321j7ta |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 101.               | Available relative direct/indirect instructions              | . 181 |

|--------------------------|--------------------------------------------------------------|-------|

| Table 102.               | Instruction groups                                           |       |

| Table 103.               | Instruction set overview                                     |       |

| Table 104.               | Voltage characteristics                                      |       |

| Table 105.               | Current characteristics                                      |       |

| Table 106.               | Thermal characteristics.                                     |       |

| Table 107.               | General operating conditions                                 |       |

| Table 108.               | Operating conditions with low voltage detector (LVD)         |       |

| Table 109.               | Auxiliary voltage detector (AVD) thresholds                  |       |

| Table 110.               | External voltage detector (EVD) thresholds                   |       |

| Table 111.               | Current consumption                                          |       |

| Table 112.               | Oscillators, PLL and LVD current consumption                 |       |

| Table 113.               | On-chip peripherals current consumption.                     |       |

| Table 114.               | General timings.                                             |       |

| Table 115.               | External clock source                                        |       |

| Table 116.               | Crystal and ceramic resonator oscillators                    |       |

| Table 117.               | OSCRANGE selection for typical resonators                    |       |

| Table 118.               | RC oscillator characteristics                                |       |

| Table 119.               | PLL characteristics                                          |       |

| Table 119.               | RAM supply voltage                                           |       |

| Table 120.               | Dual voltage HDFlash memory                                  |       |

| Table 121.               | EMS test results                                             |       |

| Table 122.<br>Table 123. | EMI emissions                                                |       |

|                          |                                                              |       |

| Table 124.               | ESD absolute maximum ratings                                 |       |

| Table 125.               | Electrical sensitivities                                     |       |

| Table 126.               | I/O port pin general characteristics                         |       |

| Table 127.               |                                                              |       |

| Table 128.               | Asynchronous RESET pin characteristics                       |       |

| Table 129.               | ICCSEL/V <sub>PP</sub> pin characteristics                   |       |

| Table 130.               | 8-bit PWM-ART auto-reload timer characteristics.             |       |

| Table 131.               | 16-bit timer characteristics                                 |       |

| Table 132.               | SPI characteristics                                          |       |

| Table 133.               | I <sup>2</sup> C control interface characteristics           |       |

| Table 134.               | SCL frequency table                                          |       |

| Table 135.               | 10-bit ADC characteristics                                   |       |

| Table 136.               | ADC accuracy                                                 |       |

| Table 137.               | 64-pin (14x14) low profile quad flat package mechanical data |       |

| Table 138.               | 64-pin (10x10) low profile quad flat package mechanical data |       |

| Table 139.               | Thermal characteristics.                                     |       |

| Table 140.               | Flash option bytes                                           |       |

| Table 141.               | Option byte 0 bit description                                | . 224 |

| Table 142.               | Option byte 1 bit description                                | . 225 |

| Table 143.               | Package selection (OPT7)                                     | . 225 |

| Table 144.               | STMicroelectronics development tools                         | . 232 |

| Table 145.               | Suggested list of socket types                               | . 232 |

| Table 146.               | Document revision history                                    | . 242 |

14/243

| Figure 101. | ADC error classification                              | 219 |

|-------------|-------------------------------------------------------|-----|

| Figure 102. | 64-pin (14x14) low profile quad flat package outline  | 220 |

| Figure 103. | 64-pin (10x10) low profile quad flat package outline  | 221 |

| Figure 104. | Pin 1 orientation in tape and reel conditioning       | 222 |

| Figure 105. | ST72F321xxx-Auto Flash commercial product structure   | 226 |

| Figure 106. | ST72P321xxx-Auto FastROM commercial product structure | 228 |

| Figure 107. | ST72321xxx-Auto ROM commercial product structure.     | 229 |

| Figure 108. | LVD startup behavior                                  | 241 |

| Bit | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Z    | <ul> <li>Zero</li> <li>This bit is set and cleared by hardware. This bit indicates that the result of the last arithmetic, logical or data manipulation is zero.</li> <li>0: The result of the last operation is different from zero.</li> <li>1: The result of the last operation is zero.</li> <li>This bit is accessed by the JREQ and JRNE test instructions.</li> </ul>                                                                                                                       |

| 0   | С    | <ul> <li><i>Carry/borrow</i></li> <li>This bit is set and cleared by hardware and software. It indicates an overflow or an underflow has occurred during the last arithmetic operation.</li> <li>0: No overflow or underflow has occurred.</li> <li>1: An overflow or underflow has occurred.</li> <li>This bit is driven by the SCF and RCF instructions and tested by the JRC and JRNC instructions. It is also affected by the "bit test and branch", shift and rotate instructions.</li> </ul> |

## Table 7. Arithmetic management bits (continued)

#### Table 8.Interrupt management bits

| Bit | Name | Function                                                                                                              |  |  |  |  |  |  |

|-----|------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 5   | 11   | Interrupt Software Priority 1<br>The combination of the I1 and I0 bits gives the current interrupt software priority. |  |  |  |  |  |  |

| 3   | 10   | Interrupt Software Priority 0<br>The combination of the I1 and I0 bits gives the current interrupt software priority. |  |  |  |  |  |  |

#### Table 9. Interrupt software priority selection

| Interrupt software priority   | Level | 11 | 10 |

|-------------------------------|-------|----|----|

| Level 0 (main)                | Low   | 1  | 0  |

| Level 1                       |       | 0  | 1  |

| Level 2                       | ↓     | 0  | 0  |

| Level 3 (= interrupt disable) | High  | 1  | 1  |

These two bits are set/cleared by hardware when entering in interrupt. The loaded value is given by the corresponding bits in the interrupt software priority registers (ISPRx). They can be also set/cleared by software with the RIM, SIM, IRET, HALT, WFI and PUSH/POP instructions.

See Chapter 7: Interrupts on page 49 for more details.

## 5.3.5 Stack pointer (SP) register

| SP |    |    |    |    |    |    |   |   |     |     | Re  | eset va | alue: 0 | 1 FFh |     |     |  |

|----|----|----|----|----|----|----|---|---|-----|-----|-----|---------|---------|-------|-----|-----|--|

|    | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7   | 6   | 5   | 4       | 3       | 2     | 1   | 0   |  |

|    | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 1 | SP7 | SP6 | SP5 | SP4     | SP3     | SP2   | SP1 | SP0 |  |

|    |    |    |    |    |    |    |   |   | RW  | RW  | RW  | RW      | RW      | RW    | RW  | RW  |  |

Doc ID 13829 Rev 1

57

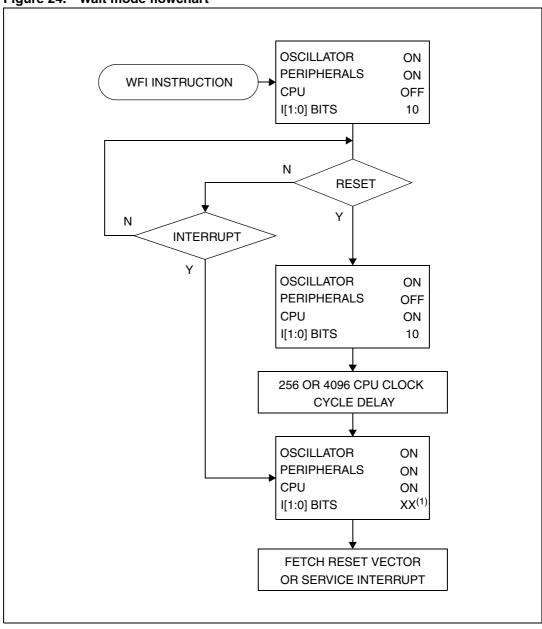

Figure 24. Wait mode flowchart

Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits of the CC register are set to the current software priority level of the interrupt routine and recovered when the CC register is popped.

|        |                     | Juneari (Corrent |                    |                  |           |  |  |

|--------|---------------------|------------------|--------------------|------------------|-----------|--|--|

| Port   | Pin name            | Input (L         | 0DR = 0)           | Output (DDR = 1) |           |  |  |

| TOIL   | T in name           | OR = 0           | OR = 0 OR = 1      |                  | OR = 1    |  |  |

| Port B | PB7, PB3            | floating         | floating interrupt | open-drain       | push-pull |  |  |

| FULD   | PB6:5, PB4, PB2:0   | floating         | pull-up interrupt  | open-drain       | push-pull |  |  |

| Port C | PC7:0               | floating         | pull-up            | open-drain       | push-pull |  |  |

| Port D | PD7:0               | floating         | pull-up            | open-drain       | push-pull |  |  |

|        | PE7:3, PE1:0        | floating         | pull-up            | open drain       | push-pull |  |  |

| Port E | PE2 (Flash devices) |                  | pull-up ir         | nput only        |           |  |  |

|        | PE2 (ROM devices)   | floa             | ting               | open drain       | push-pull |  |  |

|        | PF7:3               | floating         | pull-up            | open-drain       | push-pull |  |  |

| Port F | PF2                 | floating         | floating interrupt | open-drain       | push-pull |  |  |

|        | PF1:0               | floating         | pull-up interrupt  | open-drain       | push-pull |  |  |

Table 31.

I/O port configuration (continued)

## 9.4 Low power modes

#### Table 32. Effect of low power modes on I/O ports

| Mode | Effect                                                                               |

|------|--------------------------------------------------------------------------------------|

| Wait | No effect on I/O ports. External interrupts cause the device to exit from Wait mode. |

| Halt | No effect on I/O ports. External interrupts cause the device to exit from Halt mode. |

## 9.5 Interrupts

The external interrupt event generates an interrupt if the corresponding configuration is selected with DDR and OR registers and the interrupt mask in the CC register is not active (RIM instruction).

Table 33.

I/O port interrupt control/wake-up capability

| Interrupt event                               | Event flag | Enable<br>control bit | Exit from<br>Wait | Exit from<br>Halt |  |

|-----------------------------------------------|------------|-----------------------|-------------------|-------------------|--|

| External interrupt on selected external event | -          | DDRx, ORx             | Yes               | Yes               |  |

Table 34. I/O port register map and reset values

| Address (Hex.)                        | Register label | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|---------------------------------------|----------------|-----|---|---|---|---|---|---|-----|

| Reset value of all I/O port registers |                | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0   |

| 0000h                                 | PADR           |     |   |   |   |   |   |   |     |

| 0001h                                 | PADDR          | MSB |   |   |   |   |   |   | LSB |

| 0002h                                 | PAOR           |     |   |   |   |   |   |   |     |

## Figure 33. Exact timeout duration (t<sub>min</sub> and t<sub>max</sub>)

#### WHERE:

t<sub>min0</sub> = (LSB + 128) x 64 x t<sub>OSC2</sub>

$t_{max0} = 16384 \text{ x } t_{OSC2}$

$t_{OSC2} = 125$ ns if  $f_{OSC2} = 8$  MHz

CNT = Value of T[5:0] bits in the WDGCR register (6 bits)

MSB and LSB are values from the table below depending on the timebase selected by the TB[1:0] bits in the MCCSR register

| TB1 bit<br>(MCCSR reg.) | TB0 bit<br>(MCCSR reg.) | Selected MCCSR timebase | MSB | LSB |

|-------------------------|-------------------------|-------------------------|-----|-----|

| 0                       | 0                       | 2ms                     | 4   | 59  |

| 0                       | 1                       | 4ms                     | 8   | 53  |

| 1                       | 0                       | 10ms                    | 20  | 35  |

| 1                       | 1                       | 25ms                    | 49  | 54  |

To calculate the minimum Watchdog Timeout (t<sub>min</sub>):

**IF** CNT <

$$\left[\frac{\text{MSB}}{4}\right]$$

**THEN**

$$t_{min} = t_{min0} + 16384 \times CNT \times t_{osc2}$$

**ELSE**  $t_{min} = t_{min0} + \left[ 16384 \times \left( CNT - \left[ \frac{4CNT}{MSB} \right] \right) + (192 + LSB) \times 64 \times \left[ \frac{4CNT}{MSB} \right] \right] \times t_{osc2}$

To calculate the maximum Watchdog Timeout (t<sub>max</sub>):

$$\begin{aligned} \textbf{IF} \ \textbf{CNT} \leq & \left[\frac{\textbf{MSB}}{4}\right] & \textbf{THEN} \ \textbf{t}_{max} = \textbf{t}_{max0} + 16384 \times \textbf{CNT} \times \textbf{t}_{osc2} \\ & \textbf{ELSE} \ \textbf{t}_{max} = \textbf{t}_{max0} + \left[16384 \times \left(\textbf{CNT} - \left[\frac{4\textbf{CNT}}{\textbf{MSB}}\right]\right) + (192 + \textbf{LSB}) \times 64 \times \left[\frac{4\textbf{CNT}}{\textbf{MSB}}\right]\right] \times \textbf{t}_{osc2} \end{aligned}$$

**Note:** In the above formulae, division results must be rounded down to the next integer value. **Example:**

With 2ms timeout selected in MCCSR register

| Value of T[5:0] bits in<br>WDGCR register (Hex.) | Min. Watchdog<br>Timeout (ms)<br>t <sub>min</sub> | Max. Watchdog<br>Timeout (ms)<br>t <sub>max</sub> |

|--------------------------------------------------|---------------------------------------------------|---------------------------------------------------|

| 00                                               | 1.496                                             | 2.048                                             |

| 3F                                               | 128                                               | 128.552                                           |

# 11.6 Low power modes

### Table 38. Effect of low power modes on MCC/RTC

| Mode        | Effect                                                                                                                                               |  |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Wait        | No effect on MCC/RTC peripheral.<br>MCC/RTC interrupt causes the device to exit from Wait mode.                                                      |  |  |  |

| Active Halt | No effect on MCC/RTC counter (OIE bit is set), the registers are frozen.<br>MCC/RTC interrupt causes the device to exit from Active Halt mode.       |  |  |  |

| Halt        | MCC/RTC counter and registers are frozen.<br>MCC/RTC operation resumes when the MCU is woken up by an interrupt with<br>"exit from HALT" capability. |  |  |  |

# 11.7 Interrupts

The MCC/RTC interrupt event generates an interrupt if the OIE bit of the MCCSR register is set and the interrupt mask in the CC register is not active (RIM instruction).

Table 39. MCC/RTC interrupt control/wake-up capability

| Interrupt event          | Event flag | Event flag Enable control bit |     | Exit from<br>Halt |

|--------------------------|------------|-------------------------------|-----|-------------------|

| Time base overflow event | OIF        | OIE                           | Yes | No <sup>(1)</sup> |

1. The MCC/RTC interrupt wakes up the MCU from Active Halt mode, not from Halt mode.

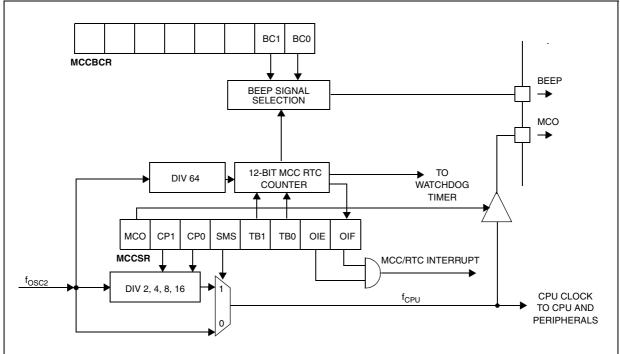

# 11.8 Main clock controller registers

# 11.8.1 MCC control/status register (MCCSR)

| MCCSR | t value: 0000 | 0000 (00h) 0000 |     |     |         |    |     |

|-------|---------------|-----------------|-----|-----|---------|----|-----|

| 7     | 6             | 5               | 4   | 3   | 2       | 1  | 0   |

| MCO   | CP[1:0]       |                 | SMS | TB[ | TB[1:0] |    | OIF |

| RW    | RW            |                 | RW  | RW  |         | RW | RW  |

| Bit | Name           | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | МСО            | <ul> <li>Main clock out selection</li> <li>This bit enables the MCO alternate function on the PF0 I/O port. It is set and cleared by software.</li> <li>0: MCO alternate function disabled (I/O pin free for general-purpose I/O)</li> <li>1: MCO alternate function enabled (f<sub>CPU</sub> on I/O port)</li> <li>Note: To reduce power consumption, the MCO function is not active in Active Halt mode.</li> </ul>                                                           |

| 6:5 | CP[1:0]        | CPU clock prescalerThese bits select the CPU clock prescaler which is applied in the different slowmodes. Their action is conditioned by the setting of the SMS bit. These two bits areset and cleared by software.00: $f_{CPU}$ in Slow mode = $f_{OSC2}/2$ 01: $f_{CPU}$ in Slow mode = $f_{OSC2}/4$ 10: $f_{CPU}$ in Slow mode = $f_{OSC2}/4$ 10: $f_{CPU}$ in Slow mode = $f_{OSC2}/4$ 10: $f_{CPU}$ in Slow mode = $f_{OSC2}/4$ 11: $f_{CPU}$ in Slow mode = $f_{OSC2}/16$ |

| 4   | SMS            | Slow mode select<br>This bit is set and cleared by software.<br>0: Normal mode. f <sub>CPU</sub> = f <sub>OSC2</sub><br>1: Slow mode. f <sub>CPU</sub> is given by CP1, CP0<br>See Section 8.2: Slow mode on page 62 and Chapter 11: Main clock controller with<br>real-time clock and beeper (MCC/RTC) for more details.                                                                                                                                                       |

| 3:2 | TB[1:0]<br>OIE | <i>Time base control</i><br>These bits select the programmable divider time base. They are set and cleared by software (see <i>Table 41</i> ).<br>A modification of the time base is taken into account at the end of the current period (previously set) to avoid an unwanted time shift. This allows to use this time base as a real-time clock.                                                                                                                              |

| 1   |                | Oscillator interrupt enable<br>This bit set and cleared by software.<br>0: Oscillator interrupt disabled<br>1: Oscillator interrupt enabled<br>This interrupt can be used to exit from Active Halt mode.<br>When this bit is set, calling the ST7 software HALT instruction enters the Active Halt<br>power saving mode.                                                                                                                                                        |

|                          | · · · · · · · · · · · · · · · · · · · |     |     |     |

|--------------------------|---------------------------------------|-----|-----|-----|

| fcounter                 | With f <sub>INPUT</sub> = 8 MHz       | CC2 | CC1 | CC0 |

| f <sub>INPUT</sub> / 8   | 1 MHz                                 | 0   | 1   | 1   |

| f <sub>INPUT</sub> / 16  | 500 kHz                               | 1   | 0   | 0   |

| f <sub>INPUT</sub> / 32  | 250 kHz                               | 1   | 0   | 1   |

| f <sub>INPUT</sub> / 64  | 125 kHz                               | 1   | 1   | 0   |

| f <sub>INPUT</sub> / 128 | 62.5 kHz                              | 1   | 1   | 1   |

Table 46.

Prescaler selection for ART (continued)

## 12.3.2 Counter access register (ARTCAR)

| ARTCAR  |   | Reset value: 00 |   |   |   |   | 0000 (00h) |  |

|---------|---|-----------------|---|---|---|---|------------|--|

| 7       | 6 | 5               | 4 | 3 | 2 | 1 | 0          |  |

| CA[7:0] |   |                 |   |   |   |   |            |  |

| RW      |   |                 |   |   |   |   |            |  |

## Table 47. ARTCAR register description

| Bit | Name    | Function                                                                                                                                                                                                    |

|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | CA[7:0] | Counter Access Data<br>These bits can be set and cleared either by hardware or by software. The<br>ARTCAR register is used to read or write the auto-reload counter "on the fly"<br>(while it is counting). |

## 12.3.3 Auto-reload register (ARTARR)

## Table 48. ARTAAR register description

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                             |

|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | AR[7:0] | Counter Auto-Reload Data<br>These bits are set and cleared by software. They are used to hold the auto-reload<br>value which is automatically loaded in the counter when an overflow occurs. At the<br>same time, the PWM output levels are changed according to the corresponding<br>OPx bit in the PWMCR register. |

This register has two PWM management functions:

- Adjusting the PWM frequency

- Setting the PWM duty cycle resolution

The OC1R register value required for a specific timing application can be calculated using the following formula:

$$OC_{i}R value = \frac{t \cdot f_{CPU} - 5}{PRESC}$$

Where:

t

= Pulse period (in seconds)

$f_{CPU}$  = CPU clock frequency (in hertz)

PRESC = Timer prescaler factor (2, 4 or 8 depending on the CC[1:0] bits; see *Table 61: Timer clock selection*)

If the timer clock is an external clock the formula is:

$OCiR = t * f_{EXT} - 5$

Where: t

= Pulse period (in seconds)

f<sub>EXT</sub> = External clock frequency (in hertz)

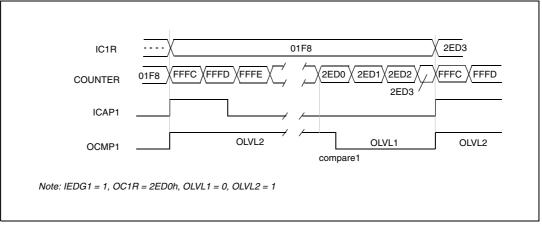

When the value of the counter is equal to the value of the contents of the OC1R register, the OLVL1 bit is output on the OCMP1 pin (see *Figure 52*).

- Note: 1 The OCF1 bit cannot be set by hardware in one pulse mode but the OCF2 bit can generate an Output Compare interrupt.

- 2 When the Pulse Width Modulation (PWM) and One Pulse Mode (OPM) bits are both set, the PWM mode is the only active one.

- 3 If OLVL1 = OLVL2 a continuous signal will be seen on the OCMP1 pin.

- 4 The ICAP1 pin cannot be used to perform input capture. The ICAP2 pin can be used to perform input capture (ICF2 can be set and IC2R can be loaded) but the user must take care that the counter is reset each time a valid edge occurs on the ICAP1 pin and ICF1 can also generates interrupt if ICIE is set.

- 5 When one pulse mode is used OC1R is dedicated to this mode. Nevertheless OC2R and OCF2 can be used to indicate a period of time has been elapsed but cannot generate an output waveform because the level OLVL2 is dedicated to the one pulse mode.

Figure 52. One pulse mode timing example

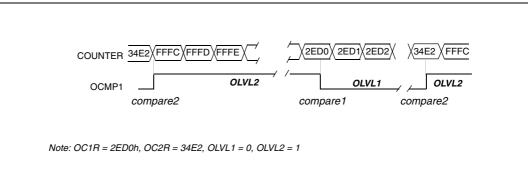

# Figure 53. Pulse width modulation mode timing example with 2 output compare functions

Note:

On timers with only one Output Compare register, a fixed frequency PWM signal can be generated using the output compare and the counter overflow to define the pulse length.

## 13.3.7 Pulse width modulation mode

Pulse Width Modulation (PWM) mode enables the generation of a signal with a frequency and pulse length determined by the value of the OC1R and OC2R registers.

Pulse Width Modulation mode uses the complete Output Compare 1 function plus the OC2R register, and so this functionality cannot be used when PWM mode is activated.

In PWM mode, double buffering is implemented on the output compare registers. Any new values written in the OC1R and OC2R registers are taken into account only at the end of the PWM period (OC2) to avoid spikes on the PWM output pin (OCMP1).

## Procedure

To use pulse width modulation mode:

- 1. Load the OC2R register with the value corresponding to the period of the signal using the appropriate formula below according to the timer clock source used.

- Load the OC1R register with the value corresponding to the period of the pulse if OLVL1 = 0 and OLVL2 = 1 using the appropriate formula below according to the timer clock source used.

- 3. Select the following in the CR1 register:

- Using the OLVL1 bit, select the level to be applied to the OCMP1 pin after a successful comparison with the OC1R register.

- Using the OLVL2 bit, select the level to be applied to the OCMP1 pin after a successful comparison with the OC2R register.

- 4. Select the following in the CR2 register:

- Set OC1E bit: the OCMP1 pin is then dedicated to the output compare 1 function.

- Set the PWM bit.

- Select the timer clock (CC[1:0]) (see *Table 61: Timer clock selection*).

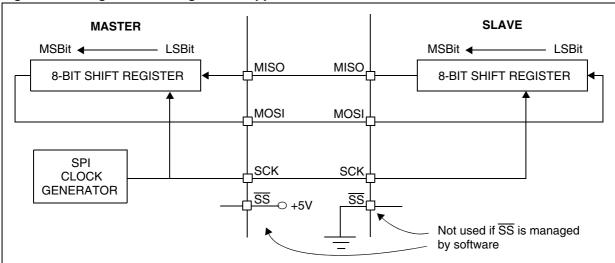

#### Figure 56. Single master/single slave application

## 14.3.2 Slave select management

As an alternative to using the  $\overline{SS}$  pin to control the Slave Select signal, the application can choose to manage the Slave Select signal by software. This is configured by the SSM bit in the SPICSR register (see *Figure 58*)

In software management, the external  $\overline{SS}$  pin is free for other application uses and the internal  $\overline{SS}$  signal level is driven by writing to the SSI bit in the SPICSR register.

#### In Master mode

• SS internal must be held high continuously

#### In Slave mode

There are two cases depending on the data/clock timing relationship (see *Figure 57*):

If CPHA = 1 (data latched on 2nd clock edge):

SS internal must be held low during the entire transmission. This implies that in single slave applications the SS pin either can be tied to V<sub>SS</sub>, or made free for standard I/O by managing the SS function by software (SSM = 1 and SSI = 0 in the in the SPICSR register)

If CPHA = 0 (data latched on 1st clock edge):

• SS internal must be held low during byte transmission and pulled high between each byte to allow the slave to write to the shift register. If SS is not pulled high, a Write Collision error will occur when the slave writes to the shift register (see *Write collision error (WCOL) on page 128*).

# Warning: A write to the SPIDR register places data directly into the shift register for transmission.

A read to the SPIDR register returns the value located in the buffer and not the content of the shift register (see *Figure 55*).

| Address<br>(Hex.) | Register<br>label     | 7         | 6         | 5         | 4         | 3         | 2         | 1         | 0         |

|-------------------|-----------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| 0021h             | SPIDR<br>Reset value  | MSB<br>x  | x         | x         | x         | х         | х         | х         | LSB<br>x  |

| 0022h             | SPICR<br>Reset value  | SPIE<br>0 | SPE<br>0  | SPR2<br>0 | MSTR<br>0 | CPOL<br>x | CPHA<br>x | SPR1<br>x | SPR0<br>x |

| 0023h             | SPICSR<br>Reset value | SPIF<br>0 | WCOL<br>0 | OVR<br>0  | MODF<br>0 | 0         | SOD<br>0  | SSM<br>0  | SSI<br>0  |

Table 69. SPI register map and reset values

# 15.7.2 Control register 1 (SCICR1)

| SCICR1 |    |    |      |    |      |     | Reset value: X000 0000 (x0h) |     |  |  |

|--------|----|----|------|----|------|-----|------------------------------|-----|--|--|

|        | 7  | 6  | 5    | 4  | 3    | 2   | 1                            | 0   |  |  |

|        | R8 | Т8 | SCID | М  | WAKE | PCE | PS                           | PIE |  |  |

|        | RW | RW | RW   | RW | RW   | RW  | RW                           | RW  |  |  |

## Table 74. SCICR1 register description

| Bit | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7   | R8   | Receive data bit 8<br>This bit is used to store the 9th bit of the received word when $M = 1$ .                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 6   | Т8   | <i>Transmit data bit 8</i><br>This bit is used to store the 9th bit of the transmitted word when $M = 1$ .                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 5   | SCID | <ul> <li>Disabled for low power consumption</li> <li>When this bit is set the SCI prescalers and outputs are stopped and the end of the current byte transfer in order to reduce power consumption. This bit is set and cleared by software.</li> <li>0: SCI enabled</li> <li>1: SCI prescaler and outputs disabled</li> </ul>                                                                                                                                                                                |  |  |  |  |  |

| 4   | М    | <ul> <li>Word length</li> <li>This bit determines the word length. It is set or cleared by software.</li> <li>0: 1 Start bit, 8 Data bits, 1 Stop bit</li> <li>1: 1 Start bit, 9 Data bits, 1 Stop bit</li> <li>Note: The M bit must not be modified during a data transfer (both transmission and reception).</li> </ul>                                                                                                                                                                                     |  |  |  |  |  |

| 3   | WAKE | Wake-up method<br>This bit determines the SCI wake-up method. It is set or cleared by software.<br>0: Idle line<br>1: Address mark                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 2   | PCE  | <ul> <li>Parity control enable</li> <li>This bit selects the hardware parity control (generation and detection). When the parity control is enabled, the computed parity is inserted at the MSB position (9th bit if M = 1; 8th bit if M = 0) and parity is checked on the received data. This bit is set and cleared by software. Once it is set, PCE is active after the current byte (in reception and in transmission).</li> <li>0: Parity control disabled</li> <li>1: Parity control enabled</li> </ul> |  |  |  |  |  |

| 1   | PS   | <ul> <li>Parity selection         This bit selects the odd or even parity when the parity generation/detection is enabled (PCE bit set). It is set and cleared by software. The parity is selected afte the current byte.         0: Even parity         1: Odd parity         </li> </ul>                                                                                                                                                                                                                    |  |  |  |  |  |

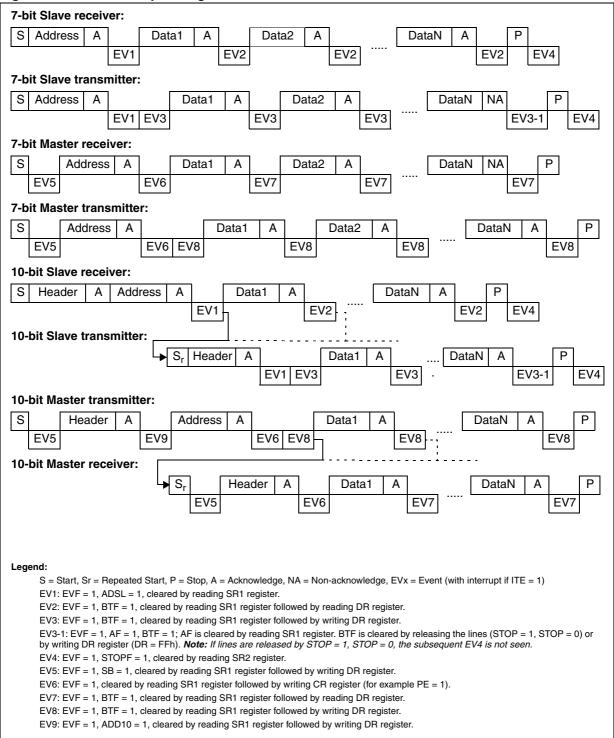

#### Figure 68. Transfer sequencing

# 19.8 I/O port pin characteristics

## 19.8.1 General characteristics

Subject to general operating conditions for  $V_{DD,}$  f<sub>OSC</sub>, and T<sub>A</sub> unless otherwise specified.

| Table 126. I/O port pin general characteristics | Table 126. | I/O port pin general characteristics |

|-------------------------------------------------|------------|--------------------------------------|

|-------------------------------------------------|------------|--------------------------------------|

| Symbol                               | Parameter                                                | Con                                          | ditions       | Min                             | Тур | Max                             | Unit             |

|--------------------------------------|----------------------------------------------------------|----------------------------------------------|---------------|---------------------------------|-----|---------------------------------|------------------|

| V <sub>IL</sub>                      | Input low level voltage <sup>(1)</sup>                   |                                              |               |                                 |     | $0.3 \mathrm{xV}_{\mathrm{DD}}$ |                  |

| V <sub>IH</sub>                      | Input high level voltage <sup>(1)</sup>                  | CMOS ports                                   |               | $0.7 \mathrm{xV}_{\mathrm{DD}}$ |     |                                 | V                |

| V <sub>hys</sub>                     | Schmitt trigger voltage hysteresis <sup>(2)</sup>        |                                              |               |                                 | 0.7 |                                 |                  |

| I <sub>INJ(PIN)</sub> <sup>(3)</sup> | Injected current on PC6 pin (Flash devices only)         |                                              |               | 0                               |     | +4                              |                  |

|                                      | Injected current on an I/O pin                           | $V_{DD} = 5V$                                |               |                                 | ±4  | mA                              |                  |

| $\Sigma I_{\rm INJ(PIN)}^{(3)}$      | Total injected current (sum of all I/O and control pins) |                                              |               |                                 |     | ±25                             |                  |

| ١L                                   | Input leakage current                                    | $V_{SS} \leq V_{IN} \leq V_{DD}$             |               |                                 |     | ±1                              |                  |

| ۱ <sub>S</sub>                       | Static current consumption                               | Floating input mode <sup>(4)</sup>           |               |                                 | 400 |                                 | μA               |

| R <sub>PU</sub>                      | Weak pull-up equivalent resistor <sup>(5)</sup>          | $V_{IN} = V_{SS}$                            | $V_{DD} = 5V$ | 50                              | 120 | 250                             | kΩ               |

| C <sub>IO</sub>                      | I/O pin capacitance                                      |                                              |               |                                 | 5   |                                 | pF               |

| t <sub>f(IO)out</sub>                | Output high to low level fall time <sup>(1)</sup>        | C <sub>L</sub> = 50pF<br>Between 10% and 90% |               |                                 | 25  |                                 | - ns             |

| t <sub>r(IO)out</sub>                | Output low to high level rise time <sup>(1)</sup>        |                                              |               |                                 | 25  |                                 |                  |

| t <sub>w(IT)in</sub>                 | External interrupt pulse time <sup>(6)</sup>             |                                              |               | 1                               |     |                                 | t <sub>CPU</sub> |

1. Data based on characterization results, not tested in production.

2. Hysteresis voltage between Schmitt trigger switching levels. Based on characterization results, not tested.

- When the current limitation is not possible, the V<sub>IN</sub> maximum must be respected, otherwise refer to I<sub>INJ(PIN)</sub> specification. A positive injection is induced by V<sub>IN</sub> > V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. Refer to Section 19.2.2: Current characteristics for more details.

- 4. Configuration not recommended. All unused pins must be kept at a fixed voltage. This can be done by using the output mode of the I/O, for example, and leaving the I/O unconnected on the board or by an external pull-up or pull-down resistor (see *Figure 82*). Static peak current value taken at a fixed V<sub>IN</sub> value, based on design simulation and technology characteristics, not tested in production. This value depends on V<sub>DD</sub> and temperature values.

- 5. The R<sub>PU</sub> pull-up equivalent resistor is based on a resistive transistor (corresponding I<sub>PU</sub> current characteristics described in *Figure 83*).

6. To generate an external interrupt, a minimum pulse width has to be applied on an I/O port pin configured as an external interrupt source.

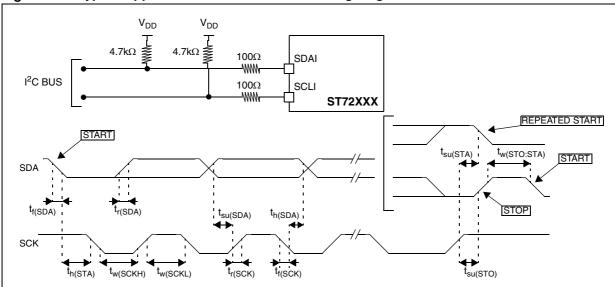

Figure 96. Typical application with I<sup>2</sup>C BUS and timing diagram<sup>(1)</sup>

1. Measurement points are done at CMOS levels:  $0.3xV_{DD}$  and  $0.7xV_{DD}$ .

The following table provides the values to be written in the I2CCCR register to obtain the required  $I^2C$  SCL line frequency.

|                  | I2CCCR value                  |                               |                     |                          |                        |                               |                     |                     |  |

|------------------|-------------------------------|-------------------------------|---------------------|--------------------------|------------------------|-------------------------------|---------------------|---------------------|--|

| f <sub>SCL</sub> | f <sub>CPU</sub> = 4 MHz      |                               |                     | f <sub>CPU</sub> = 8 MHz |                        |                               |                     |                     |  |

| (kHz)            | V <sub>DD</sub> = 4.1V        |                               | $V_{DD} = 5V$       |                          | V <sub>DD</sub> = 4.1V |                               | $V_{DD} = 5V$       |                     |  |

|                  | <b>R<sub>P</sub> = 3.3k</b> Ω | <b>R<sub>P</sub> = 4.7k</b> Ω | $R_P = 3.3 k\Omega$ | $R_P = 4.7 k\Omega$      | $R_P = 3.3 k\Omega$    | <b>R<sub>P</sub> = 4.7k</b> Ω | $R_P = 3.3 k\Omega$ | $R_P = 4.7 k\Omega$ |  |

| 400              |                               | Not ach                       | nievable            |                          |                        | 83                            | ßh                  |                     |  |

| 300              | Not achievable 85h            |                               |                     |                          |                        |                               |                     |                     |  |

| 200              | 83h 8Ah 89h 8Ah               |                               |                     |                          | ۹h                     |                               |                     |                     |  |

| 100              | 10h                           |                               |                     | 24h                      | 23h                    | 24h 23h                       |                     |                     |  |

| 50               | 24h 4Ch                       |                               |                     |                          |                        |                               |                     |                     |  |

| 20               | 5Fh                           |                               |                     |                          | FFh                    |                               |                     |                     |  |

### Table 134. SCL frequency table

Legend:

R<sub>P</sub> = External pull-up resistance

$$f_{SCL} = I^2 C$$

speed

Note:

- For speeds around 200 kHz, the achieved speed can have a  $\pm 5\%$  tolerance. - For other speed ranges, the achieved speed can have a  $\pm 2\%$  tolerance.

The above variations depend on the accuracy of the external components used.

# 20.1 Thermal characteristics

### Table 139. Thermal characteristics

| Symbol            | Ratings                                                                                          | Value          | Unit |

|-------------------|--------------------------------------------------------------------------------------------------|----------------|------|

| R <sub>thJA</sub> | Package thermal resistance (junction to ambient)<br>LQFP64 14x14<br>LQFP64 10x10<br>LQFP44 10x10 | 47<br>50<br>52 | °C/W |

| PD                | Power dissipation <sup>(1)</sup>                                                                 | 500            | mW   |

| T <sub>Jmax</sub> | Maximum junction temperature <sup>(2)</sup>                                                      | 150            | °C   |

1. The maximum power dissipation is obtained from the formula  $P_D = (T_J - T_A) / R_{thJA}$ . The power dissipation of an application can be defined by the user with the formula:  $P_D = P_{INT} + P_{PORT}$  where  $P_{INT}$  is the chip internal power ( $I_{DD} \times V_{DD}$ ) and  $P_{PORT}$  is the port power dissipation depending on the ports used in the application.

2. The maximum chip-junction temperature is based on technology characteristics.

# 20.2 Ecopack information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

# 20.3 Packaging for automatic handling

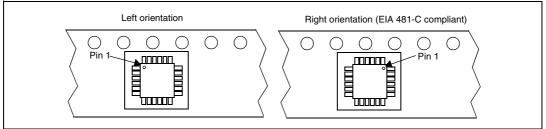

The devices can be supplied in trays or with tape and reel conditioning.

Tape and reel conditioning can be ordered with pin 1 left-oriented or right-oriented when facing the tape sprocket holes as shown in *Figure 104*.

#### Figure 104. Pin 1 orientation in tape and reel conditioning

See also Section Figure 105.: ST72F321xxx-Auto Flash commercial product structure on page 226 and Figure 106: ST72P321xxx-Auto FastROM commercial product structure on page 228.

```

; check the semaphore status if edge is detected

CP A,#01

jrne OUT

call call_routine

; call the interrupt routine

OUT:LD A,#00

LD sema,A

.call_routine

; entry to call_routine

PUSH A

PUSH X

PUSH CC

.ext1_rt

; entry to interrupt routine

LD A,#00

LD sema,A

IRET

Case 2: Writing to PxOR or PxDDR with global interrupts disabled:

SIM

; set the interrupt mask

LD A, PFDR

AND A,#$02

LD X,A

; store the level before writing to PxOR/PxDDR

LD A,#$90

LD PFDDR,A

; Write into PFDDR

LD A,#$ff

LD PFOR,A

; Write to PFOR

LD A, PFDR

AND A,#$02

LD Y,A

; store the level after writing to PxOR/PxDDR

LD A,X

```

Doc ID 13829 Rev 1

## 22.1.6 Clearing active interrupts outside interrupt routine

When an active interrupt request occurs at the same time as the related flag is being cleared, an unwanted reset may occur.

Note: Clearing the related interrupt mask will not generate an unwanted reset.

#### **Concurrent interrupt context**

The symptom does not occur when the interrupts are handled normally, that is, when:

- The interrupt flag is cleared within its own interrupt routine

- The interrupt flag is cleared within any interrupt routine

- The interrupt flag is cleared in any part of the code while this interrupt is disabled

If these conditions are not met, the symptom can be avoided by implementing the following sequence:

Perform SIM and RIM operation before and after resetting an active interrupt request.

Example: SIM Reset interrupt flag

RIM

#### Nested interrupt context

The symptom does not occur when the interrupts are handled normally, that is, when:

- The interrupt flag is cleared within its own interrupt routine

- The interrupt flag is cleared within any interrupt routine with higher or identical priority level

- The interrupt flag is cleared in any part of the code while this interrupt is disabled

If these conditions are not met, the symptom can be avoided by implementing the following sequence:

PUSH CC SIM Reset interrupt flag POP CC