Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                             |

|--------------------------------|-----------------------------------------------------------------------------|

| Product Status                 | Active                                                                      |

| Number of LABs/CLBs            | 768                                                                         |

| Number of Logic Elements/Cells | -                                                                           |

| Total RAM Bits                 | -                                                                           |

| Number of I/O                  | 113                                                                         |

| Number of Gates                | 12000                                                                       |

| Voltage - Supply               | 2.25V ~ 5.25V                                                               |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | -40°C ~ 85°C (TA)                                                           |

| Package / Case                 | 144-LQFP                                                                    |

| Supplier Device Package        | 144-TQFP (20x20)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a54sx08a-1tqg144i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

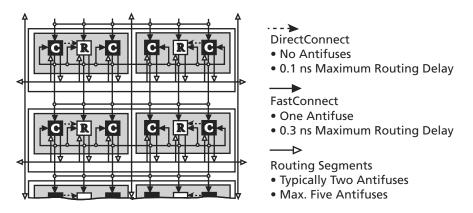

Figure 1-5 • DirectConnect and FastConnect for Type 1 SuperClusters

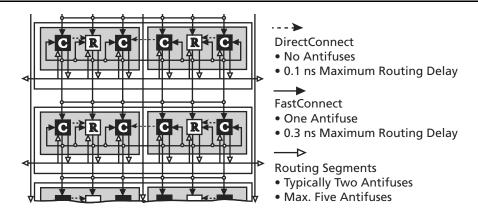

Figure 1-6 • DirectConnect and FastConnect for Type 2 SuperClusters

1-4 v5.3

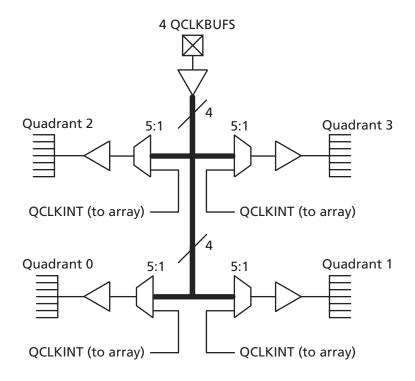

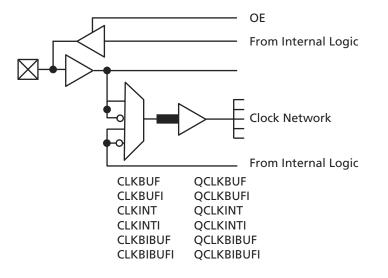

Figure 1-9 • SX-A QCLK Architecture

Figure 1-10 • A54SX72A Routed Clock and QCLK Buffer

1-6 v5.3

### **Boundary-Scan Testing (BST)**

All SX-A devices are IEEE 1149.1 compliant and offer superior diagnostic and testing capabilities by providing Boundary Scan Testing (BST) and probing capabilities. The BST function is controlled through the special JTAG pins (TMS, TDI, TCK, TDO, and TRST). The functionality of the JTAG pins is defined by two available modes: Dedicated and Flexible. TMS cannot be employed as a user I/O in either mode.

### **Dedicated Mode**

In Dedicated mode, all JTAG pins are reserved for BST; designers cannot use them as regular I/Os. An internal pull-up resistor is automatically enabled on both TMS and TDI pins, and the TMS pin will function as defined in the IEEE 1149.1 (JTAG) specification.

To select Dedicated mode, the user must reserve the JTAG pins in Actel's Designer software. Reserve the JTAG pins by checking the **Reserve JTAG** box in the Device Selection Wizard (Figure 1-12).

The default for the software is Flexible mode; all boxes are unchecked. Table 1-5 lists the definitions of the options in the Device Selection Wizard.

Figure 1-12 • Device Selection Wizard

Table 1-5 • Reserve Pin Definitions

| Pin                        | Function                                                                             |

|----------------------------|--------------------------------------------------------------------------------------|

| Reserve JTAG               | Keeps pins from being used and changes the behavior of JTAG pins (no pull-up on TMS) |

| Reserve JTAG Test<br>Reset | Regular I/O or JTAG reset with an internal pull-up                                   |

| Reserve Probe              | Keeps pins from being used or regular I/O                                            |

#### Flexible Mode

In Flexible mode, TDI, TCK, and TDO may be employed as either user I/Os or as JTAG input pins. The internal resistors on the TMS and TDI pins are not present in flexible JTAG mode.

To select the Flexible mode, uncheck the **Reserve JTAG** box in the Device Selection Wizard dialog in the Actel Designer software. In Flexible mode, TDI, TCK, and TDO pins may function as user I/Os or BST pins. The functionality is controlled by the BST Test Access Port (TAP) controller. The TAP controller receives two control inputs, TMS and TCK. Upon power-up, the TAP controller enters the Test-Logic-Reset state. In this state, TDI, TCK, and TDO function as user I/Os. The TDI, TCK, and TDO are transformed from user I/Os into BST pins when a rising edge on TCK is detected while TMS is at logic low. To return to Test-Logic Reset state, TMS must be high for at least five TCK cycles. **An external 10 k pull-up resistor to V**<sub>CCI</sub> **should be placed on the TMS pin to pull it High by default.**

Table 1-6 describes the different configuration requirements of BST pins and their functionality in different modes.

Table 1-6 • Boundary-Scan Pin Configurations and Functions

| Mode                | Designer<br>"Reserve JTAG"<br>Selection | TAP Controller<br>State         |

|---------------------|-----------------------------------------|---------------------------------|

| Dedicated (JTAG)    | Checked                                 | Any                             |

| Flexible (User I/O) | Unchecked                               | Test-Logic-Reset                |

| Flexible (JTAG)     | Unchecked                               | Any EXCEPT Test-<br>Logic-Reset |

#### **TRST Pin**

The TRST pin functions as a dedicated Boundary-Scan Reset pin when the **Reserve JTAG Test Reset** option is selected as shown in Figure 1-12. An internal pull-up resistor is permanently enabled on the TRST pin in this mode. Actel recommends connecting this pin to ground in normal operation to keep the JTAG state controller in the Test-Logic-Reset state. When JTAG is being used, it can be left floating or can be driven high.

When the **Reserve JTAG Test Reset** option is not selected, this pin will function as a regular I/O. If unused as an I/O in the design, it will be configured as a tristated output.

v5.3 1-9

# **Electrical Specifications**

Table 2-5 • 3.3 V LVTTL and 5 V TTL Electrical Specifications

|                                  |                                                          |                            | Comm                 | ercial | Indu                 | strial |       |

|----------------------------------|----------------------------------------------------------|----------------------------|----------------------|--------|----------------------|--------|-------|

| Symbol                           | Parameter                                                |                            | Min.                 | Max.   | Min.                 | Max.   | Units |

| V <sub>OH</sub>                  | $V_{CCI} = Minimum$<br>$V_I = V_{IH} \text{ or } V_{IL}$ | $(I_{OH} = -1 \text{ mA})$ | 0.9 V <sub>CCI</sub> |        | 0.9 V <sub>CCI</sub> |        | V     |

|                                  | $V_{CCI} = Minimum$<br>$V_I = V_{IH} \text{ or } V_{IL}$ | $(I_{OH} = -8 \text{ mA})$ | 2.4                  |        | 2.4                  |        | V     |

| V <sub>OL</sub>                  | $V_{CCI} = Minimum$<br>$V_I = V_{IH} \text{ or } V_{IL}$ | (I <sub>OL</sub> = 1 mA)   |                      | 0.4    |                      | 0.4    | V     |

|                                  | $V_{CCI} = Minimum$<br>$V_I = V_{IH} \text{ or } V_{IL}$ | (I <sub>OL</sub> = 12 mA)  |                      | 0.4    |                      | 0.4    | V     |

| V <sub>IL</sub>                  | Input Low Voltage                                        |                            |                      | 8.0    |                      | 0.8    | V     |

| V <sub>IH</sub>                  | Input High Voltage                                       |                            | 2.0                  | 5.75   | 2.0                  | 5.75   | V     |

| I <sub>IL</sub> /I <sub>IH</sub> | Input Leakage Current, $V_{IN} = V_{CCI}$ or GND         |                            | -10                  | 10     | -10                  | 10     | μΑ    |

| I <sub>OZ</sub>                  | Tristate Output Leakage Current                          |                            | -10                  | 10     | -10                  | 10     | μΑ    |

| t <sub>R</sub> , t <sub>F</sub>  | Input Transition Time t <sub>R</sub> , t <sub>F</sub>    |                            |                      | 10     |                      | 10     | ns    |

| C <sub>IO</sub>                  | I/O Capacitance                                          |                            |                      | 10     |                      | 10     | рF    |

| I <sub>CC</sub>                  | Standby Current                                          |                            |                      | 10     |                      | 20     | mA    |

| IV Curve*                        | Can be derived from the IBIS model on the web            | O.                         |                      |        | •                    |        | •     |

**Note:** \*The IBIS model can be found at http://www.actel.com/download/ibis/default.aspx.

Table 2-6 • 2.5 V LVCMOS2 Electrical Specifications

|                                  |                                                                  |                               | Comn | nercial | Indu | strial |       |

|----------------------------------|------------------------------------------------------------------|-------------------------------|------|---------|------|--------|-------|

| Symbol                           | Parameter                                                        |                               | Min. | Мах.    | Min. | Max.   | Units |

| V <sub>OH</sub>                  | $V_{DD} = MIN,$<br>$V_{I} = V_{IH} \text{ or } V_{IL}$           | $(I_{OH} = -100 \mu\text{A})$ | 2.1  |         | 2.1  |        | V     |

|                                  | $V_{DD} = MIN,$<br>$V_{I} = V_{IH} \text{ or } V_{IL}$           | $(I_{OH} = -1 \text{ mA})$    | 2.0  |         | 2.0  |        | V     |

|                                  | $V_{DD} = MIN,$<br>$V_{I} = V_{IH} \text{ or } V_{IL}$           | (I <sub>OH</sub> =2 mA)       | 1.7  |         | 1.7  |        | V     |

| V <sub>OL</sub>                  | $V_{DD} = MIN,$<br>$V_{I} = V_{IH} \text{ or } V_{IL}$           | (I <sub>OL</sub> = 100 μA)    |      | 0.2     |      | 0.2    | V     |

|                                  | $V_{DD} = MIN,$<br>$V_{I} = V_{IH} \text{ or } V_{IL}$           | (I <sub>OL</sub> = 1 mA)      |      | 0.4     |      | 0.4    | V     |

|                                  | $V_{DD} = MIN,$<br>$V_{I} = V_{IH} \text{ or } V_{IL}$           | (I <sub>OL</sub> = 2 mA)      |      | 0.7     |      | 0.7    | V     |

| V <sub>IL</sub>                  | Input Low Voltage, V <sub>OUT</sub> ≤ V <sub>VOL(max)</sub>      |                               | -0.3 | 0.7     | -0.3 | 0.7    | V     |

| V <sub>IH</sub>                  | Input High Voltage, V <sub>OUT</sub> ≥ V <sub>VOH(min)</sub>     |                               | 1.7  | 5.75    | 1.7  | 5.75   | V     |

| I <sub>IL</sub> /I <sub>IH</sub> | Input Leakage Current, V <sub>IN</sub> = V <sub>CCI</sub> or GND |                               | -10  | 10      | -10  | 10     | μΑ    |

| I <sub>OZ</sub>                  | Tristate Output Leakage Current, $V_{OUT} = V_{CCI}$ or GND      |                               | -10  | 10      | -10  | 10     | μΑ    |

| t <sub>R</sub> , t <sub>F</sub>  | Input Transition Time t <sub>R</sub> , t <sub>F</sub>            |                               |      | 10      |      | 10     | ns    |

| C <sub>IO</sub>                  | I/O Capacitance                                                  |                               |      | 10      |      | 10     | рF    |

| I <sub>CC</sub>                  | Standby Current                                                  |                               |      | 10      |      | 20     | mA    |

| IV Curve*                        | Can be derived from the IBIS model on the web.                   |                               |      |         |      |        | -     |

**Note:** \*The IBIS model can be found at http://www.actel.com/download/ibis/default.aspx.

2-2 v5.3

EQ 2-2

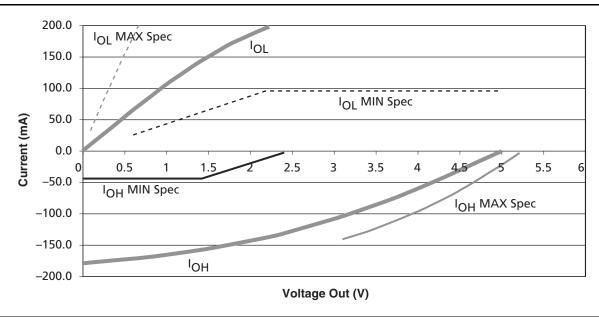

Figure 2-1 shows the 5 V PCI V/I curve and the minimum and maximum PCI drive characteristics of the SX-A family.

Figure 2-1 • 5 V PCI V/I Curve for SX-A Family

$$I_{OH} = 11.9 * (V_{OUT} - 5.25) * (V_{OUT} + 2.45)$$

$I_{OL} = 78.5 * V_{OUT} * (4.4 - V_{OUT})$  for  $V_{CCI} > V_{OUT} > 3.1V$  for  $0V < V_{OUT} < 0.71V$

Table 2-9 • DC Specifications (3.3 V PCI Operation)

| Symbol           | Parameter                          | Condition                   | Min.                | Max.                   | Units |

|------------------|------------------------------------|-----------------------------|---------------------|------------------------|-------|

| $V_{CCA}$        | Supply Voltage for Array           |                             | 2.25                | 2.75                   | V     |

| $V_{CCI}$        | Supply Voltage for I/Os            |                             | 3.0                 | 3.6                    | V     |

| $V_{IH}$         | Input High Voltage                 |                             | 0.5V <sub>CCI</sub> | V <sub>CCI</sub> + 0.5 | V     |

| $V_{IL}$         | Input Low Voltage                  |                             | -0.5                | 0.3V <sub>CCI</sub>    | V     |

| I <sub>IPU</sub> | Input Pull-up Voltage <sup>1</sup> |                             | 0.7V <sub>CCI</sub> | _                      | V     |

| I <sub>IL</sub>  | Input Leakage Current <sup>2</sup> | $0 < V_{IN} < V_{CCI}$      | -10                 | +10                    | μΑ    |

| $V_{OH}$         | Output High Voltage                | I <sub>OUT</sub> = -500 μA  | 0.9V <sub>CCI</sub> | _                      | V     |

| $V_{OL}$         | Output Low Voltage                 | I <sub>OUT</sub> = 1,500 μA |                     | 0.1V <sub>CCI</sub>    | V     |

| C <sub>IN</sub>  | Input Pin Capacitance <sup>3</sup> |                             | -                   | 10                     | pF    |

| $C_{CLK}$        | CLK Pin Capacitance                |                             | 5                   | 12                     | pF    |

#### Notes:

- 1. This specification should be guaranteed by design. It is the minimum voltage to which pull-up resistors are calculated to pull a floated network. Designers should ensure that the input buffer is conducting minimum current at this input voltage in applications sensitive to static power utilization.

- 2. Input leakage currents include hi-Z output leakage for all bidirectional buffers with tristate outputs.

- 3. Absolute maximum pin capacitance for a PCI input is 10 pF (except for CLK).

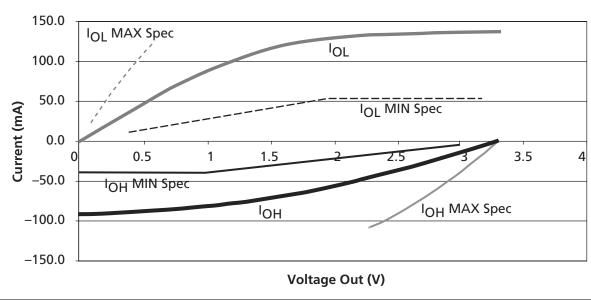

Figure 2-2 shows the 3.3 V PCI V/I curve and the minimum and maximum PCI drive characteristics of the SX-A family.

Figure 2-2 • 3.3 V PCI V/I Curve for SX-A Family

$$I_{OH} = (98.0/V_{CCI}) * (V_{OUT} - V_{CCI}) * (V_{OUT} + 0.4V_{CCI})$$

for 0.7  $V_{CCI} < V_{OUT} < V_{CCI}$

$$I_{OL} = (256/V_{CCI}) * V_{OUT} * (V_{CCI} - V_{OUT})$$

for  $0V < V_{OUT} < 0.18 \ V_{CCI}$

EQ 2-3 EQ 2-4

#### Where:

C<sub>EQCM</sub> = Equivalent capacitance of combinatorial modules (C-cells) in pF

$C_{FOSM}$  = Equivalent capacitance of sequential modules (R-Cells) in pF

C<sub>EOI</sub> = Equivalent capacitance of input buffers in pF

C<sub>EOO</sub> = Equivalent capacitance of output buffers in pF

C<sub>EOCR</sub> = Equivalent capacitance of CLKA/B in pF

$C_{EQHV}$  = Variable capacitance of HCLK in pF

$C_{EOHF}$  = Fixed capacitance of HCLK in pF

C<sub>L =</sub> Output lead capacitance in pF

$f_m$  = Average logic module switching rate in MHz

$f_n$  = Average input buffer switching rate in MHz

$f_p$  = Average output buffer switching rate in MHz

$f_{q1}$  = Average CLKA rate in MHz

$f_{q2}$  = Average CLKB rate in MHz

$f_{s1}$  = Average HCLK rate in MHz

m = Number of logic modules switching at fm

n = Number of input buffers switching at fn

p = Number of output buffers switching at fp

$q_1$  = Number of clock loads on CLKA

$q_2$  = Number of clock loads on CLKB

$r_1$  = Fixed capacitance due to CLKA

$r_2$  = Fixed capacitance due to CLKB

s<sub>1</sub> = Number of clock loads on HCLK

x = Number of I/Os at logic low

y = Number of I/Os at logic high

### Table 2-11 • CEQ Values for SX-A Devices

|                                                        | A54SX08A | A54SX16A | A54SX32A  | A54SX72A  |

|--------------------------------------------------------|----------|----------|-----------|-----------|

| Combinatorial modules (C <sub>EQCM</sub> )             | 1.70 pF  | 2.00 pF  | 2.00 pF   | 1.80 pF   |

| Sequential modules (C <sub>EQCM</sub> )                | 1.50 pF  | 1.50 pF  | 1.30 pF   | 1.50 pF   |

| Input buffers (C <sub>EQI</sub> )                      | 1.30 pF  | 1.30 pF  | 1.30 pF   | 1.30 pF   |

| Output buffers (C <sub>EQO</sub> )                     | 7.40 pF  | 7.40 pF  | 7.40 pF   | 7.40 pF   |

| Routed array clocks (C <sub>EQCR</sub> )               | 1.05 pF  | 1.05 pF  | 1.05 pF   | 1.05 pF   |

| Dedicated array clocks – variable (C <sub>EQHV</sub> ) | 0.85 pF  | 0.85 pF  | 0.85 pF   | 0.85 pF   |

| Dedicated array clocks – fixed (C <sub>EQHF</sub> )    | 30.00 pF | 55.00 pF | 110.00 pF | 240.00 pF |

| Routed array clock A (r <sub>1</sub> )                 | 35.00 pF | 50.00 pF | 90.00 pF  | 310.00 pF |

### Theta-JA

Junction-to-ambient thermal resistance ( $\theta_{JA}$ ) is determined under standard conditions specified by JESD-51 series but has little relevance in actual performance of the product in real application. It should be employed with caution but is useful for comparing the thermal performance of one package to another.

A sample calculation to estimate the absolute maximum power dissipation allowed (worst case) for a 329-pin PBGA package at still air is as follows. i.e.:

$\theta_{IA}$  = 17.1°C/W is taken from Table 2-12 on page 2-11

$T_A = 125$ °C is the maximum limit of ambient (from the datasheet)

Max. Allowed Power =

$$\frac{\text{Max Junction Temp} - \text{Max. Ambient Temp}}{\theta_{\text{JA}}} = \frac{150^{\circ}\text{C} - 125^{\circ}\text{C}}{17.1^{\circ}\text{C/W}} = 1.46 \text{ W}$$

EQ 2-11

The device's power consumption must be lower than the calculated maximum power dissipation by the package.

The power consumption of a device can be calculated using the Actel power calculator. If the power consumption is higher than the device's maximum allowable power dissipation, then a heat sink can be attached on top of the case or the airflow inside the system must be increased.

### Theta-JC

Junction-to-case thermal resistance ( $\theta_{JC}$ ) measures the ability of a device to dissipate heat from the surface of the chip to the top or bottom surface of the package. It is applicable for packages used with external heat sinks and only applies to situations where all or nearly all of the heat is dissipated through the surface in consideration. If the power consumption is higher than the calculated maximum power dissipation of the package, then a heat sink is required.

### **Calculation for Heat Sink**

For example, in a design implemented in a FG484 package, the power consumption value using the power calculator is 3.00 W. The user-dependent data  $T_J$  and  $T_A$  are given as follows:

$T_J = 110$ °C

$T_A = 70^{\circ}C$

From the datasheet:

$\theta_{JA} = 18.0$ °C/W

$\theta_{JC} = 3.2 \, ^{\circ}C/W$

$$P = \frac{Max \ Junction \ Temp - Max. \ Ambient \ Temp}{\theta_{JA}} = \frac{110^{\circ}C - 70^{\circ}C}{18.0^{\circ}C / W} = 2.22 \ W$$

EQ 2-12

The 2.22 W power is less than then required 3.00 W; therefore, the design requires a heat sink or the airflow where the device is mounted should be increased. The design's junction-to-air thermal resistance requirement can be estimated by:

$$\theta_{JA} = \frac{\text{Max Junction Temp} - \text{Max. Ambient Temp}}{P} = \frac{110^{\circ}\text{C} - 70^{\circ}\text{C}}{3.00 \text{ W}} = 13.33^{\circ}\text{C/W}$$

EQ 2-13

2-12 v5.3

# **Input Buffer Delays**

# **C-Cell Delays**

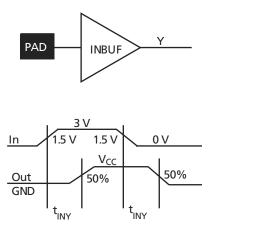

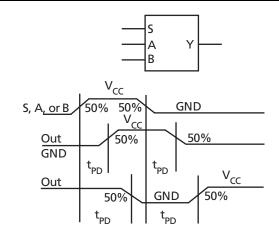

Figure 2-6 • Input Buffer Delays

Figure 2-7 • C-Cell Delays

# **Cell Timing Characteristics**

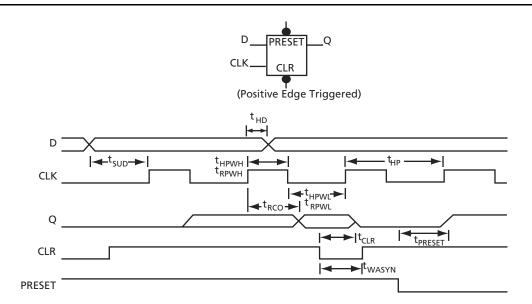

Figure 2-8 • Flip-Flops

2-16 v5.3

Table 2-14 • A54SX08A Timing Characteristics (Continued) (Worst-Case Commercial Conditions, V<sub>CCA</sub> = 2.25 V, V<sub>CCI</sub> = 3.0 V, T<sub>J</sub> = 70°C)

|                    |                                         | -2 Sp | peed | -1 S | peed | Std. S | Speed | −F S <sub>l</sub> | peed |       |

|--------------------|-----------------------------------------|-------|------|------|------|--------|-------|-------------------|------|-------|

| Parameter          | Description                             | Min.  | Max. | Min. | Мах. | Min.   | Мах.  | Min.              | Мах. | Units |

| t <sub>INYH</sub>  | Input Data Pad to Y High 5 V PCI        |       | 0.5  |      | 0.6  |        | 0.7   |                   | 0.9  | ns    |

| t <sub>INYL</sub>  | Input Data Pad to Y Low 5 V PCI         |       | 0.8  |      | 0.9  |        | 1.1   |                   | 1.5  | ns    |

| t <sub>INYH</sub>  | Input Data Pad to Y High 5 V TTL        |       | 0.5  |      | 0.6  |        | 0.7   |                   | 0.9  | ns    |

| t <sub>INYL</sub>  | Input Data Pad to Y Low 5 V TTL         |       | 0.8  |      | 0.9  |        | 1.1   |                   | 1.5  | ns    |

| Input Modul        | e Predicted Routing Delays <sup>2</sup> |       |      |      |      |        |       | •                 |      |       |

| t <sub>IRD1</sub>  | FO = 1 Routing Delay                    |       | 0.3  |      | 0.3  |        | 0.4   |                   | 0.6  | ns    |

| t <sub>IRD2</sub>  | FO = 2 Routing Delay                    |       | 0.5  |      | 0.5  |        | 0.6   |                   | 8.0  | ns    |

| t <sub>IRD3</sub>  | FO = 3 Routing Delay                    |       | 0.6  |      | 0.7  |        | 8.0   |                   | 1.1  | ns    |

| t <sub>IRD4</sub>  | FO = 4 Routing Delay                    |       | 0.8  |      | 0.9  |        | 1     |                   | 1.4  | ns    |

| t <sub>IRD8</sub>  | FO = 8 Routing Delay                    |       | 1.4  |      | 1.5  |        | 1.8   |                   | 2.5  | ns    |

| t <sub>IRD12</sub> | FO = 12 Routing Delay                   |       | 2    |      | 2.2  |        | 2.6   |                   | 3.6  | ns    |

#### Notes:

- 1. For dual-module macros, use  $t_{PD}+t_{RD1}+t_{PDn}$ ,  $t_{RCO}+t_{RD1}+t_{PDn}$ , or  $t_{PD1}+t_{RD1}+t_{SUD}$ , whichever is appropriate.

- 2. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual performance.

Table 2-16 • A54SX08A Timing Characteristics

(Worst-Case Commercial Conditions V<sub>CCA</sub> = 2.25 V, V<sub>CCI</sub> = 3.0 V, T<sub>J</sub> = 70°C)

|                    |                                                         | -2 S | peed | -1 S | peed | Std. | Speed | −F S | peed |       |

|--------------------|---------------------------------------------------------|------|------|------|------|------|-------|------|------|-------|

| Parameter          | Description                                             | Min. | Мах. | Min. | Мах. | Min. | Мах.  | Min. | Мах. | Units |

| Dedicated (        | Hardwired) Array Clock Networks                         | •    |      |      |      | •    |       |      |      |       |

| t <sub>HCKH</sub>  | Input Low to High<br>(Pad to R-cell Input)              |      | 1.3  |      | 1.5  |      | 1.7   |      | 2.6  | ns    |

| t <sub>HCKL</sub>  | Input High to Low<br>(Pad to R-cell Input)              |      | 1.1  |      | 1.3  |      | 1.5   |      | 2.2  | ns    |

| t <sub>HPWH</sub>  | Minimum Pulse Width High                                | 1.6  |      | 1.8  |      | 2.1  |       | 2.9  |      | ns    |

| t <sub>HPWL</sub>  | Minimum Pulse Width Low                                 | 1.6  |      | 1.8  |      | 2.1  |       | 2.9  |      | ns    |

| t <sub>HCKSW</sub> | Maximum Skew                                            |      | 0.4  |      | 0.5  |      | 0.5   |      | 8.0  | ns    |

| t <sub>HP</sub>    | Minimum Period                                          | 3.2  |      | 3.6  |      | 4.2  |       | 5.8  |      | ns    |

| f <sub>HMAX</sub>  | Maximum Frequency                                       |      | 313  |      | 278  |      | 238   |      | 172  | MHz   |

| Routed Arra        | y Clock Networks                                        |      |      |      |      |      |       |      |      |       |

| t <sub>RCKH</sub>  | Input Low to High (Light Load)<br>(Pad to R-cell Input) |      | 0.8  |      | 0.9  |      | 1.1   |      | 1.5  | ns    |

| t <sub>RCKL</sub>  | Input High to Low (Light Load)<br>(Pad to R-cell Input) |      | 1.1  |      | 1.2  |      | 1.4   |      | 2    | ns    |

| t <sub>RCKH</sub>  | Input Low to High (50% Load)<br>(Pad to R-cell Input)   |      | 0.8  |      | 0.9  |      | 1.1   |      | 1.5  | ns    |

| t <sub>RCKL</sub>  | Input High to Low (50% Load)<br>(Pad to R-cell Input)   |      | 1.1  |      | 1.2  |      | 1.4   |      | 2    | ns    |

| t <sub>RCKH</sub>  | Input Low to High (100% Load)<br>(Pad to R-cell Input)  |      | 1.1  |      | 1.2  |      | 1.4   |      | 1.9  | ns    |

| t <sub>RCKL</sub>  | Input High to Low (100% Load)<br>(Pad to R-cell Input)  |      | 1.2  |      | 1.3  |      | 1.6   |      | 2.2  | ns    |

| t <sub>RPWH</sub>  | Minimum Pulse Width High                                | 1.6  |      | 1.8  |      | 2.1  |       | 2.9  |      | ns    |

| t <sub>RPWL</sub>  | Minimum Pulse Width Low                                 | 1.6  |      | 1.8  |      | 2.1  |       | 2.9  |      | ns    |

| t <sub>RCKSW</sub> | Maximum Skew (Light Load)                               |      | 0.7  |      | 8.0  |      | 0.9   |      | 1.3  | ns    |

| t <sub>RCKSW</sub> | Maximum Skew (50% Load)                                 |      | 0.7  |      | 0.8  |      | 0.9   |      | 1.3  | ns    |

| t <sub>RCKSW</sub> | Maximum Skew (100% Load)                                |      | 8.0  |      | 0.9  |      | 1.1   |      | 1.5  | ns    |

Table 2-22 • A54SX16A Timing Characteristics (Worst-Case Commercial Conditions V<sub>CCA</sub> = 2.25 V, V<sub>CCI</sub> = 2.25 V, T<sub>J</sub> = 70°C)

|                    |                                                         | -3 S <sub>I</sub> | peed* | -2 S | peed | -1 S | peed | Std. | Speed | −F S | peed |       |

|--------------------|---------------------------------------------------------|-------------------|-------|------|------|------|------|------|-------|------|------|-------|

| Parameter          | Description                                             | Min.              | Мах.  | Min. | Мах. | Min. | Max. | Min. | Мах.  | Min. | Max. | Units |

| Dedicated (        | (Hardwired) Array Clock Netwo                           | rks               |       | ı    |      |      |      |      |       |      |      |       |

| t <sub>HCKH</sub>  | Input Low to High<br>(Pad to R-cell Input)              |                   | 1.2   |      | 1.4  |      | 1.6  |      | 1.8   |      | 2.8  | ns    |

| t <sub>HCKL</sub>  | Input High to Low<br>(Pad to R-cell Input)              |                   | 1.0   |      | 1.1  |      | 1.2  |      | 1.5   |      | 2.2  | ns    |

| t <sub>HPWH</sub>  | Minimum Pulse Width High                                | 1.4               |       | 1.7  |      | 1.9  |      | 2.2  |       | 3.0  |      | ns    |

| t <sub>HPWL</sub>  | Minimum Pulse Width Low                                 | 1.4               |       | 1.7  |      | 1.9  |      | 2.2  |       | 3.0  |      | ns    |

| t <sub>HCKSW</sub> | Maximum Skew                                            |                   | 0.3   |      | 0.3  |      | 0.4  |      | 0.4   |      | 0.7  | ns    |

| t <sub>HP</sub>    | Minimum Period                                          | 2.8               |       | 3.4  |      | 3.8  |      | 4.4  |       | 6.0  |      | ns    |

| f <sub>HMAX</sub>  | Maximum Frequency                                       |                   | 357   |      | 294  |      | 263  |      | 227   |      | 167  | MHz   |

| Routed Arr         | ay Clock Networks                                       | •                 |       |      |      |      |      |      |       |      |      |       |

| t <sub>RCKH</sub>  | Input Low to High (Light Load)<br>(Pad to R-cell Input) |                   | 1.0   |      | 1.2  |      | 1.3  |      | 1.6   |      | 2.2  | ns    |

| t <sub>RCKL</sub>  | Input High to Low (Light Load)<br>(Pad to R-cell Input) |                   | 1.1   |      | 1.3  |      | 1.5  |      | 1.7   |      | 2.4  | ns    |

| t <sub>RCKH</sub>  | Input Low to High (50% Load)<br>(Pad to R-cell Input)   |                   | 1.1   |      | 1.3  |      | 1.5  |      | 1.7   |      | 2.4  | ns    |

| t <sub>RCKL</sub>  | Input High to Low (50% Load)<br>(Pad to R-cell Input)   |                   | 1.1   |      | 1.3  |      | 1.5  |      | 1.7   |      | 2.4  | ns    |

| t <sub>RCKH</sub>  | Input Low to High (100% Load)<br>(Pad to R-cell Input)  |                   | 1.3   |      | 1.5  |      | 1.7  |      | 2.0   |      | 2.8  | ns    |

| t <sub>RCKL</sub>  | Input High to Low (100% Load)<br>(Pad to R-cell Input)  |                   | 1.3   |      | 1.5  |      | 1.7  |      | 2.0   |      | 2.8  | ns    |

| t <sub>RPWH</sub>  | Minimum Pulse Width High                                | 1.4               |       | 1.7  |      | 1.9  |      | 2.2  |       | 3.0  |      | ns    |

| t <sub>RPWL</sub>  | Minimum Pulse Width Low                                 | 1.4               |       | 1.7  |      | 1.9  |      | 2.2  |       | 3.0  |      | ns    |

| t <sub>RCKSW</sub> | Maximum Skew (Light Load)                               |                   | 0.8   |      | 0.9  |      | 1.0  |      | 1.2   |      | 1.7  | ns    |

| t <sub>RCKSW</sub> | Maximum Skew (50% Load)                                 |                   | 8.0   |      | 0.9  |      | 1.0  |      | 1.2   |      | 1.7  | ns    |

| t <sub>RCKSW</sub> | Maximum Skew (100% Load)                                |                   | 1.0   |      | 1.1  |      | 1.3  |      | 1.5   |      | 2.1  | ns    |

Note: \*All –3 speed grades have been discontinued.

2-28 v5.3

Table 2-23 • A54SX16A Timing Characteristics (Worst-Case Commercial Conditions V<sub>CCA</sub> = 2.25 V, V<sub>CCI</sub> = 3.0 V, T<sub>J</sub> = 70°C)

|                    |                                                         | -3 S <sub>I</sub> | peed* | -2 S | peed | -1 S | peed | Std. | Speed | −F S | peed |       |

|--------------------|---------------------------------------------------------|-------------------|-------|------|------|------|------|------|-------|------|------|-------|

| Parameter          | Description                                             | Min.              | Мах.  | Min. | Мах. | Min. | Мах. | Min. | Мах.  | Min. | Мах. | Units |

| Dedicated (        | (Hardwired) Array Clock Netwo                           | rks               |       |      |      |      |      |      |       |      |      |       |

| t <sub>HCKH</sub>  | Input Low to High<br>(Pad to R-cell Input)              |                   | 1.2   |      | 1.4  |      | 1.6  |      | 1.8   |      | 2.8  | ns    |

| t <sub>HCKL</sub>  | Input High to Low<br>(Pad to R-cell Input)              |                   | 1.0   |      | 1.1  |      | 1.3  |      | 1.5   |      | 2.2  | ns    |

| t <sub>HPWH</sub>  | Minimum Pulse Width High                                | 1.4               |       | 1.7  |      | 1.9  |      | 2.2  |       | 3.0  |      | ns    |

| t <sub>HPWL</sub>  | Minimum Pulse Width Low                                 | 1.4               |       | 1.7  |      | 1.9  |      | 2.2  |       | 3.0  |      | ns    |

| t <sub>HCKSW</sub> | Maximum Skew                                            |                   | 0.3   |      | 0.3  |      | 0.4  |      | 0.4   |      | 0.6  | ns    |

| t <sub>HP</sub>    | Minimum Period                                          | 2.8               |       | 3.4  |      | 3.8  |      | 4.4  |       | 6.0  |      | ns    |

| $f_{\text{HMAX}}$  | Maximum Frequency                                       |                   | 357   |      | 294  |      | 263  |      | 227   |      | 167  | MHz   |

| Routed Arr         | ay Clock Networks                                       |                   |       |      |      |      |      |      |       |      |      |       |

| t <sub>RCKH</sub>  | Input Low to High (Light Load)<br>(Pad to R-cell Input) |                   | 1.0   |      | 1.2  |      | 1.3  |      | 1.5   |      | 2.1  | ns    |

| t <sub>RCKL</sub>  | Input High to Low (Light Load)<br>(Pad to R-cell Input) |                   | 1.1   |      | 1.3  |      | 1.5  |      | 1.7   |      | 2.4  | ns    |

| t <sub>RCKH</sub>  | Input Low to High (50% Load)<br>(Pad to R-cell Input)   |                   | 1.1   |      | 1.3  |      | 1.4  |      | 1.7   |      | 2.3  | ns    |

| t <sub>RCKL</sub>  | Input High to Low (50% Load)<br>(Pad to R-cell Input)   |                   | 1.1   |      | 1.3  |      | 1.5  |      | 1.7   |      | 2.4  | ns    |

| t <sub>RCKH</sub>  | Input Low to High (100% Load)<br>(Pad to R-cell Input)  |                   | 1.3   |      | 1.5  |      | 1.7  |      | 2.0   |      | 2.7  | ns    |

| t <sub>RCKL</sub>  | Input High to Low (100% Load)<br>(Pad to R-cell Input)  |                   | 1.3   |      | 1.5  |      | 1.7  |      | 2.0   |      | 2.8  | ns    |

| t <sub>RPWH</sub>  | Minimum Pulse Width High                                | 1.4               |       | 1.7  |      | 1.9  |      | 2.2  |       | 3.0  |      | ns    |

| t <sub>RPWL</sub>  | Minimum Pulse Width Low                                 | 1.4               |       | 1.7  |      | 1.9  |      | 2.2  |       | 3.0  |      | ns    |

| t <sub>RCKSW</sub> | Maximum Skew (Light Load)                               |                   | 0.8   |      | 0.9  |      | 1.0  |      | 1.2   |      | 1.7  | ns    |

| t <sub>RCKSW</sub> | Maximum Skew (50% Load)                                 |                   | 0.8   |      | 0.9  |      | 1.0  |      | 1.2   |      | 1.7  | ns    |

| t <sub>RCKSW</sub> | Maximum Skew (100% Load)                                |                   | 1.0   |      | 1.1  |      | 1.3  |      | 1.5   |      | 2.1  | ns    |

**Note:** \*All –3 speed grades have been discontinued.

Table 2-29 • A54SX32A Timing Characteristics (Worst-Case Commercial Conditions V<sub>CCA</sub> = 2.25 V, V<sub>CCI</sub> = 2.25 V, T<sub>J</sub> = 70°C)

|                    |                                                         | -3 Sı | peed* | -2 S | peed | -1 S | peed | Std.     | Speed | −F S     | peed |       |

|--------------------|---------------------------------------------------------|-------|-------|------|------|------|------|----------|-------|----------|------|-------|

| Parameter          | Description                                             |       | Max.  |      | Max. |      | Мах. |          | Max.  |          | Max. | Units |

| Dedicated (        | <br> Hardwired  Array Clock Netwo                       | rks   |       | l .  |      | ı    |      | <u> </u> |       | <u> </u> |      | ı     |

| t <sub>HCKH</sub>  | Input Low to High<br>(Pad to R-cell Input)              |       | 1.7   |      | 2.0  |      | 2.2  |          | 2.6   |          | 4.0  | ns    |

| t <sub>HCKL</sub>  | Input High to Low<br>(Pad to R-cell Input)              |       | 1.7   |      | 2.0  |      | 2.2  |          | 2.6   |          | 4.0  | ns    |

| t <sub>HPWH</sub>  | Minimum Pulse Width High                                | 1.4   |       | 1.6  |      | 1.8  |      | 2.1      |       | 2.9      |      | ns    |

| t <sub>HPWL</sub>  | Minimum Pulse Width Low                                 | 1.4   |       | 1.6  |      | 1.8  |      | 2.1      |       | 2.9      |      | ns    |

| t <sub>HCKSW</sub> | Maximum Skew                                            |       | 0.6   |      | 0.6  |      | 0.7  |          | 8.0   |          | 1.3  | ns    |

| t <sub>HP</sub>    | Minimum Period                                          | 2.8   |       | 3.2  |      | 3.6  |      | 4.2      |       | 5.8      |      | ns    |

| $f_{HMAX}$         | Maximum Frequency                                       |       | 357   |      | 313  |      | 278  |          | 238   |          | 172  | MHz   |

| Routed Arr         | ay Clock Networks                                       |       |       |      |      |      |      |          |       |          |      |       |

| t <sub>RCKH</sub>  | Input Low to High (Light Load)<br>(Pad to R-cell Input) |       | 2.2   |      | 2.5  |      | 2.9  |          | 3.4   |          | 4.7  | ns    |

| t <sub>RCKL</sub>  | Input High to Low (Light Load)<br>(Pad to R-cell Input) |       | 2.1   |      | 2.4  |      | 2.7  |          | 3.2   |          | 4.4  | ns    |

| t <sub>RCKH</sub>  | Input Low to High (50% Load)<br>(Pad to R-cell Input)   |       | 2.4   |      | 2.7  |      | 3.1  |          | 3.6   |          | 5.1  | ns    |

| t <sub>RCKL</sub>  | Input High to Low (50% Load)<br>(Pad to R-cell Input)   |       | 2.2   |      | 2.5  |      | 2.8  |          | 3.3   |          | 4.6  | ns    |

| t <sub>RCKH</sub>  | Input Low to High (100% Load)<br>(Pad to R-cell Input)  |       | 2.5   |      | 2.9  |      | 3.2  |          | 3.8   |          | 5.3  | ns    |

| t <sub>RCKL</sub>  | Input High to Low (100% Load)<br>(Pad to R-cell Input)  |       | 2.4   |      | 2.7  |      | 3.1  |          | 3.6   |          | 5.0  | ns    |

| t <sub>RPWH</sub>  | Minimum Pulse Width High                                | 1.4   |       | 1.6  |      | 1.8  |      | 2.1      |       | 2.9      |      | ns    |

| t <sub>RPWL</sub>  | Minimum Pulse Width Low                                 | 1.4   |       | 1.6  |      | 1.8  |      | 2.1      |       | 2.9      |      | ns    |

| t <sub>RCKSW</sub> | Maximum Skew (Light Load)                               |       | 1.0   |      | 1.1  |      | 1.3  |          | 1.5   |          | 2.1  | ns    |

| t <sub>RCKSW</sub> | Maximum Skew (50% Load)                                 |       | 0.9   |      | 1.0  |      | 1.2  |          | 1.4   |          | 1.9  | ns    |

| t <sub>RCKSW</sub> | Maximum Skew (100% Load)                                |       | 0.9   |      | 1.0  |      | 1.2  |          | 1.4   |          | 1.9  | ns    |

Note: \*All –3 speed grades have been discontinued.

2-36 v5.3

| SX-A | <b>Family</b> | <b>FPGAs</b> |

|------|---------------|--------------|

|------|---------------|--------------|

| 144-Pin TQFP |                      |                      |                      |  |  |  |  |  |  |

|--------------|----------------------|----------------------|----------------------|--|--|--|--|--|--|

| Pin Number   | A54SX08A<br>Function | A54SX16A<br>Function | A54SX32A<br>Function |  |  |  |  |  |  |

| 1            | GND                  | GND                  | GND                  |  |  |  |  |  |  |

| 2            | TDI, I/O             | TDI, I/O             | TDI, I/O             |  |  |  |  |  |  |

| 3            | I/O                  | 1/0                  | 1/0                  |  |  |  |  |  |  |

| 4            | I/O                  | 1/0                  | I/O                  |  |  |  |  |  |  |

| 5            | I/O                  | 1/0                  | I/O                  |  |  |  |  |  |  |

| 6            | I/O                  | 1/0                  | 1/0                  |  |  |  |  |  |  |

| 7            | I/O                  | 1/0                  | I/O                  |  |  |  |  |  |  |

| 8            | I/O                  | I/O                  | 1/0                  |  |  |  |  |  |  |

| 9            | TMS                  | TMS                  | TMS                  |  |  |  |  |  |  |

| 10           | V <sub>CCI</sub>     | $V_{CCI}$            | $V_{CCI}$            |  |  |  |  |  |  |

| 11           | GND                  | GND                  | GND                  |  |  |  |  |  |  |

| 12           | I/O                  | I/O                  | I/O                  |  |  |  |  |  |  |

| 13           | I/O                  | 1/0                  | I/O                  |  |  |  |  |  |  |

| 14           | I/O                  | I/O                  | I/O                  |  |  |  |  |  |  |

| 15           | I/O                  | 1/0                  | I/O                  |  |  |  |  |  |  |

| 16           | I/O                  | 1/0                  | I/O                  |  |  |  |  |  |  |

| 17           | I/O                  | 1/0                  | I/O                  |  |  |  |  |  |  |

| 18           | I/O                  | 1/0                  | I/O                  |  |  |  |  |  |  |

| 19           | NC                   | NC                   | NC                   |  |  |  |  |  |  |

| 20           | V <sub>CCA</sub>     | V <sub>CCA</sub>     | $V_{CCA}$            |  |  |  |  |  |  |

| 21           | I/O                  | I/O                  | I/O                  |  |  |  |  |  |  |

| 22           | TRST, I/O            | TRST, I/O            | TRST, I/O            |  |  |  |  |  |  |

| 23           | I/O                  | I/O                  | I/O                  |  |  |  |  |  |  |

| 24           | I/O                  | I/O                  | I/O                  |  |  |  |  |  |  |

| 25           | I/O                  | I/O                  | I/O                  |  |  |  |  |  |  |

| 26           | I/O                  | I/O                  | I/O                  |  |  |  |  |  |  |

| 27           | I/O                  | 1/0                  | I/O                  |  |  |  |  |  |  |

| 28           | GND                  | GND                  | GND                  |  |  |  |  |  |  |

| 29           | V <sub>CCI</sub>     | V <sub>CCI</sub>     | V <sub>CCI</sub>     |  |  |  |  |  |  |

| 30           | $V_{CCA}$            | V <sub>CCA</sub>     | $V_{CCA}$            |  |  |  |  |  |  |

| 31           | I/O                  | I/O                  | I/O                  |  |  |  |  |  |  |

| 32           | I/O                  | I/O                  | I/O                  |  |  |  |  |  |  |

| 33           | I/O                  | 1/0                  | I/O                  |  |  |  |  |  |  |

| 34           | I/O                  | 1/0                  | I/O                  |  |  |  |  |  |  |

| 35           | I/O                  | 1/0                  | I/O                  |  |  |  |  |  |  |

| 36           | GND                  | GND                  | GND                  |  |  |  |  |  |  |

| 37           | I/O                  | I/O                  | I/O                  |  |  |  |  |  |  |

| 144-Pin TQFP |                      |                      |                      |  |  |  |  |  |  |  |

|--------------|----------------------|----------------------|----------------------|--|--|--|--|--|--|--|

| Pin Number   | A54SX08A<br>Function | A54SX16A<br>Function | A54SX32A<br>Function |  |  |  |  |  |  |  |

| 38           | I/O                  | 1/0                  | 1/0                  |  |  |  |  |  |  |  |

| 39           | I/O                  | 1/0                  | 1/0                  |  |  |  |  |  |  |  |

| 40           | I/O                  | 1/0                  | I/O                  |  |  |  |  |  |  |  |

| 41           | I/O                  | 1/0                  | 1/0                  |  |  |  |  |  |  |  |

| 42           | I/O                  | 1/0                  | 1/0                  |  |  |  |  |  |  |  |

| 43           | I/O                  | 1/0                  | 1/0                  |  |  |  |  |  |  |  |

| 44           | V <sub>CCI</sub>     | V <sub>CCI</sub>     | V <sub>CCI</sub>     |  |  |  |  |  |  |  |

| 45           | I/O                  | 1/0                  | 1/0                  |  |  |  |  |  |  |  |

| 46           | I/O                  | I/O                  | 1/0                  |  |  |  |  |  |  |  |

| 47           | I/O                  | I/O                  | 1/0                  |  |  |  |  |  |  |  |

| 48           | I/O                  | 1/0                  | 1/0                  |  |  |  |  |  |  |  |

| 49           | I/O                  | 1/0                  | 1/0                  |  |  |  |  |  |  |  |

| 50           | I/O                  | 1/0                  | 1/0                  |  |  |  |  |  |  |  |

| 51           | I/O                  | I/O                  | 1/0                  |  |  |  |  |  |  |  |

| 52           | I/O                  | 1/0                  | 1/0                  |  |  |  |  |  |  |  |

| 53           | I/O                  | 1/0                  | 1/0                  |  |  |  |  |  |  |  |

| 54           | PRB, I/O             | PRB, I/O             | PRB, I/O             |  |  |  |  |  |  |  |

| 55           | I/O                  | 1/0                  | 1/0                  |  |  |  |  |  |  |  |

| 56           | $V_{CCA}$            | $V_{CCA}$            | $V_{CCA}$            |  |  |  |  |  |  |  |

| 57           | GND                  | GND                  | GND                  |  |  |  |  |  |  |  |

| 58           | NC                   | NC                   | NC                   |  |  |  |  |  |  |  |

| 59           | 1/0                  | 1/0                  | I/O                  |  |  |  |  |  |  |  |

| 60           | HCLK                 | HCLK                 | HCLK                 |  |  |  |  |  |  |  |

| 61           | I/O                  | 1/0                  | 1/0                  |  |  |  |  |  |  |  |

| 62           | 1/0                  | 1/0                  | 1/0                  |  |  |  |  |  |  |  |

| 63           | 1/0                  | 1/0                  | I/O                  |  |  |  |  |  |  |  |

| 64           | I/O                  | 1/0                  | 1/0                  |  |  |  |  |  |  |  |

| 65           | 1/0                  | 1/0                  | I/O                  |  |  |  |  |  |  |  |

| 66           | I/O                  | 1/0                  | I/O                  |  |  |  |  |  |  |  |

| 67           | 1/0                  | 1/0                  | I/O                  |  |  |  |  |  |  |  |

| 68           | V <sub>CCI</sub>     | V <sub>CCI</sub>     | V <sub>CCI</sub>     |  |  |  |  |  |  |  |

| 69           | I/O                  | 1/0                  | I/O                  |  |  |  |  |  |  |  |

| 70           | 1/0                  | 1/0                  | I/O                  |  |  |  |  |  |  |  |

| 71           | TDO, I/O             | TDO, I/O             | TDO, I/O             |  |  |  |  |  |  |  |

| 72           | I/O                  | 1/0                  | I/O                  |  |  |  |  |  |  |  |

| 73           | GND                  | GND                  | GND                  |  |  |  |  |  |  |  |

| 74           | I/O                  | 1/0                  | I/O                  |  |  |  |  |  |  |  |

v5.3 3-9

| 176-Pin TQFP  |                      |  |  |  |  |  |  |  |

|---------------|----------------------|--|--|--|--|--|--|--|

| Pin<br>Number | A54SX32A<br>Function |  |  |  |  |  |  |  |

| 145           | I/O                  |  |  |  |  |  |  |  |

| 146           | I/O                  |  |  |  |  |  |  |  |

| 147           | I/O                  |  |  |  |  |  |  |  |

| 148           | I/O                  |  |  |  |  |  |  |  |

| 149           | I/O                  |  |  |  |  |  |  |  |

| 150           | I/O                  |  |  |  |  |  |  |  |

| 151           | I/O                  |  |  |  |  |  |  |  |

| 152           | CLKA                 |  |  |  |  |  |  |  |

| 153           | CLKB                 |  |  |  |  |  |  |  |

| 154           | NC                   |  |  |  |  |  |  |  |

| 155           | GND                  |  |  |  |  |  |  |  |

| 156           | V <sub>CCA</sub>     |  |  |  |  |  |  |  |

| 157           | PRA, I/O             |  |  |  |  |  |  |  |

| 158           | 1/0                  |  |  |  |  |  |  |  |

| 159           | 1/0                  |  |  |  |  |  |  |  |

| 160           | 1/0                  |  |  |  |  |  |  |  |

| 161           | 1/0                  |  |  |  |  |  |  |  |

| 162           | 1/0                  |  |  |  |  |  |  |  |

| 163           | 1/0                  |  |  |  |  |  |  |  |

| 164           | 1/0                  |  |  |  |  |  |  |  |

| 165           | 1/0                  |  |  |  |  |  |  |  |

| 166           | 1/0                  |  |  |  |  |  |  |  |

| 167           | 1/0                  |  |  |  |  |  |  |  |

| 168           | 1/0                  |  |  |  |  |  |  |  |

| 169           | V <sub>CCI</sub>     |  |  |  |  |  |  |  |

| 170           | 1/0                  |  |  |  |  |  |  |  |

| 171           | 1/0                  |  |  |  |  |  |  |  |

| 172           | 1/0                  |  |  |  |  |  |  |  |

| 173           | 1/0                  |  |  |  |  |  |  |  |

| 174           | 1/0                  |  |  |  |  |  |  |  |

| 175           | 1/0                  |  |  |  |  |  |  |  |

| 176           | TCK, I/O             |  |  |  |  |  |  |  |

v5.3 3-13

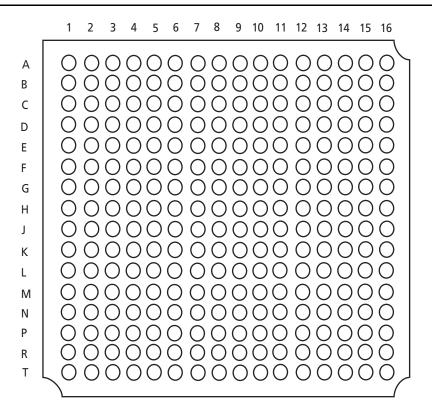

### 256-Pin FBGA

Figure 3-7 • 256-Pin FBGA (Top View)

### **Note**

For Package Manufacturing and Environmental information, visit Resource center at http://www.actel.com/products/rescenter/package/index.html.

v5.3 3-21

| 256-Pin FBGA |                      |                      |                      |  |  |  |  |  |  |

|--------------|----------------------|----------------------|----------------------|--|--|--|--|--|--|

| Pin Number   | A54SX16A<br>Function | A54SX32A<br>Function | A54SX72A<br>Function |  |  |  |  |  |  |

| K5           | I/O                  | 1/0                  | 1/0                  |  |  |  |  |  |  |

| K6           | V <sub>CCI</sub>     | V <sub>CCI</sub>     | V <sub>CCI</sub>     |  |  |  |  |  |  |

| K7           | GND                  | GND                  | GND                  |  |  |  |  |  |  |

| K8           | GND                  | GND                  | GND                  |  |  |  |  |  |  |

| К9           | GND                  | GND                  | GND                  |  |  |  |  |  |  |

| K10          | GND                  | GND                  | GND                  |  |  |  |  |  |  |

| K11          | V <sub>CCI</sub>     | V <sub>CCI</sub>     | V <sub>CCI</sub>     |  |  |  |  |  |  |

| K12          | I/O                  | 1/0                  | 1/0                  |  |  |  |  |  |  |

| K13          | I/O                  | I/O                  | 1/0                  |  |  |  |  |  |  |

| K14          | I/O                  | 1/0                  | 1/0                  |  |  |  |  |  |  |

| K15          | NC                   | I/O                  | 1/0                  |  |  |  |  |  |  |

| K16          | I/O                  | I/O                  | 1/0                  |  |  |  |  |  |  |

| L1           | I/O                  | I/O                  | 1/0                  |  |  |  |  |  |  |

| L2           | I/O                  | 1/0                  | 1/0                  |  |  |  |  |  |  |

| L3           | I/O                  | 1/0                  | 1/0                  |  |  |  |  |  |  |

| L4           | I/O                  | 1/0                  | I/O                  |  |  |  |  |  |  |

| L5           | I/O                  | 1/0                  | 1/0                  |  |  |  |  |  |  |

| L6           | I/O                  | 1/0                  | 1/0                  |  |  |  |  |  |  |

| L7           | V <sub>CCI</sub>     | V <sub>CCI</sub>     | V <sub>CCI</sub>     |  |  |  |  |  |  |

| L8           | V <sub>CCI</sub>     | V <sub>CCI</sub>     | V <sub>CCI</sub>     |  |  |  |  |  |  |

| L9           | V <sub>CCI</sub>     | V <sub>CCI</sub>     | V <sub>CCI</sub>     |  |  |  |  |  |  |

| L10          | V <sub>CCI</sub>     | V <sub>CCI</sub>     | V <sub>CCI</sub>     |  |  |  |  |  |  |

| L11          | I/O                  | 1/0                  | I/O                  |  |  |  |  |  |  |

| L12          | I/O                  | 1/0                  | I/O                  |  |  |  |  |  |  |

| L13          | I/O                  | I/O                  | 1/0                  |  |  |  |  |  |  |

| L14          | I/O                  | 1/0                  | I/O                  |  |  |  |  |  |  |

| L15          | I/O                  | 1/0                  | I/O                  |  |  |  |  |  |  |

| L16          | NC                   | I/O                  | 1/0                  |  |  |  |  |  |  |

| M1           | I/O                  | 1/0                  | I/O                  |  |  |  |  |  |  |

| M2           | I/O                  | 1/0                  | I/O                  |  |  |  |  |  |  |

| M3           | I/O                  | 1/0                  | I/O                  |  |  |  |  |  |  |

| M4           | I/O                  | 1/0                  | I/O                  |  |  |  |  |  |  |

| M5           | I/O                  | 1/0                  | I/O                  |  |  |  |  |  |  |

| M6           | I/O                  | 1/0                  | I/O                  |  |  |  |  |  |  |

| M7           | I/O                  | 1/0                  | QCLKA                |  |  |  |  |  |  |

| M8           | PRB, I/O             | PRB, I/O             | PRB, I/O             |  |  |  |  |  |  |

| M9           | I/O                  | 1/0                  | I/O                  |  |  |  |  |  |  |

| 256-Pin FBGA |                      |                      |                      |  |  |  |  |  |  |

|--------------|----------------------|----------------------|----------------------|--|--|--|--|--|--|

| Pin Number   | A54SX16A<br>Function | A54SX32A<br>Function | A54SX72A<br>Function |  |  |  |  |  |  |

| M10          | 1/0                  | 1/0                  | 1/0                  |  |  |  |  |  |  |

| M11          | 1/0                  | 1/0                  | 1/0                  |  |  |  |  |  |  |

| M12          | NC                   | I/O                  | 1/0                  |  |  |  |  |  |  |

| M13          | 1/0                  | 1/0                  | 1/0                  |  |  |  |  |  |  |

| M14          | NC                   | 1/0                  | 1/0                  |  |  |  |  |  |  |

| M15          | 1/0                  | I/O                  | I/O                  |  |  |  |  |  |  |

| M16          | 1/0                  | I/O                  | 1/0                  |  |  |  |  |  |  |

| N1           | 1/0                  | I/O                  | I/O                  |  |  |  |  |  |  |

| N2           | 1/0                  | I/O                  | I/O                  |  |  |  |  |  |  |

| N3           | 1/0                  | I/O                  | I/O                  |  |  |  |  |  |  |

| N4           | 1/0                  | I/O                  | I/O                  |  |  |  |  |  |  |

| N5           | 1/0                  | I/O                  | I/O                  |  |  |  |  |  |  |

| N6           | 1/0                  | I/O                  | I/O                  |  |  |  |  |  |  |

| N7           | 1/0                  | I/O                  | I/O                  |  |  |  |  |  |  |

| N8           | 1/0                  | I/O                  | I/O                  |  |  |  |  |  |  |

| N9           | 1/0                  | I/O                  | I/O                  |  |  |  |  |  |  |

| N10          | I/O                  | I/O                  | I/O                  |  |  |  |  |  |  |

| N11          | 1/0                  | I/O                  | I/O                  |  |  |  |  |  |  |

| N12          | 1/0                  | I/O                  | I/O                  |  |  |  |  |  |  |

| N13          | 1/0                  | I/O                  | I/O                  |  |  |  |  |  |  |

| N14          | 1/0                  | I/O                  | I/O                  |  |  |  |  |  |  |

| N15          | 1/0                  | I/O                  | I/O                  |  |  |  |  |  |  |

| N16          | 1/0                  | I/O                  | I/O                  |  |  |  |  |  |  |

| P1           | I/O                  | I/O                  | I/O                  |  |  |  |  |  |  |

| P2           | GND                  | GND                  | GND                  |  |  |  |  |  |  |

| P3           | 1/0                  | I/O                  | I/O                  |  |  |  |  |  |  |

| P4           | 1/0                  | I/O                  | I/O                  |  |  |  |  |  |  |

| P5           | NC                   | I/O                  | I/O                  |  |  |  |  |  |  |

| P6           | 1/0                  | I/O                  | 1/0                  |  |  |  |  |  |  |

| P7           | I/O                  | I/O                  | 1/0                  |  |  |  |  |  |  |

| P8           | I/O                  | I/O                  | 1/0                  |  |  |  |  |  |  |

| P9           | I/O                  | I/O                  | 1/0                  |  |  |  |  |  |  |

| P10          | NC                   | I/O                  | 1/0                  |  |  |  |  |  |  |

| P11          | I/O                  | I/O                  | 1/0                  |  |  |  |  |  |  |

| P12          | I/O                  | I/O                  | 1/0                  |  |  |  |  |  |  |

| P13          | V <sub>CCA</sub>     | V <sub>CCA</sub>     | V <sub>CCA</sub>     |  |  |  |  |  |  |

| P14          | 1/0                  | I/O                  | 1/0                  |  |  |  |  |  |  |

3-24 v5.3

## 484-Pin FBGA

| _                                | 1                   | 2                    | 3                  | 4                    | 5                    | 6    | 7    | 8    | 9     | 10            | 11            | 12            | 13   | 14            | 15            | 16            | 17            | 18   | 19   | 20   | 21   | 22                   | 23                   | 242                | 252 | 6 |

|----------------------------------|---------------------|----------------------|--------------------|----------------------|----------------------|------|------|------|-------|---------------|---------------|---------------|------|---------------|---------------|---------------|---------------|------|------|------|------|----------------------|----------------------|--------------------|-----|---|

| ABCDEFGHJKLMNPRTUVWY             | 0000000000000000000 | 00000000000000000000 | 000000000000000000 | 00000000000000000000 | 00000000000000000000 | 0000 | 0000 | 0000 | 00000 | 00000 0000000 | 00000 0000000 | 00000 0000000 | 0000 | 00000 0000000 | 00000 0000000 | 00000 0000000 | 00000 0000000 | 0000 | 0000 | 0000 | 0000 | 00000000000000000000 | 00000000000000000000 | 000000000000000000 |     |   |

| T<br>U<br>V<br>W                 | 0000                | 0000                 | 0000               | 0000                 | 0000                 |      |      |      |       | Ō             | Õ             | Õ             | Ō    | Ō             | Ō             | Õ             | Ō             |      |      |      |      | 0000                 | 0000                 | 0000               |     |   |

| AA<br>AB<br>AC<br>AD<br>AE<br>AF | 00000               | 00000                | 000                | 00000                | 00000                | 000  | 000  | 000  | 000   | 000           | 000           | 000           | 000  | 000           | 000           | 000           | 000           | 000  | 000  | 000  | 000  | 00000                | 00000                | 00000              |     |   |

Figure 3-8 • 484-Pin FBGA (Top View)

### Note

For Package Manufacturing and Environmental information, visit Resource center at http://www.actel.com/products/rescenter/package/index.html.

3-26 v5.3

# **Datasheet Information**

# **List of Changes**

The following table lists critical changes that were made in the current version of the document.

| <b>Previous Version</b> | Changes in Current Version (v5.3)                                                                             | Page  |

|-------------------------|---------------------------------------------------------------------------------------------------------------|-------|

| v5.2                    | –3 speed grades have been discontinued.                                                                       | N/A   |

| (June 2006)             | The "SX-A Timing Model" was updated with –2 data.                                                             | 2-14  |

| v5.1                    | RoHS information was added to the "Ordering Information".                                                     | ii    |

| February 2005           | The "Programming" section was updated.                                                                        | 1-13  |

| v5.0                    | Revised Table 1 and the timing data to reflect the phase out of the $-3$ speed grade for the A54SX08A device. | i     |

|                         | The "Thermal Characteristics" section was updated.                                                            | 2-11  |

|                         | The "176-Pin TQFP" was updated to add pins 81 to 90.                                                          | 3-11  |

|                         | The "484-Pin FBGA" was updated to add pins R4 to Y26                                                          | 3-26  |

| v4.0                    | The "Temperature Grade Offering" is new.                                                                      | 1-iii |

|                         | The "Speed Grade and Temperature Grade Matrix" is new.                                                        | 1-iii |

|                         | "SX-A Family Architecture" was updated.                                                                       | 1-1   |

|                         | "Clock Resources" was updated.                                                                                | 1-5   |

|                         | "User Security" was updated.                                                                                  | 1-7   |

|                         | "Power-Up/Down and Hot Swapping" was updated.                                                                 | 1-7   |

|                         | "Dedicated Mode" is new                                                                                       | 1-9   |

|                         | Table 1-5 is new.                                                                                             | 1-9   |

|                         | "JTAG Instructions" is new                                                                                    | 1-10  |

|                         | "Design Considerations" was updated.                                                                          | 1-12  |

|                         | The "Programming" section is new.                                                                             | 1-13  |

|                         | "Design Environment" was updated.                                                                             | 1-13  |

|                         | "Pin Description" was updated.                                                                                | 1-15  |

|                         | Table 2-1 was updated.                                                                                        | 2-1   |

|                         | Table 2-2 was updated.                                                                                        | 2-1   |

|                         | Table 2-3 is new.                                                                                             | 2-1   |

|                         | Table 2-4 is new.                                                                                             | 2-1   |

|                         | Table 2-5 was updated.                                                                                        | 2-2   |

|                         | Table 2-6 was updated.                                                                                        | 2-2   |

|                         | "Power Dissipation" is new.                                                                                   | 2-8   |

|                         | Table 2-11 was updated.                                                                                       | 2-9   |

v5.3 4