Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

### Details

E-XF

| Details                        |                                                                          |

|--------------------------------|--------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                 |

| Number of LABs/CLBs            | 768                                                                      |

| Number of Logic Elements/Cells | -                                                                        |

| Total RAM Bits                 | -                                                                        |

| Number of I/O                  | 81                                                                       |

| Number of Gates                | 12000                                                                    |

| Voltage - Supply               | 2.25V ~ 5.25V                                                            |

| Mounting Type                  | Surface Mount                                                            |

| Operating Temperature          | 0°C ~ 70°C (TA)                                                          |

| Package / Case                 | 100-LQFP                                                                 |

| Supplier Device Package        | 100-TQFP (14x14)                                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a54sx08a-tq100 |

|                                |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### SX-A Family FPGAs

## Theta-JA

Junction-to-ambient thermal resistance ( $\theta_{JA}$ ) is determined under standard conditions specified by JESD-51 series but has little relevance in actual performance of the product in real application. It should be employed with caution but is useful for comparing the thermal performance of one package to another.

A sample calculation to estimate the absolute maximum power dissipation allowed (worst case) for a 329-pin PBGA package at still air is as follows. i.e.:

$$\theta_{JA} = 17.1^{\circ}$$

C/W is taken from Table 2-12 on page 2-11

$T_A = 125$ °C is the maximum limit of ambient (from the datasheet)

Max. Allowed Power =

$$\frac{\text{Max Junction Temp - Max. Ambient Temp}}{\theta_{JA}} = \frac{150^{\circ}\text{C} - 125^{\circ}\text{C}}{17.1^{\circ}\text{C/W}} = 1.46 \text{ W}$$

EQ 2-11

The device's power consumption must be lower than the calculated maximum power dissipation by the package.

The power consumption of a device can be calculated using the Actel power calculator. If the power consumption is higher than the device's maximum allowable power dissipation, then a heat sink can be attached on top of the case or the airflow inside the system must be increased.

## Theta-JC

Junction-to-case thermal resistance ( $\theta_{JC}$ ) measures the ability of a device to dissipate heat from the surface of the chip to the top or bottom surface of the package. It is applicable for packages used with external heat sinks and only applies to situations where all or nearly all of the heat is dissipated through the surface in consideration. If the power consumption is higher than the calculated maximum power dissipation of the package, then a heat sink is required.

## **Calculation for Heat Sink**

For example, in a design implemented in a FG484 package, the power consumption value using the power calculator is 3.00 W. The user-dependent data  $T_J$  and  $T_A$  are given as follows:

$$T_J = 110^{\circ}C$$

$T_A = 70^{\circ}C$

From the datasheet:

$\theta_{JA} = 18.0^{\circ}C/W$  $\theta_{JC} = 3.2^{\circ}C/W$

$$P = \frac{\text{Max Junction Temp} - \text{Max. Ambient Temp}}{\theta_{JA}} = \frac{110^{\circ}\text{C} - 70^{\circ}\text{C}}{18.0^{\circ}\text{C/W}} = 2.22 \text{ W}$$

EQ 2-12

The 2.22 W power is less than then required 3.00 W; therefore, the design requires a heat sink or the airflow where the device is mounted should be increased. The design's junction-to-air thermal resistance requirement can be estimated by:

$$\theta_{JA} = \frac{Max Junction Temp - Max. Ambient Temp}{P} = \frac{110^{\circ}C - 70^{\circ}C}{3.00 W} = 13.33^{\circ}C/W$$

EQ 2-13

# **SX-A Timing Model**

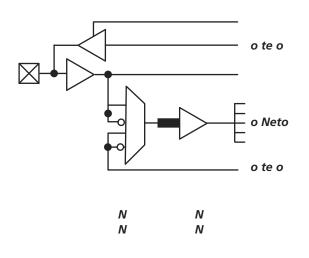

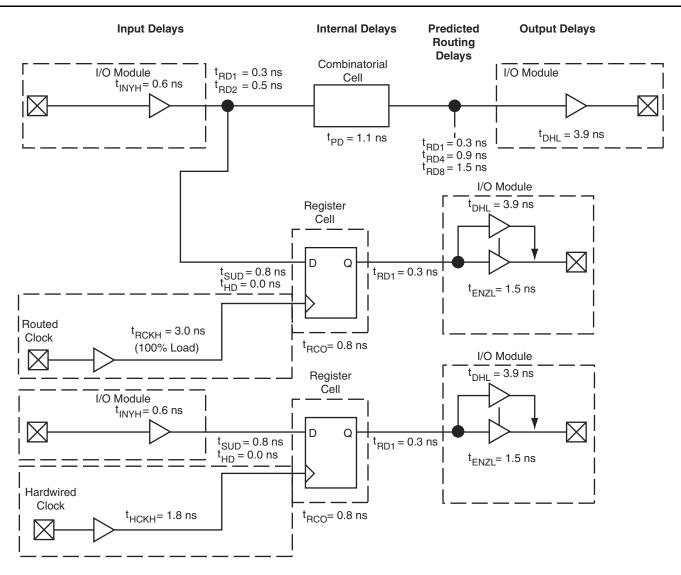

*Note:* \*Values shown for A54SX72A, –2, worst-case commercial conditions at 5 V PCI with standard place-and-route. Figure 2-3 • SX-A Timing Model

# **Sample Path Calculations**

## **Hardwired Clock**

| External Setup            | = | (t <sub>INYH</sub> + t <sub>RD1</sub> + t <sub>SUD</sub> ) – t <sub>HCKH</sub> |

|---------------------------|---|--------------------------------------------------------------------------------|

|                           | = | 0.6 + 0.3 + 0.8 - 1.8 = - 0.1 ns                                               |

| Clock-to-Out (Pad-to-Pad) | = | t <sub>HCKH</sub> + t <sub>RCO</sub> + t <sub>RD1</sub> + t <sub>DHL</sub>     |

|                           | = | 1.8 + 0.8 + 0.3 + 3.9 = 6.8 ns                                                 |

## **Routed Clock**

| External Setup           | = (t <sub>INYH</sub> + t <sub>RD1</sub> + t <sub>SUD</sub> ) – t <sub>RCKH</sub> |

|--------------------------|----------------------------------------------------------------------------------|

|                          | = 0.6 + 0.3 + 0.8 - 3.0 = -1.3 ns                                                |

| Clock-to-Out (Pad-to-Pad | $I) = t_{RCKH} + t_{RCO} + t_{RD1} + t_{DHL}$                                    |

|                          | = 3.0 + 0.8 + 0.3 + 3.9 = 8.0  ns                                                |

### SX-A Family FPGAs

### Table 2-36 A54SX72A Timing Characteristics

| (Worst-Case Commercial Conditions | $V_{CCA} = 2.25 V, V_{CCI} =$ | 2.25 V, T <sub>J</sub> = 70°C) |

|-----------------------------------|-------------------------------|--------------------------------|

|-----------------------------------|-------------------------------|--------------------------------|

|                    |                                                         | -3 Speed* |      | -2 Speed |      | -1 Speed |      | Std. Speed |      | -F Speed |      |       |

|--------------------|---------------------------------------------------------|-----------|------|----------|------|----------|------|------------|------|----------|------|-------|

| Parameter          | Description                                             | Min.      | Max. | Min.     | Max. | Min.     | Max. | Min.       | Max. | Min.     | Max. | Units |

| Dedicated (        | (Hardwired) Array Clock Netwo                           | orks      |      |          |      |          |      |            |      |          |      |       |

| t <sub>нскн</sub>  | Input Low to High<br>(Pad to R-cell Input)              |           | 1.6  |          | 1.9  |          | 2.1  |            | 2.5  |          | 3.8  | ns    |

| t <sub>HCKL</sub>  | Input High to Low<br>(Pad to R-cell Input)              |           | 1.6  |          | 1.9  |          | 2.1  |            | 2.5  |          | 3.8  | ns    |

| t <sub>HPWH</sub>  | Minimum Pulse Width High                                | 1.5       |      | 1.7      |      | 2.0      |      | 2.3        |      | 3.2      |      | ns    |

| t <sub>HPWL</sub>  | Minimum Pulse Width Low                                 | 1.5       |      | 1.7      |      | 2.0      |      | 2.3        |      | 3.2      |      | ns    |

| t <sub>HCKSW</sub> | Maximum Skew                                            |           | 1.4  |          | 1.6  |          | 1.8  |            | 2.1  |          | 3.3  | ns    |

| t <sub>HP</sub>    | Minimum Period                                          | 3.0       |      | 3.4      |      | 4.0      |      | 4.6        |      | 6.4      |      | ns    |

| f <sub>HMAX</sub>  | Maximum Frequency                                       |           | 333  |          | 294  |          | 250  |            | 217  |          | 156  | MHz   |

| Routed Arra        | ay Clock Networks                                       |           |      |          |      |          |      |            |      |          |      |       |

| t <sub>RCKH</sub>  | Input Low to High (Light Load)<br>(Pad to R-cell Input) |           | 2.3  |          | 2.6  |          | 2.9  |            | 3.4  |          | 4.8  | ns    |

| t <sub>RCKL</sub>  | Input High to Low (Light Load)<br>(Pad to R-cell Input) |           | 2.8  |          | 3.2  |          | 3.7  |            | 4.3  |          | 6.0  | ns    |

| t <sub>RCKH</sub>  | Input Low to High (50% Load)<br>(Pad to R-cell Input)   |           | 2.4  |          | 2.8  |          | 3.2  |            | 3.7  |          | 5.2  | ns    |

| t <sub>RCKL</sub>  | Input High to Low (50% Load)<br>(Pad to R-cell Input)   |           | 2.9  |          | 3.3  |          | 3.8  |            | 4.5  |          | 6.2  | ns    |

| t <sub>RCKH</sub>  | Input Low to High (100% Load)<br>(Pad to R-cell Input)  |           | 2.6  |          | 3.0  |          | 3.4  |            | 4.0  |          | 5.6  | ns    |

| t <sub>RCKL</sub>  | Input High to Low (100% Load)<br>(Pad to R-cell Input)  |           | 3.1  |          | 3.6  |          | 4.0  |            | 4.7  |          | 6.6  | ns    |

| t <sub>RPWH</sub>  | Minimum Pulse Width High                                | 1.5       |      | 1.7      |      | 2.0      |      | 2.3        |      | 3.2      |      | ns    |

| t <sub>RPWL</sub>  | Minimum Pulse Width Low                                 | 1.5       |      | 1.7      |      | 2.0      |      | 2.3        |      | 3.2      |      | ns    |

| t <sub>RCKSW</sub> | Maximum Skew (Light Load)                               |           | 1.9  |          | 2.2  |          | 2.5  |            | 3.0  |          | 4.1  | ns    |

| t <sub>RCKSW</sub> | Maximum Skew (50% Load)                                 |           | 1.8  |          | 2.1  |          | 2.4  |            | 2.8  |          | 3.9  | ns    |

| t <sub>RCKSW</sub> | Maximum Skew (100% Load)                                |           | 1.8  |          | 2.1  |          | 2.4  |            | 2.8  |          | 3.9  | ns    |

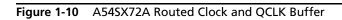

| Quadrant A         | rray Clock Networks                                     |           |      |          |      |          |      |            |      |          |      |       |

| t <sub>QCKH</sub>  | Input Low to High (Light Load)<br>(Pad to R-cell Input) |           | 2.6  |          | 3.0  |          | 3.4  |            | 4.0  |          | 5.6  | ns    |

| t <sub>QCHKL</sub> | Input High to Low (Light Load)<br>(Pad to R-cell Input) |           | 2.6  |          | 3.0  |          | 3.3  |            | 3.9  |          | 5.5  | ns    |

| t <sub>QCKH</sub>  | Input Low to High (50% Load)<br>(Pad to R-cell Input)   |           | 2.8  |          | 3.2  |          | 3.6  |            | 4.3  |          | 6.0  | ns    |

| t <sub>QCHKL</sub> | Input High to Low (50% Load)<br>(Pad to R-cell Input)   |           | 2.8  |          | 3.2  |          | 3.6  |            | 4.2  |          | 5.9  | ns    |

Note: \*All –3 speed grades have been discontinued.