Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

EXF

| Product Status                 | Active                                                                      |

|--------------------------------|-----------------------------------------------------------------------------|

| Number of LABs/CLBs            | 1452                                                                        |

| Number of Logic Elements/Cells | ·                                                                           |

| Total RAM Bits                 | ·                                                                           |

| Number of I/O                  | 81                                                                          |

| Number of Gates                | 24000                                                                       |

| Voltage - Supply               | 2.25V ~ 5.25V                                                               |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | -40°C ~ 85°C (TA)                                                           |

| Package / Case                 | 100-LQFP                                                                    |

| Supplier Device Package        | 100-TQFP (14x14)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a54sx16a-1tqg100i |

|                                |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Logic Module Design

The SX-A family architecture is described as a "sea-ofmodules" architecture because the entire floor of the device is covered with a grid of logic modules with virtually no chip area lost to interconnect elements or routing. The Actel SX-A family provides two types of logic modules: the register cell (R-cell) and the combinatorial cell (C-cell).

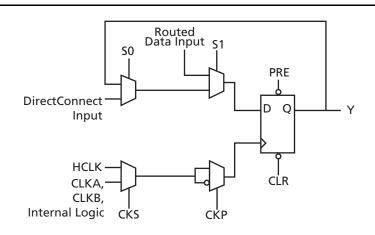

The R-cell contains a flip-flop featuring asynchronous clear, asynchronous preset, and clock enable, using the S0 and S1 lines control signals (Figure 1-2). The R-cell registers feature programmable clock polarity selectable on a register-byregister basis. This provides additional flexibility while allowing mapping of synthesized functions into the SX-A FPGA. The clock source for the R-cell can be chosen from either the hardwired clock, the routed clocks, or internal logic.

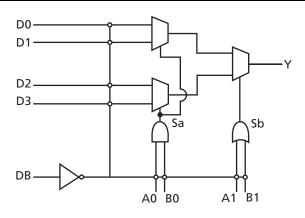

The C-cell implements a range of combinatorial functions of up to five inputs (Figure 1-3). Inclusion of the DB input and its associated inverter function allows up to 4,000 different combinatorial functions to be implemented in a single module. An example of the flexibility enabled by the inversion capability is the ability to integrate a 3-input exclusive-OR function into a single C-cell. This facilitates construction of 9-bit parity-tree functions with 1.9 ns propagation delays.

## **Module Organization**

All C-cell and R-cell logic modules are arranged into horizontal banks called Clusters. There are two types of Clusters: Type 1 contains two C-cells and one R-cell, while Type 2 contains one C-cell and two R-cells.

Clusters are grouped together into SuperClusters (Figure 1-4 on page 1-3). SuperCluster 1 is a two-wide grouping of Type 1 Clusters. SuperCluster 2 is a two-wide group containing one Type 1 Cluster and one Type 2 Cluster. SX-A devices feature more SuperCluster 1 modules than SuperCluster 2 modules because designers typically require significantly more combinatorial logic than flip-flops.

#### Figure 1-2 • R-Cell

Figure 1-3 • C-Cell

## **Boundary-Scan Testing (BST)**

All SX-A devices are IEEE 1149.1 compliant and offer superior diagnostic and testing capabilities by providing Boundary Scan Testing (BST) and probing capabilities. The BST function is controlled through the special JTAG pins (TMS, TDI, TCK, TDO, and TRST). The functionality of the JTAG pins is defined by two available modes: Dedicated and Flexible. TMS cannot be employed as a user I/O in either mode.

## **Dedicated Mode**

In Dedicated mode, all JTAG pins are reserved for BST; designers cannot use them as regular I/Os. An internal pull-up resistor is automatically enabled on both TMS and TDI pins, and the TMS pin will function as defined in the IEEE 1149.1 (JTAG) specification.

To select Dedicated mode, the user must reserve the JTAG pins in Actel's Designer software. Reserve the JTAG pins by checking the **Reserve JTAG** box in the Device Selection Wizard (Figure 1-12).

The default for the software is Flexible mode; all boxes are unchecked. Table 1-5 lists the definitions of the options in the Device Selection Wizard.

## Flexible Mode

In Flexible mode, TDI, TCK, and TDO may be employed as either user I/Os or as JTAG input pins. The internal resistors on the TMS and TDI pins are not present in flexible JTAG mode.

To select the Flexible mode, uncheck the **Reserve JTAG** box in the Device Selection Wizard dialog in the Actel Designer software. In Flexible mode, TDI, TCK, and TDO pins may function as user I/Os or BST pins. The functionality is controlled by the BST Test Access Port (TAP) controller. The TAP controller receives two control inputs, TMS and TCK. Upon power-up, the TAP controller enters the Test-Logic-Reset state. In this state, TDI, TCK, and TDO function as user I/Os. The TDI, TCK, and TDO are transformed from user I/Os into BST pins when a rising edge on TCK is detected while TMS is at logic low. To return to Test-Logic Reset state, TMS must be high for at least five TCK cycles. **An external 10 k pull-up resistor to V<sub>CCI</sub> should be placed on the TMS pin to pull it High by default.**

Table 1-6 describes the different configuration requirements of BST pins and their functionality in different modes.

| Table 1-6 • | <b>Boundary-Scan Pin Configurations and</b> |

|-------------|---------------------------------------------|

|             | Functions                                   |

| Mode                | Designer<br>"Reserve JTAG"<br>Selection | TAP Controller<br>State         |

|---------------------|-----------------------------------------|---------------------------------|

| Dedicated (JTAG)    | Checked                                 | Any                             |

| Flexible (User I/O) | Unchecked                               | Test-Logic-Reset                |

| Flexible (JTAG)     | Unchecked                               | Any EXCEPT Test-<br>Logic-Reset |

#### Figure 1-12 • Device Selection Wizard

Table 1-5 • Reserve Pin Definitions

| Pin                        | Function                                                                                   |  |  |  |  |  |

|----------------------------|--------------------------------------------------------------------------------------------|--|--|--|--|--|

| Reserve JTAG               | Keeps pins from being used and<br>changes the behavior of JTAG pins (no<br>pull-up on TMS) |  |  |  |  |  |

| Reserve JTAG Test<br>Reset | Regular I/O or JTAG reset with an internal pull-up                                         |  |  |  |  |  |

| Reserve Probe              | Keeps pins from being used or regular<br>I/O                                               |  |  |  |  |  |

## TRST Pin

The TRST pin functions as a dedicated Boundary-Scan Reset pin when the **Reserve JTAG Test Reset** option is selected as shown in Figure 1-12. An internal pull-up resistor is permanently enabled on the TRST pin in this mode. Actel recommends connecting this pin to ground in normal operation to keep the JTAG state controller in the Test-Logic-Reset state. When JTAG is being used, it can be left floating or can be driven high.

When the **Reserve JTAG Test Reset** option is not selected, this pin will function as a regular I/O. If unused as an I/O in the design, it will be configured as a tristated output.

## **Probing Capabilities**

SX-A devices also provide an internal probing capability that is accessed with the JTAG pins. The Silicon Explorer II diagnostic hardware is used to control the TDI, TCK, TMS, and TDO pins to select the desired nets for debugging. The user assigns the selected internal nets in Actel Silicon Explorer II software to the PRA/PRB output pins for observation. Silicon Explorer II automatically places the device into JTAG mode. However, probing functionality is only activated when the TRST pin is driven high or left floating, allowing the internal pull-up resistor to pull TRST High. If the TRST pin is held Low, the TAP controller remains in the Test-Logic-Reset state so no probing can be performed. However, the user must drive the TRST pin High or allow the internal pull-up resistor to pull TRST High. When selecting the **Reserve Probe Pin** box as shown in Figure 1-12 on page 1-9, direct the layout tool to reserve the PRA and PRB pins as dedicated outputs for probing. This **Reserve** option is merely a guideline. If the designer assigns user I/Os to the PRA and PRB pins and selects the **Reserve Probe Pin** option, Designer Layout will override the **Reserve Probe Pin** option and place the user I/Os on those pins.

To allow probing capabilities, the security fuse must not be programmed. Programming the security fuse disables the JTAG and probe circuitry. Table 1-9 summarizes the possible device configurations for probing once the device leaves the Test-Logic-Reset JTAG state.

| JTAG Mode | TRST <sup>1</sup> | Security Fuse Programmed | PRA, PRB <sup>2</sup> | TDI, TCK, TDO <sup>2</sup> |

|-----------|-------------------|--------------------------|-----------------------|----------------------------|

| Dedicated | Low               | No                       | User I/O <sup>3</sup> | JTAG Disabled              |

|           | High              | No                       | Probe Circuit Outputs | JTAG I/O                   |

| Flexible  | Low               | No                       | User I/O <sup>3</sup> | User I/O <sup>3</sup>      |

|           | High No           |                          | Probe Circuit Outputs | JTAG I/O                   |

|           |                   | Yes                      | Probe Circuit Secured | Probe Circuit Secured      |

Table 1-9 • Device Configuration Options for Probe Capability (TRST Pin Reserved)

Notes:

1. If the TRST pin is not reserved, the device behaves according to TRST = High as described in the table.

2. Avoid using the TDI, TCK, TDO, PRA, and PRB pins as input or bidirectional ports. Since these pins are active during probing, input signals will not pass through these pins and may cause contention.

3. If no user signal is assigned to these pins, they will behave as unused I/Os in this mode. Unused pins are automatically tristated by the Designer software.

# **Electrical Specifications**

Table 2-5 • 3.3 V LVTTL and 5 V TTL Electrical Specifications

|                                  |                                                                  |                            | Comm                 | ercial | Industrial           |      |       |  |

|----------------------------------|------------------------------------------------------------------|----------------------------|----------------------|--------|----------------------|------|-------|--|

| Symbol                           | Parameter                                                        |                            | Min.                 | Max.   | Min.                 | Max. | Units |  |

| V <sub>OH</sub>                  | $V_{CCI} = Minimum$<br>$V_I = V_{IH} \text{ or } V_{IL}$         | $(I_{OH} = -1 \text{ mA})$ | 0.9 V <sub>CCI</sub> |        | 0.9 V <sub>CCI</sub> |      | V     |  |

|                                  | $V_{CCI} = Minimum$<br>$V_I = V_{IH} \text{ or } V_{IL}$         | (I <sub>OH</sub> = -8 mA)  | 2.4                  |        | 2.4                  |      | V     |  |

| V <sub>OL</sub>                  | $V_{CCI} = Minimum$<br>$V_I = V_{IH} \text{ or } V_{IL}$         | (I <sub>OL</sub> = 1 mA)   |                      | 0.4    |                      | 0.4  | V     |  |

|                                  | $V_{CCI} = Minimum$<br>$V_I = V_{IH} \text{ or } V_{IL}$         | (I <sub>OL</sub> = 12 mA)  |                      | 0.4    |                      | 0.4  | V     |  |

| V <sub>IL</sub>                  | Input Low Voltage                                                |                            |                      | 0.8    |                      | 0.8  | V     |  |

| V <sub>IH</sub>                  | Input High Voltage                                               |                            | 2.0                  | 5.75   | 2.0                  | 5.75 | V     |  |

| I <sub>IL</sub> /I <sub>IH</sub> | Input Leakage Current, V <sub>IN</sub> = V <sub>CCI</sub> or GND |                            | -10                  | 10     | -10                  | 10   | μA    |  |

| I <sub>OZ</sub>                  | Tristate Output Leakage Current                                  |                            | -10                  | 10     | -10                  | 10   | μΑ    |  |

| t <sub>R</sub> , t <sub>F</sub>  | Input Transition Time t <sub>R</sub> , t <sub>F</sub>            |                            |                      | 10     |                      | 10   | ns    |  |

| C <sub>IO</sub>                  | I/O Capacitance                                                  |                            |                      | 10     |                      | 10   | pF    |  |

| I <sub>CC</sub>                  | Standby Current                                                  |                            |                      | 10     |                      | 20   | mA    |  |

| IV Curve*                        | Can be derived from the IBIS model on the web                    | •<br>).                    |                      |        | •                    |      |       |  |

Note: \*The IBIS model can be found at http://www.actel.com/download/ibis/default.aspx.

## Table 2-6 • 2.5 V LVCMOS2 Electrical Specifications

|                                  |                                                                  |                               | Comn | nercial | Indu |      |       |

|----------------------------------|------------------------------------------------------------------|-------------------------------|------|---------|------|------|-------|

| Symbol                           | Parameter                                                        |                               | Min. | Max.    | Min. | Max. | Units |

| V <sub>OH</sub>                  | $V_{DD} = MIN,$<br>$V_{I} = V_{IH} \text{ or } V_{IL}$           | $(I_{OH} = -100 \mu\text{A})$ | 2.1  |         | 2.1  |      | V     |

|                                  | $V_{DD} = MIN,$<br>$V_{I} = V_{IH} \text{ or } V_{IL}$           | (I <sub>OH</sub> = -1 mA)     | 2.0  |         | 2.0  |      | V     |

|                                  | $V_{DD} = MIN,$<br>$V_{I} = V_{IH} \text{ or } V_{IL}$           | (I <sub>OH</sub> =2 mA)       | 1.7  |         | 1.7  |      | V     |

| V <sub>OL</sub>                  | $V_{DD} = MIN,$<br>$V_{I} = V_{IH} \text{ or } V_{IL}$           | (I <sub>OL</sub> = 100 μA)    |      | 0.2     |      | 0.2  | V     |

|                                  | $V_{DD} = MIN,$<br>$V_{I} = V_{IH} \text{ or } V_{IL}$           | (I <sub>OL</sub> = 1 mA)      |      | 0.4     |      | 0.4  | V     |

|                                  | $V_{DD} = MIN,$<br>$V_{I} = V_{IH} \text{ or } V_{IL}$           | (I <sub>OL</sub> = 2 mA)      |      | 0.7     |      | 0.7  | V     |

| V <sub>IL</sub>                  | Input Low Voltage, V <sub>OUT</sub> ≤ V <sub>VOL(max)</sub>      |                               | -0.3 | 0.7     | -0.3 | 0.7  | V     |

| V <sub>IH</sub>                  | Input High Voltage, V <sub>OUT</sub> ≥ V <sub>VOH(min)</sub>     |                               | 1.7  | 5.75    | 1.7  | 5.75 | V     |

| I <sub>IL</sub> /I <sub>IH</sub> | Input Leakage Current, V <sub>IN</sub> = V <sub>CCI</sub> or GND |                               | -10  | 10      | -10  | 10   | μΑ    |

| I <sub>OZ</sub>                  | Tristate Output Leakage Current, $V_{OUT} = V_{CCI}$ or GND      |                               | -10  | 10      | -10  | 10   | μΑ    |

| t <sub>R</sub> , t <sub>F</sub>  | Input Transition Time t <sub>R</sub> , t <sub>F</sub>            |                               |      | 10      |      | 10   | ns    |

| C <sub>IO</sub>                  | I/O Capacitance                                                  |                               |      | 10      |      | 10   | pF    |

| I <sub>CC</sub>                  | Standby Current                                                  |                               |      | 10      |      | 20   | mA    |

| IV Curve*                        | Can be derived from the IBIS model on the web.                   |                               |      |         |      |      | •     |

Note: \*The IBIS model can be found at http://www.actel.com/download/ibis/default.aspx.

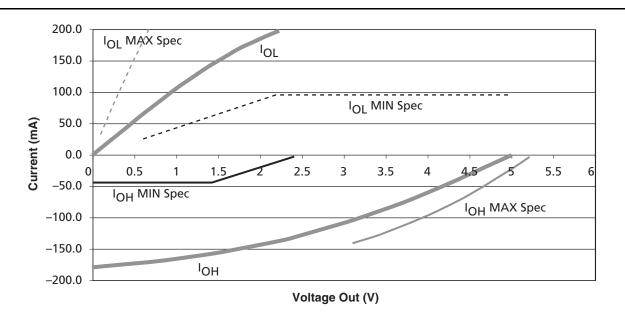

Figure 2-1 shows the 5 V PCI V/I curve and the minimum and maximum PCI drive characteristics of the SX-A family.

## Figure 2-1 • 5 V PCI V/I Curve for SX-A Family

$I_{OH} = 11.9 * (V_{OUT} - 5.25) * (V_{OUT} + 2.45)$ for  $V_{CCI} > V_{OUT} > 3.1V$   $I_{OL} = 78.5 * V_{OUT} * (4.4 - V_{OUT})$ for 0V < V<sub>OUT</sub> < 0.71V

EQ 2-2

#### Table 2-9 • DC Specifications (3.3 V PCI Operation)

| Symbol           | Parameter                          | Condition                   | Min.                | Max.                   | Units |

|------------------|------------------------------------|-----------------------------|---------------------|------------------------|-------|

| V <sub>CCA</sub> | Supply Voltage for Array           |                             | 2.25                | 2.75                   | V     |

| V <sub>CCI</sub> | Supply Voltage for I/Os            |                             | 3.0                 | 3.6                    | V     |

| V <sub>IH</sub>  | Input High Voltage                 |                             | 0.5V <sub>CCI</sub> | V <sub>CCI</sub> + 0.5 | V     |

| V <sub>IL</sub>  | Input Low Voltage                  |                             | -0.5                | 0.3V <sub>CCI</sub>    | V     |

| I <sub>IPU</sub> | Input Pull-up Voltage <sup>1</sup> |                             | 0.7V <sub>CCI</sub> | -                      | V     |

| IIL              | Input Leakage Current <sup>2</sup> | $0 < V_{IN} < V_{CCI}$      | -10                 | +10                    | μΑ    |

| V <sub>OH</sub>  | Output High Voltage                | I <sub>OUT</sub> = -500 μA  | 0.9V <sub>CCI</sub> | -                      | V     |

| V <sub>OL</sub>  | Output Low Voltage                 | I <sub>OUT</sub> = 1,500 μA |                     | 0.1V <sub>CCI</sub>    | V     |

| C <sub>IN</sub>  | Input Pin Capacitance <sup>3</sup> |                             | -                   | 10                     | pF    |

| C <sub>CLK</sub> | CLK Pin Capacitance                |                             | 5                   | 12                     | рF    |

EQ 2-1

Notes:

1. This specification should be guaranteed by design. It is the minimum voltage to which pull-up resistors are calculated to pull a floated network. Designers should ensure that the input buffer is conducting minimum current at this input voltage in applications sensitive to static power utilization.

2. Input leakage currents include hi-Z output leakage for all bidirectional buffers with tristate outputs.

3. Absolute maximum pin capacitance for a PCI input is 10 pF (except for CLK).

| Symbol                | Parameter              | Condition                                                                 | Min.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Max.                                      | Units |

|-----------------------|------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------|

| I <sub>OH(AC)</sub>   | Switching Current High | $0 < V_{OUT} \le 0.3 V_{CCI}$ <sup>1</sup>                                | -12V <sub>CCI</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -                                         | mA    |

|                       |                        | $0.3V_{CCI} \le V_{OUT} < 0.9V_{CCI}$ <sup>1</sup>                        | (–17.1(V <sub>CCI</sub> – V <sub>OUT</sub> ))                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -                                         | mA    |

|                       |                        | 0.7V <sub>CCI</sub> < V <sub>OUT</sub> < V <sub>CCI</sub> <sup>1, 2</sup> | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | EQ 2-3 on<br>page 2-7                     | _     |

|                       | (Test Point)           | $V_{OUT} = 0.7 V_{CC}^2$                                                  | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -32V <sub>CCI</sub>                       | mA    |

| I <sub>OL(AC)</sub>   | Switching Current Low  | $V_{CCI} > V_{OUT} \ge 0.6 V_{CCI}^{1}$                                   | 16V <sub>CCI</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -                                         | mA    |

| I <sub>OL(AC)</sub> S |                        | $0.6V_{CCI} > V_{OUT} > 0.1V_{CCI}^{1}$                                   | (26.7V <sub>OUT</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -                                         | mA    |

|                       |                        | 0.18V <sub>CCI</sub> > V <sub>OUT</sub> > 0 <sup>1, 2</sup>               | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | EQ 2-3 on page 2-7<br>-32V <sub>CCI</sub> | _     |

|                       | (Test Point)           | $V_{OUT} = 0.18 V_{CC}^2$                                                 | $\begin{array}{c c} -12V_{CCI} & - & \\ & - & \\ \hline (-17.1(V_{CCI} - V_{OUT})) & - & \\ \hline & & \\ \hline \hline & & \\ \hline & & \\ \hline & & \\ \hline & & \\ \hline \hline & & \\ \hline \hline & & \\ \hline \hline \\ \hline & & \\ \hline \hline & & \\ \hline \hline \hline \\ \hline \hline \hline \hline \\ \hline \hline \hline \hline \hline \hline \\ \hline \hline$ | mA                                        |       |

| I <sub>CL</sub>       | Low Clamp Current      | $-3 < V_{IN} \le -1$                                                      | –25 + (V <sub>IN</sub> + 1)/0.015                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                                         | mA    |

| I <sub>CH</sub>       | High Clamp Current     | $V_{CCI} + 4 > V_{IN} \ge V_{CCI} + 1$                                    | 25 + (V <sub>IN</sub> – V <sub>CCI</sub> – 1)/0.015                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -                                         | mA    |

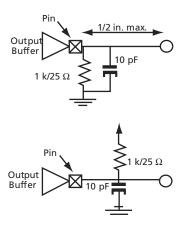

| slew <sub>R</sub>     | Output Rise Slew Rate  | 0.2V <sub>CCI</sub> - 0.6V <sub>CCI</sub> load <sup>3</sup>               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4                                         | V/ns  |

| slew <sub>F</sub>     | Output Fall Slew Rate  | 0.6V <sub>CCI</sub> - 0.2V <sub>CCI</sub> load <sup>3</sup>               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4                                         | V/ns  |

Table 2-10 • AC Specifications (3.3 V PCI Operation)

#### Notes:

1. Refer to the V/I curves in Figure 2-2 on page 2-7. Switching current characteristics for REQ# and GNT# are permitted to be one half of that specified here; i.e., half size output drivers may be used on these signals. This specification does not apply to CLK and RST#, which are system outputs. "Switching Current High" specifications are not relevant to SERR#, INTA#, INTB#, INTC#, and INTD#, which are open drain outputs.

- 2. Maximum current requirements must be met as drivers pull beyond the last step voltage. Equations defining these maximums (C and D) are provided with the respective diagrams in Figure 2-2 on page 2-7. The equation defined maximum should be met by design. In order to facilitate component testing, a maximum current test point is defined for each side of the output driver.

- 3. This parameter is to be interpreted as the cumulative edge rate across the specified range, rather than the instantaneous rate at any point within the transition range. The specified load (diagram below) is optional; i.e., the designer may elect to meet this parameter with an unloaded output per the latest revision of the PCI Local Bus Specification. However, adherence to both maximum and minimum parameters is required (the maximum is no longer simply a guideline). Rise slew rate does not apply to open drain outputs.

## Where:

- C<sub>EQCM</sub> = Equivalent capacitance of combinatorial modules (C-cells) in pF

- C<sub>EQSM</sub> = Equivalent capacitance of sequential modules (R-Cells) in pF

- $C_{EQI}$  = Equivalent capacitance of input buffers in pF

- $C_{EQO}$  = Equivalent capacitance of output buffers in pF

- C<sub>EQCR</sub> = Equivalent capacitance of CLKA/B in pF

- $C_{EQHV}$  = Variable capacitance of HCLK in pF

- $C_{EQHF}$  = Fixed capacitance of HCLK in pF

- C<sub>L =</sub> Output lead capacitance in pF

- $f_m$  = Average logic module switching rate in MHz

- $f_n =$  Average input buffer switching rate in MHz

- $f_p$  = Average output buffer switching rate in MHz

- $f_{a1} =$  Average CLKA rate in MHz

- $f_{\alpha 2}$  = Average CLKB rate in MHz

- $f_{s1}$  = Average HCLK rate in MHz

- m = Number of logic modules switching at fm

- n = Number of input buffers switching at fn

- p = Number of output buffers switching at fp

- q<sub>1</sub> = Number of clock loads on CLKA

- q<sub>2</sub> = Number of clock loads on CLKB

- $r_1 =$  Fixed capacitance due to CLKA

- r<sub>2</sub> = Fixed capacitance due to CLKB

- s1 = Number of clock loads on HCLK

- x = Number of I/Os at logic low

- y = Number of I/Os at logic high

#### Table 2-11 • CEQ Values for SX-A Devices

|                                                           | A54SX08A | A54SX16A | A54SX32A  | A54SX72A  |

|-----------------------------------------------------------|----------|----------|-----------|-----------|

| Combinatorial modules (C <sub>EQCM</sub> )                | 1.70 pF  | 2.00 pF  | 2.00 pF   | 1.80 pF   |

| Sequential modules (C <sub>EQCM</sub> )                   | 1.50 pF  | 1.50 pF  | 1.30 pF   | 1.50 pF   |

| Input buffers (C <sub>EQI</sub> )                         | 1.30 pF  | 1.30 pF  | 1.30 pF   | 1.30 pF   |

| Output buffers (C <sub>EQO</sub> )                        | 7.40 pF  | 7.40 pF  | 7.40 pF   | 7.40 pF   |

| Routed array clocks (C <sub>EQCR</sub> )                  | 1.05 pF  | 1.05 pF  | 1.05 pF   | 1.05 pF   |

| Dedicated array clocks – variable<br>(C <sub>EQHV</sub> ) | 0.85 pF  | 0.85 pF  | 0.85 pF   | 0.85 pF   |

| Dedicated array clocks – fixed (C <sub>EQHF</sub> )       | 30.00 pF | 55.00 pF | 110.00 pF | 240.00 pF |

| Routed array clock A (r <sub>1</sub> )                    | 35.00 pF | 50.00 pF | 90.00 pF  | 310.00 pF |

## Table 2-24 A54SX16A Timing Characteristics

| (Worst-Case Commercial Conditions | V <sub>CCA</sub> = 2.25 V, V <sub>CCI</sub> =4.75 V, T <sub>J</sub> = 70°C) |

|-----------------------------------|-----------------------------------------------------------------------------|

|-----------------------------------|-----------------------------------------------------------------------------|

|                    |                                                         | -3 S | beed* | -2 S | -2 Speed |      | -1 Speed |      | Std. Speed |      | -F Speed |                                              |

|--------------------|---------------------------------------------------------|------|-------|------|----------|------|----------|------|------------|------|----------|----------------------------------------------|

| Parameter          | Description                                             | Min. | Max.  | Min. | Max.     | Min. | Max.     | Min. | Max.       | Min. | Max.     | Units                                        |

| Dedicated          | (Hardwired) Array Clock Netwo                           | rks  |       | 1    |          |      |          |      |            |      |          | <u>.                                    </u> |

| t <sub>HCKH</sub>  | Input Low to High<br>(Pad to R-cell Input)              |      | 1.2   |      | 1.4      |      | 1.6      |      | 1.8        |      | 2.8      | ns                                           |

| t <sub>HCKL</sub>  | Input High to Low<br>(Pad to R-cell Input)              |      | 1.0   |      | 1.1      |      | 1.2      |      | 1.5        |      | 2.2      | ns                                           |

| t <sub>HPWH</sub>  | Minimum Pulse Width High                                | 1.4  |       | 1.7  |          | 1.9  |          | 2.2  |            | 3.0  |          | ns                                           |

| t <sub>HPWL</sub>  | Minimum Pulse Width Low                                 | 1.4  |       | 1.7  |          | 1.9  |          | 2.2  |            | 3.0  |          | ns                                           |

| t <sub>HCKSW</sub> | Maximum Skew                                            |      | 0.3   |      | 0.3      |      | 0.4      |      | 0.4        |      | 0.7      | ns                                           |

| t <sub>HP</sub>    | Minimum Period                                          | 2.8  |       | 3.4  |          | 3.8  |          | 4.4  |            | 6.0  |          | ns                                           |

| f <sub>HMAX</sub>  | Maximum Frequency                                       |      | 357   |      | 294      |      | 263      |      | 227        |      | 167      | MHz                                          |

| <b>Routed Arr</b>  | ay Clock Networks                                       |      |       |      |          |      |          |      |            |      |          |                                              |

| t <sub>RCKH</sub>  | Input Low to High (Light Load)<br>(Pad to R-cell Input) |      | 1.0   |      | 1.2      |      | 1.3      |      | 1.6        |      | 2.2      | ns                                           |

| t <sub>rckl</sub>  | Input High to Low (Light Load)<br>(Pad to R-cell Input) |      | 1.1   |      | 1.3      |      | 1.5      |      | 1.7        |      | 2.4      | ns                                           |

| t <sub>RCKH</sub>  | Input Low to High (50% Load)<br>(Pad to R-cell Input)   |      | 1.1   |      | 1.3      |      | 1.5      |      | 1.7        |      | 2.4      | ns                                           |

| t <sub>RCKL</sub>  | Input High to Low (50% Load)<br>(Pad to R-cell Input)   |      | 1.1   |      | 1.3      |      | 1.5      |      | 1.7        |      | 2.4      | ns                                           |

| t <sub>RCKH</sub>  | Input Low to High (100% Load)<br>(Pad to R-cell Input)  |      | 1.3   |      | 1.5      |      | 1.7      |      | 2.0        |      | 2.8      | ns                                           |

| t <sub>RCKL</sub>  | Input High to Low (100% Load)<br>(Pad to R-cell Input)  |      | 1.3   |      | 1.5      |      | 1.7      |      | 2.0        |      | 2.8      | ns                                           |

| t <sub>RPWH</sub>  | Minimum Pulse Width High                                | 1.4  |       | 1.7  |          | 1.9  |          | 2.2  |            | 3.0  |          | ns                                           |

| t <sub>RPWL</sub>  | Minimum Pulse Width Low                                 | 1.4  |       | 1.7  |          | 1.9  |          | 2.2  |            | 3.0  |          | ns                                           |

| t <sub>RCKSW</sub> | Maximum Skew (Light Load)                               |      | 0.8   |      | 0.9      |      | 1.0      |      | 1.2        |      | 1.7      | ns                                           |

| t <sub>RCKSW</sub> | Maximum Skew (50% Load)                                 |      | 0.8   |      | 0.9      |      | 1.0      |      | 1.2        |      | 1.7      | ns                                           |

| t <sub>RCKSW</sub> | Maximum Skew (100% Load)                                |      | 1.0   |      | 1.1      |      | 1.3      |      | 1.5        |      | 2.1      | ns                                           |

## Table 2-27 A54SX16A Timing Characteristics

| (Worst-Case Commercial Conditions V <sub>CCA</sub> | $x = 2.25 \text{ V}, \text{ V}_{\text{CCI}} = 4.75 \text{ V}, \text{ T}_{\text{J}} = 70^{\circ}\text{C}$ |

|----------------------------------------------------|----------------------------------------------------------------------------------------------------------|

|----------------------------------------------------|----------------------------------------------------------------------------------------------------------|

|                                |                                  | –3 Sj | beed <sup>1</sup> | -2 S | peed  | -1 S | peed  | Std. | Speed –F Speed |      |       |       |

|--------------------------------|----------------------------------|-------|-------------------|------|-------|------|-------|------|----------------|------|-------|-------|

| Parameter                      | Description                      | Min.  | Max.              | Min. | Max.  | Min. | Max.  | Min. | Max.           | Min. | Max.  | Units |

| 5 V PCI Out                    | put Module Timing <sup>2</sup>   |       |                   |      |       |      |       |      |                |      |       |       |

| t <sub>DLH</sub>               | Data-to-Pad Low to High          |       | 2.2               |      | 2.5   |      | 2.8   |      | 3.3            |      | 4.6   | ns    |

| t <sub>DHL</sub>               | Data-to-Pad High to Low          |       | 2.8               |      | 3.2   |      | 3.6   |      | 4.2            |      | 5.9   | ns    |

| t <sub>ENZL</sub>              | Enable-to-Pad, Z to L            |       | 1.3               |      | 1.5   |      | 1.7   |      | 2.0            |      | 2.8   | ns    |

| t <sub>ENZH</sub>              | Enable-to-Pad, Z to H            |       | 2.2               |      | 2.5   |      | 2.8   |      | 3.3            |      | 4.6   | ns    |

| t <sub>ENLZ</sub>              | Enable-to-Pad, L to Z            |       | 3.0               |      | 3.5   |      | 3.9   |      | 4.6            |      | 6.4   | ns    |

| t <sub>ENHZ</sub>              | Enable-to-Pad, H to Z            |       | 2.8               |      | 3.2   |      | 3.6   |      | 4.2            |      | 5.9   | ns    |

| $d_{\text{TLH}}^{3}$           | Delta Low to High                |       | 0.016             |      | 0.016 |      | 0.02  |      | 0.022          |      | 0.032 | ns/pF |

| $d_{THL}^{3}$                  | Delta High to Low                |       | 0.026             |      | 0.03  |      | 0.032 |      | 0.04           |      | 0.052 | ns/pF |

| 5 V TTL Out                    | put Module Timing <sup>4</sup>   |       |                   |      |       |      |       |      |                |      |       |       |

| t <sub>DLH</sub>               | Data-to-Pad Low to High          |       | 2.2               |      | 2.5   |      | 2.8   |      | 3.3            |      | 4.6   | ns    |

| t <sub>DHL</sub>               | Data-to-Pad High to Low          |       | 2.8               |      | 3.2   |      | 3.6   |      | 4.2            |      | 5.9   | ns    |

| t <sub>DHLS</sub>              | Data-to-Pad High to Low—low slew |       | 6.7               |      | 7.7   |      | 8.7   |      | 10.2           |      | 14.3  | ns    |

| t <sub>ENZL</sub>              | Enable-to-Pad, Z to L            |       | 2.1               |      | 2.4   |      | 2.7   |      | 3.2            |      | 4.5   | ns    |

| t <sub>ENZLS</sub>             | Enable-to-Pad, Z to L—low slew   |       | 7.4               |      | 8.4   |      | 9.5   |      | 11.0           |      | 15.4  | ns    |

| t <sub>ENZH</sub>              | Enable-to-Pad, Z to H            |       | 1.9               |      | 2.2   |      | 2.5   |      | 2.9            |      | 4.1   | ns    |

| t <sub>ENLZ</sub>              | Enable-to-Pad, L to Z            |       | 3.6               |      | 4.2   |      | 4.7   |      | 5.6            |      | 7.8   | ns    |

| t <sub>ENHZ</sub>              | Enable-to-Pad, H to Z            |       | 2.5               |      | 2.9   |      | 3.3   |      | 3.9            |      | 5.4   | ns    |

| $d_{TLH}^{3}$                  | Delta Low to High                |       | 0.014             |      | 0.017 |      | 0.017 |      | 0.023          |      | 0.031 | ns/pF |

| d <sub>THL</sub> <sup>3</sup>  | Delta High to Low                |       | 0.023             |      | 0.029 |      | 0.031 |      | 0.037          |      | 0.051 | ns/pF |

| d <sub>THLS</sub> <sup>3</sup> | Delta High to Low—low slew       |       | 0.043             |      | 0.046 |      | 0.057 |      | 0.066          |      | 0.089 | ns/pF |

Notes:

1. All –3 speed grades have been discontinued.

2. Delays based on 50 pF loading.

3. To obtain the slew rate, substitute the appropriate Delta value, load capacitance, and the  $V_{CCI}$  value into the following equation: Slew Rate [V/ns] = (0.1\* $V_{CCI}$  - 0.9\* $V_{CCI}$ / ( $C_{load}$  \*  $d_{T[LH|HL|HLS]}$ ) where  $C_{load}$  is the load capacitance driven by the I/O in pF

$d_{T[LH|HL|HLS]}$  is the worst case delta value from the datasheet in ns/pF.

4. Delays based on 35 pF loading.

## Table 2-29 A54SX32A Timing Characteristics

| (Worst-Case Commercial Condition | <sup>5</sup> V <sub>CCA</sub> = 2.25 V, V <sub>CCI</sub> = 2.25 V, T <sub>J</sub> = 70°C) |

|----------------------------------|-------------------------------------------------------------------------------------------|

|----------------------------------|-------------------------------------------------------------------------------------------|

|                    |                                                         | -3 Sp | beed* | –2 S | peed | -1 S | peed | Std. | Speed | –F S | peed |          |

|--------------------|---------------------------------------------------------|-------|-------|------|------|------|------|------|-------|------|------|----------|

| Parameter          | Description                                             | Min.  | Max.  | Min. | Max. | Min. | Max. | Min. | Max.  | Min. | Max. | Units    |

| Dedicated (        | (Hardwired) Array Clock Netwo                           | rks   |       |      |      |      |      |      |       |      |      | <u>.</u> |

| t <sub>нскн</sub>  | Input Low to High<br>(Pad to R-cell Input)              |       | 1.7   |      | 2.0  |      | 2.2  |      | 2.6   |      | 4.0  | ns       |

| t <sub>HCKL</sub>  | Input High to Low<br>(Pad to R-cell Input)              |       | 1.7   |      | 2.0  |      | 2.2  |      | 2.6   |      | 4.0  | ns       |

| t <sub>HPWH</sub>  | Minimum Pulse Width High                                | 1.4   |       | 1.6  |      | 1.8  |      | 2.1  |       | 2.9  |      | ns       |

| t <sub>HPWL</sub>  | Minimum Pulse Width Low                                 | 1.4   |       | 1.6  |      | 1.8  |      | 2.1  |       | 2.9  |      | ns       |

| t <sub>HCKSW</sub> | Maximum Skew                                            |       | 0.6   |      | 0.6  |      | 0.7  |      | 0.8   |      | 1.3  | ns       |

| t <sub>HP</sub>    | Minimum Period                                          | 2.8   |       | 3.2  |      | 3.6  |      | 4.2  |       | 5.8  |      | ns       |

| f <sub>HMAX</sub>  | Maximum Frequency                                       |       | 357   |      | 313  |      | 278  |      | 238   |      | 172  | MHz      |

| Routed Arra        | ay Clock Networks                                       |       |       |      |      |      |      |      |       |      |      |          |

| t <sub>RCKH</sub>  | Input Low to High (Light Load)<br>(Pad to R-cell Input) |       | 2.2   |      | 2.5  |      | 2.9  |      | 3.4   |      | 4.7  | ns       |

| t <sub>RCKL</sub>  | Input High to Low (Light Load)<br>(Pad to R-cell Input) |       | 2.1   |      | 2.4  |      | 2.7  |      | 3.2   |      | 4.4  | ns       |

| t <sub>RCKH</sub>  | Input Low to High (50% Load)<br>(Pad to R-cell Input)   |       | 2.4   |      | 2.7  |      | 3.1  |      | 3.6   |      | 5.1  | ns       |

| t <sub>RCKL</sub>  | Input High to Low (50% Load)<br>(Pad to R-cell Input)   |       | 2.2   |      | 2.5  |      | 2.8  |      | 3.3   |      | 4.6  | ns       |

| t <sub>RCKH</sub>  | Input Low to High (100% Load)<br>(Pad to R-cell Input)  |       | 2.5   |      | 2.9  |      | 3.2  |      | 3.8   |      | 5.3  | ns       |

| t <sub>RCKL</sub>  | Input High to Low (100% Load)<br>(Pad to R-cell Input)  |       | 2.4   |      | 2.7  |      | 3.1  |      | 3.6   |      | 5.0  | ns       |

| t <sub>RPWH</sub>  | Minimum Pulse Width High                                | 1.4   |       | 1.6  |      | 1.8  |      | 2.1  |       | 2.9  |      | ns       |

| t <sub>RPWL</sub>  | Minimum Pulse Width Low                                 | 1.4   |       | 1.6  |      | 1.8  |      | 2.1  |       | 2.9  |      | ns       |

| t <sub>RCKSW</sub> | Maximum Skew (Light Load)                               |       | 1.0   |      | 1.1  |      | 1.3  |      | 1.5   |      | 2.1  | ns       |

| t <sub>RCKSW</sub> | Maximum Skew (50% Load)                                 |       | 0.9   |      | 1.0  |      | 1.2  |      | 1.4   |      | 1.9  | ns       |