Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                           |

|--------------------------------|---------------------------------------------------------------------------|

| Product Status                 | Active                                                                    |

| Number of LABs/CLBs            | 6036                                                                      |

| Number of Logic Elements/Cells | -                                                                         |

| Total RAM Bits                 | -                                                                         |

| Number of I/O                  | 203                                                                       |

| Number of Gates                | 108000                                                                    |

| Voltage - Supply               | 2.25V ~ 5.25V                                                             |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | 0°C ~ 70°C (TA)                                                           |

| Package / Case                 | 256-BFCQFP with Tie Bar                                                   |

| Supplier Device Package        | 256-CQFP (75x75)                                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a54sx72a-1cq256 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Temperature Grade Offering**

| Package | A54SX08A | A54SX16A | A54SX32A | A54SX72A |

|---------|----------|----------|----------|----------|

| PQ208   | C,I,A,M  | C,I,A,M  | C,I,A,M  | C,I,A,M  |

| TQ100   | C,I,A,M  | C,I,A,M  | C,I,A,M  |          |

| TQ144   | C,I,A,M  | C,I,A,M  | C,I,A,M  |          |

| TQ176   |          |          | C,I,M    |          |

| BG329   |          |          | C,I,M    |          |

| FG144   | C,I,A,M  | C,I,A,M  | C,I,A,M  |          |

| FG256   |          | C,I,A,M  | C,I,A,M  | C,I,A,M  |

| FG484   |          |          | C,I,M    | C,I,A,M  |

| CQ208   |          |          | C,M,B    | C,M,B    |

| CQ256   |          |          | C,M,B    | C,M,B    |

#### Notes:

- 1. C = Commercial

- 2. I = Industrial

- 3. A = Automotive

- 4. M = Military

- 5. B = MIL-STD-883 Class B

- 6. For more information regarding automotive products, refer to the SX-A Automotive Family FPGAs datasheet.

- 7. For more information regarding Mil-Temp and ceramic packages, refer to the HiRel SX-A Family FPGAs datasheet.

## **Speed Grade and Temperature Grade Matrix**

|              | F | Std | -1 | -2 | -3           |

|--------------|---|-----|----|----|--------------|

| Commercial   | ✓ | ✓   | ✓  | 1  | Discontinued |

| Industrial   |   | ✓   | ✓  | 1  | Discontinued |

| Automotive   |   | ✓   |    |    |              |

| Military     |   | ✓   | ✓  |    |              |

| MIL-STD-883B |   | ✓   | ✓  |    |              |

#### Notes:

- 1. For more information regarding automotive products, refer to the SX-A Automotive Family FPGAs datasheet.

- 2. For more information regarding Mil-Temp and ceramic packages, refer to the HiRel SX-A Family FPGAs datasheet.

Contact your Actel Sales representative for more information on availability.

v5.3

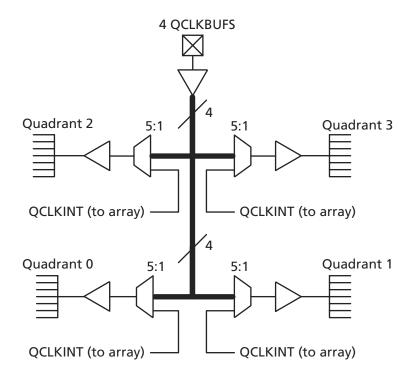

Figure 1-9 • SX-A QCLK Architecture

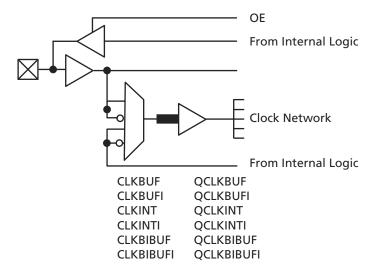

Figure 1-10 • A54SX72A Routed Clock and QCLK Buffer

1-6 v5.3

## Other Architectural Features

## **Technology**

The Actel SX-A family is implemented on a high-voltage, twin-well CMOS process using 0.22  $\mu$ / 0.25  $\mu$  design rules. The metal-to-metal antifuse is comprised of a combination of amorphous silicon and dielectric material with barrier metals and has a programmed ('on' state) resistance of 25  $\Omega$  with capacitance of 1.0 fF for low signal impedance.

#### **Performance**

The unique architectural features of the SX-A family enable the devices to operate with internal clock frequencies of 350 MHz, causing very fast execution of even complex logic functions. The SX-A family is an optimal platform upon which to integrate the functionality previously contained in multiple complex programmable logic devices (CPLDs). In addition, designs that previously would have required a gate array to meet performance goals can be integrated into an SX-A device with dramatic improvements in cost and time-to-market. Using timing-driven place-and-route tools, designers can achieve highly deterministic device performance.

## **User Security**

Reverse engineering is virtually impossible in SX-A devices because it is extremely difficult to distinguish between programmed and unprogrammed antifuses. In addition, since SX-A is a nonvolatile, single-chip solution, there is no configuration bitstream to intercept at device power-up.

The Actel FuseLock advantage ensures that unauthorized users will not be able to read back the contents of an Actel antifuse FPGA. In addition to the inherent strengths of the architecture, special security fuses that prevent internal probing and overwriting are hidden throughout the fabric of the device. They are located where they cannot be accessed or bypassed without destroying access to the rest of the device, making both invasive and more-subtle noninvasive attacks ineffective against Actel antifuse FPGAs.

Look for this symbol to ensure your valuable IP is secure (Figure 1-11).

Figure 1-11 • FuseLock

For more information, refer to Actel's *Implementation of Security in Actel Antifuse FPGAs* application note.

#### **I/O Modules**

For a simplified I/O schematic, refer to Figure 1 in the application note, Actel eX, SX-A, and RTSX-S I/Os.

Each user I/O on an SX-A device can be configured as an input, an output, a tristate output, or a bidirectional pin. Mixed I/O standards can be set for individual pins, though this is only allowed with the same voltage as the input. These I/Os, combined with array registers, can achieve clock-to-output-pad timing as fast as 3.8 ns, even without the dedicated I/O registers. In most FPGAs, I/O cells that have embedded latches and flip-flops, requiring instantiation in HDL code; this is a design complication not encountered in SX-A FPGAs. Fast pinto-pin timing ensures that the device is able to interface with any other device in the system, which in turn enables parallel design of system components and reduces overall design time. All unused I/Os are configured as tristate outputs by the Actel Designer software, for maximum flexibility when designing new boards or migrating existing designs.

SX-A I/Os should be driven by high-speed push-pull devices with a low-resistance pull-up device when being configured as tristate output buffers. If the I/O is driven by a voltage level greater than V<sub>CCI</sub> and a fast push-pull device is NOT used, the high-resistance pull-up of the driver and the internal circuitry of the SX-A I/O may create a voltage divider. This voltage divider could pull the input voltage below specification for some devices connected to the driver. A logic '1' may not be correctly presented in this case. For example, if an open drain driver is used with a pull-up resistor to 5 V to provide the logic '1' input, and V<sub>CCI</sub> is set to 3.3 V on the SX-A device, the input signal may be pulled down by the SX-A input. Each I/O module has an available power-up resistor of

approximately 50 k $\Omega$  that can configure the I/O in a known state during power-up. For nominal pull-up and pull-down resistor values, refer to Table 1-4 on page 1-8 of the application note *Actel eX, SX-A, and RTSX-S I/Os*. Just slightly before V<sub>CCA</sub> reaches 2.5 V, the resistors are disabled, so the I/Os will be controlled by user logic. See Table 1-2 on page 1-8 and Table 1-3 on page 1-8 for more information concerning available I/O features.

v5.3 1-7

To determine the heat sink's thermal performance, use the following equation:

$$\theta_{JA(TOTAL)} = \theta_{JC} + \theta_{CS} + \theta_{SA}$$

EQ 2-14

where:

$\theta_{CS} = 0.37^{\circ}\text{C/W}$

= thermal resistance of the interface material between the case and the heat sink, usually provided by the thermal interface manufacturer

$\theta_{SA}$  = thermal resistance of the heat sink in °C/W

$$\theta_{SA} = \theta_{JA(TOTAL)} - \theta_{JC} - \theta_{CS}$$

EQ 2-15

$$\theta_{SA} = 13.33^{\circ}\text{C/W} - 3.20^{\circ}\text{C/W} - 0.37^{\circ}\text{C/W}$$

$$\theta_{SA} = 9.76$$

°C/W

A heat sink with a thermal resistance of 9.76°C/W or better should be used. Thermal resistance of heat sinks is a function of airflow. The heat sink performance can be significantly improved with the presence of airflow.

Carefully estimating thermal resistance is important in the long-term reliability of an Actel FPGA. Design engineers should always correlate the power consumption of the device with the maximum allowable power dissipation of the package selected for that device, using the provided thermal resistance data.

Note: The values may vary depending on the application.

v5.3 2-13

Table 2-18 • A54SX08A Timing Characteristics

(Worst-Case Commercial Conditions V<sub>CCA</sub> = 2.25 V, V<sub>CCI</sub> = 2.3 V, T<sub>J</sub> = 70°C)

|                                |                                       | -2 S | peed  | -1 S | peed  | Std. | Speed | −F S | peed  |       |

|--------------------------------|---------------------------------------|------|-------|------|-------|------|-------|------|-------|-------|

| Parameter                      | Description                           | Min. | Max.  | Min. | Max.  | Min. | Max.  | Min. | Max.  | Units |

| 2.5 V LVCMO                    | S Output Module Timing <sup>1,2</sup> | •    |       |      |       |      |       |      |       |       |

| t <sub>DLH</sub>               | Data-to-Pad Low to High               |      | 3.9   |      | 4.4   |      | 5.2   |      | 7.2   | ns    |

| t <sub>DHL</sub>               | Data-to-Pad High to Low               |      | 3.0   |      | 3.4   |      | 3.9   |      | 5.5   | ns    |

| t <sub>DHLS</sub>              | Data-to-Pad High to Low—low slew      |      | 13.3  |      | 15.1  |      | 17.7  |      | 24.8  | ns    |

| t <sub>ENZL</sub>              | Enable-to-Pad, Z to L                 |      | 2.8   |      | 3.2   |      | 3.7   |      | 5.2   | ns    |

| t <sub>ENZLS</sub>             | Data-to-Pad, Z to L—low slew          |      | 13.7  |      | 15.5  |      | 18.2  |      | 25.5  | ns    |

| t <sub>ENZH</sub>              | Enable-to-Pad, Z to H                 |      | 3.9   |      | 4.4   |      | 5.2   |      | 7.2   | ns    |

| t <sub>ENLZ</sub>              | Enable-to-Pad, L to Z                 |      | 2.5   |      | 2.8   |      | 3.3   |      | 4.7   | ns    |

| t <sub>ENHZ</sub>              | Enable-to-Pad, H to Z                 |      | 3.0   |      | 3.4   |      | 3.9   |      | 5.5   | ns    |

| $d_{TLH}^3$                    | Delta Low to High                     |      | 0.037 |      | 0.043 |      | 0.051 |      | 0.071 | ns/pF |

| d <sub>THL</sub> <sup>3</sup>  | Delta High to Low                     |      | 0.017 |      | 0.023 |      | 0.023 |      | 0.037 | ns/pF |

| d <sub>THLS</sub> <sup>3</sup> | Delta High to Low—low slew            |      | 0.06  |      | 0.071 |      | 0.086 |      | 0.117 | ns/pF |

#### Note:

- 1. Delays based on 35 pF loading.

- 2. The equivalent I/O Attribute Editor settings for 2.5 V LVCMOS is 2.5 V LVTTL in the software.

- 3. To obtain the slew rate, substitute the appropriate Delta value, load capacitance, and the  $V_{CCI}$  value into the following equation: Slew Rate [V/ns] =  $(0.1*V_{CCI} 0.9*V_{CCI})/(C_{load}*d_{T[LH|HL|HLS]})$  where  $C_{load}$  is the load capacitance driven by the I/O in pF

$d_{T[LH|HL|HLS]}$  is the worst case delta value from the datasheet in ns/pF.

v5.3 2-23

*Table 2-20* • **A54SX08A Timing Characteristics** (Worst-Case Commercial Conditions  $V_{CCA} = 2.25 \text{ V}$ ,  $V_{CCI} = 4.75 \text{ V}$ ,  $T_J = 70^{\circ}\text{C}$ )

|                               |                                  | -2 S | peed  | -1 S | peed  | Std. S | Speed | −F S | peed  |       |

|-------------------------------|----------------------------------|------|-------|------|-------|--------|-------|------|-------|-------|

| Parameter                     | Description                      | Min. | Мах.  | Min. | Мах.  | Min.   | Max.  | Min. | Мах.  | Units |

| 5 V PCI Outp                  | ut Module Timing <sup>1</sup>    |      |       |      |       |        |       |      |       | •     |

| t <sub>DLH</sub>              | Data-to-Pad Low to High          |      | 2.4   |      | 2.8   |        | 3.2   |      | 4.5   | ns    |

| t <sub>DHL</sub>              | Data-to-Pad High to Low          |      | 3.2   |      | 3.6   |        | 4.2   |      | 5.9   | ns    |

| t <sub>ENZL</sub>             | Enable-to-Pad, Z to L            |      | 1.5   |      | 1.7   |        | 2.0   |      | 2.8   | ns    |

| t <sub>ENZH</sub>             | Enable-to-Pad, Z to H            |      | 2.4   |      | 2.8   |        | 3.2   |      | 4.5   | ns    |

| t <sub>ENLZ</sub>             | Enable-to-Pad, L to Z            |      | 3.5   |      | 3.9   |        | 4.6   |      | 6.4   | ns    |

| t <sub>ENHZ</sub>             | Enable-to-Pad, H to Z            |      | 3.2   |      | 3.6   |        | 4.2   |      | 5.9   | ns    |

| $d_{TLH}^2$                   | Delta Low to High                |      | 0.016 |      | 0.02  |        | 0.022 |      | 0.032 | ns/pF |

| d <sub>THL</sub> <sup>2</sup> | Delta High to Low                |      | 0.03  |      | 0.032 |        | 0.04  |      | 0.052 | ns/pF |

| 5 V TTL Outp                  | out Module Timing <sup>3</sup>   |      |       |      |       |        |       |      |       |       |

| t <sub>DLH</sub>              | Data-to-Pad Low to High          |      | 2.4   |      | 2.8   |        | 3.2   |      | 4.5   | ns    |

| t <sub>DHL</sub>              | Data-to-Pad High to Low          |      | 3.2   |      | 3.6   |        | 4.2   |      | 5.9   | ns    |

| t <sub>DHLS</sub>             | Data-to-Pad High to Low—low slew |      | 7.6   |      | 8.6   |        | 10.1  |      | 14.2  | ns    |

| t <sub>ENZL</sub>             | Enable-to-Pad, Z to L            |      | 2.4   |      | 2.7   |        | 3.2   |      | 4.5   | ns    |

| t <sub>ENZLS</sub>            | Enable-to-Pad, Z to L—low slew   |      | 8.4   |      | 9.5   |        | 11.0  |      | 15.4  | ns    |

| t <sub>ENZH</sub>             | Enable-to-Pad, Z to H            |      | 2.4   |      | 2.8   |        | 3.2   |      | 4.5   | ns    |

| t <sub>ENLZ</sub>             | Enable-to-Pad, L to Z            |      | 4.2   |      | 4.7   |        | 5.6   |      | 7.8   | ns    |

| t <sub>ENHZ</sub>             | Enable-to-Pad, H to Z            |      | 3.2   |      | 3.6   |        | 4.2   |      | 5.9   | ns    |

| $d_{TLH}$                     | Delta Low to High                |      | 0.017 |      | 0.017 |        | 0.023 |      | 0.031 | ns/pF |

| d <sub>THL</sub>              | Delta High to Low                |      | 0.029 |      | 0.031 |        | 0.037 |      | 0.051 | ns/pF |

| d <sub>THLS</sub>             | Delta High to Low—low slew       |      | 0.046 |      | 0.057 |        | 0.066 |      | 0.089 | ns/pF |

#### Notes:

- 1. Delays based on 50 pF loading.

- 2. To obtain the slew rate, substitute the appropriate Delta value, load capacitance, and the  $V_{CCI}$  value into the following equation: Slew Rate [V/ns] = (0.1 \* $V_{CCI}$  – 0.9 \* $V_{CCI}$ / ( $C_{load}$  \*  $d_{T[LH|HL|HLS]}$ ) where C<sub>load</sub> is the load capacitance driven by the I/O in pF

- $d_{T[LH|HL|HLS]}$  is the worst case delta value from the datasheet in ns/pF.

- 3. Delays based on 35 pF loading.

v5.3 2-25

Table 2-21 • A54SX16A Timing Characteristics (Continued) (Worst-Case Commercial Conditions, V<sub>CCA</sub> = 2.25 V, V<sub>CCI</sub> = 3.0 V, T<sub>J</sub> = 70°C)

|                    |                                                   | -3 Sp | oeed <sup>1</sup> | -2 S | peed | -1 S <sub> </sub> | peed | Std. 9 | peed | −F S <sub>I</sub> | peed |       |

|--------------------|---------------------------------------------------|-------|-------------------|------|------|-------------------|------|--------|------|-------------------|------|-------|

| Parameter          | Description                                       | Min.  | Max.              | Min. | Max. | Min.              | Max. | Min.   | Max. | Min.              | Max. | Units |

| t <sub>INYH</sub>  | Input Data Pad to Y High 5 V PCI                  |       | 0.5               |      | 0.5  |                   | 0.6  |        | 0.7  |                   | 0.9  | ns    |

| t <sub>INYL</sub>  | Input Data Pad to Y Low 5 V PCI                   |       | 0.7               |      | 0.8  |                   | 0.9  |        | 1.1  |                   | 1.5  | ns    |

| t <sub>INYH</sub>  | Input Data Pad to Y High 5 V TTL                  |       | 0.5               |      | 0.5  |                   | 0.6  |        | 0.7  |                   | 0.9  | ns    |

| t <sub>INYL</sub>  | Input Data Pad to Y Low 5 V TTL                   |       | 0.7               |      | 0.8  |                   | 0.9  |        | 1.1  |                   | 1.5  | ns    |

| Input Modu         | nput Module Predicted Routing Delays <sup>2</sup> |       |                   |      |      |                   |      |        |      |                   |      |       |

| t <sub>IRD1</sub>  | FO = 1 Routing Delay                              |       | 0.3               |      | 0.3  |                   | 0.3  |        | 0.4  |                   | 0.6  | ns    |

| t <sub>IRD2</sub>  | FO = 2 Routing Delay                              |       | 0.4               |      | 0.5  |                   | 0.5  |        | 0.6  |                   | 0.8  | ns    |

| t <sub>IRD3</sub>  | FO = 3 Routing Delay                              |       | 0.5               |      | 0.6  |                   | 0.7  |        | 8.0  |                   | 1.1  | ns    |

| t <sub>IRD4</sub>  | FO = 4 Routing Delay                              |       | 0.7               |      | 0.8  |                   | 0.9  |        | 1.0  |                   | 1.4  | ns    |

| t <sub>IRD8</sub>  | FO = 8 Routing Delay                              |       | 1.2               |      | 1.4  |                   | 1.5  |        | 0.8  |                   | 2.5  | ns    |

| t <sub>IRD12</sub> | FO = 12 Routing Delay                             |       | 1.7               |      | 2.0  |                   | 2.2  |        | 2.6  |                   | 3.6  | ns    |

#### Notes:

- 1. All –3 speed grades have been discontinued.

- 2. For dual-module macros, use  $t_{PD}$  +  $t_{RD1}$  +  $t_{PDn}$ ,  $t_{RCO}$  +  $t_{RD1}$  +  $t_{PDn}$ , or  $t_{PD1}$  +  $t_{RD1}$  +  $t_{SUD}$ , whichever is appropriate.

- 3. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual performance.

v5.3 2-27

Table 2-31 • A54SX32A Timing Characteristics (Worst-Case Commercial Conditions V<sub>CCA</sub> = 2.25 V, V<sub>CCI</sub> = 4.75 V, T<sub>J</sub> = 70°C)

|                    |                                                         | -3 Sp | eed* | -2 S | peed | -1 S | peed | Std. | Speed | −F S | peed |       |

|--------------------|---------------------------------------------------------|-------|------|------|------|------|------|------|-------|------|------|-------|

| Parameter          | Description                                             | Min.  | Мах. | Min. | Max. | Min. | Мах. | Min. | Мах.  | Min. | Мах. | Units |

| Dedicated (        | Dedicated (Hardwired) Array Clock Networks              |       |      |      |      |      |      |      |       |      |      |       |

| t <sub>HCKH</sub>  | Input Low to High<br>(Pad to R-cell Input)              |       | 1.7  |      | 1.9  |      | 2.2  |      | 2.6   |      | 4.0  | ns    |

| t <sub>HCKL</sub>  | Input High to Low<br>(Pad to R-cell Input)              |       | 1.7  |      | 2.0  |      | 2.2  |      | 2.6   |      | 4.0  | ns    |

| t <sub>HPWH</sub>  | Minimum Pulse Width High                                | 1.4   |      | 1.6  |      | 1.8  |      | 2.1  |       | 2.9  |      | ns    |

| t <sub>HPWL</sub>  | Minimum Pulse Width Low                                 | 1.4   |      | 1.6  |      | 1.8  |      | 2.1  |       | 2.9  |      | ns    |

| t <sub>HCKSW</sub> | Maximum Skew                                            |       | 0.6  |      | 0.6  |      | 0.7  |      | 8.0   |      | 1.3  | ns    |

| t <sub>HP</sub>    | Minimum Period                                          | 2.8   |      | 3.2  |      | 3.6  |      | 4.2  |       | 5.8  |      | ns    |

| f <sub>HMAX</sub>  | Maximum Frequency                                       |       | 357  |      | 313  |      | 278  |      | 238   |      | 172  | MHz   |

| Routed Arr         | ay Clock Networks                                       |       |      |      |      |      |      |      |       |      |      |       |

| t <sub>RCKH</sub>  | Input Low to High (Light Load)<br>(Pad to R-cell Input) |       | 2.2  |      | 2.5  |      | 2.8  |      | 3.3   |      | 4.7  | ns    |

| t <sub>RCKL</sub>  | Input High to Low (Light Load)<br>(Pad to R-cell Input) |       | 2.1  |      | 2.5  |      | 2.8  |      | 3.3   |      | 4.5  | ns    |

| t <sub>RCKH</sub>  | Input Low to High (50% Load)<br>(Pad to R-cell Input)   |       | 2.4  |      | 2.7  |      | 3.1  |      | 3.6   |      | 5.1  | ns    |

| t <sub>RCKL</sub>  | Input High to Low (50% Load)<br>(Pad to R-cell Input)   |       | 2.2  |      | 2.6  |      | 2.9  |      | 3.4   |      | 4.7  | ns    |

| t <sub>RCKH</sub>  | Input Low to High (100% Load)<br>(Pad to R-cell Input)  |       | 2.5  |      | 2.8  |      | 3.2  |      | 3.8   |      | 5.3  | ns    |

| t <sub>RCKL</sub>  | Input High to Low (100% Load)<br>(Pad to R-cell Input)  |       | 2.4  |      | 2.8  |      | 3.1  |      | 3.7   |      | 5.2  | ns    |

| t <sub>RPWH</sub>  | Minimum Pulse Width High                                | 1.4   |      | 1.6  |      | 1.8  |      | 2.1  |       | 2.9  |      | ns    |

| t <sub>RPWL</sub>  | Minimum Pulse Width Low                                 | 1.4   |      | 1.6  |      | 1.8  |      | 2.1  |       | 2.9  |      | ns    |

| t <sub>RCKSW</sub> | Maximum Skew (Light Load)                               |       | 1.0  |      | 1.1  |      | 1.3  |      | 1.5   |      | 2.1  | ns    |

| t <sub>RCKSW</sub> | Maximum Skew (50% Load)                                 |       | 1.0  |      | 1.1  |      | 1.3  |      | 1.5   |      | 2.1  | ns    |

| t <sub>RCKSW</sub> | Maximum Skew (100% Load)                                |       | 1.0  |      | 1.1  |      | 1.3  |      | 1.5   |      | 2.1  | ns    |

**Note:** \*All –3 speed grades have been discontinued.

2-38 v5.3

Table 2-33 • A54SX32A Timing Characteristics (Worst-Case Commercial Conditions V<sub>CCA</sub> = 2.25 V, V<sub>CCI</sub> = 3.0 V, T<sub>J</sub> = 70°C)

|                                |                                             | -3 Sp | eed <sup>1</sup> | -2 S | peed  | -1 S | peed  | Std. S | Speed | −F S | peed  |       |

|--------------------------------|---------------------------------------------|-------|------------------|------|-------|------|-------|--------|-------|------|-------|-------|

| Parameter                      | Description                                 | Min.  | Max.             | Min. | Max.  | Min. | Max.  | Min.   | Мах.  | Min. | Мах.  | Units |

| 3.3 V PCI O                    | 3.3 V PCI Output Module Timing <sup>2</sup> |       |                  |      |       |      |       |        |       |      |       |       |

| t <sub>DLH</sub>               | Data-to-Pad Low to High                     |       | 1.9              |      | 2.2   |      | 2.4   |        | 2.9   |      | 4.0   | ns    |

| t <sub>DHL</sub>               | Data-to-Pad High to Low                     |       | 2.0              |      | 2.3   |      | 2.6   |        | 3.1   |      | 4.3   | ns    |

| t <sub>ENZL</sub>              | Enable-to-Pad, Z to L                       |       | 1.4              |      | 1.7   |      | 1.9   |        | 2.2   |      | 3.1   | ns    |

| t <sub>ENZH</sub>              | Enable-to-Pad, Z to H                       |       | 1.9              |      | 2.2   |      | 2.4   |        | 2.9   |      | 4.0   | ns    |

| t <sub>ENLZ</sub>              | Enable-to-Pad, L to Z                       |       | 2.5              |      | 2.8   |      | 3.2   |        | 3.8   |      | 5.3   | ns    |

| t <sub>ENHZ</sub>              | Enable-to-Pad, H to Z                       |       | 2.0              |      | 2.3   |      | 2.6   |        | 3.1   |      | 4.3   | ns    |

| $d_{TLH}^3$                    | Delta Low to High                           |       | 0.025            |      | 0.03  |      | 0.03  |        | 0.04  |      | 0.045 | ns/pF |

| d <sub>THL</sub> <sup>3</sup>  | Delta High to Low                           |       | 0.015            |      | 0.015 |      | 0.015 |        | 0.015 |      | 0.025 | ns/pF |

| 3.3 V LVTTL                    | Output Module Timing <sup>4</sup>           |       |                  |      |       |      |       |        |       |      |       |       |

| t <sub>DLH</sub>               | Data-to-Pad Low to High                     |       | 2.6              |      | 3.0   |      | 3.4   |        | 4.0   |      | 5.6   | ns    |

| t <sub>DHL</sub>               | Data-to-Pad High to Low                     |       | 2.6              |      | 3.0   |      | 3.3   |        | 3.9   |      | 5.5   | ns    |

| t <sub>DHLS</sub>              | Data-to-Pad High to Low—low slew            |       | 9.0              |      | 10.4  |      | 11.8  |        | 13.8  |      | 19.3  | ns    |

| t <sub>ENZL</sub>              | Enable-to-Pad, Z to L                       |       | 2.2              |      | 2.6   |      | 2.9   |        | 3.4   |      | 4.8   | ns    |

| t <sub>ENZLS</sub>             | Enable-to-Pad, Z to L—low slew              |       | 15.8             |      | 18.9  |      | 21.3  |        | 25.4  |      | 34.9  | ns    |

| t <sub>ENZH</sub>              | Enable-to-Pad, Z to H                       |       | 2.6              |      | 3.0   |      | 3.4   |        | 4.0   |      | 5.6   | ns    |

| t <sub>ENLZ</sub>              | Enable-to-Pad, L to Z                       |       | 2.9              |      | 3.3   |      | 3.7   |        | 4.4   |      | 6.2   | ns    |

| t <sub>ENHZ</sub>              | Enable-to-Pad, H to Z                       |       | 2.6              |      | 3.0   |      | 3.3   |        | 3.9   |      | 5.5   | ns    |

| $d_{TLH}^3$                    | Delta Low to High                           |       | 0.025            |      | 0.03  |      | 0.03  |        | 0.04  |      | 0.045 | ns/pF |

| $d_{THL}^3$                    | Delta High to Low                           |       | 0.015            |      | 0.015 |      | 0.015 |        | 0.015 |      | 0.025 | ns/pF |

| d <sub>THLS</sub> <sup>3</sup> | Delta High to Low—low slew                  |       | 0.053            |      | 0.053 |      | 0.067 |        | 0.073 |      | 0.107 | ns/pF |

#### Notes:

- 1. All –3 speed grades have been discontinued.

- 2. Delays based on 10 pF loading and 25  $\Omega$  resistance.

- 3. To obtain the slew rate, substitute the appropriate Delta value, load capacitance, and the  $V_{CCI}$  value into the following equation: Slew Rate [V/ns] =  $(0.1*V_{CCI} 0.9*V_{CCI})'$  ( $C_{load} * d_{T[LH|HL]HLS}$ ) where  $C_{load}$  is the load capacitance driven by the I/O in pF

$d_{T[LH|HL|HLS]}$  is the worst case delta value from the datasheet in ns/pF.

4. Delays based on 35 pF loading.

2-40 v5.3

Table 2-34 • A54SX32A Timing Characteristics (Worst-Case Commercial Conditions V<sub>CCA</sub> = 2.25 V, V<sub>CCI</sub> = 4.75 V, T<sub>J</sub> = 70°C)

|                                |                                           | -3 Sp | eed <sup>1</sup> | -2 S | peed  | -1 S | peed  | Std. 9 | Speed | −F S | peed  |       |

|--------------------------------|-------------------------------------------|-------|------------------|------|-------|------|-------|--------|-------|------|-------|-------|

| Parameter                      | Description                               | Min.  | Max.             | Min. | Max.  | Min. | Max.  | Min.   | Max.  | Min. | Max.  | Units |

| 5 V PCI Out                    | 5 V PCI Output Module Timing <sup>2</sup> |       |                  |      |       |      |       |        |       |      |       |       |

| t <sub>DLH</sub>               | Data-to-Pad Low to High                   |       | 2.1              |      | 2.4   |      | 2.8   |        | 3.2   |      | 4.5   | ns    |

| t <sub>DHL</sub>               | Data-to-Pad High to Low                   |       | 2.8              |      | 3.2   |      | 3.6   |        | 4.2   |      | 5.9   | ns    |

| t <sub>ENZL</sub>              | Enable-to-Pad, Z to L                     |       | 1.3              |      | 1.5   |      | 1.7   |        | 2.0   |      | 2.8   | ns    |

| t <sub>ENZH</sub>              | Enable-to-Pad, Z to H                     |       | 2.1              |      | 2.4   |      | 2.8   |        | 3.2   |      | 4.5   | ns    |

| t <sub>ENLZ</sub>              | Enable-to-Pad, L to Z                     |       | 3.0              |      | 3.5   |      | 3.9   |        | 4.6   |      | 6.4   | ns    |

| t <sub>ENHZ</sub>              | Enable-to-Pad, H to Z                     |       | 2.8              |      | 3.2   |      | 3.6   |        | 4.2   |      | 5.9   | ns    |

| $d_{TLH}^3$                    | Delta Low to High                         |       | 0.016            |      | 0.016 |      | 0.02  |        | 0.022 |      | 0.032 | ns/pF |

| $d_{THL}^3$                    | Delta High to Low                         |       | 0.026            |      | 0.03  |      | 0.032 |        | 0.04  |      | 0.052 | ns/pF |

| 5 V TTL Out                    | put Module Timing <sup>4</sup>            |       |                  |      |       |      |       |        |       |      |       |       |

| t <sub>DLH</sub>               | Data-to-Pad Low to High                   |       | 1.9              |      | 2.2   |      | 2.5   |        | 2.9   |      | 4.1   | ns    |

| t <sub>DHL</sub>               | Data-to-Pad High to Low                   |       | 2.5              |      | 2.9   |      | 3.3   |        | 3.9   |      | 5.4   | ns    |

| t <sub>DHLS</sub>              | Data-to-Pad High to Low—low slew          |       | 6.6              |      | 7.6   |      | 8.6   |        | 10.1  |      | 14.2  | ns    |

| t <sub>ENZL</sub>              | Enable-to-Pad, Z to L                     |       | 2.1              |      | 2.4   |      | 2.7   |        | 3.2   |      | 4.5   | ns    |

| t <sub>ENZLS</sub>             | Enable-to-Pad, Z to L—low slew            |       | 7.4              |      | 8.4   |      | 9.5   |        | 11.0  |      | 15.4  | ns    |

| t <sub>ENZH</sub>              | Enable-to-Pad, Z to H                     |       | 1.9              |      | 2.2   |      | 2.5   |        | 2.9   |      | 4.1   | ns    |

| t <sub>ENLZ</sub>              | Enable-to-Pad, L to Z                     |       | 3.6              |      | 4.2   |      | 4.7   |        | 5.6   |      | 7.8   | ns    |

| t <sub>ENHZ</sub>              | Enable-to-Pad, H to Z                     |       | 2.5              |      | 2.9   |      | 3.3   |        | 3.9   |      | 5.4   | ns    |

| $d_{TLH}^3$                    | Delta Low to High                         |       | 0.014            |      | 0.017 |      | 0.017 |        | 0.023 |      | 0.031 | ns/pF |

| $d_{THL}^3$                    | Delta High to Low                         |       | 0.023            |      | 0.029 |      | 0.031 |        | 0.037 |      | 0.051 | ns/pF |

| d <sub>THLS</sub> <sup>3</sup> | Delta High to Low—low slew                |       | 0.043            |      | 0.046 |      | 0.057 |        | 0.066 |      | 0.089 | ns/pF |

#### Notes:

- 1. All –3 speed grades have been discontinued.

- 2. Delays based on 50 pF loading.

- 3. To obtain the slew rate, substitute the appropriate Delta value, load capacitance, and the  $V_{CCI}$  value into the following equation: Slew Rate [V/ns] =  $(0.1*V_{CCI} 0.9*V_{CCI})'$  ( $C_{load} * d_{T[LH|HL]HLS}$ ) where  $C_{load}$  is the load capacitance driven by the I/O in pF

$d_{T[LH|HL|HLS]}$  is the worst case delta value from the datasheet in ns/pF.

4. Delays based on 35 pF loading.

v5.3 2-41

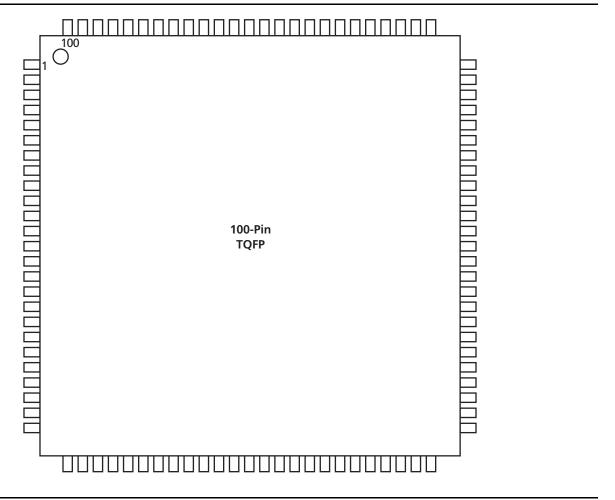

## 100-Pin TQFP

Figure 3-2 • 100-Pin TQFP

### Note

For Package Manufacturing and Environmental information, visit Resource center at http://www.actel.com/products/rescenter/package/index.html.

| 100-TQFP   |                      |                      |                      |  |  |  |  |

|------------|----------------------|----------------------|----------------------|--|--|--|--|

| Pin Number | A54SX08A<br>Function | A54SX16A<br>Function | A54SX32A<br>Function |  |  |  |  |

| 1          | GND                  | GND                  | GND                  |  |  |  |  |

| 2          | TDI, I/O             | TDI, I/O             | TDI, I/O             |  |  |  |  |

| 3          | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 4          | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 5          | I/O                  | 1/0                  | I/O                  |  |  |  |  |

| 6          | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 7          | TMS                  | TMS                  | TMS                  |  |  |  |  |

| 8          | V <sub>CCI</sub>     | V <sub>CCI</sub>     | V <sub>CCI</sub>     |  |  |  |  |

| 9          | GND                  | GND                  | GND                  |  |  |  |  |

| 10         | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 11         | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 12         | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 13         | I/O                  | 1/0                  | 1/0                  |  |  |  |  |

| 14         | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 15         | I/O                  | 1/0                  | 1/0                  |  |  |  |  |

| 16         | TRST, I/O            | TRST, I/O            | TRST, I/O            |  |  |  |  |

| 17         | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 18         | I/O                  | 1/0                  | I/O                  |  |  |  |  |

| 19         | I/O                  | 1/0                  | 1/0                  |  |  |  |  |

| 20         | V <sub>CCI</sub>     | V <sub>CCI</sub>     | V <sub>CCI</sub>     |  |  |  |  |

| 21         | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 22         | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 23         | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 24         | I/O                  | 1/0                  | 1/0                  |  |  |  |  |

| 25         | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 26         | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 27         | I/O                  | 1/0                  | I/O                  |  |  |  |  |

| 28         | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 29         | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 30         | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 31         | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 32         | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 33         | I/O                  | I/O                  | 1/0                  |  |  |  |  |

| 34         | PRB, I/O             | PRB, I/O             | PRB, I/O             |  |  |  |  |

| 35         | V <sub>CCA</sub>     | V <sub>CCA</sub>     | V <sub>CCA</sub>     |  |  |  |  |

| 100-TQFP   |                      |                      |                      |  |  |  |  |

|------------|----------------------|----------------------|----------------------|--|--|--|--|

| Pin Number | A54SX08A<br>Function | A54SX16A<br>Function | A54SX32A<br>Function |  |  |  |  |

| 36         | GND                  | GND                  | GND                  |  |  |  |  |

| 37         | NC                   | NC                   | NC                   |  |  |  |  |

| 38         | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 39         | HCLK                 | HCLK                 | HCLK                 |  |  |  |  |

| 40         | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 41         | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 42         | I/O                  | 1/0                  | I/O                  |  |  |  |  |

| 43         | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 44         | V <sub>CCI</sub>     | V <sub>CCI</sub>     | $V_{CCI}$            |  |  |  |  |

| 45         | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 46         | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 47         | I/O                  | 1/0                  | I/O                  |  |  |  |  |

| 48         | I/O                  | 1/0                  | I/O                  |  |  |  |  |

| 49         | TDO, I/O             | TDO, I/O             | TDO, I/O             |  |  |  |  |

| 50         | I/O                  | 1/0                  | I/O                  |  |  |  |  |

| 51         | GND                  | GND                  | GND                  |  |  |  |  |

| 52         | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 53         | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 54         | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 55         | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 56         | I/O                  | 1/0                  | I/O                  |  |  |  |  |

| 57         | $V_{CCA}$            | $V_{CCA}$            | $V_{CCA}$            |  |  |  |  |

| 58         | V <sub>CCI</sub>     | V <sub>CCI</sub>     | $V_{CCI}$            |  |  |  |  |

| 59         | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 60         | I/O                  | 1/0                  | I/O                  |  |  |  |  |

| 61         | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 62         | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 63         | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 64         | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 65         | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 66         | I/O                  | I/O                  | I/O                  |  |  |  |  |

| 67         | $V_{CCA}$            | $V_{CCA}$            | $V_{CCA}$            |  |  |  |  |

| 68         | GND                  | GND                  | GND                  |  |  |  |  |

| 69         | GND                  | GND                  | GND                  |  |  |  |  |

| 70         | I/O                  | 1/0                  | I/O                  |  |  |  |  |

3-6 v5.3

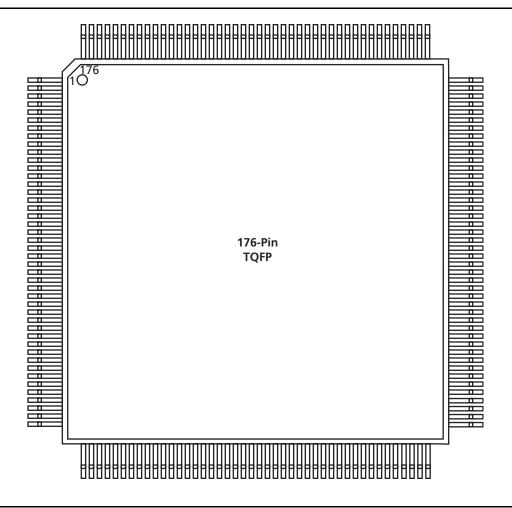

## 176-Pin TQFP

Figure 3-4 • 176-Pin TQFP (Top View)

### Note

For Package Manufacturing and Environmental information, visit Resource center at http://www.actel.com/products/rescenter/package/index.html.

| 329-Pin PBGA |           |  |  |  |  |  |

|--------------|-----------|--|--|--|--|--|

| Pin          | A54SX32A  |  |  |  |  |  |

| Number       | Function  |  |  |  |  |  |

| V22          | 1/0       |  |  |  |  |  |

| V23          | I/O       |  |  |  |  |  |

| W1           | 1/0       |  |  |  |  |  |

| W2           | 1/0       |  |  |  |  |  |

| W3           | 1/0       |  |  |  |  |  |

| W4           | 1/0       |  |  |  |  |  |

| W20          | I/O       |  |  |  |  |  |

| W21          | 1/0       |  |  |  |  |  |

| W22          | 1/0       |  |  |  |  |  |

| W23          | NC        |  |  |  |  |  |

| Y1           | NC        |  |  |  |  |  |

| Y2           | 1/0       |  |  |  |  |  |

| Y3           | 1/0       |  |  |  |  |  |

| Y4           | GND       |  |  |  |  |  |

| Y5           | 1/0       |  |  |  |  |  |

| Y6           | 1/0       |  |  |  |  |  |

| Y7           | 1/0       |  |  |  |  |  |

| Y8           | 1/0       |  |  |  |  |  |

| Y9           | 1/0       |  |  |  |  |  |

| Y10          | 1/0       |  |  |  |  |  |

| Y11          | 1/0       |  |  |  |  |  |

| Y12          | $V_{CCA}$ |  |  |  |  |  |

| Y13          | NC        |  |  |  |  |  |

| Y14          | 1/0       |  |  |  |  |  |

| Y15          | 1/0       |  |  |  |  |  |

| Y16          | I/O       |  |  |  |  |  |

| Y17          | I/O       |  |  |  |  |  |

| Y18          | I/O       |  |  |  |  |  |

| Y19          | I/O       |  |  |  |  |  |

| Y20          | GND       |  |  |  |  |  |

| Y21          | I/O       |  |  |  |  |  |

| Y22          | I/O       |  |  |  |  |  |

| Y23          | I/O       |  |  |  |  |  |

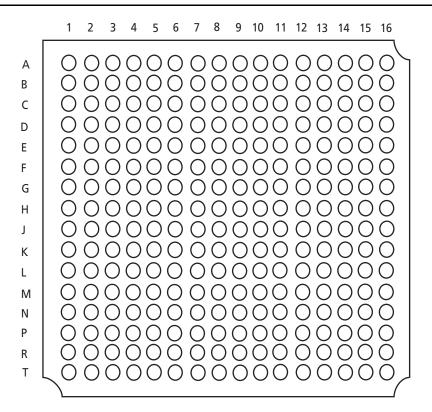

## 256-Pin FBGA

Figure 3-7 • 256-Pin FBGA (Top View)

#### **Note**

For Package Manufacturing and Environmental information, visit Resource center at http://www.actel.com/products/rescenter/package/index.html.

| 256-Pin FBGA |                      |                      |                      |

|--------------|----------------------|----------------------|----------------------|

| Pin Number   | A54SX16A<br>Function | A54SX32A<br>Function | A54SX72A<br>Function |

| A1           | GND                  | GND                  | GND                  |

| A2           | TCK, I/O             | TCK, I/O             | TCK, I/O             |

| А3           | I/O                  | 1/0                  | 1/0                  |

| A4           | I/O                  | 1/0                  | 1/0                  |

| A5           | I/O                  | 1/0                  | 1/0                  |

| A6           | I/O                  | 1/0                  | 1/0                  |

| Α7           | I/O                  | 1/0                  | I/O                  |

| A8           | I/O                  | 1/0                  | 1/0                  |

| A9           | CLKB                 | CLKB                 | CLKB                 |

| A10          | I/O                  | 1/0                  | 1/0                  |

| A11          | I/O                  | 1/0                  | 1/0                  |

| A12          | NC                   | 1/0                  | 1/0                  |

| A13          | I/O                  | 1/0                  | I/O                  |

| A14          | I/O                  | 1/0                  | 1/0                  |

| A15          | GND                  | GND                  | GND                  |

| A16          | GND                  | GND                  | GND                  |

| B1           | I/O                  | 1/0                  | 1/0                  |

| В2           | GND                  | GND                  | GND                  |

| В3           | I/O                  | 1/0                  | I/O                  |

| В4           | I/O                  | 1/0                  | I/O                  |

| B5           | I/O                  | 1/0                  | I/O                  |

| В6           | NC                   | 1/0                  | I/O                  |

| В7           | I/O                  | 1/0                  | I/O                  |

| В8           | $V_{CCA}$            | $V_{CCA}$            | $V_{CCA}$            |

| В9           | I/O                  | 1/0                  | I/O                  |

| B10          | I/O                  | 1/0                  | I/O                  |

| B11          | NC                   | 1/0                  | I/O                  |

| B12          | I/O                  | 1/0                  | I/O                  |

| B13          | I/O                  | 1/0                  | I/O                  |

| B14          | 1/0                  | 1/0                  | I/O                  |

| B15          | GND                  | GND                  | GND                  |

| B16          | I/O                  | 1/0                  | I/O                  |

| C1           | 1/0                  | 1/0                  | I/O                  |

| C2           | TDI, I/O             | TDI, I/O             | TDI, I/O             |

| C3           | GND                  | GND                  | GND                  |

| C4           | I/O                  | 1/0                  | I/O                  |

| C5           | NC                   | 1/0                  | I/O                  |

| 256-Pin FBGA |                      |                      |                      |

|--------------|----------------------|----------------------|----------------------|

| Pin Number   | A54SX16A<br>Function | A54SX32A<br>Function | A54SX72A<br>Function |

| C6           | I/O                  | I/O                  | I/O                  |

| C7           | I/O                  | I/O                  | I/O                  |

| C8           | I/O                  | I/O                  | I/O                  |

| С9           | CLKA                 | CLKA                 | CLKA                 |

| C10          | I/O                  | I/O                  | 1/0                  |

| C11          | I/O                  | I/O                  | I/O                  |

| C12          | I/O                  | I/O                  | I/O                  |

| C13          | I/O                  | I/O                  | I/O                  |

| C14          | I/O                  | I/O                  | I/O                  |

| C15          | I/O                  | I/O                  | I/O                  |

| C16          | I/O                  | I/O                  | I/O                  |

| D1           | I/O                  | I/O                  | I/O                  |

| D2           | I/O                  | I/O                  | I/O                  |

| D3           | I/O                  | I/O                  | I/O                  |

| D4           | I/O                  | I/O                  | I/O                  |

| D5           | I/O                  | I/O                  | I/O                  |

| D6           | I/O                  | 1/0                  | 1/0                  |

| D7           | I/O                  | 1/0                  | 1/0                  |

| D8           | PRA, I/O             | PRA, I/O             | PRA, I/O             |

| D9           | I/O                  | I/O                  | QCLKD                |

| D10          | I/O                  | I/O                  | I/O                  |

| D11          | NC                   | I/O                  | I/O                  |

| D12          | I/O                  | I/O                  | I/O                  |

| D13          | I/O                  | I/O                  | I/O                  |

| D14          | I/O                  | I/O                  | I/O                  |

| D15          | I/O                  | I/O                  | I/O                  |

| D16          | I/O                  | I/O                  | I/O                  |

| E1           | I/O                  | I/O                  | I/O                  |

| E2           | I/O                  | I/O                  | 1/0                  |

| E3           | I/O                  | I/O                  | 1/0                  |

| E4           | I/O                  | I/O                  | 1/0                  |

| E5           | I/O                  | I/O                  | 1/0                  |

| E6           | I/O                  | I/O                  | 1/0                  |

| E7           | I/O                  | I/O                  | QCLKC                |

| E8           | I/O                  | I/O                  | 1/0                  |

| E9           | I/O                  | I/O                  | 1/0                  |

| E10          | I/O                  | I/O                  | I/O                  |

3-22 v5.3

| Pin Number         A54SX32A Function         A54SXX Function           A1         NC*         NC           A2         NC*         NC           A3         NC*         I/O           A4         NC*         I/O           A5         NC*         I/O           A6         I/O         I/O           A7         I/O         I/O           A8         I/O         I/O           A9         I/O         I/O           A10         I/O         I/O           A11         NC*         I/O           A12         NC*         I/O           A13         I/O         I/O           A14         NC*         I/O           A15         NC*         I/O           A16         NC*         I/O           A17         I/O         I/O           A18         I/O         I/O           A20         I/O         I/O |   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| A2 NC* NC A3 NC* I/O A4 NC* I/O A5 NC* I/O A6 I/O I/O A7 I/O I/O A8 I/O I/O A9 I/O I/O A10 I/O I/O A11 NC* I/O A12 NC* I/O A13 I/O I/O A14 NC* NC A15 NC* I/O A16 NC* I/O A17 I/O I/O A17 I/O I/O A18 I/O I/O A19 I/O I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |

| A3 NC* I/O A4 NC* I/O A5 NC* I/O A6 I/O I/O A7 I/O I/O A8 I/O I/O A9 I/O I/O A10 I/O I/O A11 NC* I/O A12 NC* I/O A13 I/O I/O A14 NC* NC A15 NC* I/O A16 NC* I/O A17 I/O I/O A18 I/O I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

| A4       NC*       I/O         A5       NC*       I/O         A6       I/O       I/O         A7       I/O       I/O         A8       I/O       I/O         A9       I/O       I/O         A10       I/O       I/O         A11       NC*       I/O         A12       NC*       I/O         A13       I/O       I/O         A14       NC*       NC         A15       NC*       I/O         A16       NC*       I/O         A17       I/O       I/O         A18       I/O       I/O         A19       I/O       I/O                                                                                                                                                                                                                                                                                    |   |

| A5 NC* I/O A6 I/O I/O A7 I/O I/O A8 I/O I/O A9 I/O I/O A10 I/O I/O A11 NC* I/O A12 NC* I/O A13 I/O I/O A14 NC* NC A15 NC* I/O A16 NC* I/O A17 I/O I/O A18 I/O I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |

| A6       I/O       I/O         A7       I/O       I/O         A8       I/O       I/O         A9       I/O       I/O         A10       I/O       I/O         A11       NC*       I/O         A12       NC*       I/O         A13       I/O       I/O         A14       NC*       NC         A15       NC*       I/O         A16       NC*       I/O         A17       I/O       I/O         A18       I/O       I/O         A19       I/O       I/O                                                                                                                                                                                                                                                                                                                                                  |   |

| A7 I/O I/O  A8 I/O I/O  A9 I/O I/O  A10 I/O I/O  A11 NC* I/O  A12 NC* I/O  A13 I/O I/O  A14 NC* NC  A15 NC* I/O  A16 NC* I/O  A17 I/O I/O  A18 I/O I/O  A19 I/O I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |

| A8 I/O I/O A9 I/O I/O A10 I/O I/O A11 NC* I/O A12 NC* I/O A13 I/O I/O A14 NC* NC A15 NC* I/O A16 NC* I/O A17 I/O I/O A18 I/O I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| A9 I/O I/O A10 I/O I/O A11 NC* I/O A12 NC* I/O A13 I/O I/O A14 NC* NC A15 NC* I/O A16 NC* I/O A17 I/O I/O A18 I/O I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |

| A10 I/O I/O  A11 NC* I/O  A12 NC* I/O  A13 I/O I/O  A14 NC* NC  A15 NC* I/O  A16 NC* I/O  A17 I/O I/O  A18 I/O I/O  A19 I/O I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |

| A11 NC* I/O A12 NC* I/O A13 I/O I/O A14 NC* NC A15 NC* I/O A16 NC* I/O A17 I/O I/O A18 I/O I/O A19 I/O I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

| A12 NC* I/O  A13 I/O I/O  A14 NC* NC  A15 NC* I/O  A16 NC* I/O  A17 I/O I/O  A18 I/O I/O  A19 I/O I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |

| A13 I/O I/O  A14 NC* NC  A15 NC* I/O  A16 NC* I/O  A17 I/O I/O  A18 I/O I/O  A19 I/O I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |

| A14 NC* NC A15 NC* I/O A16 NC* I/O A17 I/O I/O A18 I/O I/O A19 I/O I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |

| A15 NC* I/O A16 NC* I/O A17 I/O I/O A18 I/O I/O A19 I/O I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |

| A16 NC* I/O A17 I/O I/O A18 I/O I/O A19 I/O I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |

| A17 I/O I/O A18 I/O I/O A19 I/O I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |

| A18 I/O I/O A19 I/O I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

| A19 I/O I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |

| 120 110 11-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |

| A20 I/O I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |

| A21 NC* I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |

| A22 NC* I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |

| A23 NC* I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |

| A24 NC* I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |

| A25 NC* NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

| A26 NC* NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

| AA1 NC* I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |

| AA2 NC* I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |

| AA3 V <sub>CCA</sub> V <sub>CCA</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Α |

| AA4 I/O I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |

| AA5 I/O I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |