Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

E·XFI

| Product Status                 | Active                                                                    |

|--------------------------------|---------------------------------------------------------------------------|

| Number of LABs/CLBs            | 6036                                                                      |

| Number of Logic Elements/Cells | -                                                                         |

| Total RAM Bits                 | -                                                                         |

| Number of I/O                  | 203                                                                       |

| Number of Gates                | 108000                                                                    |

| Voltage - Supply               | 2.25V ~ 5.25V                                                             |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | -40°C ~ 125°C (TA)                                                        |

| Package / Case                 | 256-BGA                                                                   |

| Supplier Device Package        | 256-FPBGA (17x17)                                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a54sx72a-fg256a |

|                                |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Temperature Grade Offering**

| Package | A54SX08A | A54SX16A | A54SX32A | A54SX72A |

|---------|----------|----------|----------|----------|

| PQ208   | C,I,A,M  | C,I,A,M  | C,I,A,M  | C,I,A,M  |

| TQ100   | C,I,A,M  | C,I,A,M  | C,I,A,M  |          |

| TQ144   | C,I,A,M  | C,I,A,M  | C,I,A,M  |          |

| TQ176   |          |          | C,I,M    |          |

| BG329   |          |          | C,I,M    |          |

| FG144   | C,I,A,M  | C,I,A,M  | C,I,A,M  |          |

| FG256   |          | C,I,A,M  | C,I,A,M  | C,I,A,M  |

| FG484   |          |          | C,I,M    | C,I,A,M  |

| CQ208   |          |          | C,M,B    | C,M,B    |

| CQ256   |          |          | C,M,B    | C,M,B    |

### Notes:

1. C = Commercial

- 2. I = Industrial

- 3. A = Automotive

- 4. M = Military

- 5. B = MIL-STD-883 Class B

6. For more information regarding automotive products, refer to the SX-A Automotive Family FPGAs datasheet.

7. For more information regarding Mil-Temp and ceramic packages, refer to the HiRel SX-A Family FPGAs datasheet.

# Speed Grade and Temperature Grade Matrix

|              | F | Std | -1 | -2 | -3           |

|--------------|---|-----|----|----|--------------|

| Commercial   | ✓ | 1   | 1  | 1  | Discontinued |

| Industrial   |   | 1   | 1  | 1  | Discontinued |

| Automotive   |   | 1   |    |    |              |

| Military     |   | 1   | 1  |    |              |

| MIL-STD-883B |   | 1   | 1  |    |              |

#### Notes:

1. For more information regarding automotive products, refer to the SX-A Automotive Family FPGAs datasheet.

2. For more information regarding Mil-Temp and ceramic packages, refer to the HiRel SX-A Family FPGAs datasheet.

Contact your Actel Sales representative for more information on availability.

# **General Description**

# Introduction

The Actel SX-A family of FPGAs offers a cost-effective, single-chip solution for low-power, high-performance designs. Fabricated on 0.22  $\mu m$  / 0.25  $\mu m$  CMOS antifuse technology and with the support of 2.5 V, 3.3 V and 5 V I/Os, the SX-A is a versatile platform to integrate designs while significantly reducing time-to-market.

# **SX-A Family Architecture**

The SX-A family's device architecture provides a unique approach to module organization and chip routing that satisfies performance requirements and delivers the most optimal register/logic mix for a wide variety of applications.

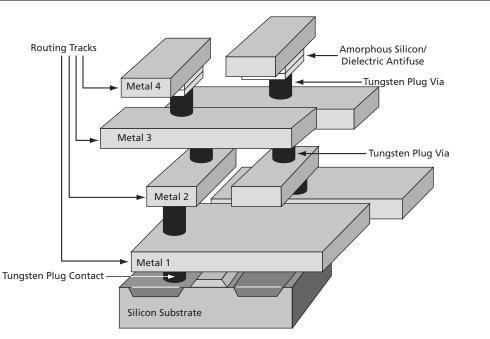

Interconnection between these logic modules is achieved using Actel's patented metal-to-metal programmable antifuse interconnect elements (Figure 1-1). The antifuses are normally open circuit and, when programmed, form a permanent low-impedance connection.

**Note:** The A54SX72A device has four layers of metal with the antifuse between Metal 3 and Metal 4. The A54SX08A, A54SX16A, and A54SX32A devices have three layers of metal with the antifuse between Metal 2 and Metal 3.

Figure 1-1 • SX-A Family Interconnect Elements

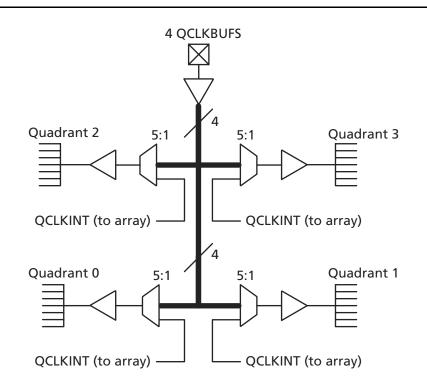

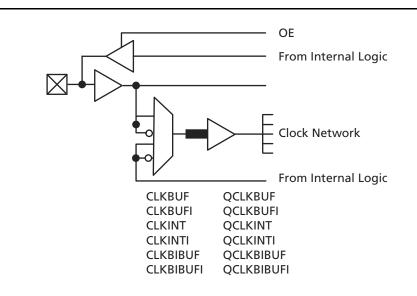

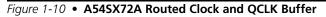

## Figure 1-9 • SX-A QCLK Architecture

# **Probing Capabilities**

SX-A devices also provide an internal probing capability that is accessed with the JTAG pins. The Silicon Explorer II diagnostic hardware is used to control the TDI, TCK, TMS, and TDO pins to select the desired nets for debugging. The user assigns the selected internal nets in Actel Silicon Explorer II software to the PRA/PRB output pins for observation. Silicon Explorer II automatically places the device into JTAG mode. However, probing functionality is only activated when the TRST pin is driven high or left floating, allowing the internal pull-up resistor to pull TRST High. If the TRST pin is held Low, the TAP controller remains in the Test-Logic-Reset state so no probing can be performed. However, the user must drive the TRST pin High or allow the internal pull-up resistor to pull TRST High. When selecting the **Reserve Probe Pin** box as shown in Figure 1-12 on page 1-9, direct the layout tool to reserve the PRA and PRB pins as dedicated outputs for probing. This **Reserve** option is merely a guideline. If the designer assigns user I/Os to the PRA and PRB pins and selects the **Reserve Probe Pin** option, Designer Layout will override the **Reserve Probe Pin** option and place the user I/Os on those pins.

To allow probing capabilities, the security fuse must not be programmed. Programming the security fuse disables the JTAG and probe circuitry. Table 1-9 summarizes the possible device configurations for probing once the device leaves the Test-Logic-Reset JTAG state.

| JTAG Mode | TRST <sup>1</sup> | Security Fuse Programmed | PRA, PRB <sup>2</sup> | TDI, TCK, TDO <sup>2</sup> |

|-----------|-------------------|--------------------------|-----------------------|----------------------------|

| Dedicated | Low               | No                       | User I/O <sup>3</sup> | JTAG Disabled              |

|           | High              | No                       | Probe Circuit Outputs | JTAG I/O                   |

| Flexible  | Low               | No                       | User I/O <sup>3</sup> | User I/O <sup>3</sup>      |

|           | High              | No                       | Probe Circuit Outputs | JTAG I/O                   |

|           |                   | Yes                      | Probe Circuit Secured | Probe Circuit Secured      |

Table 1-9 • Device Configuration Options for Probe Capability (TRST Pin Reserved)

Notes:

1. If the TRST pin is not reserved, the device behaves according to TRST = High as described in the table.

2. Avoid using the TDI, TCK, TDO, PRA, and PRB pins as input or bidirectional ports. Since these pins are active during probing, input signals will not pass through these pins and may cause contention.

3. If no user signal is assigned to these pins, they will behave as unused I/Os in this mode. Unused pins are automatically tristated by the Designer software.

# **Detailed Specifications**

# **Operating Conditions**

### Table 2-1 • Absolute Maximum Ratings

| Symbol           | Parameter                    | Limits                           | Units |

|------------------|------------------------------|----------------------------------|-------|

| V <sub>CCI</sub> | DC Supply Voltage for I/Os   | -0.3 to +6.0                     | V     |

| V <sub>CCA</sub> | DC Supply Voltage for Arrays | -0.3 to +3.0                     | V     |

| VI               | Input Voltage                | -0.5 to +5.75                    | V     |

| V <sub>O</sub>   | Output Voltage               | –0.5 to + V <sub>CCI</sub> + 0.5 | V     |

| T <sub>STG</sub> | Storage Temperature          | -65 to +150                      | °C    |

**Note:** \*Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum rated conditions for extended periods may affect device reliability. Devices should not be operated outside the "Recommended Operating Conditions".

### Table 2-2 Recommended Operating Conditions

| Parameter                                                         | Commercial   | Industrial   | Units |

|-------------------------------------------------------------------|--------------|--------------|-------|

| Temperature Range                                                 | 0 to +70     | -40 to +85   | °C    |

| 2.5 V Power Supply Range (V <sub>CCA</sub> and V <sub>CCI</sub> ) | 2.25 to 2.75 | 2.25 to 2.75 | V     |

| 3.3 V Power Supply Range (V <sub>CCI</sub> )                      | 3.0 to 3.6   | 3.0 to 3.6   | V     |

| 5 V Power Supply Range (V <sub>CCI</sub> )                        | 4.75 to 5.25 | 4.75 to 5.25 | V     |

# **Typical SX-A Standby Current**

# Table 2-3 • Typical Standby Current for SX-A at 25°C with $V_{CCA} = 2.5 V$

| Product  | V <sub>CCI</sub> = 2.5 V | V <sub>CCI</sub> = 3.3 V | V <sub>CCI</sub> = 5 V |

|----------|--------------------------|--------------------------|------------------------|

| A54SX08A | 0.8 mA                   | 1.0 mA                   | 2.9 mA                 |

| A54SX16A | 0.8 mA                   | 1.0 mA                   | 2.9 mA                 |

| A54SX32A | 0.9 mA                   | 1.0 mA                   | 3.0 mA                 |

| A54SX72A | 3.6 mA                   | 3.8 mA                   | 4.5 mA                 |

#### Table 2-4 • Supply Voltages

| V <sub>CCA</sub> | V <sub>CCI</sub> * | Maximum Input Tolerance | Maximum Output Drive |

|------------------|--------------------|-------------------------|----------------------|

| 2. 5 V           | 2.5 V              | 5.75 V                  | 2.7 V                |

| 2.5 V            | 3.3 V              | 5.75 V                  | 3.6 V                |

| 2.5 V            | 5 V                | 5.75 V                  | 5.25 V               |

Note: \*3.3 V PCI is not 5 V tolerant due to the clamp diode, but instead is 3.3 V tolerant.

# **Electrical Specifications**

Table 2-5 • 3.3 V LVTTL and 5 V TTL Electrical Specifications

|                                  |                                                                  |                           | Comm                 | ercial | Indus                | strial |       |

|----------------------------------|------------------------------------------------------------------|---------------------------|----------------------|--------|----------------------|--------|-------|

| Symbol                           | Parameter                                                        |                           | Min.                 | Max.   | Min.                 | Max.   | Units |

| V <sub>OH</sub>                  | $V_{CCI} = Minimum$<br>$V_I = V_{IH} \text{ or } V_{IL}$         | (I <sub>OH</sub> = -1 mA) | 0.9 V <sub>CCI</sub> |        | 0.9 V <sub>CCI</sub> |        | V     |

|                                  | $V_{CCI} = Minimum$<br>$V_I = V_{IH} \text{ or } V_{IL}$         | (I <sub>OH</sub> = -8 mA) | 2.4                  |        | 2.4                  |        | V     |

| V <sub>OL</sub>                  | $V_{CCI} = Minimum$<br>$V_I = V_{IH} \text{ or } V_{IL}$         | (I <sub>OL</sub> = 1 mA)  |                      | 0.4    |                      | 0.4    | V     |

|                                  | $V_{CCI} = Minimum$<br>$V_I = V_{IH} \text{ or } V_{IL}$         | (I <sub>OL</sub> = 12 mA) |                      | 0.4    |                      | 0.4    | V     |

| V <sub>IL</sub>                  | Input Low Voltage                                                |                           |                      | 0.8    |                      | 0.8    | V     |

| V <sub>IH</sub>                  | Input High Voltage                                               |                           | 2.0                  | 5.75   | 2.0                  | 5.75   | V     |

| I <sub>IL</sub> /I <sub>IH</sub> | Input Leakage Current, V <sub>IN</sub> = V <sub>CCI</sub> or GND |                           | -10                  | 10     | -10                  | 10     | μA    |

| I <sub>OZ</sub>                  | Tristate Output Leakage Current                                  |                           | -10                  | 10     | -10                  | 10     | μΑ    |

| t <sub>R</sub> , t <sub>F</sub>  | Input Transition Time t <sub>R</sub> , t <sub>F</sub>            |                           |                      | 10     |                      | 10     | ns    |

| C <sub>IO</sub>                  | I/O Capacitance                                                  |                           |                      | 10     |                      | 10     | pF    |

| I <sub>CC</sub>                  | Standby Current                                                  |                           |                      | 10     |                      | 20     | mA    |

| IV Curve*                        | Can be derived from the IBIS model on the web                    | •<br>).                   |                      |        | •                    |        |       |

Note: \*The IBIS model can be found at http://www.actel.com/download/ibis/default.aspx.

## Table 2-6 • 2.5 V LVCMOS2 Electrical Specifications

|                                  |                                                                  |                               | Commercial |      | Indu | strial |       |

|----------------------------------|------------------------------------------------------------------|-------------------------------|------------|------|------|--------|-------|

| Symbol                           | Parameter                                                        |                               | Min.       | Max. | Min. | Max.   | Units |

| V <sub>OH</sub>                  | $V_{DD} = MIN,$<br>$V_{I} = V_{IH} \text{ or } V_{IL}$           | $(I_{OH} = -100 \mu\text{A})$ | 2.1        |      | 2.1  |        | V     |

|                                  | $V_{DD} = MIN,$<br>$V_{I} = V_{IH} \text{ or } V_{IL}$           | (I <sub>OH</sub> = -1 mA)     | 2.0        |      | 2.0  |        | V     |

|                                  | $V_{DD} = MIN,$<br>$V_{I} = V_{IH} \text{ or } V_{IL}$           | (I <sub>OH</sub> =2 mA)       | 1.7        |      | 1.7  |        | V     |

| V <sub>OL</sub>                  | $V_{DD} = MIN,$<br>$V_{I} = V_{IH} \text{ or } V_{IL}$           | (I <sub>OL</sub> = 100 μA)    |            | 0.2  |      | 0.2    | V     |

|                                  | $V_{DD} = MIN,$<br>$V_{I} = V_{IH} \text{ or } V_{IL}$           | (I <sub>OL</sub> = 1 mA)      |            | 0.4  |      | 0.4    | V     |

|                                  | $V_{DD} = MIN,$<br>$V_{I} = V_{IH} \text{ or } V_{IL}$           | (I <sub>OL</sub> = 2 mA)      |            | 0.7  |      | 0.7    | V     |

| V <sub>IL</sub>                  | Input Low Voltage, V <sub>OUT</sub> ≤ V <sub>VOL(max)</sub>      |                               | -0.3       | 0.7  | -0.3 | 0.7    | V     |

| V <sub>IH</sub>                  | Input High Voltage, V <sub>OUT</sub> ≥ V <sub>VOH(min)</sub>     |                               | 1.7        | 5.75 | 1.7  | 5.75   | V     |

| I <sub>IL</sub> /I <sub>IH</sub> | Input Leakage Current, V <sub>IN</sub> = V <sub>CCI</sub> or GND |                               | -10        | 10   | -10  | 10     | μΑ    |

| I <sub>OZ</sub>                  | Tristate Output Leakage Current, $V_{OUT} = V_{CCI}$ or GND      |                               | -10        | 10   | -10  | 10     | μΑ    |

| t <sub>R</sub> , t <sub>F</sub>  | Input Transition Time t <sub>R</sub> , t <sub>F</sub>            |                               |            | 10   |      | 10     | ns    |

| C <sub>IO</sub>                  | I/O Capacitance                                                  |                               |            | 10   |      | 10     | pF    |

| I <sub>CC</sub>                  | Standby Current                                                  |                               |            | 10   |      | 20     | mA    |

| IV Curve*                        | Can be derived from the IBIS model on the web.                   |                               |            |      |      |        | •     |

Note: \*The IBIS model can be found at http://www.actel.com/download/ibis/default.aspx.

## Table 2-22 A54SX16A Timing Characteristics

|                    |                                                         | -3 Speed* |      | -2 Speed |      | –1 Speed |      | Std. Speed |      | -F Speed |      |       |

|--------------------|---------------------------------------------------------|-----------|------|----------|------|----------|------|------------|------|----------|------|-------|

| Parameter          | Description                                             | Min.      | Max. | Min.     | Max. | Min.     | Max. | Min.       | Max. | Min.     | Max. | Units |

| Dedicated (        | (Hardwired) Array Clock Netwo                           | rks       |      |          |      |          |      |            |      |          |      |       |

| t <sub>нскн</sub>  | Input Low to High<br>(Pad to R-cell Input)              |           | 1.2  |          | 1.4  |          | 1.6  |            | 1.8  |          | 2.8  | ns    |

| t <sub>HCKL</sub>  | Input High to Low<br>(Pad to R-cell Input)              |           | 1.0  |          | 1.1  |          | 1.2  |            | 1.5  |          | 2.2  | ns    |

| t <sub>HPWH</sub>  | Minimum Pulse Width High                                | 1.4       |      | 1.7      |      | 1.9      |      | 2.2        |      | 3.0      |      | ns    |

| t <sub>HPWL</sub>  | Minimum Pulse Width Low                                 | 1.4       |      | 1.7      |      | 1.9      |      | 2.2        |      | 3.0      |      | ns    |

| t <sub>HCKSW</sub> | Maximum Skew                                            |           | 0.3  |          | 0.3  |          | 0.4  |            | 0.4  |          | 0.7  | ns    |

| t <sub>HP</sub>    | Minimum Period                                          | 2.8       |      | 3.4      |      | 3.8      |      | 4.4        |      | 6.0      |      | ns    |

| f <sub>HMAX</sub>  | Maximum Frequency                                       |           | 357  |          | 294  |          | 263  |            | 227  |          | 167  | MHz   |

| Routed Arr         | ay Clock Networks                                       |           |      |          |      |          |      |            |      |          |      |       |

| t <sub>RCKH</sub>  | Input Low to High (Light Load)<br>(Pad to R-cell Input) |           | 1.0  |          | 1.2  |          | 1.3  |            | 1.6  |          | 2.2  | ns    |

| t <sub>RCKL</sub>  | Input High to Low (Light Load)<br>(Pad to R-cell Input) |           | 1.1  |          | 1.3  |          | 1.5  |            | 1.7  |          | 2.4  | ns    |

| t <sub>RCKH</sub>  | Input Low to High (50% Load)<br>(Pad to R-cell Input)   |           | 1.1  |          | 1.3  |          | 1.5  |            | 1.7  |          | 2.4  | ns    |

| t <sub>RCKL</sub>  | Input High to Low (50% Load)<br>(Pad to R-cell Input)   |           | 1.1  |          | 1.3  |          | 1.5  |            | 1.7  |          | 2.4  | ns    |

| t <sub>RCKH</sub>  | Input Low to High (100% Load)<br>(Pad to R-cell Input)  |           | 1.3  |          | 1.5  |          | 1.7  |            | 2.0  |          | 2.8  | ns    |

| t <sub>RCKL</sub>  | Input High to Low (100% Load)<br>(Pad to R-cell Input)  |           | 1.3  |          | 1.5  |          | 1.7  |            | 2.0  |          | 2.8  | ns    |

| t <sub>RPWH</sub>  | Minimum Pulse Width High                                | 1.4       |      | 1.7      |      | 1.9      |      | 2.2        |      | 3.0      |      | ns    |

| t <sub>RPWL</sub>  | Minimum Pulse Width Low                                 | 1.4       |      | 1.7      |      | 1.9      |      | 2.2        |      | 3.0      |      | ns    |

| t <sub>RCKSW</sub> | Maximum Skew (Light Load)                               |           | 0.8  |          | 0.9  |          | 1.0  |            | 1.2  |          | 1.7  | ns    |

| t <sub>RCKSW</sub> | Maximum Skew (50% Load)                                 |           | 0.8  |          | 0.9  |          | 1.0  |            | 1.2  |          | 1.7  | ns    |

| t <sub>RCKSW</sub> | Maximum Skew (100% Load)                                |           | 1.0  |          | 1.1  |          | 1.3  |            | 1.5  |          | 2.1  | ns    |

*Note:* \*All –3 speed grades have been discontinued.

## Table 2-31 A54SX32A Timing Characteristics

| (Worst-Case Commercial Conditions | V <sub>CCA</sub> = 2.25 V, V <sub>CCI</sub> = 4.7 | ′5 V, T <sub>J</sub> = 70°C) |

|-----------------------------------|---------------------------------------------------|------------------------------|

|-----------------------------------|---------------------------------------------------|------------------------------|

|                    |                                                         | -3 Sp | beed* | -2 S | peed | -1 S | peed | Std. | Speed | –F S |      |          |

|--------------------|---------------------------------------------------------|-------|-------|------|------|------|------|------|-------|------|------|----------|

| Parameter          | Description                                             | Min.  | Max.  | Min. | Max. | Min. | Max. | Min. | Max.  | Min. | Max. | Units    |

| Dedicated (        | (Hardwired) Array Clock Netwo                           | rks   |       | 1    |      |      |      |      |       |      |      | 1        |

| t <sub>нскн</sub>  | Input Low to High<br>(Pad to R-cell Input)              |       | 1.7   |      | 1.9  |      | 2.2  |      | 2.6   |      | 4.0  | ns       |

| t <sub>HCKL</sub>  | Input High to Low<br>(Pad to R-cell Input)              |       | 1.7   |      | 2.0  |      | 2.2  |      | 2.6   |      | 4.0  | ns       |

| t <sub>HPWH</sub>  | Minimum Pulse Width High                                | 1.4   |       | 1.6  |      | 1.8  |      | 2.1  |       | 2.9  |      | ns       |

| t <sub>HPWL</sub>  | Minimum Pulse Width Low                                 | 1.4   |       | 1.6  |      | 1.8  |      | 2.1  |       | 2.9  |      | ns       |

| t <sub>HCKSW</sub> | Maximum Skew                                            |       | 0.6   |      | 0.6  |      | 0.7  |      | 0.8   |      | 1.3  | ns       |

| t <sub>HP</sub>    | Minimum Period                                          | 2.8   |       | 3.2  |      | 3.6  |      | 4.2  |       | 5.8  |      | ns       |

| f <sub>HMAX</sub>  | Maximum Frequency                                       |       | 357   |      | 313  |      | 278  |      | 238   |      | 172  | MHz      |

| Routed Arr         | ay Clock Networks                                       | 4     |       |      |      |      |      |      |       |      |      | <u>.</u> |

| t <sub>RCKH</sub>  | Input Low to High (Light Load)<br>(Pad to R-cell Input) |       | 2.2   |      | 2.5  |      | 2.8  |      | 3.3   |      | 4.7  | ns       |

| t <sub>RCKL</sub>  | Input High to Low (Light Load)<br>(Pad to R-cell Input) |       | 2.1   |      | 2.5  |      | 2.8  |      | 3.3   |      | 4.5  | ns       |

| t <sub>RCKH</sub>  | Input Low to High (50% Load)<br>(Pad to R-cell Input)   |       | 2.4   |      | 2.7  |      | 3.1  |      | 3.6   |      | 5.1  | ns       |

| t <sub>RCKL</sub>  | Input High to Low (50% Load)<br>(Pad to R-cell Input)   |       | 2.2   |      | 2.6  |      | 2.9  |      | 3.4   |      | 4.7  | ns       |

| t <sub>RCKH</sub>  | Input Low to High (100% Load)<br>(Pad to R-cell Input)  |       | 2.5   |      | 2.8  |      | 3.2  |      | 3.8   |      | 5.3  | ns       |

| t <sub>RCKL</sub>  | Input High to Low (100% Load)<br>(Pad to R-cell Input)  |       | 2.4   |      | 2.8  |      | 3.1  |      | 3.7   |      | 5.2  | ns       |

| t <sub>RPWH</sub>  | Minimum Pulse Width High                                | 1.4   |       | 1.6  |      | 1.8  |      | 2.1  |       | 2.9  |      | ns       |

| t <sub>RPWL</sub>  | Minimum Pulse Width Low                                 | 1.4   |       | 1.6  |      | 1.8  |      | 2.1  |       | 2.9  |      | ns       |

| t <sub>RCKSW</sub> | Maximum Skew (Light Load)                               |       | 1.0   |      | 1.1  |      | 1.3  |      | 1.5   |      | 2.1  | ns       |

| t <sub>RCKSW</sub> | Maximum Skew (50% Load)                                 |       | 1.0   |      | 1.1  |      | 1.3  |      | 1.5   |      | 2.1  | ns       |

| t <sub>RCKSW</sub> | Maximum Skew (100% Load)                                |       | 1.0   |      | 1.1  |      | 1.3  |      | 1.5   |      | 2.1  | ns       |

*Note:* \*All –3 speed grades have been discontinued.

### Table 2-32 A54SX32A Timing Characteristics

| (Worst-Case Commercial Conditions V | / <sub>CCA</sub> = 2.25 V, V <sub>CCI</sub> = 2.3 V, T <sub>J</sub> = 70°C) |

|-------------------------------------|-----------------------------------------------------------------------------|

|-------------------------------------|-----------------------------------------------------------------------------|

|                      |                                        | -3 Sp | eed <sup>1</sup> | -2 S | peed  | –1 S | peed  | Std. 9 | 5peed | -F Speed |       |       |

|----------------------|----------------------------------------|-------|------------------|------|-------|------|-------|--------|-------|----------|-------|-------|

| Parameter            | Description                            | Min.  | Max.             | Min. | Max.  | Min. | Max.  | Min.   | Max.  | Min.     | Max.  | Units |

| 2.5 V LVCM           | OS Output Module Timing <sup>2,3</sup> |       |                  |      |       |      |       |        |       |          |       |       |

| t <sub>DLH</sub>     | Data-to-Pad Low to High                |       | 3.3              |      | 3.8   |      | 4.2   |        | 5.0   |          | 7.0   | ns    |

| t <sub>DHL</sub>     | Data-to-Pad High to Low                |       | 2.5              |      | 2.9   |      | 3.2   |        | 3.8   |          | 5.3   | ns    |

| t <sub>DHLS</sub>    | Data-to-Pad High to Low—low slew       |       | 11.1             |      | 12.8  |      | 14.5  |        | 17.0  |          | 23.8  | ns    |

| t <sub>ENZL</sub>    | Enable-to-Pad, Z to L                  |       | 2.4              |      | 2.8   |      | 3.2   |        | 3.7   |          | 5.2   | ns    |

| t <sub>ENZLS</sub>   | Data-to-Pad, Z to L—low slew           |       | 11.8             |      | 13.7  |      | 15.5  |        | 18.2  |          | 25.5  | ns    |

| t <sub>ENZH</sub>    | Enable-to-Pad, Z to H                  |       | 3.3              |      | 3.8   |      | 4.2   |        | 5.0   |          | 7.0   | ns    |

| t <sub>ENLZ</sub>    | Enable-to-Pad, L to Z                  |       | 2.1              |      | 2.5   |      | 2.8   |        | 3.3   |          | 4.7   | ns    |

| t <sub>ENHZ</sub>    | Enable-to-Pad, H to Z                  |       | 2.5              |      | 2.9   |      | 3.2   |        | 3.8   |          | 5.3   | ns    |

| $d_{\text{TLH}}^{4}$ | Delta Low to High                      |       | 0.031            |      | 0.037 |      | 0.043 |        | 0.051 |          | 0.071 | ns/pF |

| $d_{\text{THL}}^4$   | Delta High to Low                      |       | 0.017            |      | 0.017 |      | 0.023 |        | 0.023 |          | 0.037 | ns/pF |

| ${\sf d_{THLS}}^4$   | Delta High to Low—low slew             |       | 0.057            |      | 0.06  |      | 0.071 |        | 0.086 |          | 0.117 | ns/pF |

### Note:

1. All –3 speed grades have been discontinued.

2. Delays based on 35 pF loading.

3. The equivalent IO Attribute settings for 2.5 V LVCMOS is 2.5 V LVTTL in the software.

4. To obtain the slew rate, substitute the appropriate Delta value, load capacitance, and the  $V_{CCI}$  value into the following equation: Slew Rate [V/ns] =  $(0.1 * V_{CCI} - 0.9 * V_{CCI})/(C_{load} * d_{T[LH|HL|HLS]})$ where  $C_{load}$  is the load capacitance driven by the I/O in pF

$d_{T[LH|HL|HLS]}$  is the worst case delta value from the datasheet in ns/pF.

### Table 2-33 • A54SX32A Timing Characteristics

| (Worst-Case Commercial Conditions | $V_{CCA} = 2.25 V, V_{CCI} = 3.0$ | V, T <sub>J</sub> = 70°C) |

|-----------------------------------|-----------------------------------|---------------------------|

|-----------------------------------|-----------------------------------|---------------------------|

|                                |                                   | –3 Sp | beed <sup>1</sup> | -2 S | peed  | -1 S | peed  | Std. | Speed | –F S |       |       |

|--------------------------------|-----------------------------------|-------|-------------------|------|-------|------|-------|------|-------|------|-------|-------|

| Parameter                      | Description                       | Min.  | Max.              | Min. | Max.  | Min. | Max.  | Min. | Max.  | Min. | Max.  | Units |

| 3.3 V PCI Ou                   | utput Module Timing <sup>2</sup>  |       |                   |      |       |      |       |      |       |      |       |       |

| t <sub>DLH</sub>               | Data-to-Pad Low to High           |       | 1.9               |      | 2.2   |      | 2.4   |      | 2.9   |      | 4.0   | ns    |

| t <sub>DHL</sub>               | Data-to-Pad High to Low           |       | 2.0               |      | 2.3   |      | 2.6   |      | 3.1   |      | 4.3   | ns    |

| t <sub>ENZL</sub>              | Enable-to-Pad, Z to L             |       | 1.4               |      | 1.7   |      | 1.9   |      | 2.2   |      | 3.1   | ns    |

| t <sub>ENZH</sub>              | Enable-to-Pad, Z to H             |       | 1.9               |      | 2.2   |      | 2.4   |      | 2.9   |      | 4.0   | ns    |

| t <sub>ENLZ</sub>              | Enable-to-Pad, L to Z             |       | 2.5               |      | 2.8   |      | 3.2   |      | 3.8   |      | 5.3   | ns    |

| t <sub>ENHZ</sub>              | Enable-to-Pad, H to Z             |       | 2.0               |      | 2.3   |      | 2.6   |      | 3.1   |      | 4.3   | ns    |

| $d_{TLH}^{3}$                  | Delta Low to High                 |       | 0.025             |      | 0.03  |      | 0.03  |      | 0.04  |      | 0.045 | ns/pF |

| d <sub>THL</sub> <sup>3</sup>  | Delta High to Low                 |       | 0.015             |      | 0.015 |      | 0.015 |      | 0.015 |      | 0.025 | ns/pF |

| 3.3 V LVTTL                    | Output Module Timing <sup>4</sup> |       |                   |      |       |      |       |      |       |      |       |       |

| t <sub>DLH</sub>               | Data-to-Pad Low to High           |       | 2.6               |      | 3.0   |      | 3.4   |      | 4.0   |      | 5.6   | ns    |

| t <sub>DHL</sub>               | Data-to-Pad High to Low           |       | 2.6               |      | 3.0   |      | 3.3   |      | 3.9   |      | 5.5   | ns    |

| t <sub>DHLS</sub>              | Data-to-Pad High to Low—low slew  |       | 9.0               |      | 10.4  |      | 11.8  |      | 13.8  |      | 19.3  | ns    |

| t <sub>ENZL</sub>              | Enable-to-Pad, Z to L             |       | 2.2               |      | 2.6   |      | 2.9   |      | 3.4   |      | 4.8   | ns    |

| t <sub>ENZLS</sub>             | Enable-to-Pad, Z to L—low slew    |       | 15.8              |      | 18.9  |      | 21.3  |      | 25.4  |      | 34.9  | ns    |

| t <sub>ENZH</sub>              | Enable-to-Pad, Z to H             |       | 2.6               |      | 3.0   |      | 3.4   |      | 4.0   |      | 5.6   | ns    |

| t <sub>ENLZ</sub>              | Enable-to-Pad, L to Z             |       | 2.9               |      | 3.3   |      | 3.7   |      | 4.4   |      | 6.2   | ns    |

| t <sub>ENHZ</sub>              | Enable-to-Pad, H to Z             |       | 2.6               |      | 3.0   |      | 3.3   |      | 3.9   |      | 5.5   | ns    |

| d <sub>TLH</sub> <sup>3</sup>  | Delta Low to High                 |       | 0.025             |      | 0.03  |      | 0.03  |      | 0.04  |      | 0.045 | ns/pF |

| $d_{THL}^3$                    | Delta High to Low                 |       | 0.015             |      | 0.015 |      | 0.015 |      | 0.015 |      | 0.025 | ns/pF |

| d <sub>THLS</sub> <sup>3</sup> | Delta High to Low—low slew        |       | 0.053             |      | 0.053 |      | 0.067 |      | 0.073 |      | 0.107 | ns/pF |

Notes:

1. All –3 speed grades have been discontinued.

2. Delays based on 10 pF loading and 25  $\Omega$  resistance.

3. To obtain the slew rate, substitute the appropriate Delta value, load capacitance, and the  $V_{CCI}$  value into the following equation: Slew Rate [V/ns] = (0.1\* $V_{CCI}$  - 0.9\* $V_{CCI}$ / ( $C_{load}$  \*  $d_{T[LH|HL|HLS]}$ ) where  $C_{load}$  is the load capacitance driven by the I/O in pF

$d_{T[LH|HL|HLS]}$  is the worst case delta value from the datasheet in ns/pF.

4. Delays based on 35 pF loading.

## Table 2-35 A545X72A Timing Characteristics (Continued)

|                    |                                          | -3 Sp | beed <sup>1</sup> | -2 S | peed | –1 S | peed | Std. 9 | Speed | -F Sj | peed |       |

|--------------------|------------------------------------------|-------|-------------------|------|------|------|------|--------|-------|-------|------|-------|

| Parameter          | Description                              | Min.  | Max.              | Min. | Max. | Min. | Max. | Min.   | Max.  | Min.  | Max. | Units |

| t <sub>INYH</sub>  | Input Data Pad to Y High 5 V PCI         |       | 0.5               |      | 0.6  |      | 0.7  |        | 0.8   |       | 1.1  | ns    |

| t <sub>INYL</sub>  | Input Data Pad to Y Low 5 V PCI          |       | 0.8               |      | 0.9  |      | 1.0  |        | 1.2   |       | 1.6  | ns    |

| t <sub>INYH</sub>  | Input Data Pad to Y High 5 V TTL         |       | 0.7               |      | 0.8  |      | 0.9  |        | 1.0   |       | 1.4  | ns    |

| t <sub>INYL</sub>  | Input Data Pad to Y Low 5 V TTL          |       | 0.9               |      | 1.1  |      | 1.2  |        | 1.4   |       | 1.9  | ns    |

| Input Modu         | le Predicted Routing Delays <sup>3</sup> |       |                   |      |      |      |      |        |       |       |      |       |

| t <sub>IRD1</sub>  | FO = 1 Routing Delay                     |       | 0.3               |      | 0.3  |      | 0.4  |        | 0.5   |       | 0.7  | ns    |

| t <sub>IRD2</sub>  | FO = 2 Routing Delay                     |       | 0.4               |      | 0.5  |      | 0.6  |        | 0.7   |       | 1    | ns    |

| t <sub>IRD3</sub>  | FO = 3 Routing Delay                     |       | 0.5               |      | 0.7  |      | 0.8  |        | 0.9   |       | 1.3  | ns    |

| t <sub>IRD4</sub>  | FO = 4 Routing Delay                     |       | 0.7               |      | 0.9  |      | 1    |        | 1.1   |       | 1.5  | ns    |

| t <sub>IRD8</sub>  | FO = 8 Routing Delay                     |       | 1.2               |      | 1.5  |      | 1.7  |        | 2.1   |       | 2.9  | ns    |

| t <sub>IRD12</sub> | FO = 12 Routing Delay                    |       | 1.7               |      | 2.2  |      | 2.5  |        | 3     |       | 4.2  | ns    |

## (Worst-Case Commercial Conditions, V<sub>CCA</sub> = 2.25 V, V<sub>CCI</sub> = 3.0 V, T<sub>J</sub> = 70°C)

Notes:

1. All –3 speed grades have been discontinued.

2. For dual-module macros, use  $t_{PD} + t_{RD1} + t_{PDn}$ ,  $t_{RCO} + t_{RD1} + t_{PDn}$ , or  $t_{PD1} + t_{RD1} + t_{SUD}$ , whichever is appropriate.

3. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual performance.

# Table 2-36 • A54SX72A Timing Characteristics (Continued)

|                    |                                                        | -3 Sp | beed* | -2 S | peed | -1 S | peed | Std. Speed |      | -F Speed |      |       |

|--------------------|--------------------------------------------------------|-------|-------|------|------|------|------|------------|------|----------|------|-------|

| Parameter          | Description                                            | Min.  | Max.  | Min. | Max. | Min. | Max. | Min.       | Max. | Min.     | Max. | Units |

| t <sub>QCKH</sub>  | Input Low to High (100% Load)<br>(Pad to R-cell Input) |       | 3.0   |      | 3.4  |      | 3.9  |            | 4.6  |          | 6.4  | ns    |

| t <sub>QCHKL</sub> | Input High to Low (100% Load)<br>(Pad to R-cell Input) |       | 2.9   |      | 3.4  |      | 3.8  |            | 4.5  |          | 6.3  | ns    |

| t <sub>QPWH</sub>  | Minimum Pulse Width High                               | 1.5   |       | 1.7  |      | 2.0  |      | 2.3        |      | 3.2      |      | ns    |

| t <sub>QPWL</sub>  | Minimum Pulse Width Low                                | 1.5   |       | 1.7  |      | 2.0  |      | 2.3        |      | 3.2      |      | ns    |

| t <sub>qcksw</sub> | Maximum Skew (Light Load)                              |       | 0.2   |      | 0.3  |      | 0.3  |            | 0.3  |          | 0.5  | ns    |

| t <sub>QCKSW</sub> | Maximum Skew (50% Load)                                |       | 0.4   |      | 0.5  |      | 0.5  |            | 0.6  |          | 0.9  | ns    |

| t <sub>QCKSW</sub> | Maximum Skew (100% Load)                               |       | 0.4   |      | 0.5  |      | 0.5  |            | 0.6  |          | 0.9  | ns    |

Note: \*All –3 speed grades have been discontinued.

#### Table 2-39 A54SX72A Timing Characteristics

# (Worst-Case Commercial Conditions $V_{CCA} = 2.25 \text{ V}$ , $V_{CCI} = 2.3 \text{ V}$ , $T_J = 70^{\circ}\text{C}$ )

|                      |                                         | -3 Sp | eed <sup>1</sup> | -2 S | peed  | -1 S | peed  | Std. 9 | 5peed | -F Speed |       |       |

|----------------------|-----------------------------------------|-------|------------------|------|-------|------|-------|--------|-------|----------|-------|-------|

| Parameter            | Description                             | Min.  | Max.             | Min. | Max.  | Min. | Max.  | Min.   | Max.  | Min.     | Max.  | Units |

| 2.5 V LVCM           | OS Output Module Timing <sup>2, 3</sup> |       |                  |      |       |      |       |        |       |          |       |       |

| t <sub>DLH</sub>     | Data-to-Pad Low to High                 |       | 3.9              |      | 4.5   |      | 5.1   |        | 6.0   |          | 8.4   | ns    |

| t <sub>DHL</sub>     | Data-to-Pad High to Low                 |       | 3.1              |      | 3.6   |      | 4.1   |        | 4.8   |          | 6.7   | ns    |

| t <sub>DHLS</sub>    | Data-to-Pad High to Low—low slew        |       | 12.7             |      | 14.6  |      | 16.5  |        | 19.4  |          | 27.2  | ns    |

| t <sub>ENZL</sub>    | Enable-to-Pad, Z to L                   |       | 2.4              |      | 2.8   |      | 3.2   |        | 3.7   |          | 5.2   | ns    |

| t <sub>ENZLS</sub>   | Data-to-Pad, Z to L—low slew            |       | 11.8             |      | 13.7  |      | 15.5  |        | 18.2  |          | 25.5  | ns    |

| t <sub>ENZH</sub>    | Enable-to-Pad, Z to H                   |       | 3.9              |      | 4.5   |      | 5.1   |        | 6.0   |          | 8.4   | ns    |

| t <sub>ENLZ</sub>    | Enable-to-Pad, L to Z                   |       | 2.1              |      | 2.5   |      | 2.8   |        | 3.3   |          | 4.7   | ns    |

| t <sub>ENHZ</sub>    | Enable-to-Pad, H to Z                   |       | 3.1              |      | 3.6   |      | 4.1   |        | 4.8   |          | 6.7   | ns    |

| $d_{\text{TLH}}^{4}$ | Delta Low to High                       |       | 0.031            |      | 0.037 |      | 0.043 |        | 0.051 |          | 0.071 | ns/pF |

| $d_{THL}^4$          | Delta High to Low                       |       | 0.017            |      | 0.017 |      | 0.023 |        | 0.023 |          | 0.037 | ns/pF |

| $d_{\text{THLS}}^4$  | Delta High to Low—low slew              |       | 0.057            |      | 0.06  |      | 0.071 |        | 0.086 |          | 0.117 | ns/pF |

### Note:

1. All –3 speed grades have been discontinued.

2. Delays based on 35 pF loading.

3. The equivalent IO Attribute settings for 2.5 V LVCMOS is 2.5 V LVTTL in the software.

4. To obtain the slew rate, substitute the appropriate Delta value, load capacitance, and the  $V_{CCI}$  value into the following equation: Slew Rate [V/ns] =  $(0.1 * V_{CCI} - 0.9 * V_{CCI})/(C_{load} * d_{T[LH|HL|HLS]})$ where  $C_{load}$  is the load capacitance driven by the I/O in pF

$d_{T[LH|HL|HLS]}$  is the worst case delta value from the datasheet in ns/pF.

| 176-P         | in TQFP              |

|---------------|----------------------|

| Pin<br>Number | A54SX32A<br>Function |

| 145           | I/O                  |

| 146           | I/O                  |

| 147           | I/O                  |

| 148           | I/O                  |

| 149           | I/O                  |

| 150           | I/O                  |

| 151           | I/O                  |

| 152           | CLKA                 |

| 153           | CLKB                 |

| 154           | NC                   |

| 155           | GND                  |

| 156           | V <sub>CCA</sub>     |

| 157           | PRA, I/O             |

| 158           | I/O                  |

| 159           | I/O                  |

| 160           | I/O                  |

| 161           | I/O                  |

| 162           | I/O                  |

| 163           | I/O                  |

| 164           | I/O                  |

| 165           | I/O                  |

| 166           | I/O                  |

| 167           | I/O                  |

| 168           | I/O                  |

| 169           | V <sub>CCI</sub>     |

| 170           | I/O                  |

| 171           | I/O                  |

| 172           | I/O                  |

| 173           | I/O                  |

| 174           | I/O                  |

| 175           | I/O                  |

| 176           | TCK, I/O             |

|               |                      |

# 329-Pin PBGA

|          | 1          | 2        | 3 | 4        | 5      | 6 | 7 | 8        | 9 | 10       | 11         | 12         | 13 | 14         | 15       | 16 | 17       | 18 | 19     | 20         | 21       | 22         | 23           |

|----------|------------|----------|---|----------|--------|---|---|----------|---|----------|------------|------------|----|------------|----------|----|----------|----|--------|------------|----------|------------|--------------|

| Α        | 0          | 0        | 0 | 0        | 0      | 0 | 0 | 0        | 0 | 0        | 0          | 0          | 0  | 0          | 0        | 0  | 0        | 0  | 0      | 0          | 0        | 0          | 0            |

| в        | 0          | 0        | 0 | 0        | 0      | 0 | 0 | 0        | 0 | 0        | 0          | 0          | 0  | 0          | 0        | 0  | 0        | 0  | 0      | 0          | 0        | 0          | 0            |

| C        | 0          | 0        | 0 | 0        | 0      | 0 | 0 | 0        | 0 | ~        | ~          | ~          | 0  | ~          | 0        | Õ  | 0        | 0  | 0      | 0          | 0        | ~          | 0            |

| D        | 0          | 0        | 0 | 0        | 0      | 0 | 0 | 0        | 0 | 0        | 0          | 0          | 0  | $\bigcirc$ | 0        | 0  | 0        | 0  | 0      | 0          | ~        | ~          | 0            |

| E<br>F   | 0          | <u> </u> | 0 | <u> </u> |        |   |   |          |   |          |            |            |    |            |          |    |          |    |        | 0          | <u> </u> | 0          | 0            |

| G        | 0          | <u> </u> | 0 | $\sim$   |        |   |   |          |   |          |            |            |    |            |          |    |          |    |        | 0          | $\sim$   | ž          | 0            |

| н        | ŏ          | -        | õ | -        |        |   |   |          |   |          |            |            |    |            |          |    |          |    |        | õ          | · ·      | õ          | 0            |

| ſ        | Ō          | Õ        | Õ | Ō        |        |   |   |          |   |          |            |            |    |            |          |    |          |    |        | Õ          | Õ        | Õ          | Õ            |

| к        | 0          | Ο        | Ο | Ο        |        |   |   |          |   | Ο        | Ο          | Ο          | 0  | Ο          |          |    |          |    |        | Ο          | Ο        | Ο          | 0            |

| L        | 0          | 0        | 0 | ~        |        |   |   |          |   | -        | -          | -          | 0  | Ξ          |          |    |          |    |        | 0          | 0        | 0          | 0            |

| M<br>N   | 0          |          | ~ | 0        |        |   |   |          |   | <u> </u> | $\tilde{}$ | $\tilde{}$ | O  | ~          |          |    |          |    |        | 0          | ~        | ~          | 0            |

| P        | 0          | 0        | 0 | 0        |        |   |   |          |   | -        | -          | -          |    | -          |          |    |          |    |        | $\bigcirc$ | $\sim$   | $\tilde{}$ | $\mathbf{O}$ |

| R        | -          | -        | õ | <u> </u> |        |   |   |          |   | 0        | 0          | $\cup$     |    | $\cup$     |          |    |          |    |        | õ          | -        | õ          | Ŭ            |

| т        | Õ          | Õ        | Õ | Õ        |        |   |   |          |   |          |            |            |    |            |          |    |          |    |        | Õ          | õ        | õ          | Õ            |

| υ        | 0          | 0        | 0 | 0        |        |   |   |          |   |          |            |            |    |            |          |    |          |    |        | 0          | Ο        | 0          | 0            |

| V        | 0          | Ο        | Ο | 0        |        |   |   |          |   |          |            |            |    |            |          |    |          |    |        | Ο          | Ο        | Ο          | 0            |

| W        | -          | 0        | - | -        | _      | _ | _ | _        | _ | _        | _          | _          | _  | _          | _        | _  | _        | _  | _      | 0          | $\sim$   | 0          | $\sim$       |

| Y        | 0          | 0        | 0 | 0        | $\sim$ | ~ | - | _        | - | -        | -          | -          | -  | _          | _        | _  | -        | -  | $\sim$ | 0          | -        | ~          | ~            |

| AA<br>AB | 0          | 0        | 0 | 0        | 0      | 0 | - | <u> </u> | - | -        | -          | -          |    | -          | <u> </u> | -  | <u> </u> | -  | 0      | 0          |          | 0          | 0            |

| AC       | 0          | 0        |   | ~        | -      | - | - | -        | - | -        | -          | -          | -  | -          | -        | -  | -        | -  | -      | 0          | -        | -          | -            |

| L        | $\searrow$ | _        | _ | _        | _      | _ | _ | _        | _ | _        |            |            |    | $\sim$     | _        | _  | _        | _  | _      | _          |          | $\sim$     | $\leq$       |

Figure 3-5 • 329-Pin PBGA (Top View)

## Note

For Package Manufacturing and Environmental information, visit Resource center at http://www.actel.com/products/rescenter/package/index.html.

| 329-Pin PBGA  |                      | 329-Pin PBGA  |                      | 329-Pin PBGA  |                      | 329-Pi        | 329-Pin PBGA         |  |

|---------------|----------------------|---------------|----------------------|---------------|----------------------|---------------|----------------------|--|

| Pin<br>Number | A54SX32A<br>Function | Pin<br>Number | A54SX32A<br>Function | Pin<br>Number | A54SX32A<br>Function | Pin<br>Number | A54SX32A<br>Function |  |

| A1            | GND                  | AA15          | I/O                  | AC6           | I/O                  | B20           | I/O                  |  |

| A2            | GND                  | AA16          | I/O                  | AC7           | I/O                  | B21           | I/O                  |  |

| A3            | V <sub>CCI</sub>     | AA17          | I/O                  | AC8           | I/O                  | B22           | GND                  |  |

| A4            | NC                   | AA18          | I/O                  | AC9           | V <sub>CCI</sub>     | B23           | V <sub>CCI</sub>     |  |

| A5            | I/O                  | AA19          | I/O                  | AC10          | I/O                  | C1            | NC                   |  |

| A6            | I/O                  | AA20          | TDO, I/O             | AC11          | I/O                  | C2            | TDI, I/O             |  |

| A7            | V <sub>CCI</sub>     | AA21          | V <sub>CCI</sub>     | AC12          | I/O                  | C3            | GND                  |  |

| A8            | NC                   | AA22          | I/O                  | AC13          | I/O                  | C4            | I/O                  |  |

| A9            | I/O                  | AA23          | V <sub>CCI</sub>     | AC14          | I/O                  | C5            | I/O                  |  |

| A10           | I/O                  | AB1           | I/O                  | AC15          | NC                   | C6            | I/O                  |  |

| A11           | I/O                  | AB2           | GND                  | AC16          | I/O                  | С7            | I/O                  |  |

| A12           | I/O                  | AB3           | I/O                  | AC17          | I/O                  | С8            | I/O                  |  |

| A13           | CLKB                 | AB4           | I/O                  | AC18          | I/O                  | С9            | I/O                  |  |

| A14           | I/O                  | AB5           | I/O                  | AC19          | I/O                  | C10           | I/O                  |  |

| A15           | I/O                  | AB6           | I/O                  | AC20          | I/O                  | C11           | I/O                  |  |

| A16           | I/O                  | AB7           | I/O                  | AC21          | NC                   | C12           | I/O                  |  |

| A17           | I/O                  | AB8           | I/O                  | AC22          | V <sub>CCI</sub>     | C13           | I/O                  |  |

| A18           | I/O                  | AB9           | I/O                  | AC23          | GND                  | C14           | I/O                  |  |

| A19           | I/O                  | AB10          | I/O                  | B1            | V <sub>CCI</sub>     | C15           | I/O                  |  |

| A20           | I/O                  | AB11          | PRB, I/O             | B2            | GND                  | C16           | I/O                  |  |

| A21           | NC                   | AB12          | I/O                  | B3            | I/O                  | C17           | I/O                  |  |

| A22           | V <sub>CCI</sub>     | AB13          | HCLK                 | B4            | I/O                  | C18           | I/O                  |  |

| A23           | GND                  | AB14          | I/O                  | B5            | I/O                  | C19           | I/O                  |  |

| AA1           | V <sub>CCI</sub>     | AB15          | I/O                  | B6            | I/O                  | C20           | I/O                  |  |

| AA2           | I/O                  | AB16          | I/O                  | B7            | I/O                  | C21           | V <sub>CCI</sub>     |  |

| AA3           | GND                  | AB17          | I/O                  | B8            | I/O                  | C22           | GND                  |  |

| AA4           | I/O                  | AB18          | I/O                  | B9            | I/O                  | C23           | NC                   |  |

| AA5           | I/O                  | AB19          | I/O                  | B10           | I/O                  | D1            | I/O                  |  |

| AA6           | I/O                  | AB20          | I/O                  | B11           | I/O                  | D2            | I/O                  |  |

| AA7           | I/O                  | AB21          | I/O                  | B12           | PRA, I/O             | D3            | I/O                  |  |

| AA8           | I/O                  | AB22          | GND                  | B13           | CLKA                 | D4            | TCK, I/O             |  |

| AA9           | I/O                  | AB23          | I/O                  | B14           | I/O                  | D5            | I/O                  |  |

| AA10          | I/O                  | AC1           | GND                  | B15           | I/O                  | D6            | I/O                  |  |

| AA11          | I/O                  | AC2           | V <sub>CCI</sub>     | B16           | I/O                  | D7            | I/O                  |  |

| AA12          | I/O                  | AC3           | NC                   | B17           | I/O                  | D8            | I/O                  |  |

| AA13          | I/O                  | AC4           | I/O                  | B18           | I/O                  | D9            | I/O                  |  |

| AA14          | I/O                  | AC5           | I/O                  | B19           | I/O                  | D10           | I/O                  |  |

| Actel <sup>®</sup> |  |  |  |  |  |  |  |

|--------------------|--|--|--|--|--|--|--|

| SX-A Family FPGAs  |  |  |  |  |  |  |  |

|               | 484-Pin FBG          | Α                    |

|---------------|----------------------|----------------------|

| Pin<br>Number | A54SX32A<br>Function | A54SX72A<br>Function |

| T3            | I/O                  | I/O                  |

| T4            | I/O                  | I/O                  |

| T5            | I/O                  | I/O                  |

| T10           | GND                  | GND                  |

| T11           | GND                  | GND                  |

| T12           | GND                  | GND                  |

| T13           | GND                  | GND                  |

| T14           | GND                  | GND                  |

| T15           | GND                  | GND                  |

| T16           | GND                  | GND                  |

| T17           | GND                  | GND                  |

| T22           | I/O                  | I/O                  |

| T23           | I/O                  | I/O                  |

| T24           | I/O                  | I/O                  |

| T25           | NC*                  | I/O                  |

| T26           | NC*                  | I/O                  |

| U1            | I/O                  | I/O                  |

| U2            | V <sub>CCI</sub>     | V <sub>CCI</sub>     |

| U3            | I/O                  | I/O                  |

| U4            | I/O                  | I/O                  |

| U5            | I/O                  | I/O                  |

| U10           | GND                  | GND                  |

| U11           | GND                  | GND                  |

| U12           | GND                  | GND                  |

| U13           | GND                  | GND                  |

| U14           | GND                  | GND                  |

| U15           | GND                  | GND                  |

| U16           | GND                  | GND                  |

| U17           | GND                  | GND                  |

| U22           | I/O                  | I/O                  |

| U23           | I/O                  | I/O                  |

| U24           | I/O                  | I/O                  |

| U25           | V <sub>CCI</sub>     | V <sub>CCI</sub>     |

| U26           | I/O                  | I/O                  |

| V1            | NC*                  | I/O                  |

| 484-Pin FBGA  |                      |                      |  |  |  |

|---------------|----------------------|----------------------|--|--|--|

| Pin<br>Number | A54SX32A<br>Function | A54SX72A<br>Function |  |  |  |

| V2            | NC*                  | I/O                  |  |  |  |

| V3            | I/O                  | I/O                  |  |  |  |

| V4            | I/O                  | I/O                  |  |  |  |

| V5            | I/O                  | I/O                  |  |  |  |

| V22           | V <sub>CCA</sub>     | V <sub>CCA</sub>     |  |  |  |

| V23           | I/O                  | I/O                  |  |  |  |

| V24           | I/O                  | I/O                  |  |  |  |

| V25           | NC*                  | I/O                  |  |  |  |

| V26           | NC*                  | I/O                  |  |  |  |

| W1            | I/O                  | I/O                  |  |  |  |

| W2            | I/O                  | I/O                  |  |  |  |

| W3            | I/O                  | I/O                  |  |  |  |

| W4            | I/O                  | I/O                  |  |  |  |

| W5            | I/O                  | I/O                  |  |  |  |

| W22           | I/O                  | I/O                  |  |  |  |

| W23           | V <sub>CCA</sub>     | V <sub>CCA</sub>     |  |  |  |

| W24           | I/O                  | I/O                  |  |  |  |

| W25           | NC*                  | I/O                  |  |  |  |

| W26           | NC*                  | I/O                  |  |  |  |

| Y1            | NC*                  | I/O                  |  |  |  |

| Y2            | NC*                  | I/O                  |  |  |  |

| Y3            | I/O                  | I/O                  |  |  |  |

| Y4            | I/O                  | I/O                  |  |  |  |

| Y5            | NC*                  | I/O                  |  |  |  |

| Y22           | I/O                  | I/O                  |  |  |  |

| Y23           | I/O                  | I/O                  |  |  |  |

| Y24           | V <sub>CCI</sub>     | V <sub>CCI</sub>     |  |  |  |

| Y25           | I/O                  | I/O                  |  |  |  |

| Y26           | I/O                  | I/O                  |  |  |  |

*Note:* \*These pins must be left floating on the A54SX32A device.

# **Datasheet Information**

# List of Changes

The following table lists critical changes that were made in the current version of the document.

| <b>Previous Version</b> | Changes in Current Version (v5.3)                                                                             | Page  |

|-------------------------|---------------------------------------------------------------------------------------------------------------|-------|

| v5.2                    | –3 speed grades have been discontinued.                                                                       | N/A   |

| (June 2006)             | The "SX-A Timing Model" was updated with –2 data.                                                             | 2-14  |

| v5.1                    | RoHS information was added to the "Ordering Information".                                                     | ii    |

| February 2005           | The "Programming" section was updated.                                                                        | 1-13  |

| v5.0                    | Revised Table 1 and the timing data to reflect the phase out of the $-3$ speed grade for the A54SX08A device. |       |

|                         | The "Thermal Characteristics" section was updated.                                                            | 2-11  |

|                         | The "176-Pin TQFP" was updated to add pins 81 to 90.                                                          |       |

|                         | The "484-Pin FBGA" was updated to add pins R4 to Y26                                                          | 3-26  |

| v4.0                    | The "Temperature Grade Offering" is new.                                                                      | 1-iii |

|                         | The "Speed Grade and Temperature Grade Matrix" is new.                                                        | 1-iii |

|                         | "SX-A Family Architecture" was updated.                                                                       | 1-1   |

|                         | "Clock Resources" was updated.                                                                                | 1-5   |

|                         | "User Security" was updated.                                                                                  | 1-7   |

|                         | "Power-Up/Down and Hot Swapping" was updated.                                                                 | 1-7   |

|                         | "Dedicated Mode" is new                                                                                       | 1-9   |

|                         | Table 1-5 is new.                                                                                             | 1-9   |

|                         | "JTAG Instructions" is new                                                                                    | 1-10  |

|                         | "Design Considerations" was updated.                                                                          | 1-12  |

|                         | The "Programming" section is new.                                                                             | 1-13  |

|                         | "Design Environment" was updated.                                                                             | 1-13  |

|                         | "Pin Description" was updated.                                                                                | 1-15  |

|                         | Table 2-1 was updated.                                                                                        | 2-1   |

|                         | Table 2-2 was updated.                                                                                        | 2-1   |

|                         | Table 2-3 is new.                                                                                             | 2-1   |

|                         | Table 2-4 is new.                                                                                             | 2-1   |

|                         | Table 2-5 was updated.                                                                                        | 2-2   |

|                         | Table 2-6 was updated.                                                                                        | 2-2   |

|                         | "Power Dissipation" is new.                                                                                   | 2-8   |

|                         | Table 2-11 was updated.                                                                                       | 2-9   |

Actel and the Actel logo are registered trademarks of Actel Corporation. All other trademarks are the property of their owners.

www.actel.com

#### **Actel Corporation**

#### Actel Europe Ltd.

2061 Stierlin Court Mountain View, CA 94043-4655 USA **Phone** 650.318.4200 **Fax** 650.318.4600 River Court, Meadows Business Park Station Approach, Blackwater Camberley, Surrey GU17 9AB United Kingdom Phone +44 (0) 1276 609 300 Fax +44 (0) 1276 607 540

### Actel Japan

EXOS Ebisu Bldg. 4F 1-24-14 Ebisu Shibuya-ku Tokyo 150 Japan Phone +81.03.3445.7671 Fax +81.03.3445.7668 www.jp.actel.com

#### Actel Hong Kong

Suite 2114, Two Pacific Place 88 Queensway, Admiralty Hong Kong Phone +852 2185 6460 Fax +852 2185 6488 www.actel.com.cn