Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |  |

|----------------------------|------------------------------------------------------------------------|--|

| Product Status             | Active                                                                 |  |

| Core Processor             | STM8                                                                   |  |

| Core Size                  | 8-Bit                                                                  |  |

| Speed                      | 16MHz                                                                  |  |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART             |  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                  |  |

| Number of I/O              | 5                                                                      |  |

| Program Memory Size        | 8KB (8K x 8)                                                           |  |

| Program Memory Type        | FLASH                                                                  |  |

| EEPROM Size                | 128 x 8                                                                |  |

| RAM Size                   | 1K x 8                                                                 |  |

| Voltage - Supply (Vcc/Vdd) | 2.95V ~ 5.5V                                                           |  |

| Data Converters            | A/D 3x10b                                                              |  |

| Oscillator Type            | Internal                                                               |  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |  |

| Mounting Type              | Surface Mount                                                          |  |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                          |  |

| Supplier Device Package    | 8-SOIC                                                                 |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8s001j3m3tr |  |

Contents STM8S001J3

| 13 | Revis | sion his | tory8                      | 4  |

|----|-------|----------|----------------------------|----|

|    | 12.3  | Prograi  | mming tools                | 3  |

|    |       | 12.2.2   | C and assembly toolchains8 | 33 |

|    |       | 12.2.1   | STM8 toolset8              | 33 |

|    | 12.2  | Softwa   | re tools                   | 3  |

|    |       |          |                            |    |

STM8S001J3 List of figures

# **List of figures**

| Figure 1.  | STM8S001J3 block diagram                                                                          | 10 |

|------------|---------------------------------------------------------------------------------------------------|----|

| Figure 2.  | Flash memory organization                                                                         | 13 |

| Figure 3.  | STM8S001J3 SO8N pinout                                                                            | 21 |

| Figure 4.  | Memory map                                                                                        | 25 |

| Figure 5.  | Pin loading conditions                                                                            | 40 |

| Figure 6.  | Pin input voltage                                                                                 | 41 |

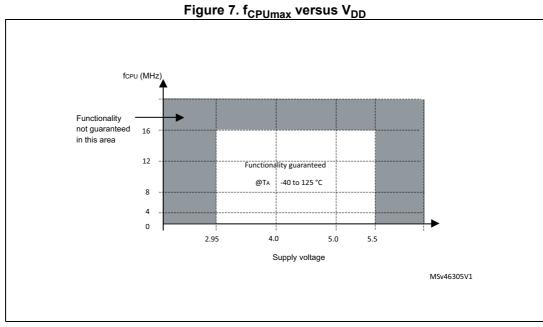

| Figure 7.  | f <sub>CPUmax</sub> versus V <sub>DD</sub>                                                        | 43 |

| Figure 8.  | External capacitor C <sub>EXT</sub>                                                               | 45 |

| Figure 9.  | Typ. I <sub>DD(RUN)</sub> vs V <sub>DD</sub> , HSE user external clock, f <sub>CPU</sub> = 16 MHz | 51 |

| Figure 10. | Typ. I <sub>DD(RUN)</sub> vs f <sub>CPU</sub> , HSE user external clock, V <sub>DD</sub> = 5 V    | 51 |

| Figure 11. | Typ. I <sub>DD(RUN)</sub> vs V <sub>DD</sub> , HSI RC osc, f <sub>CPU</sub> = 16 MHz              | 52 |

| Figure 12. | Typ. I <sub>DD(WFI)</sub> vs. V <sub>DD</sub> HSE user external clock, f <sub>CPU</sub> = 16 MHz  | 52 |

| Figure 13. | Typ. I <sub>DD(WFI)</sub> vs. f <sub>CPU</sub> , HSE user external clock, V <sub>DD</sub> = 5 V   | 53 |

| Figure 14. | Typ. $I_{DD(WFI)}$ vs $V_{DD}$ , HSI RC osc, $f_{CPU} = 16$ MHz                                   | 53 |

| Figure 15. | HSE external clock source                                                                         |    |

| Figure 16. | Typical HSI frequency variation vs V <sub>DD</sub> at 4 temperatures                              | 55 |

| Figure 17. | Typical LSI frequency variation vs V <sub>DD</sub> @ 4 temperatures                               | 56 |

| Figure 18. | Typical V <sub>IL</sub> and V <sub>IH</sub> vs V <sub>DD</sub> @ 4 temperatures                   | 59 |

| Figure 19. | Typical pull-up resistance vs V <sub>DD</sub> @ 4 temperatures                                    | 59 |

| Figure 20. | Typical pull-up current vs V <sub>DD</sub> @ 4 temperatures                                       |    |

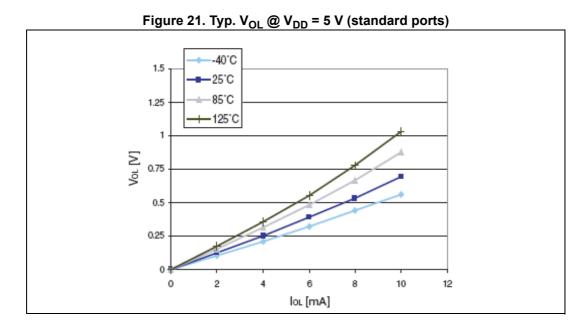

| Figure 21. | Typ. V <sub>OL</sub> @ V <sub>DD</sub> = 5 V (standard ports)                                     |    |

| Figure 22. | Typ. V <sub>OL</sub> @ V <sub>DD</sub> = 3.3 V (standard ports)                                   |    |

| Figure 23. | Typ. V <sub>OL</sub> @ V <sub>DD</sub> = 5 V (true open drain ports)                              |    |

| Figure 24. | Typ. V <sub>OL</sub> @ V <sub>DD</sub> = 3.3 V (true open drain ports)                            |    |

| Figure 25. | Typ. $V_{OL} @ V_{DD} = 5 V$ (high sink ports)                                                    |    |

| Figure 26. | Typ. $V_{OL}$ @ $V_{DD}$ = 3.3 V (high sink ports)                                                |    |

| Figure 27. | Typ. $V_{DD}$ - $V_{OH}$ @ $V_{DD}$ = 5 V (standard ports)                                        |    |

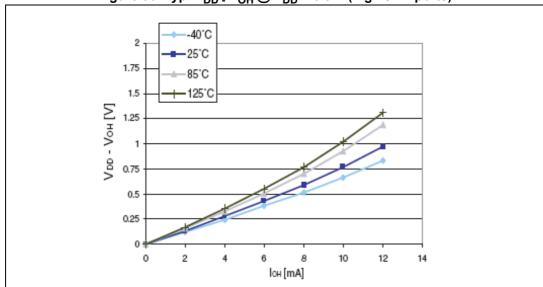

| Figure 28. | Typ. $V_{DD}$ - $V_{OH}$ @ $V_{DD}$ = 3.3 V (standard ports)                                      |    |

| Figure 29. | Typ. $V_{DD}$ - $V_{OH}$ @ $V_{DD}$ = 5 V (high sink ports)                                       |    |

| Figure 30. | Typ. $V_{DD}$ - $V_{OH}$ @ $V_{DD}$ = 3.3 V (high sink ports)                                     | 66 |

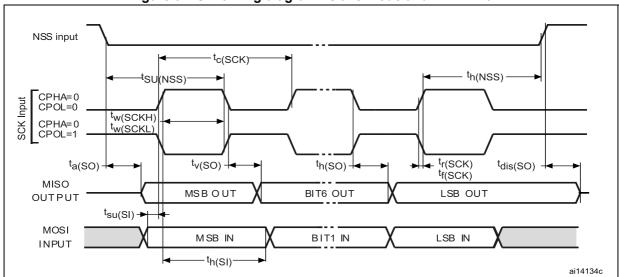

| Figure 31. | SPI timing diagram - slave mode and CPHA = 0                                                      | 67 |

| Figure 32. | SPI timing diagram - slave mode and CPHA = 1 <sup>(1)</sup>                                       | 68 |

| Figure 33. | SPI timing diagram - master mode <sup>(1)</sup>                                                   |    |

| Figure 34. | Typical application with I2C bus and timing diagram                                               |    |

| Figure 35. | ADC accuracy characteristics                                                                      |    |

| Figure 36. | Typical application with ADC                                                                      |    |

| Figure 37. | SO8N – 8-lead, 4.9 x 6 mm, plastic small outline, 150 mils body width, package outline .          | 77 |

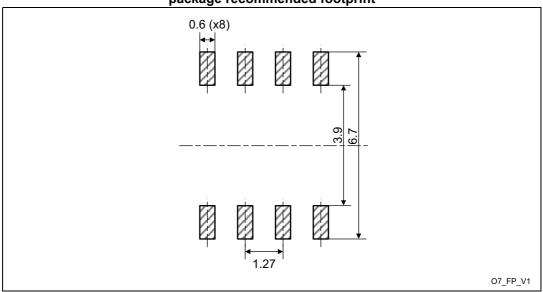

| Figure 38. | SO8N – 8-lead 4.9 x 6 mm, plastic small outline, 150 mils body width,                             |    |

|            | package recommended footprint                                                                     | 78 |

| Figure 39. | SO8N – 8-lead 4.9 x 6 mm, plastic small outline, 150 mils body width,                             |    |

|            | marking example                                                                                   | 79 |

| Figure 40. | STM8S001J3 ordering information scheme(')                                                         | 81 |

DS12129 Rev 3 7/85

Introduction STM8S001J3

# 1 Introduction

This datasheet contains the description of the STM8S001J3 features, pinout, electrical characteristics, mechanical data and ordering information.

For complete information on the STM8S microcontroller memory, registers and peripherals, please refer to the STM8S and STM8A microcontroller families reference manual (RM0016).

- For information on programming, erasing and protection of the internal Flash memory please refer to the PM0051 (How to program STM8S and STM8A Flash program memory and data EEPROM).

- For information on the debug and SWIM (single wire interface module) refer to the STM8 SWIM communication protocol and debug module user manual (UM0470).

- For information on the STM8 core, please refer to the STM8 CPU programming manual (PM0044).

Functional overview STM8S001J3

### 4.6 Power management

For efficient power management, the application can be put in one of four different low-power modes. You can configure each mode to obtain the best compromise between the lowest power consumption, the fastest start-up time and available wakeup sources.

- **Wait mode**: In this mode, the CPU is stopped, but peripherals are kept running. The wakeup is performed by an internal or external interrupt or reset.

- Active halt mode with regulator on: In this mode, the CPU and peripheral clocks are stopped. An internal wakeup is generated at programmable intervals by the auto wake up unit (AWU). The main voltage regulator is kept powered on, so current consumption is higher than in active halt mode with regulator off, but the wakeup time is faster.

Wakeup is triggered by the internal AWU interrupt, external interrupt or reset.

- Active halt mode with regulator off: This mode is the same as active halt with regulator on, except that the main voltage regulator is powered off, so the wake up time is slower.

- Halt mode: In this mode the microcontroller uses the least power. The CPU and

peripheral clocks are stopped, the main voltage regulator is powered off. Wakeup is

triggered by external event or reset.

# 4.7 Watchdog timers

The watchdog system is based on two independent timers providing maximum security to the applications.

Activation of the watchdog timers is controlled by option bytes or by software. Once activated, the watchdogs cannot be disabled by the user program without performing a reset.

#### Window watchdog timer

The window watchdog is used to detect the occurrence of a software fault, usually generated by external interferences or by unexpected logical conditions, which cause the application program to abandon its normal sequence.

The window function can be used to trim the watchdog behavior to match the application perfectly.

The application software must refresh the counter before time-out and during a limited time window.

A reset is generated in two situations:

- Timeout: at 16 MHz CPU clock the time-out period can be adjusted between 75 μs up to 64 ms.

- 2. Refresh out of window: the down-counter is refreshed before its value is lower than the one stored in the window register.

Functional overview STM8S001J3

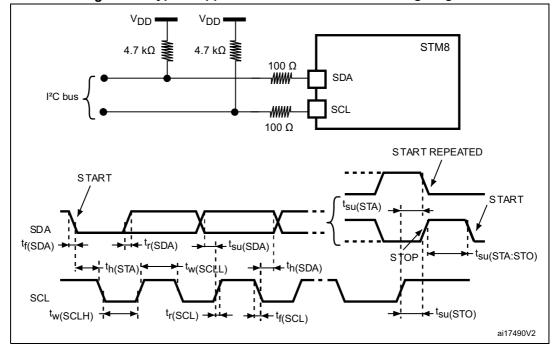

#### 4.13.3 I2C

20/85

- I2C master features

- Clock generation

- Start and stop generation

- I2C slave features

- Programmable I2C address detection

- Stop bit detection

- Generation and detection of 7-bit/10-bit addressing and general call

- Supports different communication speeds

- Standard speed (up to 100 kHz)

- Fast speed (up to 400 kHz)

*Table 6* lists the boundary addresses for each memory size. The top of the stack is at the RAM end address in each case.

Table 6. Flash, Data EEPROM and RAM boundary addresses

| Memory area          | Size (byte) | Start address | End address |

|----------------------|-------------|---------------|-------------|

| Flash program memory | 8 K         | 0x00 8000     | 0x00 9FFF   |

| RAM                  | 1 K         | 0x00 0000     | 0x00 03FF   |

| Data EEPROM          | 128         | 0x00 4000     | 0x00 407F   |

# 6.2 Register map

## 6.2.1 I/O port hardware register map

Table 7. I/O port hardware register map

| Address   | Block  | Register label | Register name                     | Reset<br>status     |

|-----------|--------|----------------|-----------------------------------|---------------------|

| 0x00 5000 |        | PA_ODR         | Port A data output latch register | 0x00                |

| 0x00 5001 |        | PA_IDR         | Port A input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5002 | Port A | PA_DDR         | Port A data direction register    | 0x00                |

| 0x00 5003 |        | PA_CR1         | Port A control register 1         | 0x00                |

| 0x00 5004 |        | PA_CR2         | Port A control register 2         | 0x00                |

| 0x00 5005 |        | PB_ODR         | Port B data output latch register | 0x00                |

| 0x00 5006 |        | PB_IDR         | Port B input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5007 | Port B | PB_DDR         | Port B data direction register    | 0x00                |

| 0x00 5008 |        | PB_CR1         | Port B control register 1         | 0x00                |

| 0x00 5009 |        | PB_CR2         | Port B control register 2         | 0x00                |

| 0x00 500A |        | PC_ODR         | Port C data output latch register | 0x00                |

| 0x00 500B |        | PB_IDR         | Port C input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 500C | Port C | PC_DDR         | Port C data direction register    | 0x00                |

| 0x00 500D |        | PC_CR1         | Port C control register 1         | 0x00                |

| 0x00 500E |        | PC_CR2         | Port C control register 2         | 0x00                |

| 0x00 500F |        | PD_ODR         | Port D data output latch register | 0x00                |

| 0x00 5010 |        | PD_IDR         | Port D input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5011 | Port D | PD_DDR         | Port D data direction register    | 0x00                |

| 0x00 5012 |        | PD_CR1         | Port D control register 1         | 0x02                |

| 0x00 5013 |        | PD_CR2         | Port D control register 2         | 0x00                |

Table 8. General hardware register map (continued)

| Address                   | Block | Register label | Register name                                   | Reset status |

|---------------------------|-------|----------------|-------------------------------------------------|--------------|

| 0x00 5300                 |       | TIM2_CR1       | TIM2 control register 1                         | 0x00         |

| 0x00 5301                 |       |                | Reserved                                        |              |

| 0x00 5302                 |       |                | Reserved                                        |              |

| 0x00 5303                 | 1     | TIM2_IER       | TIM2 interrupt enable register                  | 0x00         |

| 0x00 5304                 |       | TIM2_SR1       | TIM2 status register 1                          | 0x00         |

| 0x00 5305                 | 1     | TIM2_SR2       | TIM2 status register 2                          | 0x00         |

| 0x00 5306                 | 1     | TIM2_EGR       | TIM2_CCMR1 TIM2 capture/compare mode register 1 |              |

| 0x00 5307                 | 1     |                |                                                 | 0x00         |

| 0x00 5308                 | 1     | TIM2_CCMR2     | TIM2_CCMR2 TIM2 capture/compare mode register 2 |              |

| 0x00 5309                 | 1     | TIM2_CCMR3     |                                                 |              |

| 0x00 530A                 | 1     | TIM2_CCER1     | TIM2 capture/compare enable register 1          | 0x00         |

| 0x00 530B                 | TIM2  | TIM2_CCER2     | TIM2 capture/compare enable register 2          | 0x00         |

| 0x00 530C                 |       | TIM2_CNTRH     |                                                 |              |

| 0x00 530D                 | 1     | TIM2_CNTRL     | TIM2_CNTRL TIM2 counter low                     |              |

| 0x00 530E                 | 1     | TIM2_PSCR      | TIM2_PSCR TIM2 prescaler register               |              |

| 0x00 530F                 | 1     | TIM2_ARRH      |                                                 |              |

| 0x00 5310                 | 1     | TIM2_ARRL      |                                                 |              |

| 0x00 5311                 | 1     | TIM2_CCR1H     | TIM2_CCR1H TIM2 capture/compare register 1 high |              |

| 0x00 5312                 | 1     | TIM2_CCR1L     | TIM2_CCR1H TIM2 capture/compare register 1 high |              |

| 0x00 5313                 | 1     | TIM2_CCR2H     | TIM2_CCR1L TIM2 capture/compare register 1 low  |              |

| 0x00 5314                 | 1     | TIM2_CCR2L     | TIM2 capture/compare register 2 low             | 0x00         |

| 0x00 5315                 | 1     | TIM2_CCR3H     | TIM2 capture/compare register 3 high            | 0x00         |

| 0x00 5316                 | 1     | TIM2_CCR3L     | TIM2 capture/compare register 3 low             | 0x00         |

| 0x00 5317 to<br>0x00 533F |       |                | Reserved area (43 byte)                         |              |

| 0x00 5340                 |       | TIM4_CR1       | TIM4 control register 1                         | 0x00         |

| 0x00 5341                 | 1     |                | Reserved                                        |              |

| 0x00 5342                 |       |                | Reserved                                        |              |

| 0x00 5343                 |       | TIM4_IER       | TIM4 interrupt enable register                  | 0x00         |

| 0x00 5344                 | TIM4  | TIM4_SR        |                                                 |              |

| 0x00 5345                 | 1     | TIM4_EGR       | <u> </u>                                        |              |

| 0x00 5346                 | 1     | TIM4_CNTR      | TIM4_EGR TIM4 event generation register         |              |

| 0x00 5347                 | 1     | TIM4_PSCR      | TIM4 prescaler register                         | 0x00         |

| 0x00 5348                 | 1     | TIM4_ARR       | TIM4 auto-reload register                       | 0xFF         |

#### Interrupt vector mapping 7

Table 10. Interrupt mapping

| IRQ<br>no. | Source<br>block | Description                                      | Wakeup from<br>Halt mode | Wakeup from<br>Active-halt mode | Vector address            |

|------------|-----------------|--------------------------------------------------|--------------------------|---------------------------------|---------------------------|

| -          | RESET           | Reset                                            | Yes                      | Yes                             | 0x00 8000                 |

| -          | TRAP            | Software interrupt                               | -                        | -                               | 0x00 8004                 |

| 0          | TLI             | External top level interrupt                     | -                        | -                               | 0x00 8008                 |

| 1          | AWU             | Auto wake up from halt                           | -                        | Yes                             | 0x00 800C                 |

| 2          | CLK             | Clock controller                                 | -                        | -                               | 0x00 8010                 |

| 3          | EXTI0           | Port A external interrupts                       | Yes <sup>(1)</sup>       | Yes <sup>(1)</sup>              | 0x00 8014                 |

| 4          | EXTI1           | Port B external interrupts                       | Yes                      | Yes                             | 0x00 8018                 |

| 5          | EXTI2           | Port C external interrupts                       | Yes                      | Yes                             | 0x00 801C                 |

| 6          | EXTI3           | Port D external interrupts                       | Yes                      | Yes                             | 0x00 8020                 |

| 7          | EXTI4           | Port E external interrupts                       | Yes                      | Yes                             | 0x00 8024                 |

| 8          | -               | Rese                                             | erved                    |                                 | 0x00 8028                 |

| 9          | -               | Rese                                             | erved                    |                                 | 0x00 802C                 |

| 10         | SPI             | End of transfer                                  | Yes                      | Yes                             | 0x00 8030                 |

| 11         | TIM1            | TIM1 update/overflow/underflow/trigger/break     | -                        | -                               | 0x00 8034                 |

| 12         | TIM1            | TIM1 capture/compare                             | -                        | -                               | 0x00 8038                 |

| 13         | TIM2            | TIM2 update /overflow                            | -                        | -                               | 0x00 803C                 |

| 14         | TIM2            | TIM2 capture/compare                             | -                        | -                               | 0x00 8040                 |

| 15         | -               | Rese                                             | erved                    |                                 | 0x00 8044                 |

| 16         | -               | Rese                                             | erved                    |                                 | 0x00 8048                 |

| 17         | UART1           | Tx complete                                      | -                        | -                               | 0x00 804C                 |

| 18         | UART1           | Receive register DATA FULL                       | -                        | -                               | 0x00 8050                 |

| 19         | I2C             | I2C interrupt                                    | Yes                      | Yes                             | 0x00 8054                 |

| 20         | -               | Rese                                             | erved                    |                                 | 0x00 8058                 |

| 21         | -               | Rese                                             | erved                    |                                 | 0x00 805C                 |

| 22         | ADC1            | ADC1 end of conversion/analog watchdog interrupt | -                        | -                               | 0x00 8060                 |

| 23         | TIM4            | TIM4 update/overflow                             | -                        | -                               | 0x00 8064                 |

| 24         | Flash           | EOP/WR_PG_DIS                                    | -                        | -                               | 0x00 8068                 |

|            |                 | Reserved                                         |                          |                                 | 0x00 806C to<br>0x00 807C |

<sup>1.</sup> Except PA1

Table 15. Current characteristics

| Symbol                             | Ratings                                                                 | Max. <sup>(1)</sup> | Unit |

|------------------------------------|-------------------------------------------------------------------------|---------------------|------|

| I <sub>VDD</sub>                   | Total current into V <sub>DD</sub> power lines (source) <sup>(2)</sup>  | 100                 |      |

| I <sub>VSS</sub>                   | Total current out of V <sub>SS</sub> ground lines (sink) <sup>(2)</sup> | 80                  |      |

|                                    | Output current sunk by any I/O and control pin                          | 20                  |      |

| I <sub>IO</sub>                    | Output current source by any I/Os and control pin                       | -20                 | mA   |

| (3)(4)                             | Injected current on OSCIN pin                                           | ±4                  |      |

| I <sub>INJ(PIN)</sub> (3)(4)       | Injected current on any other pin <sup>(5)</sup>                        | ±4                  |      |

| $\Sigma I_{\text{INJ(PIN)}}^{(3)}$ | Total injected current (sum of all I/O and control pins) <sup>(5)</sup> | ±20                 |      |

- 1. Guaranteed by characterization results.

- 2. All power ( $V_{DD}$ ) and ground ( $V_{SS}$ ) pins must always be connected to the external supply.

- 3. I<sub>INJ(PIN)</sub> must never be exceeded. This is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub>>V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. For true open-drain pads, there is no positive injection current, and the corresponding V<sub>IN</sub> maximum must always be respected

- 4. ADC accuracy vs. negative injection current: Injecting negative current on any of the analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to standard analog pins which may potentially inject negative current. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in the I/O port pin characteristics section does not affect the ADC accuracy.

- 5. When several inputs are submitted to a current injection, the maximum Δ<sub>I<sub>NJ(PIN)</sub></sub> is the absolute sum of the positive and negative injected currents (instantaneous values). These results are based on characterization with Δ<sub>I<sub>NJ(PIN)</sub></sub> maximum current injection on four I/O port pins of the device.

**Table 16. Thermal characteristics**

| Symbol           | Ratings                      | Value      | Unit |

|------------------|------------------------------|------------|------|

| T <sub>STG</sub> | Storage temperature range    | -65 to 150 | °C   |

| T <sub>J</sub>   | Maximum junction temperature | 150        | C    |

#### 9.3 **Operating conditions**

The device must be used in operating conditions that respect the parameters in Table 17. In addition, full account must be taken of all physical capacitor characteristics and tolerances.

|                               | Table 111 Control of C |                           |      |      |      |  |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------|------|------|--|

| Symbol                        | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Conditions                | Min  | Max  | Unit |  |

| f <sub>CPU</sub>              | Internal CPU clock frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -                         | 0    | 16   | MHz  |  |

| $V_{DD}$                      | Standard operating voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                         | 2.95 | 5.5  | V    |  |

| (1)                           | C <sub>EXT</sub> : capacitance of external capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -                         | 470  | 3300 | nF   |  |

| $V_{CAP}^{(1)}$               | ESR of external capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | At 1 MHz <sup>(2)</sup>   | -    | 0.3  | ohm  |  |

|                               | ESL of external capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ALT WITZ                  | -    | 15   | nH   |  |

| P <sub>D</sub> <sup>(3)</sup> | Power dissipation at T <sub>A</sub> = 125° C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SO8N                      | -    | 49   | mW   |  |

| T <sub>A</sub>                | Ambient temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Maximum power dissipation | -40  | 125  | °C   |  |

| T <sub>J</sub>                | Junction temperature range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                         | -40  | 130  | C    |  |

Table 17. General operating conditions

- 2. This frequency of 1 MHz as a condition for  $V_{CAP}$  parameters is given by the design of the internal regulator.

- To calculate  $P_{Dmax}(T_A)$ , use the formula  $P_{Dmax} = (T_{Jmax} T_A)/\Theta_{JA}$  (see Section 10.2: Thermal characteristics on page 79) with the value for  $T_{Jmax}$  given in Table 17 above and the value for  $\Theta_{JA}$  given in Table 49: Thermal characteristics.

DS12129 Rev 3 43/85

Care should be taken when selecting the capacitor, due to its tolerance, as well as the parameter dependency on temperature, DC bias and frequency in addition to other factors. The parameter must be respected for the full application range.

Table 18. Operating conditions at power-up/power-down

| Symbol                | Parameter                                     | Conditions             | Min | Тур  | Max  | Unit |

|-----------------------|-----------------------------------------------|------------------------|-----|------|------|------|

|                       | V <sub>DD</sub> rise time rate                | -                      | 2   | -    | ∞    |      |

| t <sub>VDD</sub>      | V <sub>DD</sub> fall time rate <sup>(1)</sup> | -                      | 2   | -    | 8    | µs/V |

| t <sub>TEMP</sub>     | Reset release delay                           | V <sub>DD</sub> rising | -   | -    | 1.7  | ms   |

| V <sub>IT+</sub>      | Power-on reset threshold                      | -                      | 2.6 | 2.7  | 2.85 | V    |

| V <sub>IT-</sub>      | Brown-out reset threshold                     | -                      | 2.5 | 2.65 | 2.8  | ٧    |

| V <sub>HYS(BOR)</sub> | Brown-out reset hysteresis                    | -                      | -   | 70   | -    | mV   |

Reset is always generated after a t<sub>TEMP</sub> delay. The application must ensure that V<sub>DD</sub> is still above the minimum operating voltage (V<sub>DD</sub> min) when the t<sub>TEMP</sub> delay has elapsed.

### Total current consumption and timing in forced reset state

Table 28. Total current consumption and timing in forced reset state

| Symbol                  | Parameter                                    | Conditions              | Тур | Max <sup>(1)</sup> | Unit |

|-------------------------|----------------------------------------------|-------------------------|-----|--------------------|------|

|                         | Supply current in reset state <sup>(2)</sup> | V <sub>DD</sub> = 5 V   | 400 | -                  | uА   |

| I <sub>DD(R)</sub> Supp | supply current in reset state V              | V <sub>DD</sub> = 3.3 V | 300 | -                  | μΛ   |

| t <sub>RESETBL</sub>    | Reset release to vector fetch                | -                       | ı   | 150                | μs   |

<sup>1.</sup> Guaranteed by design.

#### **Current consumption of on-chip peripherals**

Subject to general operating conditions for  $V_{DD}$  and  $T_{A}$ . HSI internal RC/f<sub>CPU</sub> = f<sub>MASTER</sub> = 16 MHz, VDD = 5 V.

Table 29. Peripheral current consumption

| Symbol                 | Parameter                                          | Тур. | Unit |

|------------------------|----------------------------------------------------|------|------|

| I <sub>DD(TIM1)</sub>  | TIM1 supply current (1)                            | 210  |      |

| I <sub>DD(TIM2)</sub>  | TIM2 supply current (1)                            | 130  |      |

| I <sub>DD(TIM4)</sub>  | TIM4 timer supply current (1)                      | 50   |      |

| I <sub>DD(UART1)</sub> | UART1 supply current <sup>(1)</sup>                | 120  |      |

| I <sub>DD(SPI)</sub>   | SPI supply current <sup>(1)</sup>                  | 45   | μΑ   |

| I <sub>DD(I2C)</sub>   | I2C supply current (1)                             | 65   |      |

| I <sub>DD(ADC1)</sub>  | ADC1 supply current when converting <sup>(1)</sup> | 1000 |      |

Data based on a differential I<sub>DD</sub> measurement between reset configuration and timer counter running at 16 MHz. No IC/OC programmed (no I/O pads toggling). Not tested in production.

<sup>2.</sup> Characterized with all I/Os tied to  $V_{SS}$ .

# 9.3.6 I/O port pin characteristics

#### **General characteristics**

Subject to general operating conditions for  $V_{DD}$  and  $T_A$  unless otherwise specified. All unused pins must be kept at a fixed voltage: using the output mode of the I/O for example or an external pull-up or pull-down resistor.

Table 35. I/O static characteristics

| Symbol                          | Parameter                                 | Conditions                                  | Min                   | Тур | Max                     | Unit |

|---------------------------------|-------------------------------------------|---------------------------------------------|-----------------------|-----|-------------------------|------|

| V <sub>IL</sub>                 | Input low level voltage                   |                                             | -0.3                  | -   | 0.3 x V <sub>DD</sub>   | V    |

| V <sub>IH</sub>                 | Input high level voltage                  | V <sub>DD</sub> = 5 V                       | 0.7 x V <sub>DD</sub> | -   | V <sub>DD</sub> + 0.3 V | V    |

| V <sub>hys</sub>                | Hysteresis <sup>(1)</sup>                 |                                             | -                     | 700 | -                       | mV   |

| R <sub>pu</sub>                 | Pull-up resistor                          | $V_{DD}$ = 5 V, $V_{IN}$ = $V_{SS}$         | 30                    | 55  | 80                      | kΩ   |

|                                 | , Rise and fall time                      | Fast I/Os<br>Load = 50 pF                   | -                     | -   | 20 <sup>(2)</sup>       | ns   |

| t <sub>R</sub> , t <sub>F</sub> | (10% - 90%)                               | Standard and high sink I/Os<br>Load = 50 pF | -                     | -   | 125 <sup>(2)</sup>      | ns   |

| I <sub>lkg</sub>                | Input leakage current, analog and digital | $V_{SS} \le V_{IN} \le V_{DD}$              | -                     | -   | ±1                      | μΑ   |

| I <sub>lkg ana</sub>            | Analog input leakage current              | $V_{SS} \le V_{IN} \le V_{DD}$              | -                     | -   | ±250 <sup>(3)</sup>     | nA   |

| I <sub>lkg(inj)</sub>           | Leakage current in adjacent I/O           | Injection current ±4 mA                     | -                     | -   | ±1 <sup>(3)</sup>       | μΑ   |

<sup>1.</sup> Hysteresis voltage between Schmitt trigger switching levels. Guaranteed by characterization results.

<sup>2.</sup> Guaranteed by design.

<sup>3.</sup> Guaranteed by characterization results.

**Symbol Conditions Parameter** Min Max Unit Output low level with 8 pins sunk  $I_{IO}$  = 10 mA,  $V_{DD}$  = 5 V 8.0 1.0<sup>(1)</sup>  $I_{IO}$  = 10 mA,  $V_{DD}$  = 3.3 V Output low level with 4 pins sunk  $V_{OL}$  $1.5^{(1)}$ Output low level with 4 pins sunk  $I_{IO}$  = 20 mA,  $V_{DD}$  = 5 V  $I_{IO}$  = 10 mA,  $V_{DD}$  = 5 V Output high level with 8 pins sourced 4.0 2.1<sup>(1)</sup>  $I_{IO}$  = 10 mA,  $V_{DD}$  = 3.3 V  $V_{OH}$ Output high level with 4 pins sourced 3.3<sup>(1)</sup>  $I_{IO}$  = 20 mA,  $V_{DD}$  = 5 V Output high level with 4 pins sourced

Table 38. Output driving current (high sink ports)

#### Typical output level curves

*Figure 22* to *Figure 29* show typical output level curves measured with output on a single pin.

<sup>1.</sup> Guaranteed by characterization results.

Figure 30. Typ.  $V_{DD} - V_{OH} @ V_{DD} = 3.3 \text{ V (high sink ports)}$

#### 9.3.7 SPI serial peripheral interface

66/85

Unless otherwise specified, the parameters given in *Table 39* are derived from tests performed under ambient temperature,  $f_{MASTER}$  frequency and  $V_{DD}$  supply voltage conditions.  $t_{MASTER} = 1/f_{MASTER}$ .

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

**Symbol** Unit **Parameter Conditions** Min Max Master mode 0 8  $f_{SCK}$ SPI clock frequency  $\mathsf{MHz}$ 1/t<sub>c(SCK)</sub> 7 Slave mode 0

Table 39. SPI characteristics

| Symbol                                               | Parameter                                       | Conditions                      | Min                      | Max                      | Unit |

|------------------------------------------------------|-------------------------------------------------|---------------------------------|--------------------------|--------------------------|------|

| t <sub>r(SCK)</sub>                                  | SPI clock rise and fall time                    | Capacitive load: C = 30 pF      | -                        | 25                       |      |

| t <sub>su(NSS)</sub> <sup>(1)</sup>                  | NSS setup time                                  | Slave mode                      | 4 x t <sub>MASTER</sub>  | -                        |      |

| t <sub>h(NSS)</sub> <sup>(1)</sup>                   | NSS hold time                                   | Slave mode                      | 70                       | -                        |      |

| t <sub>w(SCKH)</sub> (1)<br>t <sub>w(SCKL)</sub> (1) | SCK high and low time                           | Master mode                     | t <sub>SCK</sub> /2 - 15 | t <sub>SCK</sub> /2 + 15 |      |

| t <sub>su(MI)</sub> (1)<br>t <sub>su(SI)</sub> (1)   | Data input setup time                           | Master mode                     | 5                        | -                        |      |

| t <sub>su(SI)</sub> (1)                              |                                                 | Slave mode                      | 5                        | -                        |      |

| t <sub>h(MI)</sub> (1)                               | MI) ` '   E · · · · · · · · · · · · · · · · · · | Master mode                     | 7                        | -                        | ns   |

| t <sub>h(SI)</sub> (1)                               | Data input hold time                            | Slave mode                      | 10                       | -                        |      |

| t <sub>a(SO)</sub> (1)(2)                            | Data output access time                         | Slave mode                      | -                        | 3 x t <sub>MASTER</sub>  |      |

| t <sub>dis(SO)</sub> (1)(3)                          | Data output disable time                        | Slave mode                      | 25                       | -                        |      |

| t <sub>v(SO)</sub> (1)                               | Data output valid time                          | Slave mode (after enable edge)  | -                        | 65                       |      |

| t <sub>v(MO)</sub> <sup>(1)</sup>                    | Data output valid time                          | Master mode (after enable edge) | -                        | 30                       |      |

| t <sub>h(SO)</sub> <sup>(1)</sup>                    | Data output hold time                           | Slave mode (after enable edge)  | 27                       | -                        |      |

| t <sub>h(MO)</sub> <sup>(1)</sup>                    | Data output hold time                           | Master mode (after enable edge) | 11                       | -                        |      |

Table 39. SPI characteristics (continued)

- 1. Values based on design simulation and/or characterization results, and not tested in production.

- 2. Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

- 3. Min time is for the minimum time to invalidate the output and the max time is for the maximum time to put the data in Hi-Z.

Figure 31. SPI timing diagram - slave mode and CPHA = 0

Figure 34. Typical application with I2C bus and timing diagram

1. Measurement points are made at CMOS levels: 0.3 x  $\rm V_{DD}$  and 0.7 x  $\rm V_{DD}$

Table 42. ADC accuracy with  $R_{AIN}$  < 10 k $\Omega$  ,  $V_{DD}$  = 5 V

| Symbol         | Parameter                        | Conditions               | Тур | Max <sup>(1)</sup> | Unit |

|----------------|----------------------------------|--------------------------|-----|--------------------|------|

|                |                                  | f <sub>ADC</sub> = 2 MHz | 1.6 | 3.5                |      |

| E <sub>T</sub> | Total unadjusted error (2)       | f <sub>ADC</sub> = 4 MHz | 2.2 | 4                  |      |

|                |                                  | f <sub>ADC</sub> = 6 MHz | 2.4 | 4.5                |      |

|                |                                  | f <sub>ADC</sub> = 2 MHz | 1.1 | 2.5                |      |

| E <sub>O</sub> | Offset error (2)                 | f <sub>ADC</sub> = 4 MHz | 1.5 | 3                  |      |

|                |                                  | f <sub>ADC</sub> = 6 MHz | 1.8 | 3                  |      |

|                |                                  | f <sub>ADC</sub> = 2 MHz | 1.5 | 3                  |      |

| E <sub>G</sub> | Gain error <sup>(2)</sup>        | f <sub>ADC</sub> = 4 MHz | 2.1 | 3                  | LSB  |

|                |                                  | f <sub>ADC</sub> = 6 MHz | 2.2 | 4                  |      |

|                |                                  | f <sub>ADC</sub> = 2 MHz | 0.7 | 1.5                |      |

| E <sub>D</sub> | Differential linearity error (2) | f <sub>ADC</sub> = 4 MHz | 0.7 | 1.5                |      |

|                |                                  | f <sub>ADC</sub> = 6 MHz | 0.7 | 1.5                |      |

| E <sub>L</sub> |                                  | f <sub>ADC</sub> = 2 MHz | 0.6 | 1.5                |      |

|                | Integral linearity error (2)     | f <sub>ADC</sub> = 4 MHz | 0.8 | 2                  |      |

|                |                                  | f <sub>ADC</sub> = 6 MHz | 0.8 | 2                  |      |

<sup>1.</sup> Guaranteed by characterization results.

Table 43. ADC accuracy with  $R_{AIN}$  < 10 k $\Omega$   $R_{AIN}$ ,  $V_{DD}$  = 3.3 V

| Symbol         | Parameter                                   | Conditions               | Тур | Max <sup>(1)</sup> | Unit |

|----------------|---------------------------------------------|--------------------------|-----|--------------------|------|

| IF I           | Total unadjusted error <sup>(2)</sup>       | f <sub>ADC</sub> = 2 MHz | 1.6 | 3.5                |      |

| E <sub>T</sub> | Total unaujusteu enor                       | f <sub>ADC</sub> = 4 MHz | 1.9 | 4                  |      |

| IE.I           | Offset error <sup>(2)</sup>                 | f <sub>ADC</sub> = 2 MHz | 1   | 2.5                |      |

| E <sub>O</sub> | Oliset error                                | f <sub>ADC</sub> = 4 MHz | 1.5 | 2.5                |      |

| E <sub>G</sub> | Gain error <sup>(2)</sup>                   | f <sub>ADC</sub> = 2 MHz | 1.3 | 3                  | LSB  |

|                | Gaill elloi                                 | f <sub>ADC</sub> = 4 MHz | 2   | 3                  | LOD  |

| IE I           | Differential linearity error <sup>(2)</sup> | f <sub>ADC</sub> = 2 MHz | 0.7 | 1.0                |      |

| E <sub>D</sub> |                                             | f <sub>ADC</sub> = 4 MHz | 0.7 | 1.5                |      |

| IE I           | Integral linearity error <sup>(2)</sup>     | f <sub>ADC</sub> = 2 MHz | 0.6 | 1.5                |      |

| E <sub>L</sub> | integral inteanty endity                    | f <sub>ADC</sub> = 4 MHz | 0.8 | 2                  |      |

<sup>1.</sup> Guaranteed by characterization results.

ADC accuracy vs. negative injection current: Injecting negative current on any of the analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to standard analog pins which may potentially inject negative current. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in Section 9.3.6 does not affect the ADC accuracy.

<sup>2.</sup> ADC accuracy vs. negative injection current: Injecting negative current on any of the analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to standard analog pins which may potentially inject negative current. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and  $\Sigma I_{INJ(PIN)}$  in Section 9.3.6 does not affect the ADC accuracy.

Package information STM8S001J3

| Table 48. SO8N – 8-lead 4.9 x 6 mm, plastic small outline, 150 mils body width, |

|---------------------------------------------------------------------------------|

| package mechanical data                                                         |

| Cumbal |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|--------|-------|-------------|-------|--------|-----------------------|--------|

| Symbol | Min.  | Тур.        | Max.  | Min.   | Тур.                  | Max.   |

| D      | 4.800 | 4.900       | 5.000 | 0.1890 | 0.1929                | 0.1969 |

| E      | 5.800 | 6.000       | 6.200 | 0.2283 | 0.2362                | 0.2441 |

| E1     | 3.800 | 3.900       | 4.000 | 0.1496 | 0.1535                | 0.1575 |

| е      | -     | 1.270       | -     | -      | 0.0500                | -      |

| h      | 0.250 | -           | 0.500 | 0.0098 | -                     | 0.0197 |

| k      | 0°    | -           | 8°    | 0°     | -                     | 8°     |

| L      | 0.400 | -           | 1.270 | 0.0157 | -                     | 0.0500 |

| L1     | -     | 1.040       | -     | -      | 0.0409                | -      |

| ccc    | -     | -           | 0.100 | -      | -                     | 0.0039 |

<sup>1.</sup> Values in inches are converted from mm and rounded to four decimal digits.

Figure 38. SO8N – 8-lead 4.9 x 6 mm, plastic small outline, 150 mils body width, package recommended footprint

# Device marking for SO8N – 8-lead 4.9 x 6 mm, plastic small outline, 150 mils body width

The following figure gives an example of topside marking orientation versus pin 1/ball A1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Package information STM8S001J3

| Table 49  | Thormal    | characteristics <sup>(1)</sup> |

|-----------|------------|--------------------------------|

| Table 45. | HIIEHIIIAI | Characteristics, 7             |

| Symbol            | Parameter                                | Value | Unit |

|-------------------|------------------------------------------|-------|------|

| $\Theta_{\sf JA}$ | Thermal resistance junction-ambient SO8N | 102   | °C/W |

Thermal resistances are based on JEDEC JESD51-2 with 4-layer PCB in a natural convection

environment

#### 10.2.1 Reference document

JESD51-2 integrated circuits thermal test method environment conditions - natural convection (still air). Available from www.jedec.org.

#### 10.2.2 Selecting the product temperature range

When ordering the microcontroller, the temperature range is specified in the order code (see *Figure 40: STM8S001J3 ordering information scheme(1)*).

The following example shows how to calculate the temperature range needed for a given application.

Assuming the following application conditions:

- Maximum ambient temperature T<sub>Amax</sub>= 75 °C (measured according to JESD51-2)

- $I_{DDmax} = 8 \text{ mA}, V_{DD} = 5.0 \text{ V}$

- Maximum 4 I/Os used at the same time in output at low level with

$$I_{OL}$$

= 8 mA,  $V_{OL}$  = 0.4 V

$$P_{INTmax} = 8 \text{ mA x } 5.0 \text{ V} = 40 \text{ mW}$$

$$P_{Dmax} = 40 \text{ mW} + (8 \times 0.4 \times 4) \text{ mW}$$

Thus:

$$P_{Dmax} = 52.8 \text{ mW}$$

Using the values obtained in Section Table 49.: Thermal characteristics  $T_{Jmax}$  is calculated as follows for SO8N package 102 °C/W :

$$T_{Jmax}$$

= 75 °C + (102 °C/W x 52.8 mW) = 75 °C + 5.4 °C = 80.4 °C.

Above information is within the range (-40 <  $T_J$  < 130 °C)