Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | HCS12                                                                   |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 25MHz                                                                   |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, SCI, SPI                             |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 59                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 4K x 8                                                                  |

| RAM Size                   | 12K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 5.5V                                                            |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 80-QFP                                                                  |

| Supplier Device Package    | 80-QFP (14x14)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s12kg256cfue |

Chapter 1 MC9S12KT256 Device Overview (MC9S12KT256V1)

#### 1.2.2.26 PH0 / KWH0 / MISO1 — Port H I/O Pin 0

PH0 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode. It can be configured as master input (during master mode) or slave output (during slave mode) pin MISO of the Serial Peripheral Interface 1 (SPI1).

#### 1.2.2.27 PJ7 / KWJ7 / TXCAN4 / SCL — PORT J I/O Pin 7

PJ7 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode. It can be configured as the transmit pin TXCAN for the Scalable Controller Area Network controller 4 (CAN4) or the serial clock pin SCL of the IIC module.

#### 1.2.2.28 PJ6 / KWJ6 / RXCAN4 / SDA — PORT J I/O Pin 6

PJ6 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode. It can be configured as the receive pin RXCAN for the Scalable Controller Area Network controller 4 (CAN4) or the serial data pin SDA of the IIC module.

## 1.2.2.29 PJ[1:0] / KWJ[1:0] — Port J I/O Pins [1:0]

PJ1 and PJ0 are general purpose input or output pins. They can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode.

#### 1.2.2.30 PK7 / ECS / ROMCTL — Port K I/O Pin 7

PK7 is a general purpose input or output pin. During MCU expanded modes of operation, this pin is used as the emulation chip select output ( $\overline{ECS}$ ). During MCU expanded modes of operation, this pin is used to enable the Flash EEPROM memory in the memory map (ROMCTL). At the rising edge of  $\overline{RESET}$ , the state of this pin is latched to the ROMON bit.

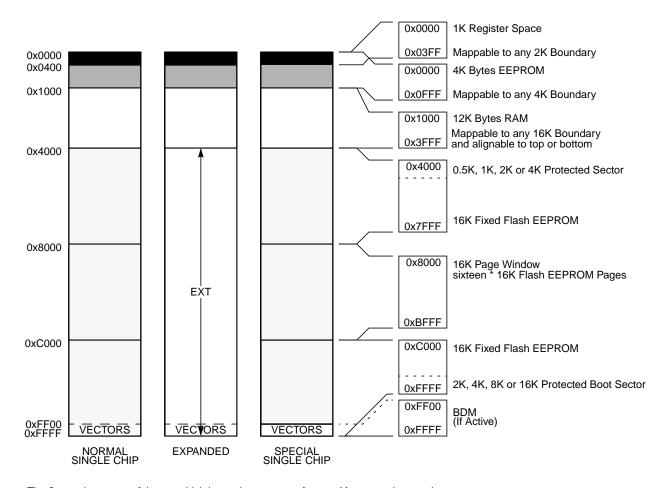

Figure 1-9 illustrates the full user configurable device memory map of MC9S12KT256.

The figure shows a useful map, which is not the map out of reset. After reset the map is:

0x0000-0x03FF: Register Space

0x1000-0x3FFF: 12K RAM

0x0000-0x0FFF: 4K EEPROM (1K hidden behind Register Space)

Figure 1-9. MC9S12KT256 Memory Map

MC9S12KT256 Data Sheet, Rev. 1.16 Freescale Semiconductor 39

Chapter 1 MC9S12KT256 Device Overview (MC9S12KT256V1)

## 0x001C-0x001D MMC Map 3 of 4 (HCS12 Module Mapping Control, Device Guide)

| Address | Name    |   | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3 | Bit 2   | Bit 1   | Bit 0   |

|---------|---------|---|---------|---------|---------|---------|-------|---------|---------|---------|

| 0x001C  | MEMSIZ0 | R | reg_sw0 | 0       | eep_sw1 | eep_sw0 | 0     | ram_sw2 | ram_sw1 | ram_sw0 |

| 0,0010  | MEMOIZO | W |         |         |         |         |       |         |         |         |

| 0x001D  | MEMSIZ1 | R | rom_sw1 | rom_sw0 | 0       | 0       | 0     | 0       | pag_sw1 | pag_sw0 |

| 00010   | MEMBILI | W |         |         |         |         |       |         |         |         |

## 0x001E-0x001E MEBI Map 2 of 3 (HCS12 Multiplexed External Bus Interface)

| Address | Name  |   | Bit 7 | Bit 6   | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|---|-------|---------|-------|-------|-------|-------|-------|-------|

| 0x001E  | INTCR | R | IRQE  | IRQEN   | 0     | 0     | 0     | 0     | 0     | 0     |

| OXOUTE  | INTOK | W | IIVQL | IIIQLIN |       |       |       |       |       |       |

## 0x001F-0x001F INT Map 2 of 2 (HCS12 Interrupt)

| Address | Name    | Bi  | t 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 |

|---------|---------|-----|-----|--------|--------|--------|--------|--------|--------|-------|

| 0x001F  | HPRIO   | R   | EL7 | PSEL6  | PSEL5  | PSEL4  | PSEL3  | PSEL2  | PSEL1  | 0     |

| 0.00011 | TIFICIO | w l | LL/ | I OLLO | I OLLO | I OLL4 | I OLLO | I OLLZ | I SLLI |       |

## 0x0020-0x002F DBG Map 1 of 1 (HCS12 Debug)

| Address | Name            |        | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 |

|---------|-----------------|--------|--------|--------|--------|--------|--------|--------|-------|-------|

| 0x0020  | DBGC1<br>—      | R<br>W | DBGEN  | ARM    | TRGSEL | BEGIN  | DBGBRK | 0      | CAPI  | MOD   |

| 0x0021  | DBGSC<br>—      | R<br>W | AF     | BF     | CF     | 0      |        | TF     | RG    |       |

| 0x0022  | DBGTBH<br>—     | R<br>W | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 |

| 0x0023  | DBGTBL<br>—     | R<br>W | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 |

| 0x0024  | DBGCNT          | R<br>W | TBF    | 0      |        |        | CN     | NT     |       |       |

| 0x0025  | DBGCCX<br>—     | R<br>W | PAG    | SEL    |        |        | EXT    | CMP    |       |       |

| 0x0026  | DBGCCH<br>—     | R<br>W | Bit 15 | 14     | 13     | 12     | 11     | 10     | 9     | Bit 8 |

| 0x0027  | DBGCCL<br>—     | R<br>W | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1     | Bit 0 |

| 0x0028  | DBGC2<br>BKPCT0 | R<br>W | BKABEN | FULL   | BDM    | TAGAB  | BKCEN  | TAGC   | RWCEN | RWC   |

| 0x0029  | DBGC3<br>BKPCT1 | R<br>W | ВКАМВН | BKAMBL | вквмвн | BKBMBL | RWAEN  | RWA    | RWBEN | RWB   |

| 0x002A  | DBGCAX<br>BKP0X | R<br>W | PAG    | SEL    |        |        | EXT    | CMP    |       |       |

| 0x002B  | DBGCAH<br>BKP0H | R<br>W | Bit 15 | 14     | 13     | 12     | 11     | 10     | 9     | Bit 8 |

MC9S12KT256 Data Sheet, Rev. 1.16

Chapter 1 MC9S12KT256 Device Overview (MC9S12KT256V1)

# 0x0080-0x009F ATD0 (Analog to Digital Converter 10 Bit 8 Channel) (continued)

| Address         | Name            |       | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----------------|-----------------|-------|--------|-------|-------|-------|-------|-------|-------|-------|

| 0x009D ATD0DR6L | R               | Bit 7 | Bit 6  | 0     | 0     | 0     | 0     | 0     | 0     |       |

| 0,009D          | AIDODROL        | W     |        |       |       |       |       |       |       |       |

| 0,000           | ATDADDZU        | R     | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

| 0x009E          | 0x009E ATD0DR7H | W     |        |       |       |       |       |       |       |       |

| 0×000E ATD0DP7I | R               | Bit 7 | Bit 6  | 0     | 0     | 0     | 0     | 0     | 0     |       |

| 0x009F ATD0DR7L |                 | w     |        |       |       |       |       |       |       |       |

| 0x00    | A0–0x00C | 7 | Re    | eserved | space |       |       |       |       |       |   |

|---------|----------|---|-------|---------|-------|-------|-------|-------|-------|-------|---|

| Address | Name     |   | Bit 7 | Bit 6   | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |   |

| 0x00A0- | Reserved | R | 0     | 0       | 0     | 0     | 0     | 0     | 0     | 0     | ] |

| 0x00C7  | Reserved | W |       |         |       |       |       |       |       |       | 1 |

# 0x00C8-0x00CF SCI0 (Asynchronous Serial Interface)

| Address | Name     |    | Bit 7 | Bit 6   | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 |

|---------|----------|----|-------|---------|-------|--------|--------|--------|-------|-------|

| 0x00C8  | SCI0BDH  | R[ | 0     | 0       | 0     | SBR12  | SBR11  | SBR10  | SBR9  | SBR8  |

| 0.0000  | OOIODDIT | W  |       |         |       | ODICIZ | ODICTI | ODICTO | ODINO | ODINO |

| 0x00C9  | SCI0BDL  | R  | SBR7  | SBR6    | SBR5  | SBR4   | SBR3   | SBR2   | SBR1  | SBR0  |

|         |          | W  |       |         |       |        |        |        |       |       |

| 0x00CA  | SCI0CR1  | R  | LOOPS | SCISWAI | RSRC  | М      | WAKE   | ILT    | PE    | PT    |

|         |          | W  |       |         |       |        |        |        |       |       |

| 0x00CB  | SCI0CR2  | R  | TIE   | TCIE    | RIE   | ILIE   | TE     | RE     | RWU   | SBK   |

|         |          | W  |       |         |       |        |        |        |       |       |

| 0x00CC  | SCI0SR1  | R  | TDRE  | TC      | RDRF  | IDLE   | OR     | NF     | FE    | PF    |

| 000000  | 00100101 | w  |       |         |       |        |        |        |       |       |

| 0x00CD  | SCI0SR2  | R  | 0     | 0       | 0     | 0      | 0      | BRK13  | TXDIR | RAF   |

| OXOOCD  | 30103N2  | W  |       |         |       |        |        | DIXIO  | IADIK |       |

| 0x00CE  | SCI0DRH  | R  | R8    | T8      | 0     | 0      | 0      | 0      | 0     | 0     |

| UXUUCE  | SCIODKII | w  |       | 10      |       |        |        |        |       |       |

| 0x00CF  | SCI0DRL  | R  | R7    | R6      | R5    | R4     | R3     | R2     | R1    | R0    |

| UXUUCE  | SCIUDICE | W[ | T7    | T6      | T5    | T4     | T3     | T2     | T1    | T0    |

# 0x00D0-0x00D7 SCI1 (Asynchronous Serial Interface)

| Address | Name     |     | Bit 7 | Bit 6   | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1          | Bit 0 |

|---------|----------|-----|-------|---------|-------|--------|--------|--------|----------------|-------|

| 0x00D0  | SCI1BDH  | R [ | 0     | 0       | 0     | SBR12  | SBR11  | SBR10  | SBR9           | SBR8  |

| OXOODO  | OCHIDDH  | W   |       |         |       | ODICIZ | ODICTT | ODICTO | ODICO          | ODINO |

| 0x00D1  | SCI1BDL  | R   | SBR7  | SBR6    | SBR5  | SBR4   | SBR3   | SBR2   | SBR1           | SBR0  |

| 0,000   | 0011222  | W   |       | OBINO   | 05.10 |        |        |        |                | OBINO |

| 0x00D2  | SCI1CR1  | R   | LOOPS | SCISWAI | RSRC  | М      | WAKE   | ILT    | PE             | PT    |

| 0,10022 | 33       | W   |       | 00.017  |       |        |        |        | · <del>-</del> |       |

| 0x00D3  | SCI1CR2  | R   | TIE   | TCIE    | RIE   | ILIE   | TE     | RE     | RWU            | SBK   |

| ONCODO  | 33.70112 | W   |       | . 512   | 1.11  | 1212   |        | 1,1    |                | OBIT  |

MC9S12KT256 Data Sheet, Rev. 1.16

Except for the sector erase abort command, a buffered command will wait for the active operation to be completed before being launched. The sector erase abort command is launched when the CBEIF flag is cleared as part of a sector erase abort command write sequence. After a command is launched, the completion of the command operation is indicated by the setting of the CCIF flag. The CCIF flag only sets when all active and buffered commands have been completed.

#### 2.4.1.3 Valid Flash Commands

Table 2-21 summarizes the valid Flash commands along with the effects of the commands on the Flash block.

NVM **FCMDB Function on Flash Memory** Command 0x05 Erase Verify all memory bytes in the Flash block are erased. If the Flash block is erased, the BLANK Verify flag in the FSTAT register will set upon command completion. 0x06 Data Compress data from a selected portion of the Flash block. The resulting signature is stored in Compress the FDATA register. Program a word (two bytes) in the Flash block. 0x20 Program 0x40 Sector Erase all memory bytes in a sector of the Flash block. Erase 0x41 Mass Erase all memory bytes in the Flash block. A mass erase of the full Flash block is only possible Erase when FPLDIS, FPHDIS, and FPOPEN bits in the FPROT register are set prior to launching the command. 0x47 Sector Abort the sector erase operation. The sector erase operation will terminate according to a set Erase procedure. The Flash sector must not be considered erased if the ACCERR flag is set upon Abort command completion.

Table 2-21. Valid Flash Command Description

A Flash word must be in the erased state before being programmed. Cumulative programming of bits within a Flash word is not allowed and will result in invalid data stored.

#### Chapter 3 256 Kbyte ECC Flash Module (S12FTS256K2ECCV2)

**Table 3-13. Flash Protection Function**

| FPOPEN | FPHDIS | FPLDIS | Function <sup>1</sup>           |

|--------|--------|--------|---------------------------------|

| 1      | 1      | 1      | No Protection                   |

| 1      | 1      | 0      | Protected Low Range             |

| 1      | 0      | 1      | Protected High Range            |

| 1      | 0      | 0      | Protected High and Low Ranges   |

| 0      | 1      | 1      | Full Block Protected            |

| 0      | 1      | 0      | Unprotected Low Range           |

| 0      | 0      | 1      | Unprotected High Range          |

| 0      | 0      | 0      | Unprotected High and Low Ranges |

<sup>&</sup>lt;sup>1</sup> For range sizes, refer to Table 3-14 and Table 3-15.

Table 3-14. Flash Protection Higher Address Range

| FPHS[1:0] | Unpaged<br>Address Range | Paged<br>Address Range       | Protected Size |

|-----------|--------------------------|------------------------------|----------------|

| 00        | 0xF800-0xFFFF            | 0x0037/0x003F: 0xC800-0xCFFF | 2 Kbytes       |

| 01        | 0xF000-0xFFFF            | 0x0037/0x003F: 0xC000-0xCFFF | 4 Kbytes       |

| 10        | 0xE000-0xFFFF            | 0x0037/0x003F: 0xB000-0xCFFF | 8 Kbytes       |

| 11        | 0xC000-0xFFFF            | 0x0037/0x003F: 0x8000-0xCFFF | 16 Kbytes      |

Table 3-15. Flash Protection Lower Address Range

| FPLS[1:0] | Unpaged<br>Address Range | Paged<br>Address Range       | Protected Size |

|-----------|--------------------------|------------------------------|----------------|

| 00        | 0x4000-0x43FF            | 0x0036/0x003E: 0x8000-0x83FF | 1 Kbyte        |

| 01        | 0x4000-0x47FF            | 0x0036/0x003E: 0x8000-0x87FF | 2 Kbytes       |

| 10        | 0x4000-0x4FFF            | 0x0036/0x003E: 0x8000-0x8FFF | 4 Kbytes       |

| 11        | 0x4000-0x5FFF            | 0x0036/0x003E: 0x8000-0x9FFF | 8 Kbytes       |

All possible Flash protection scenarios are illustrated in Figure 3-8. Although the protection scheme is loaded from the Flash array after reset, it can be changed by the user. This protection scheme can be used by applications requiring re-programming in single-chip mode while providing as much protection as possible if re-programming is not required.

Except for the sector erase abort command, a buffered command will wait for the active operation to be completed before being launched. The sector erase abort command is launched when the CBEIF flag is cleared as part of a sector erase abort command write sequence. After a command is launched, the completion of the command operation is indicated by the setting of the CCIF flag. The CCIF flag only sets when all active and buffered commands have been completed.

#### 3.4.1.3 Valid Flash Commands

Table 3-21 summarizes the valid Flash commands along with the effects of the commands on the Flash block.

NVM **FCMDB Function on Flash Memory** Command 0x05 Erase Verify all memory bytes in the Flash block are erased. If the Flash block is erased, the BLANK Verify flag in the FSTAT register will set upon command completion. 0x06 Data Compress data from a selected portion of the Flash block. The resulting signature is stored in Compress the FDATA register. Program a word (two bytes) in the Flash block. 0x20 Program 0x40 Sector Erase all memory bytes in a sector of the Flash block. Erase 0x41 Mass Erase all memory bytes in the Flash block. A mass erase of the full Flash block is only possible Erase when FPLDIS, FPHDIS, and FPOPEN bits in the FPROT register are set prior to launching the command. 0x47 Sector Abort the sector erase operation. The sector erase operation will terminate according to a set Erase procedure. The Flash sector must not be considered erased if the ACCERR flag is set upon Abort command completion.

**Table 3-21. Valid Flash Command Description**

A Flash word must be in the erased state before being programmed. Cumulative programming of bits within a Flash word is not allowed and will result in invalid data stored.

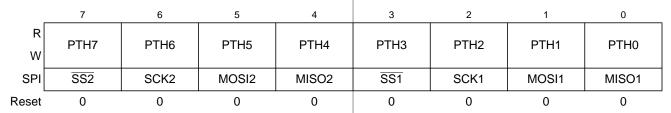

# 5.3.5 Port H Registers

Port H is associated with two serial peripheral interfaces (SPI1, SPI2). Each pin is assigned to these modules according to the following priority: SPI2/SP1 > general-purpose I/O.

When SPI2 is enabled, the respective pin configuration for PH[7:4] is determined by several status bits in the SPI2 module. When SPI1 is enabled, the respective pin configuration for PH[3:0] is determined by several status bits in the SPI1 module. Refer to the SPI block description chapter for information on enabling and disabling the SPI. The SPI1 and SPI2 pins can be re-routed. Refer to Section 5.3.3.8, "Module Routing Register (MODRR)".

During reset, port H pins are configured as high-impedance inputs.

# 5.3.5.1 Port H I/O Register (PTH)

Module Base + 0x0020

Figure 5-31. Port H I/O Register (PTH)

Read: Anytime. Write: Anytime.

If the data direction bits of the associated I/O pins are set to 1, a read returns the value of the port register, otherwise the value at the pins is read.

The SPI function takes precedence over the general purpose I/O if enabled...

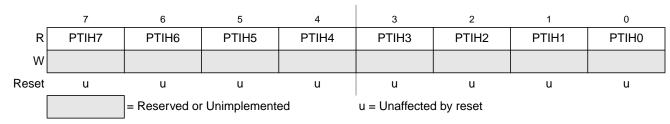

# 5.3.5.2 Port H Input Register (PTIH)

Module Base + 0x0021

Figure 5-32. Port H Input Register (PTIH)

Read: Anytime. Write: Never, writes to this register have no effect.

This register always reads back the status of the associated pins.

Chapter 5 Port Integration Module (PIM9KT256V1)

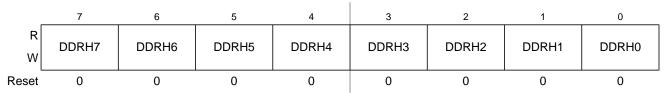

## 5.3.5.3 Port H Data Direction Register (DDRH)

Module Base + 0x0022

Figure 5-33. Port H Data Direction Register (DDRH)

Read: Anytime. Write: Anytime.

This register configures each port H pin as either input or output.

Table 5-30. DDRH Field Descriptions

| Field | Description                                                                                                |

|-------|------------------------------------------------------------------------------------------------------------|

| _     | Data Direction Port H  0 Associated pin is configured as input.  1 Associated pin is configured as output. |

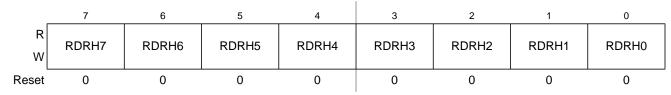

# 5.3.5.4 Port H Reduced Drive Register (RDRH)

Module Base + 0x0023

Figure 5-34. Port H Reduced Drive Register (RDRH)

Read: Anytime. Write: Anytime.

This register configures the drive strength of each port H output pin as either full or reduced. If the port is used as input this bit is ignored.

**Table 5-31. RDRH Field Descriptions**

| Field     | Description                                                                                                              |

|-----------|--------------------------------------------------------------------------------------------------------------------------|

| RDRH[7:0] | Reduced Drive Port H  0 Full drive strength at output.  1 Associated pin drives at about 1/6 of the full drive strength. |

MC9S12KT256 Data Sheet, Rev. 1.16

Table 8-7. ATDCTL3 Field Descriptions (continued)

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 2<br>FIFO       | Result Register FIFO Mode — If this bit is zero (non-FIFO mode), the A/D conversion results map into the result registers based on the conversion sequence; the result of the first conversion appears in the first result register, the second result in the second result register, and so on.                                                                                                                                                                                                               |  |  |  |  |  |

|                 | If this bit is one (FIFO mode) the conversion counter is not reset at the beginning or ending of a conversion sequence; sequential conversion results are placed in consecutive result registers. In a continuously scanning conversion sequence, the result register counter will wrap around when it reaches the end of the result register file. The conversion counter value (CC2-0 in ATDSTATO) can be used to determine where in the result register file, the current conversion result will be placed. |  |  |  |  |  |

|                 | Aborting a conversion or starting a new conversion by write to an ATDCTL register (ATDCTL5-0) clears the conversion counter even if FIFO=1. So the first result of a new conversion sequence, started by writing to ATDCTL5, will always be place in the first result register (ATDDDR0). Intended usage of FIFO mode is continuos conversion (SCAN=1) or triggered conversion (ETRIG=1).                                                                                                                      |  |  |  |  |  |

|                 | Finally, which result registers hold valid data can be tracked using the conversion complete flags. Fast flag clear mode may or may not be useful in a particular application to track valid data.  O Conversion results are placed in the corresponding result register up to the selected sequence length.  Conversion results are placed in consecutive result registers (wrap around at end).                                                                                                              |  |  |  |  |  |

| 1–0<br>FRZ[1:0] | Background Debug Freeze Enable — When debugging an application, it is useful in many cases to have the ATD pause when a breakpoint (Freeze Mode) is encountered. These 2 bits determine how the ATD will respond to a breakpoint as shown in Table 8-9. Leakage onto the storage node and comparator reference capacitors may compromise the accuracy of an immediately frozen conversion depending on the length of the freeze period.                                                                        |  |  |  |  |  |

**Table 8-8. Conversion Sequence Length Coding**

| S8C | S4C | S2C | S1C | Number of Conversions per Sequence |

|-----|-----|-----|-----|------------------------------------|

| 0   | 0   | 0   | 0   | 8                                  |

| 0   | 0   | 0   | 1   | 1                                  |

| 0   | 0   | 1   | 0   | 2                                  |

| 0   | 0   | 1   | 1   | 3                                  |

| 0   | 1   | 0   | 0   | 4                                  |

| 0   | 1   | 0   | 1   | 5                                  |

| 0   | 1   | 1   | 0   | 6                                  |

| 0   | 1   | 1   | 1   | 7                                  |

| 1   | Х   | Х   | Х   | 8                                  |

Table 8-9. ATD Behavior in Freeze Mode (Breakpoint)

| FRZ1 | FRZ0 | Behavior in Freeze Mode                |  |  |  |

|------|------|----------------------------------------|--|--|--|

| 0    | 0    | Continue conversion                    |  |  |  |

| 0    | 1    | Reserved                               |  |  |  |

| 1    | 0    | Finish current conversion, then freeze |  |  |  |

| 1    | 1    | Freeze Immediately                     |  |  |  |

MC9S12KT256 Data Sheet, Rev. 1.16 275 Freescale Semiconductor

# 9.1.2 Modes of Operation

The IIC functions the same in normal, special, and emulation modes. It has two low power modes: wait and stop modes.

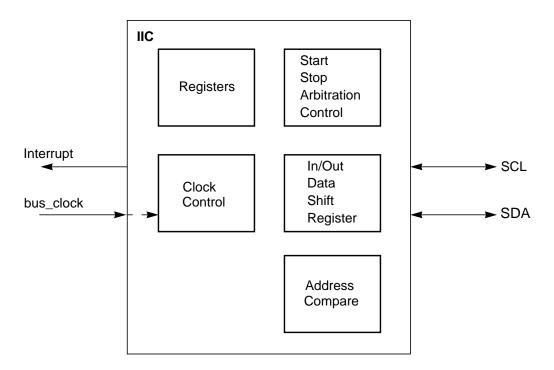

# 9.1.3 Block Diagram

The block diagram of the IIC module is shown in Figure 9-1.

Figure 9-1. IIC Block Diagram

Table 9-5. IIC Divider and Hold Values (Sheet 4 of 5)

| IBC[7:0]<br>(hex) | SCL Divider (clocks) | SDA Hold<br>(clocks) | SCL Hold<br>(start) | SCL Hold<br>(stop) |

|-------------------|----------------------|----------------------|---------------------|--------------------|

| 6A                | 896                  | 130                  | 444                 | 450                |

| 6B                | 1024                 | 130                  | 508                 | 514                |

| 6C                | 1152                 | 194                  | 572                 | 578                |

| 6D                | 1280                 | 194                  | 636                 | 642                |

| 6E                | 1536                 | 258                  | 764                 | 770                |

| 6F                | 1920                 | 258                  | 956                 | 962                |

| 70                | 1280                 | 130                  | 636                 | 642                |

| 71                | 1536                 | 130                  | 764                 | 770                |

| 72                | 1792                 | 258                  | 892                 | 898                |

| 73                | 2048                 | 258                  | 1020                | 1026               |

| 74                | 2304                 | 386                  | 1148                | 1154               |

| 75                | 2560                 | 386                  | 1276                | 1282               |

| 76                | 3072                 | 514                  | 1532                | 1538               |

| 77                | 3840                 | 514                  | 1916                | 1922               |

| 78                | 2560                 | 258                  | 1276                | 1282               |

| 79                | 3072                 | 258                  | 1532                | 1538               |

| 7A                | 3584                 | 514                  | 1788                | 1794               |

| 7B                | 4096                 | 514                  | 2044                | 2050               |

| 7C                | 4608                 | 770                  | 2300                | 2306               |

| 7D                | 5120                 | 770                  | 2556                | 2562               |

| 7E                | 6144                 | 1026                 | 3068                | 3074               |

| 7F                | 7680                 | 1026                 | 3836                | 3842               |

| 1UL=4             | <u>'</u>             |                      |                     |                    |

| 80                | 80                   | 28                   | 24                  | 44                 |

| 81                | 88                   | 28                   | 28                  | 48                 |

| 82                | 96                   | 32                   | 32                  | 52                 |

| 83                | 104                  | 32                   | 36                  | 56                 |

| 84                | 112                  | 36                   | 40                  | 60                 |

| 85                | 120                  | 36                   | 44                  | 64                 |

| 86                | 136                  | 40                   | 52                  | 72                 |

| 87                | 160                  | 40                   | 64                  | 84                 |

| 88                | 112                  | 28                   | 40                  | 60                 |

| 89                | 128                  | 28                   | 48                  | 68                 |

| 8A                | 144                  | 36                   | 56                  | 76                 |

| 8B                | 160                  | 36                   | 64                  | 84                 |

| 8C                | 176                  | 44                   | 72                  | 92                 |

| 8D                | 192                  | 44                   | 80                  | 100                |

| 8E                | 224                  | 52                   | 96                  | 116                |

| 8F                | 272                  | 52                   | 120                 | 140                |

| 90                | 192                  | 36                   | 72                  | 100                |

| 91                | 224                  | 36                   | 88                  | 116                |

| 92                | 256                  | 52                   | 104                 | 132                |

| 93                | 288                  | 52                   | 120                 | 148                |

| ن ن               | 200                  | J 2                  | 120                 | 140                |

| 94                | 320                  | 68                   | 136                 | 164                |

MC9S12KT256 Data Sheet, Rev. 1.16

## Table 9-7. IBSR Field Descriptions (continued)

| Field         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>IAAS     | Addressed as a Slave Bit — When its own specific address (I-bus address register) is matched with the calling address, this bit is set. The CPU is interrupted provided the IBIE is set. Then the CPU needs to check the SRW bit and set its Tx/Rx mode accordingly. Writing to the I-bus control register clears this bit.  0 Not addressed  1 Addressed as a slave                                                                                                                                                                                                                                                                                         |

| 5<br>IBB      | Bus Busy Bit  O This bit indicates the status of the bus. When a START signal is detected, the IBB is set. If a STOP signal is detected, IBB is cleared and the bus enters idle state.  1 Bus is busy                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4<br>IBAL     | Arbitration Lost — The arbitration lost bit (IBAL) is set by hardware when the arbitration procedure is lost.  Arbitration is lost in the following circumstances:  1. SDA sampled low when the master drives a high during an address or data transmit cycle.  2. SDA sampled low when the master drives a high during the acknowledge bit of a data receive cycle.  3. A start cycle is attempted when the bus is busy.  4. A repeated start cycle is requested in slave mode.  5. A stop condition is detected when the master did not request it.  This bit must be cleared by software, by writing a one to it. A write of 0 has no effect on this bit. |

| 3<br>RESERVED | Reserved — Bit 3 of IBSR is reserved for future use. A read operation on this bit will return 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2<br>SRW      | Slave Read/Write — When IAAS is set this bit indicates the value of the R/W command bit of the calling address sent from the master  This bit is only valid when the I-bus is in slave mode, a complete address transfer has occurred with an address match and no other transfers have been initiated.  Checking this bit, the CPU can select slave transmit/receive mode according to the command of the master.  Slave receive, master writing to slave  Slave transmit, master reading from slave                                                                                                                                                        |

| 1<br>IBIF     | I-Bus Interrupt — The IBIF bit is set when one of the following conditions occurs:  — Arbitration lost (IBAL bit set)  — Byte transfer complete (TCF bit set)  — Addressed as slave (IAAS bit set)  It will cause a processor interrupt request if the IBIE bit is set. This bit must be cleared by software, writing a one to it. A write of 0 has no effect on this bit.                                                                                                                                                                                                                                                                                   |

| 0<br>RXAK     | Received Acknowledge — The value of SDA during the acknowledge bit of a bus cycle. If the received acknowledge bit (RXAK) is low, it indicates an acknowledge signal has been received after the completion of 8 bits data transmission on the bus. If RXAK is high, it means no acknowledge signal is detected at the 9th clock.  O Acknowledge received  No acknowledge received                                                                                                                                                                                                                                                                           |

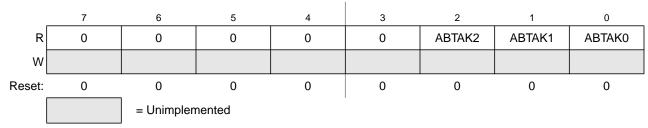

## 10.3.2.10 MSCAN Transmitter Message Abort Acknowledge Register (CANTAAK)

The CANTAAK register indicates the successful abort of a queued message, if requested by the appropriate bits in the CANTARQ register.

Module Base + 0x0009

Figure 10-13. MSCAN Transmitter Message Abort Acknowledge Register (CANTAAK)

#### **NOTE**

The CANTAAK register is held in the reset state when the initialization mode is active (INITRQ = 1 and INITAK = 1).

Read: Anytime

Write: Unimplemented for ABTAKx flags

Table 10-14. CANTAAK Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:0<br>ABTAK[2:0] | Abort Acknowledge — This flag acknowledges that a message was aborted due to a pending abort request from the CPU. After a particular message buffer is flagged empty, this flag can be used by the application software to identify whether the message was aborted successfully or was sent anyway. The ABTAKx flag is cleared whenever the corresponding TXE flag is cleared.  0 The message was not aborted.  1 The message was aborted. |

Chapter 10 Freescale's Scalable Controller Area Network (S12MSCANV2)

# 10.3.3 Programmer's Model of Message Storage

The following section details the organization of the receive and transmit message buffers and the associated control registers.

To simplify the programmer interface, the receive and transmit message buffers have the same outline. Each message buffer allocates 16 bytes in the memory map containing a 13 byte data structure.

An additional transmit buffer priority register (TBPR) is defined for the transmit buffers. Within the last two bytes of this memory map, the MSCAN stores a special 16-bit time stamp, which is sampled from an internal timer after successful transmission or reception of a message. This feature is only available for transmit and receiver buffers, if the TIME bit is set (see Section 10.3.2.1, "MSCAN Control Register 0 (CANCTL0)").

The time stamp register is written by the MSCAN. The CPU can only read these registers.

| Offset<br>Address | Register                                       | Access |

|-------------------|------------------------------------------------|--------|

| 0x00X0            | Identifier Register 0                          |        |

| 0x00X1            | Identifier Register 1                          |        |

| 0x00X2            | Identifier Register 2                          |        |

| 0x00X3            | Identifier Register 3                          |        |

| 0x00X4            | Data Segment Register 0                        |        |

| 0x00X5            | Data Segment Register 1                        |        |

| 0x00X6            | Data Segment Register 2                        |        |

| 0x00X7            | Data Segment Register 3                        |        |

| 0x00X8            | Data Segment Register 4                        |        |

| 0x00X9            | Data Segment Register 5                        |        |

| 0x00XA            | Data Segment Register 6                        |        |

| 0x00XB            | Data Segment Register 7                        |        |

| 0x00XC            | Data Length Register                           |        |

| 0x00XD            | Transmit Buffer Priority Register <sup>1</sup> |        |

| 0x00XE            | Time Stamp Register (High Byte) <sup>2</sup>   |        |

| 0x00XF            | Time Stamp Register (Low Byte) <sup>3</sup>    |        |

**Table 10-23. Message Buffer Organization**

Figure 10-23 shows the common 13-byte data structure of receive and transmit buffers for extended identifiers. The mapping of standard identifiers into the IDR registers is shown in Figure 10-24.

All bits of the receive and transmit buffers are 'x' out of reset because of RAM-based implementation<sup>1</sup>. All reserved or unused bits of the receive and transmit buffers always read 'x'.

MC9S12KT256 Data Sheet, Rev. 1.16

Not applicable for receive buffers

<sup>&</sup>lt;sup>2</sup> Read-only for CPU

<sup>&</sup>lt;sup>3</sup> Read-only for CPU

<sup>1.</sup> Exception: The transmit priority registers are 0 out of reset.

Chapter 14 Timer Module (TIM16B8CV1) Block Description

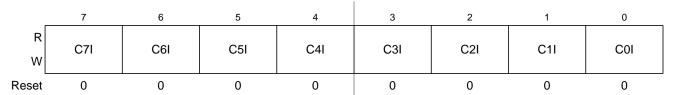

# 14.3.2.10 Timer Interrupt Enable Register (TIE)

Module Base + 0x000C

Figure 14-18. Timer Interrupt Enable Register (TIE)

Read: Anytime Write: Anytime.

**Table 14-14. TIE Field Descriptions**

| Field          | Description                                                                                                                                                                                                                                                                              |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>C7I:C0I | Input Capture/Output Compare "x" Interrupt Enable — The bits in TIE correspond bit-for-bit with the bits in the TFLG1 status register. If cleared, the corresponding flag is disabled from causing a hardware interrupt. If set, the corresponding flag is enabled to cause a interrupt. |

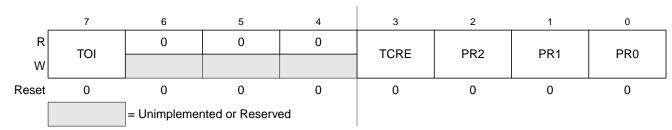

# 14.3.2.11 Timer System Control Register 2 (TSCR2)

Module Base + 0x000D

Figure 14-19. Timer System Control Register 2 (TSCR2)

Read: Anytime

Write: Anytime.

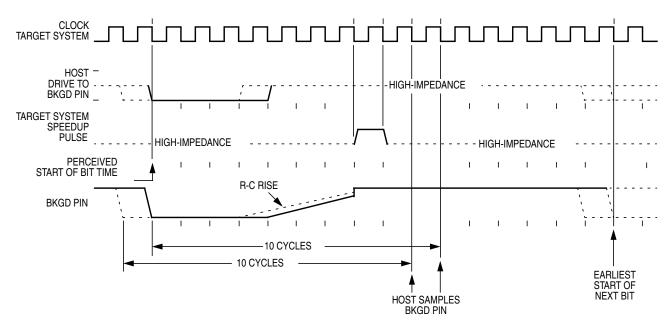

Figure 16-8. BDM Target-to-Host Serial Bit Timing (Logic 1)

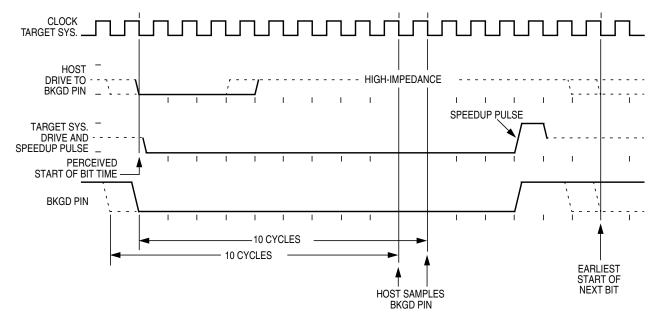

Figure 16-9 shows the host receiving a logic 0 from the target. Because the host is asynchronous to the target, there is up to a one clock-cycle delay from the host-generated falling edge on BKGD to the start of the bit time as perceived by the target. The host initiates the bit time but the target finishes it. Because the target wants the host to receive a logic 0, it drives the BKGD pin low for 13 target clock cycles then briefly drives it high to speed up the rising edge. The host samples the bit level about 10 target clock cycles after starting the bit time.

Figure 16-9. BDM Target-to-Host Serial Bit Timing (Logic 0)

This register is not in the on-chip memory map in expanded and special peripheral modes. Therefore, these accesses will be echoed externally.

#### **NOTE**

These bits have no effect when the associated pin(s) are outputs. (The pull resistors are inactive.)

Table 19-9. PUCR Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                              |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>PUPKE | Pull resistors Port K Enable 0 Port K pull resistors are disabled. 1 Enable pull resistors for port K input pins.                                                                                                                                                        |

| 4<br>PUPEE | Pull resistors Port E Enable 0 Port E pull resistors on bits 7, 4:0 are disabled. 1 Enable pull resistors for port E input pins bits 7, 4:0. Note: Pins 5 and 6 of port E have pull resistors which are only enabled during reset. This bit has no effect on these pins. |

| 1<br>PUPBE | Pull resistors Port B Enable 0 Port B pull resistors are disabled. 1 Enable pull resistors for all port B input pins.                                                                                                                                                    |

| 0<br>PUPAE | Pull resistors Port A Enable 0 Port A pull resistors are disabled. 1 Enable pull resistors for all port A input pins.                                                                                                                                                    |

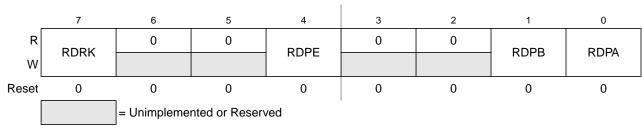

#### 19.3.2.11 Reduced Drive Register (RDRIV)

Module Base + 0x000D

Starting address location affected by INITRG register setting.

Figure 19-15. Reduced Drive Register (RDRIV)

Read: Anytime (provided this register is in the map)

Write: Anytime (provided this register is in the map)

This register is used to select reduced drive for the pins associated with the core ports. This gives reduced power consumption and reduced RFI with a slight increase in transition time (depending on loading). This feature would be used on ports which have a light loading. The reduced drive function is independent of which function is being used on a particular port.

This register is not in the on-chip memory map in expanded and special peripheral modes. Therefore, these accesses will be echoed externally.

MC9S12KT256 Data Sheet, Rev. 1.16

# Table A-5. Thermal Package Characteristics<sup>1</sup>

| Num | С | Rating                                                                           | Symbol        | Min | Тур | Max | Unit |

|-----|---|----------------------------------------------------------------------------------|---------------|-----|-----|-----|------|

| 1   | Т | Thermal Resistance LQFP112, single sided PCB <sup>2</sup>                        | $\theta_{JA}$ | _   | _   | 54  | °C/W |

| 2   | Т | Thermal Resistance LQFP112, double sided PCB with 2 internal planes <sup>3</sup> | $\theta_{JA}$ | _   | _   | 41  | °C/W |

| 3   | Т | Thermal Resistance QFP 80, single sided PCB                                      | $\theta_{JA}$ | _   | _   | 51  | °C/W |

| 4   | Т | Thermal Resistance QFP 80, double sided PCB with 2 internal planes               | $\theta_{JA}$ | _   | _   | 41  | °C/W |

<sup>1</sup> The values for thermal resistance are achieved by package simulations

<sup>&</sup>lt;sup>2</sup> PC Board according to EIA/JEDEC Standard 51-2

<sup>&</sup>lt;sup>3</sup> PC Board according to EIA/JEDEC Standard 51-7

**Appendix A Electrical Characteristics**

## A.7.1.5 Pseudo Stop and Wait Recovery

The recovery from Pseudo STOP and Wait are essentially the same since the oscillator was not stopped in both modes. The controller can be woken up by internal or external interrupts. After t<sub>wrs</sub> the CPU starts fetching the interrupt vector.

#### A.7.2 Oscillator

The device features an internal low-power loop controlled Pierce oscillator and a full swing Pierce oscillator/external clock mode. The selection of loop controlled Pierce oscillator or full swing Pierce oscillator/external clock depends on the XCLKS signal which is sampled during reset. Full swing Pierce oscillator/external clock mode allows the input of a square wave. Before asserting the oscillator to the internal system clocks the quality of the oscillation is checked for each start from either power-on, STOP or oscillator fail.  $t_{\rm CQOUT}$  specifies the maximum time before switching to the internal self clock mode after POR or STOP if a proper oscillation is not detected. The quality check also determines the minimum oscillator start-up time  $t_{\rm UPOSC}$ . The device also features a clock monitor. A Clock Monitor Failure is asserted if the frequency of the incoming clock signal is below the Assert Frequency  $t_{\rm CMFA}$ .

**Table A-19. Oscillator Characteristics**

| Conditions are shown in Table A-4 unless otherwise noted |   |                                                   |                        |                          |                |                          |      |

|----------------------------------------------------------|---|---------------------------------------------------|------------------------|--------------------------|----------------|--------------------------|------|

| Num                                                      | С | Rating                                            | Symbol                 | Min                      | Тур            | Max                      | Unit |

| 1a                                                       | С | Crystal oscillator range (loop controlled Pierce) | f <sub>OSC</sub>       | 4.0                      | _              | 16                       | MHz  |

| 1b                                                       | С | Crystal oscillator range (full swing Pierce) 1,2  | fosc                   | 0.5                      | _              | 40                       | MHz  |

| 2                                                        | Р | Startup Current                                   | iosc                   | 100                      | _              | _                        | μΑ   |

| 3                                                        | С | Oscillator start-up time (loop controlled Pierce) | t <sub>UPOSC</sub>     | _                        | 3 <sup>3</sup> | 50 <sup>4</sup>          | ms   |

| 4                                                        | D | Clock Quality check time-out                      | tcqout                 | 0.45                     |                | 2.5                      | s    |

| 5                                                        | Р | Clock Monitor Failure Assert Frequency            | f <sub>CMFA</sub>      | 50                       | 100            | 200                      | KHz  |

| 6                                                        | Р | External square wave input frequency              | f <sub>EXT</sub>       | 0.5                      | _              | 50                       | MHz  |

| 7                                                        | D | External square wave pulse width low              | t <sub>EXTL</sub>      | 9.5                      | _              | _                        | ns   |

| 8                                                        | D | External square wave pulse width high             | t <sub>EXTH</sub>      | 9.5                      | _              | _                        | ns   |

| 9                                                        | D | External square wave rise time                    | t <sub>EXTR</sub>      | _                        | _              | 1                        | ns   |

| 10                                                       | D | External square wave fall time                    | t <sub>EXTF</sub>      | _                        | _              | 1                        | ns   |

| 11                                                       | D | Input Capacitance (EXTAL, XTAL pins)              | C <sub>IN</sub>        | _                        | 7              | _                        | pF   |

| 12                                                       | Р | EXTAL Pin Input High Voltage                      | V <sub>IH,EXTAL</sub>  | 0.75*V <sub>DDPLL</sub>  | _              | _                        | V    |

|                                                          | Т | EXTAL Pin Input High Voltage                      | V <sub>IH,EXTAL</sub>  |                          |                | V <sub>DDPLL</sub> + 0.3 | V    |

| 13                                                       | Р | EXTAL Pin Input Low Voltage                       | V <sub>IL,EXTAL</sub>  |                          |                | 0.25*V <sub>DDPLL</sub>  | V    |

|                                                          | Т | EXTAL Pin Input Low Voltage                       | V <sub>IL,EXTAL</sub>  | V <sub>SSPLL</sub> – 0.3 | _              | _                        | V    |

| 14                                                       | С | EXTAL Pin Input Hysteresis                        | V <sub>HYS,EXTAL</sub> | _                        | 250            | _                        | mV   |

<sup>&</sup>lt;sup>1</sup> Depending on the crystal a damping series resistor might be necessary

MC9S12KT256 Data Sheet, Rev. 1.16

<sup>&</sup>lt;sup>2</sup> Only valid if full swing Pierce oscillator/external clock mode is selected

$<sup>^{3}</sup>$  f<sub>OSC</sub> = 4MHz, C = 22pF.

<sup>&</sup>lt;sup>4</sup> Maximum value is for extreme cases using high Q, low frequency crystals