Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                       |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 39                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 4K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 13x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-LQFP                                                               |

| Supplier Device Package    | 48-TQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f031c6t7 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|   |       | 6.3.20   | Communication interfaces                |

|---|-------|----------|-----------------------------------------|

| 7 | Packa | age info | rmation                                 |

|   | 7.1   | LQFP4    | 8 package information                   |

|   | 7.2   | LQFP32   | 2 package information                   |

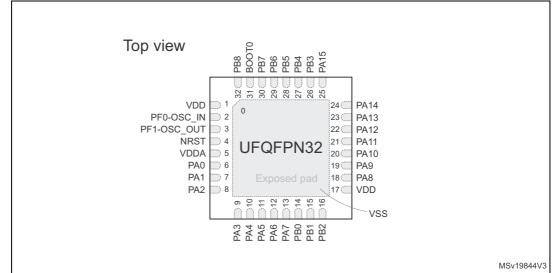

|   | 7.3   | UFQFP    | N32 package information 86              |

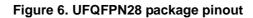

|   | 7.4   | UFQFP    | N28 package information                 |

|   | 7.5   | WLCSF    | 25 package information                  |

|   | 7.6   | TSSOP    | 20 package information                  |

|   | 7.7   | Therma   | I characteristics                       |

|   |       | 7.7.1    | Reference document                      |

|   |       | 7.7.2    | Selecting the product temperature range |

| 8 | Orde  | ring inf | ormation                                |

| 9 | Revis | ion hist | tory                                    |

| I/O AC characteristics                             | . 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NRST pin characteristics                           | . 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ADC characteristics                                | . 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| R <sub>AIN</sub> max for f <sub>ADC</sub> = 14 MHz | . 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TS characteristics                                 | . 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| V <sub>BAT</sub> monitoring characteristics        | . 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TIMx characteristics                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| IWDG min/max timeout period at 40 kHz (LSI)        | . 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| WWDG min/max timeout value at 48 MHz (PCLK)        | . 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| I <sup>2</sup> C analog filter characteristics     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SPI characteristics                                | . 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| I <sup>2</sup> S characteristics                   | . 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| LQFP48 package mechanical data                     | . 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| LQFP32 package mechanical data                     | . 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| UFQFPN32 package mechanical data                   | . 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| UFQFPN28 package mechanical data                   | . 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| WLCSP25 package mechanical data                    | . 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| WLCSP25 recommended PCB design rules               | . 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TSSOP20 package mechanical data                    | . 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Package thermal characteristics                    | . 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Ordering information scheme                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Document revision history                          | 103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                    | NRST pin characteristics         ADC characteristics         R <sub>AIN</sub> max for f <sub>ADC</sub> = 14 MHz.         ADC accuracy.         TS characteristics         V <sub>BAT</sub> monitoring characteristics         TIMx characteristics         IWDG min/max timeout period at 40 kHz (LSI).         WWDG min/max timeout value at 48 MHz (PCLK).         I <sup>2</sup> C analog filter characteristics         SPI characteristics         LQFP48 package mechanical data.         LQFP48 package mechanical data.         UFQFPN32 package mechanical data         UFQFPN28 package mechanical data         WLCSP25 package mechanical data         WLCSP25 recommended PCB design rules         TSSOP20 package mechanical data         Package thermal characteristics.         Ordering information scheme |

# 3 Functional overview

*Figure 1* shows the general block diagram of the STM32F031x4/x6 devices.

# 3.1 ARM<sup>®</sup>-Cortex<sup>®</sup>-M0 core

The ARM<sup>®</sup> Cortex<sup>®</sup>-M0 is a generation of ARM 32-bit RISC processors for embedded systems. It has been developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced system response to interrupts.

The ARM<sup>®</sup> Cortex<sup>®</sup>-M0 processors feature exceptional code-efficiency, delivering the high performance expected from an ARM core, with memory sizes usually associated with 8- and 16-bit devices.

The STM32F031x4/x6 devices embed ARM core and are compatible with all ARM tools and software.

# 3.2 Memories

The device has the following features:

- 4 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states and featuring embedded parity checking with exception generation for fail-critical applications.

- The non-volatile memory is divided into two arrays:

- 16 to 32 Kbytes of embedded Flash memory for programs and data

- Option bytes

The option bytes are used to write-protect the memory (with 4 KB granularity) and/or readout-protect the whole memory with the following options:

- Level 0: no readout protection

- Level 1: memory readout protection, the Flash memory cannot be read from or written to if either debug features are connected or boot in RAM is selected

- Level 2: chip readout protection, debug features (Cortex<sup>®</sup>-M0 serial wire) and boot in RAM selection disabled

# 3.3 Boot modes

At startup, the boot pin and boot selector option bit are used to select one of the three boot options:

- boot from User Flash memory

- boot from System Memory

- boot from embedded SRAM

The boot loader is located in System Memory. It is used to reprogram the Flash memory by using USART on pins PA14/PA15 or PA9/PA10.

# **3.8** Direct memory access controller (DMA)

The 5-channel general-purpose DMAs manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers.

The DMA supports circular buffer management, removing the need for user code intervention when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with support for software trigger on each channel. Configuration is made by software and transfer sizes between source and destination are independent.

DMA can be used with the main peripherals: SPIx, I2Sx, I2Cx, USARTx, all TIMx timers (except TIM14) and ADC.

# 3.9 Interrupts and events

#### 3.9.1 Nested vectored interrupt controller (NVIC)

The STM32F0xx family embeds a nested vectored interrupt controller able to handle up to 32 maskable interrupt channels (not including the 16 interrupt lines of Cortex<sup>®</sup>-M0) and 4 priority levels.

- Closely coupled NVIC gives low latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of late arriving higher priority interrupts

- Support for tail-chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimal interrupt latency.

## 3.9.2 Extended interrupt/event controller (EXTI)

The extended interrupt/event controller consists of 24 edge detector lines used to generate interrupt/event requests and wake-up the system. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the internal clock period. Up to 39 GPIOs can be connected to the 16 external interrupt lines.

# 3.10 Analog-to-digital converter (ADC)

The 12-bit analog-to-digital converter has up to 16 external and 3 internal (temperature sensor, voltage reference, VBAT voltage measurement) channels and performs conversions in single-shot or scan modes. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC can be served by the DMA controller.

| USART modes/features <sup>(1)</sup>         | USART1 |

|---------------------------------------------|--------|

| Hardware flow control for modem             | Х      |

| Continuous communication using DMA          | Х      |

| Multiprocessor communication                | Х      |

| Synchronous mode                            | Х      |

| Smartcard mode                              | Х      |

| Single-wire half-duplex communication       | Х      |

| IrDA SIR ENDEC block                        | Х      |

| LIN mode                                    | Х      |

| Dual clock domain and wakeup from Stop mode | Х      |

| Receiver timeout interrupt                  | Х      |

| Modbus communication                        | Х      |

| Auto baud rate detection                    | Х      |

| Driver Enable                               | Х      |

|                                             | •      |

| Table 8. STM32F031x4/x6 | <b>USART</b> im | plementation |

|-------------------------|-----------------|--------------|

|-------------------------|-----------------|--------------|

1. X = supported.

# 3.15 Serial peripheral interface (SPI) / Inter-integrated sound interface (I<sup>2</sup>S)

The SPI is able to communicate up to 18 Mbit/s in slave and master modes in full-duplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame size is configurable from 4 bits to 16 bits.

One standard I<sup>2</sup>S interface (multiplexed with SPI1) supporting four different audio standards can operate as master or slave at half-duplex communication mode. It can be configured to transfer 16 and 24 or 32 bits with 16-bit or 32-bit data resolution and synchronized by a specific signal. Audio sampling frequency from 8 kHz up to 192 kHz can be set by an 8-bit programmable linear prescaler. When operating in master mode, it can output a clock for an external audio component at 256 times the sampling frequency.

| Table 9. STM32F031x4/x6 SPI/I <sup>2</sup> S implementation | ion |

|-------------------------------------------------------------|-----|

|                                                             |     |

| SPI features <sup>(1)</sup> | SPI |

|-----------------------------|-----|

| Hardware CRC calculation    | Х   |

| Rx/Tx FIFO                  | Х   |

| NSS pulse mode              | Х   |

| I <sup>2</sup> S mode       | Х   |

| TI mode                     | Х   |

1. X = supported.

#### Pinouts and pin description

Figure 5. UFQFPN32 package pinout

|        |           | Pin nı           | umbe      | r         |           |                                      |          |               |       | Pin fund                                                                     | ctions                          |

|--------|-----------|------------------|-----------|-----------|-----------|--------------------------------------|----------|---------------|-------|------------------------------------------------------------------------------|---------------------------------|

| LQFP48 | LQFP32    | UFQFPN32         | UFQFPN28  | WLCSP25   | TSSOP20   | Pin name<br>(function upon<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                          | Additional<br>functions         |

| 6      | 3         | 3                | 3         | B5        | 3         | PF1-OSC_OUT<br>(PF1)                 | I/O      | FT            | -     | -                                                                            | OSC_OUT                         |

| 7      | 4         | 4                | 4         | C5        | 4         | NRST                                 | I/O      | RST           | -     | Device reset input / in<br>(active                                           |                                 |

| 8      | 16<br>(3) | 0 <sup>(3)</sup> | 16<br>(3) | E1<br>(3) | 15<br>(3) | VSSA                                 | S        |               | -     | Analog g                                                                     | round                           |

| 9      | 5         | 5                | 5         | D5        | 5         | VDDA                                 | S        |               | -     | Analog pow                                                                   | er supply                       |

| 10     | 6         | 6                | 6         | B4        | 6         | PA0                                  | I/O      | ТТа           | -     | TIM2_CH1_ETR,<br>USART1_CTS                                                  | ADC_IN0,<br>RTC_TAMP2,<br>WKUP1 |

| 11     | 7         | 7                | 7         | C4        | 7         | PA1                                  | I/O      | ТТа           | -     | TIM2_CH2,<br>EVENTOUT,<br>USART1_RTS                                         | ADC_IN1                         |

| 12     | 8         | 8                | 8         | D4        | 8         | PA2                                  | I/O      | ТТа           | -     | TIM2_CH3,<br>USART1_TX                                                       | ADC_IN2                         |

| 13     | 9         | 9                | 9         | E5        | 9         | PA3                                  | I/O      | ТТа           | -     | TIM2_CH4,<br>USART1_RX                                                       | ADC_IN3                         |

| 14     | 10        | 10               | 10        | В3        | 10        | PA4                                  | I/O      | ТТа           | -     | SPI1_NSS,<br>I2S1_WS,<br>TIM14_CH1,<br>USART1_CK                             | ADC_IN4                         |

| 15     | 11        | 11               | 11        | C3        | 11        | PA5                                  | I/O      | ТТа           | -     | SPI1_SCK,<br>I2S1_CK,<br>TIM2_CH1_ETR                                        | ADC_IN5                         |

| 16     | 12        | 12               | 12        | D3        | 12        | PA6                                  | I/O      | ТТа           | -     | SPI1_MISO,<br>I2S1_MCK,<br>TIM3_CH1,<br>TIM1_BKIN,<br>TIM16_CH1,<br>EVENTOUT | ADC_IN6                         |

Table 11. Pin definitions (continued)

| Bus | Boundary address          | Size | Peripheral |

|-----|---------------------------|------|------------|

|     | 0x4000 7400 - 0x4000 7FFF | 3KB  | Reserved   |

|     | 0x4000 7000 - 0x4000 73FF | 1KB  | PWR        |

|     | 0x4000 5800 - 0x4000 6FFF | 6KB  | Reserved   |

|     | 0x4000 5400 - 0x4000 57FF | 1KB  | I2C1       |

|     | 0x4000 3400 - 0x4000 53FF | 8KB  | Reserved   |

|     | 0x4000 3000 - 0x4000 33FF | 1KB  | IWDG       |

| APB | 0x4000 2C00 - 0x4000 2FFF | 1KB  | WWDG       |

|     | 0x4000 2800 - 0x4000 2BFF | 1KB  | RTC        |

|     | 0x4000 2400 - 0x4000 27FF | 1KB  | Reserved   |

|     | 0x4000 2000 - 0x4000 23FF | 1KB  | TIM14      |

|     | 0x4000 0800 - 0x4000 1FFF | 6KB  | Reserved   |

|     | 0x4000 0400 - 0x4000 07FF | 1KB  | TIM3       |

|     | 0x4000 0000 - 0x4000 03FF | 1KB  | TIM2       |

# Table 14. STM32F031x4/x6 peripheral register boundary addresses (continued)

# 6 Electrical characteristics

# 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

## 6.1.1 Minimum and maximum values

Unless otherwise specified, the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean  $\pm 3\sigma$ ).

## 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = V_{DDA} = 3.3$  V. They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean  $\pm 2\sigma$ ).

#### 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

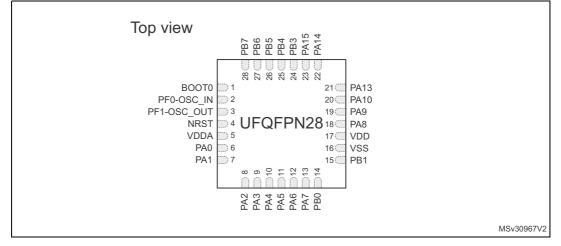

## 6.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 10*.

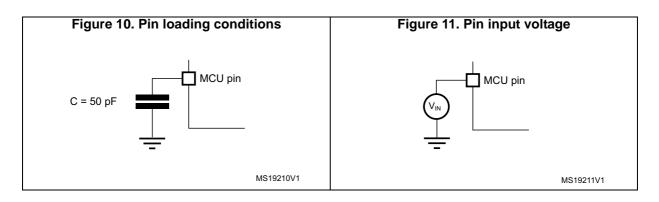

#### 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 11*.

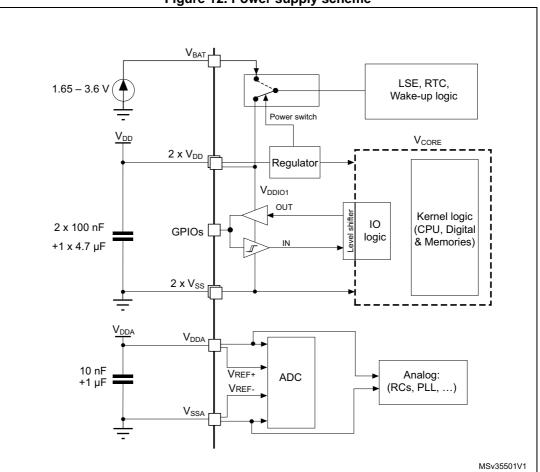

## 6.1.6 Power supply scheme

Figure 12. Power supply scheme

**Caution:** Each power supply pair (V<sub>DD</sub>/V<sub>SS</sub>, V<sub>DDA</sub>/V<sub>SSA</sub> etc.) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below, the appropriate pins on the underside of the PCB to ensure the good functionality of the device.

# 6.3 **Operating conditions**

# 6.3.1 General operating conditions

| Symbol            | Parameter                                                                                                         | Conditions                           | Min      | Max                                  | Unit   |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------|--------------------------------------|--------|--|

| f <sub>HCLK</sub> | Internal AHB clock frequency                                                                                      | -                                    | 0        | 48                                   | MHz    |  |

| f <sub>PCLK</sub> | Internal APB clock frequency                                                                                      | -                                    | 0        | 48                                   | IVITIZ |  |

| V <sub>DD</sub>   | Standard operating voltage                                                                                        | -                                    | 2.0      | 3.6                                  | V      |  |

| V                 | Analog operating voltage (ADC not used)                                                                           | Must have a potential equal          | $V_{DD}$ | 3.6                                  | V      |  |

| V <sub>DDA</sub>  | Analog operating voltage (ADC used)                                                                               | to or higher than $V_{DD}$           | 2.4      | 3.6                                  | V      |  |

| V <sub>BAT</sub>  | Backup operating voltage                                                                                          | -                                    | 1.65     | 3.6                                  | V      |  |

|                   |                                                                                                                   | TC and RST I/O                       | -0.3     | V <sub>DDIOx</sub> +0.3              |        |  |

| V                 | I/O input voltage                                                                                                 | TTa I/O                              | -0.3     | V <sub>DDA</sub> +0.3 <sup>(1)</sup> | V      |  |

| V <sub>IN</sub>   |                                                                                                                   | FT and FTf I/O                       | -0.3     | 5.5 <sup>(1)</sup>                   |        |  |

|                   |                                                                                                                   | BOOT0                                | 0        | 5.5                                  |        |  |

|                   |                                                                                                                   | LQFP48                               | -        | 364                                  | mW     |  |

|                   |                                                                                                                   | UFQFPN32                             | -        | 526                                  |        |  |

| P <sub>D</sub>    | Power dissipation at $T_A = 85 \degree C$<br>for suffix 6 or $T_A = 105 \degree C$ for<br>suffix 7 <sup>(2)</sup> | LQFP32                               | -        | 357                                  |        |  |

| Γ <sub>D</sub>    |                                                                                                                   | UFQFPN28                             | -        | 169                                  | IIIVV  |  |

|                   |                                                                                                                   | WLCSP25                              | -        | 267                                  |        |  |

|                   |                                                                                                                   | TSSOP20                              | -        | 182                                  |        |  |

|                   | Ambient temperature for the                                                                                       | Maximum power dissipation            | -40      | 85                                   | °C     |  |

| Та                | suffix 6 version                                                                                                  | Low power dissipation <sup>(3)</sup> | -40      | 105                                  | °C     |  |

| IA                | Ambient temperature for the                                                                                       | Maximum power dissipation            | -40      | 105                                  | °C     |  |

|                   | suffix 7 version                                                                                                  | Low power dissipation <sup>(3)</sup> | -40      | 125                                  | C      |  |

| ТJ                | Junction temperature range                                                                                        | Suffix 6 version                     | -40      | 105                                  | °C     |  |

| IJ                |                                                                                                                   | Suffix 7 version                     | -40      | 125                                  | ĴĴ     |  |

#### Table 18. General operating conditions

1. For operation with a voltage higher than  $V_{DDIOx}$  + 0.3 V, the internal pull-up resistor must be disabled.

2. If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}$ . See Section 7.7: Thermal characteristics.

In low power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>Jmax</sub> (see Section 7.7: Thermal characteristics).

# 6.3.2 Operating conditions at power-up / power-down

The parameters given in *Table 19* are derived from tests performed under the ambient temperature condition summarized in *Table 18*.

# 6.3.6 Wakeup time from low-power mode

The wakeup times given in *Table 30* are the latency between the event and the execution of the first user instruction. The device goes in low-power mode after the WFE (Wait For Event) instruction, in the case of a WFI (Wait For Interruption) instruction, 16 CPU cycles must be added to the following timings due to the interrupt latency in the Cortex M0 architecture.

The SYSCLK clock source setting is kept unchanged after wakeup from Sleep mode. During wakeup from Stop or Standby mode, SYSCLK takes the default setting: HSI 8 MHz.

The wakeup source from Sleep and Stop mode is an EXTI line configured in event mode. The wakeup source from Standby mode is the WKUP1 pin (PA0).

All timings are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 18: General operating conditions*..

| Symbol     | Parameter                              | Conditions                  | Typ @Vdd = Vdda |         |         |       |         | Max | Unit |

|------------|----------------------------------------|-----------------------------|-----------------|---------|---------|-------|---------|-----|------|

|            |                                        |                             | = 2.0 V         | = 2.4 V | = 2.7 V | = 3 V | = 3.3 V | wax | Unit |

| twustop    | Wakeup from Stop<br><sup>DP</sup> mode | Regulator in run<br>mode    | 3.2             | 3.1     | 2.9     | 2.9   | 2.8     | 5   |      |

|            |                                        | Regulator in low power mode | 7.0             | 5.8     | 5.2     | 4.9   | 4.6     | 9   |      |

| twustandby | Wakeup from<br>Standby mode            | -                           | 60.4            | 55.6    | 53.5    | 52    | 51      | -   | μs   |

| twusleep   | Wakeup from Sleep<br>mode              | Wakeup from Sleep           |                 |         |         |       | -       |     |      |

Table 30. Low-power mode wakeup timings

# 6.3.7 External clock source characteristics

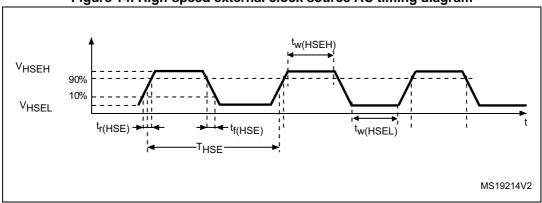

#### High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO.

The external clock signal has to respect the I/O characteristics in Section 6.3.14. However, the recommended clock input waveform is shown in *Figure 14: High-speed external clock source AC timing diagram*.

| Symbol                                       | Parameter <sup>(1)</sup>             | Min                    | Тур | Max                    | Unit |

|----------------------------------------------|--------------------------------------|------------------------|-----|------------------------|------|

| f <sub>HSE_ext</sub>                         | User external clock source frequency | -                      | 8   | 32                     | MHz  |

| V <sub>HSEH</sub>                            | OSC_IN input pin high level voltage  | 0.7 V <sub>DDIOx</sub> | -   | V <sub>DDIOx</sub>     | V    |

| V <sub>HSEL</sub>                            | OSC_IN input pin low level voltage   | V <sub>SS</sub>        | -   | 0.3 V <sub>DDIOx</sub> | v    |

| t <sub>w(HSEH)</sub><br>t <sub>w(HSEL)</sub> | OSC_IN high or low time              | 15                     | -   | -                      | ns   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub>   | OSC_IN rise or fall time             | -                      | -   | 20                     | 113  |

Table 31. High-speed external user clock characteristics

1. Guaranteed by design, not tested in production.

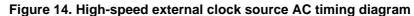

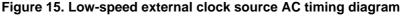

#### Low-speed external user clock generated from an external source

In bypass mode the LSE oscillator is switched off and the input pin is a standard GPIO.

The external clock signal has to respect the I/O characteristics in *Section 6.3.14*. However, the recommended clock input waveform is shown in *Figure 15*.

| Symbol                                       | Parameter <sup>(1)</sup>              | Min                    | Тур    | Max                    | Unit |

|----------------------------------------------|---------------------------------------|------------------------|--------|------------------------|------|

| f <sub>LSE_ext</sub>                         | User external clock source frequency  | -                      | 32.768 | 1000                   | kHz  |

| V <sub>LSEH</sub>                            | OSC32_IN input pin high level voltage | 0.7 V <sub>DDIOx</sub> | -      | V <sub>DDIOx</sub>     | V    |

| $V_{LSEL}$                                   | OSC32_IN input pin low level voltage  | V <sub>SS</sub>        | -      | 0.3 V <sub>DDIOx</sub> | v    |

| t <sub>w(LSEH)</sub><br>t <sub>w(LSEL)</sub> | OSC32_IN high or low time             | 450                    | -      | -                      | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub>   | OSC32_IN rise or fall time            | -                      | -      | 50                     | 115  |

Table 32. Low-speed external user clock characteristics

1. Guaranteed by design, not tested in production.

#### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 32 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 33*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                  | Parameter                   | Conditions <sup>(1)</sup>                                   | Min <sup>(2)</sup> | Тур | Max <sup>(2)</sup> | Unit |

|-------------------------|-----------------------------|-------------------------------------------------------------|--------------------|-----|--------------------|------|

| f <sub>OSC_IN</sub>     | Oscillator frequency        | -                                                           | 4                  | 8   | 32                 | MHz  |

| R <sub>F</sub>          | Feedback resistor           | -                                                           | -                  | 200 | -                  | kΩ   |

|                         |                             | During startup <sup>(3)</sup>                               | -                  | -   | 8.5                |      |

|                         |                             | V <sub>DD</sub> = 3.3 V,<br>Rm = 30 Ω,<br>CL = 10 pF@8 MHz  | -                  | 0.4 | -                  |      |

|                         |                             | V <sub>DD</sub> = 3.3 V,<br>Rm = 45 Ω,<br>CL = 10 pF@8 MHz  | -                  | 0.5 | -                  |      |

| I <sub>DD</sub>         | HSE current consumption     | V <sub>DD</sub> = 3.3 V,<br>Rm = 30 Ω,<br>CL = 5 pF@32 MHz  | -                  | 0.8 | -                  | mA   |

|                         |                             | V <sub>DD</sub> = 3.3 V,<br>Rm = 30 Ω,<br>CL = 10 pF@32 MHz | -                  | 1   | -                  |      |

|                         |                             | V <sub>DD</sub> = 3.3 V,<br>Rm = 30 Ω,<br>CL = 20 pF@32 MHz | -                  | 1.5 | -                  |      |

| 9 <sub>m</sub>          | Oscillator transconductance | Startup                                                     | 10                 | -   | -                  | mA/V |

| $t_{\rm SU(HSE)}^{(4)}$ | Startup time                | V <sub>DD</sub> is stabilized                               | -                  | 2   | -                  | ms   |

| Table 33. HSE oscillator characteristics | Table | 33. | HSE | oscillator | characteristics |

|------------------------------------------|-------|-----|-----|------------|-----------------|

|------------------------------------------|-------|-----|-----|------------|-----------------|

1. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

2. Guaranteed by design, not tested in production.

3. This consumption level occurs during the first 2/3 of the  $t_{\mbox{SU(HSE)}}$  startup time

t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 20 pF range (Typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 16*).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ .

Note: For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

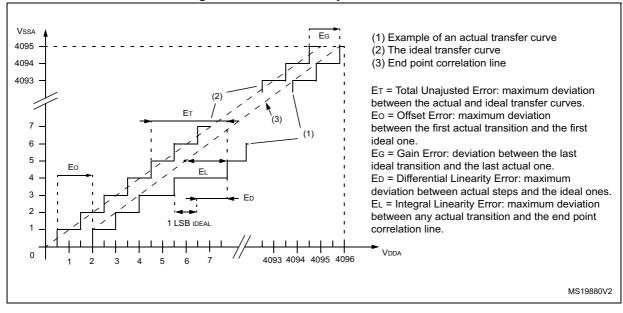

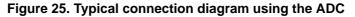

#### Figure 24. ADC accuracy characteristics

Refer to Table 50: ADC characteristics for the values of  $\mathsf{R}_{AIN},\,\mathsf{R}_{ADC}$  and  $\mathsf{C}_{ADC}.$ 1.

$C_{parasitic}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high  $C_{parasitic}$  value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced. 2.

#### **General PCB design guidelines**

Power supply decoupling should be performed as shown in Figure 12: Power supply scheme. The 10 nF capacitor should be ceramic (good quality) and it should be placed as close as possible to the chip.

| Prescaler divider | PR[2:0] bits | Min timeout RL[11:0]=<br>0x000 | Max timeout RL[11:0]=<br>0xFFF | Unit |

|-------------------|--------------|--------------------------------|--------------------------------|------|

| /4                | 0            | 0.1                            | 409.6                          |      |

| /8                | 1            | 0.2                            | 819.2                          |      |

| /16               | 2            | 0.4                            | 1638.4                         |      |

| /32               | 3            | 0.8                            | 3276.8                         | ms   |

| /64               | 4            | 1.6                            | 6553.6                         |      |

| /128              | 5            | 3.2                            | 13107.2                        |      |

| /256              | 6 or 7       | 6.4                            | 26214.4                        |      |

Table 56. IWDG min/max timeout period at 40 kHz (LSI)<sup>(1)</sup>

1. These timings are given for a 40 kHz clock but the microcontroller internal RC frequency can vary from 30 to 60 kHz. Moreover, given an exact RC oscillator frequency, the exact timings still depend on the phasing of the APB interface clock versus the LSI clock so that there is always a full RC period of uncertainty.

| Prescaler | WDGTB | Min timeout value | Max timeout value | Unit |

|-----------|-------|-------------------|-------------------|------|

| 1         | 0     | 0.0853            | 5.4613            |      |

| 2         | 1     | 0.1706            | 10.9226           | me   |

| 4         | 2     | 0.3413            | 21.8453           | ms   |

| 8         | 3     | 0.6826            | 43.6906           |      |

Table 57. WWDG min/max timeout value at 48 MHz (PCLK)

## 6.3.20 Communication interfaces

## I<sup>2</sup>C interface characteristics

The  $I^2C$  interface meets the timings requirements of the  $I^2C$ -bus specification and user manual rev. 03 for:

- Standard-mode (Sm): with a bit rate up to 100 kbit/s

- Fast-mode (Fm): with a bit rate up to 400 kbit/s

- Fast-mode Plus (Fm+): with a bit rate up to 1 Mbit/s.

The I<sup>2</sup>C timings requirements are guaranteed by design when the I2Cx peripheral is properly configured (refer to Reference manual).

The SDA and SCL I/O requirements are met with the following restrictions: the SDA and SCL I/O pins are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and  $V_{DDIOx}$  is disabled, but is still present. Only FTf I/O pins support Fm+ low level output current maximum requirement. Refer to Section 6.3.14: I/O port characteristics for the I<sup>2</sup>C I/Os characteristics.

All I<sup>2</sup>C SDA and SCL I/Os embed an analog filter. Refer to the table below for the analog filter characteristics:

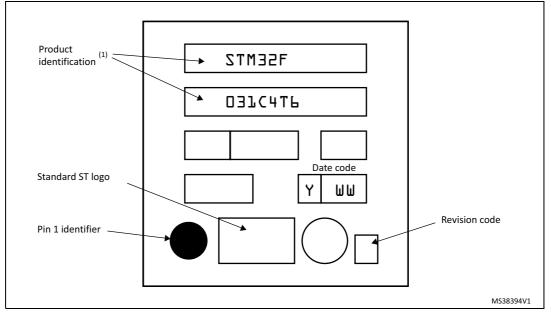

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

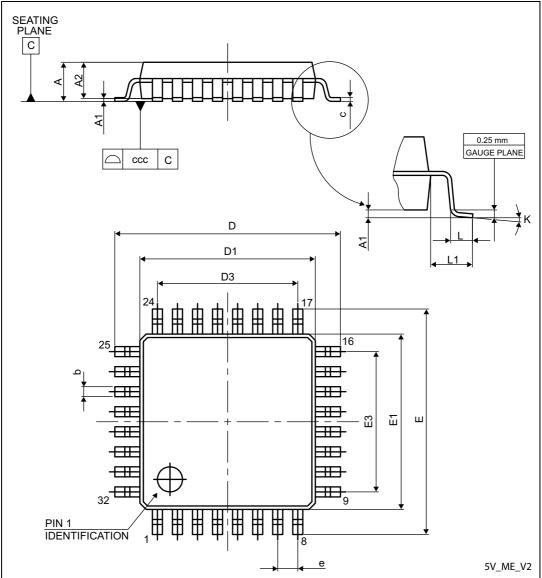

# 7.2 LQFP32 package information

LQFP32 is a 32-pin, 7 x 7 mm low-profile quad flat package.

Figure 34. LQFP32 package outline

1. Drawing is not to scale.

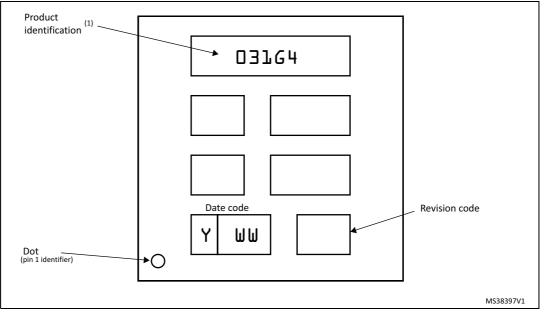

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

#### Figure 42. UFQFPN28 package marking example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

# 9 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13-Jan-2014 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11-Jul-2014 | 2        | <ul> <li>Changed the document status to Datasheet - production data.</li> <li>Updated the following: <ul> <li>Table: STM32F031x4/6 family device features and peripheral counts,</li> <li>Figure: Clock tree,</li> <li>Figure: Power supply scheme,</li> <li>Table: Peripheral current consumption.</li> </ul> </li> <li>Replaced Table Typical current consumption in Run mode, code with data processing running from Flash and Table Typical current consumption in Sleep mode, code running from Flash or RAM with Table: Typical current consumption from Flash, running from HSE 8 MHz crystal.</li> <li>Added the LQFP32 package: updates in Section: Description, Section: Pinouts and pin description and Section: Package information.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 28-Aug-2015 | 3        | <ul> <li>Updated:</li> <li><i>Figure 9:</i> STM32F031x6 memory map</li> <li>AF1 alternate functions for PA0, PA1, PA2, PA3 and PA4 in Table 12: Alternate functions selected through <i>GPIOA_AFR</i> registers for port <i>A</i></li> <li>the footnote for V<sub>IN</sub> max value in Table 15: Voltage characteristics</li> <li>the footnote for max V<sub>IN</sub> in Table 18: General operating conditions</li> <li>Table 22: Embedded internal reference voltage with the addition of t<sub>START</sub> parameter</li> <li>Table 50: ADC characteristics</li> <li>Table 53: TS characteristics: removed the min. value for t<sub>START</sub> parameter</li> <li>the typical value for R parameter in Table 54: VBAT monitoring characteristics</li> <li>the structure of Section 7: Package information.</li> <li>Added:</li> <li>Figure 33: LQFP48 marking example (package top view), Figure 39: UFQFPN32 marking example (package top view), Figure 39: UFQFPN32 marking example (package top view), Figure 42: UFQFPN28 marking example (package top view), Figure 42: UFQFPN28 marking example (package top view), Figure 42: TSSOP20 marking example (package top view)</li> </ul> |