## E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                       |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 15                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 4K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 12x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 20-TSSOP (0.173", 4.40mm Width)                                       |

| Supplier Device Package    | 20-TSSOP                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f031f6p6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| I/O AC characteristics                             | . 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NRST pin characteristics                           | . 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ADC characteristics                                | . 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| R <sub>AIN</sub> max for f <sub>ADC</sub> = 14 MHz | . 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TS characteristics                                 | . 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| V <sub>BAT</sub> monitoring characteristics        | . 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TIMx characteristics                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| IWDG min/max timeout period at 40 kHz (LSI)        | . 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| WWDG min/max timeout value at 48 MHz (PCLK)        | . 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| I <sup>2</sup> C analog filter characteristics     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SPI characteristics                                | . 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| I <sup>2</sup> S characteristics                   | . 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| LQFP48 package mechanical data                     | . 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| LQFP32 package mechanical data                     | . 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| UFQFPN32 package mechanical data                   | . 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

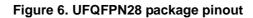

| UFQFPN28 package mechanical data                   | . 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| WLCSP25 package mechanical data                    | . 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| WLCSP25 recommended PCB design rules               | . 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TSSOP20 package mechanical data                    | . 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Package thermal characteristics                    | . 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Ordering information scheme                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Document revision history                          | 103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                    | NRST pin characteristics         ADC characteristics         R <sub>AIN</sub> max for f <sub>ADC</sub> = 14 MHz.         ADC accuracy.         TS characteristics         V <sub>BAT</sub> monitoring characteristics         TIMx characteristics         IWDG min/max timeout period at 40 kHz (LSI).         WWDG min/max timeout value at 48 MHz (PCLK).         I <sup>2</sup> C analog filter characteristics         SPI characteristics         LQFP48 package mechanical data.         LQFP48 package mechanical data.         UFQFPN32 package mechanical data         UFQFPN28 package mechanical data         WLCSP25 package mechanical data         WLCSP25 recommended PCB design rules         TSSOP20 package mechanical data         Package thermal characteristics.         Ordering information scheme |

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

## 3.10.1 Temperature sensor

The temperature sensor (TS) generates a voltage  $V_{\mbox{SENSE}}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode.

| Calibration value name | Description                                                                                                | Memory address            |

|------------------------|------------------------------------------------------------------------------------------------------------|---------------------------|

| TS_CAL1                | TS ADC raw data acquired at a temperature of 30 °C ( $\pm$ 5 °C), V <sub>DDA</sub> = 3.3 V ( $\pm$ 10 mV)  | 0x1FFF F7B8 - 0x1FFF F7B9 |

| TS_CAL2                | TS ADC raw data acquired at a temperature of 110 °C ( $\pm$ 5 °C), V <sub>DDA</sub> = 3.3 V ( $\pm$ 10 mV) | 0x1FFF F7C2 - 0x1FFF F7C3 |

Table 3. Temperature sensor calibration values

## 3.10.2 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. The precise voltage of  $V_{REFINT}$  is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode.

|                        | ternar venage reference ea                                                        |                           |  |  |

|------------------------|-----------------------------------------------------------------------------------|---------------------------|--|--|

| Calibration value name | Description                                                                       | Memory address            |  |  |

| VREFINT_CAL            | Raw data acquired at a temperature of 30 °C (± 5 °C), $V_{DDA}$ = 3.3 V (± 10 mV) | 0x1FFF F7BA - 0x1FFF F7BB |  |  |

| Table 4. Internal voltage reference calibration value | es |

|-------------------------------------------------------|----|

|-------------------------------------------------------|----|

## 3.10.3 V<sub>BAT</sub> battery voltage monitoring

This embedded hardware feature allows the application to measure the V<sub>BAT</sub> battery voltage using the internal ADC channel ADC\_IN18. As the V<sub>BAT</sub> voltage may be higher than V<sub>DDA</sub>, and thus outside the ADC input range, the V<sub>BAT</sub> pin is internally connected to a bridge divider by 2. As a consequence, the converted digital value is half the V<sub>BAT</sub> voltage.

## TIM2, TIM3

STM32F031x4/x6 devices feature two synchronizable 4-channel general-purpose timers. TIM2 is based on a 32-bit auto-reload up/downcounter and a 16-bit prescaler. TIM3 is based on a 16-bit auto-reload up/downcounter and a 16-bit prescaler. They feature 4 independent channels each for input capture/output compare, PWM or one-pulse mode output. This gives up to 12 input captures/output compares/PWMs on the largest packages.

The TIM2 and TIM3 general-purpose timers can work together or with the TIM1 advancedcontrol timer via the Timer Link feature for synchronization or event chaining.

TIM2 and TIM3 both have independent DMA request generation.

These timers are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors.

Their counters can be frozen in debug mode.

#### TIM14

This timer is based on a 16-bit auto-reload upcounter and a 16-bit prescaler.

TIM14 features one single channel for input capture/output compare, PWM or one-pulse mode output.

Its counter can be frozen in debug mode.

#### TIM16 and TIM17

Both timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler.

They each have a single channel for input capture/output compare, PWM or one-pulse mode output.

TIM16 and TIM17 have a complementary output with dead-time generation and independent DMA request generation.

Their counters can be frozen in debug mode.

### 3.11.3 Independent watchdog (IWDG)

The independent watchdog is based on an 8-bit prescaler and 12-bit downcounter with user-defined refresh window. It is clocked from an independent 40 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free running timer for application timeout management. It is hardware or software configurable through the option bytes. The counter can be frozen in debug mode.

## 3.11.4 System window watchdog (WWDG)

The system window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the APB clock (PCLK). It has an early warning interrupt capability and the counter can be frozen in debug mode.

| Aspect                              | Analog filter                                         | Digital filter                                                                                           |  |  |  |  |  |  |  |

|-------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Pulse width of<br>suppressed spikes | ≥ 50 ns                                               | Programmable length from 1 to 15<br>I2Cx peripheral clocks                                               |  |  |  |  |  |  |  |

| Benefits                            | Available in Stop mode                                | <ul> <li>Extra filtering capability vs.</li> <li>standard requirements</li> <li>Stable length</li> </ul> |  |  |  |  |  |  |  |

| Drawbacks                           | Variations depending on temperature, voltage, process | Wakeup from Stop on address<br>match is not available when digital<br>filter is enabled.                 |  |  |  |  |  |  |  |

## Table 6. Comparison of I<sup>2</sup>C analog and digital filters

In addition, I2C1 provides hardware support for SMBUS 2.0 and PMBUS 1.1: ARP capability, Host notify protocol, hardware CRC (PEC) generation/verification, timeouts verifications and ALERT protocol management. I2C1 also has a clock domain independent from the CPU clock, allowing the I2C1 to wake up the MCU from Stop mode on address match.

The I2C peripheral can be served by the DMA controller.

| I <sup>2</sup> C features <sup>(1)</sup>                     | I2C1 |

|--------------------------------------------------------------|------|

| 7-bit addressing mode                                        | Х    |

| 10-bit addressing mode                                       | Х    |

| Standard mode (up to 100 kbit/s)                             | Х    |

| Fast mode (up to 400 kbit/s)                                 | Х    |

| Fast Mode Plus with 20 mA output drive I/Os (up to 1 Mbit/s) | Х    |

| Independent clock                                            | Х    |

| SMBus                                                        | Х    |

| Wakeup from STOP                                             | Х    |

Table 7. STM32F031x4/x6 I<sup>2</sup>C implementation

1. X = supported.

# 3.14 Universal synchronous/asynchronous receiver/transmitter (USART)

The device embeds one universal synchronous/asynchronous receiver/transmitter (USART1) which communicates at speeds of up to 6 Mbit/s.

It provides hardware management of the CTS, RTS and RS485 DE signals, multiprocessor communication mode, master synchronous communication and single-wire half-duplex communication mode. USART1 supports also SmartCard communication (ISO 7816), IrDA SIR ENDEC, LIN Master/Slave capability and auto baud rate feature, and has a clock domain independent of the CPU clock, allowing to wake up the MCU from Stop mode.

The USART interface can be served by the DMA controller.

## 3.16 Serial wire debug port (SW-DP)

An ARM SW-DP interface is provided to allow a serial wire debugging tool to be connected to the MCU.

## Pinouts and pin description

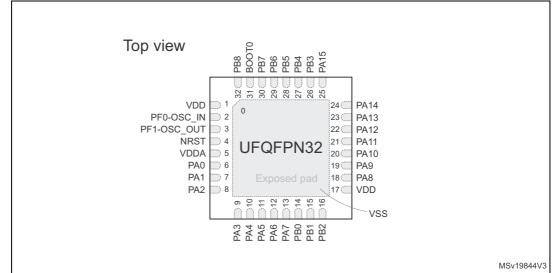

Figure 5. UFQFPN32 package pinout

| Na               | me                   | Abbreviation                                                                                     | Definition                                                                                            |  |  |  |  |  |

|------------------|----------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin n            | name                 |                                                                                                  | e specified in brackets below the pin name, the pin function reset is the same as the actual pin name |  |  |  |  |  |

|                  |                      | S                                                                                                | Supply pin                                                                                            |  |  |  |  |  |

| Pin              | type                 | I                                                                                                | Input-only pin                                                                                        |  |  |  |  |  |

|                  |                      | I/O                                                                                              | Input / output pin                                                                                    |  |  |  |  |  |

|                  |                      | FT                                                                                               | 5 V-tolerant I/O                                                                                      |  |  |  |  |  |

|                  |                      | FTf 5 V-tolerant I/O, FM+ capable                                                                |                                                                                                       |  |  |  |  |  |

| I/O atr          |                      | TTa 3.3 V-tolerant I/O directly connected to ADC                                                 |                                                                                                       |  |  |  |  |  |

| i/O str          | ucture               | TC                                                                                               | TC Standard 3.3V I/O                                                                                  |  |  |  |  |  |

|                  |                      | В                                                                                                | B Dedicated BOOT0 pin                                                                                 |  |  |  |  |  |

|                  |                      | RST                                                                                              | Bidirectional reset pin with embedded weak pull-up resiste                                            |  |  |  |  |  |

| No               | tes                  | Unless otherwise specified by a note, all I/Os are set as floating inputs during and after reset |                                                                                                       |  |  |  |  |  |

| 5.               | Alternate functions  | Functions select                                                                                 | Functions selected through GPIOx_AFR registers                                                        |  |  |  |  |  |

| Pin<br>functions | Additional functions | Functions direct                                                                                 | ly selected/enabled through peripheral registers                                                      |  |  |  |  |  |

#### Table 10. Legend/abbreviations used in the pinout table

|        | F      | Pin nu   | umbe     | r       |         |                                      |          |               |        | Pin fund            | ctions                                     |

|--------|--------|----------|----------|---------|---------|--------------------------------------|----------|---------------|--------|---------------------|--------------------------------------------|

| LQFP48 | LQFP32 | UFQFPN32 | UFQFPN28 | WLCSP25 | TSSOP20 | Pin name<br>(function upon<br>reset) | Pin type | I/O structure | Notes  | Alternate functions | Additional<br>functions                    |

| 1      | -      | -        | -        | -       | -       | VBAT                                 | S        | -             | -      | Backup pow          | er supply                                  |

| 2      | -      | -        | -        | -       | -       | PC13                                 | I/O      | тс            | (1)(2) | -                   | RTC_TAMP1,<br>RTC_TS,<br>RTC_OUT,<br>WKUP2 |

| 3      | -      | -        | -        | -       | -       | PC14-OSC32_IN<br>(PC14)              | I/O      | тс            | (1)(2) | -                   | OSC32_IN                                   |

| 4      | -      | -        | -        | -       | -       | PC15-<br>OSC32_OUT<br>(PC15)         | I/O      | тс            | (1)(2) | -                   | OSC32_OUT                                  |

| 5      | 2      | 2        | 2        | A5      | 2       | PF0-OSC_IN<br>(PF0)                  | I/O      | FT            | -      | -                   | OSC_IN                                     |

#### Table 11. Pin definitions

|        | F      | Pin nu   | umbe     | r       |         |                                      |          |               |       | Pin functions                                                   |                         |  |

|--------|--------|----------|----------|---------|---------|--------------------------------------|----------|---------------|-------|-----------------------------------------------------------------|-------------------------|--|

| LQFP48 | LQFP32 | UFQFPN32 | UFQFPN28 | WLCSP25 | TSSOP20 | Pin name<br>(function upon<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                             | Additional<br>functions |  |

| 41     | 28     | 28       | 26       | C2      | -       | PB5                                  | I/O      | FT            | -     | SPI1_MOSI,<br>I2S1_SD,<br>I2C1_SMBA,<br>TIM16_BKIN,<br>TIM3_CH2 | -                       |  |

| 42     | 29     | 29       | 27       | B2      | -       | PB6                                  | I/O      | FTf           | -     | I2C1_SCL,<br>USART1_TX,<br>TIM16_CH1N                           | -                       |  |

| 43     | 30     | 30       | 28       | A3      | -       | PB7                                  | I/O      | FTf           | -     | I2C1_SDA,<br>USART1_RX,<br>TIM17_CH1N                           | -                       |  |

| 44     | 31     | 31       | 1        | A4      | 1       | BOOT0                                | I        | В             | -     | Boot memory                                                     | / selection             |  |

| 45     | -      | 32       | -        | -       | -       | PB8                                  | I/O      | FTf           | (4)   | I2C1_SCL,<br>TIM16_CH1                                          | -                       |  |

| 46     | -      | -        | -        | -       | -       | PB9                                  | I/O      | FTf           | -     | I2C1_SDA,<br>IR_OUT,<br>TIM17_CH1,<br>EVENTOUT                  | -                       |  |

| 47     | 32     | 0        | -        | E1      | -       | VSS                                  | S        | -             | -     | Ground                                                          |                         |  |

| 48     | 1      | 1        | -        | -       | -       | VDD                                  | S        | -             | -     | Digital powe                                                    | er supply               |  |

Table 11. Pin definitions (continued)

PC13, PC14 and PC15 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 in output mode is limited:

The speed should not exceed 2 MHz with a maximum load of 30 pF

The speed should not exceed 2 MHz with a maximum load of 30 pF

These GPIOs must not be used as current sources (e.g. to drive an LED).

After the first RTC domain power-up, PC13, PC14 and PC15 operate as GPIOs. Their function then depends on the content

of the RTC registers which are not reset by the system reset. For details on how to manage these GPIOs, refer to the RTC

domain and RTC register descriptions in the reference manual.

3. VSSA pin is not in package pinout. VSSA pad of the die is connected to VSS pin.

4. On the LQFP32 package, PB2 and PB8 should be treated as unconnected pins (even when they are not available on the package, they are not forced to a defined level by hardware).

5. After reset, these pins are configured as SWDIO and SWCLK alternate functions, and the internal pull-up on the SWDIO pin and the internal pull-down on the SWCLK pin are activated.

6. On the WLCSP25 package, PB3, PB4 and PA15 must be set to defined levels by software, as their corresponding pads on the silicon die are left unconnected. Apply same recommendations as for unconnected pins.

trigger circuits used to discriminate the input value. Unless this specific configuration is required by the application, this supply current consumption can be avoided by configuring these I/Os in analog mode. This is notably the case of ADC input pins which should be configured as analog inputs.

**Caution:** Any floating input pin can also settle to an intermediate voltage level or switch inadvertently, as a result of external electromagnetic noise. To avoid current consumption related to floating pins, they must either be configured in analog mode, or forced internally to a definite digital value. This can be done either by using pull-up/down resistors or by configuring the pins in output mode.

#### I/O dynamic current consumption

In addition to the internal peripheral current consumption measured previously (see *Table 29: Peripheral current consumption*), the I/Os used by an application also contribute to the current consumption. When an I/O pin switches, it uses the current from the I/O supply voltage to supply the I/O pin circuitry and to charge/discharge the capacitive load (internal or external) connected to the pin:

$$I_{SW} = V_{DDIOx} \times f_{SW} \times C$$

where

$I_{SW}$  is the current sunk by a switching I/O to charge/discharge the capacitive load

V<sub>DDIOx</sub> is the I/O supply voltage

$\rm f_{SW}$  is the I/O switching frequency

C is the total capacitance seen by the I/O pin: C =  $C_{INT}$  +  $C_{EXT}$  +  $C_S$

$C_S$  is the PCB board capacitance including the pad pin.

The test pin is configured in push-pull output mode and is toggled by software at a fixed frequency.

## 6.3.6 Wakeup time from low-power mode

The wakeup times given in *Table 30* are the latency between the event and the execution of the first user instruction. The device goes in low-power mode after the WFE (Wait For Event) instruction, in the case of a WFI (Wait For Interruption) instruction, 16 CPU cycles must be added to the following timings due to the interrupt latency in the Cortex M0 architecture.

The SYSCLK clock source setting is kept unchanged after wakeup from Sleep mode. During wakeup from Stop or Standby mode, SYSCLK takes the default setting: HSI 8 MHz.

The wakeup source from Sleep and Stop mode is an EXTI line configured in event mode. The wakeup source from Standby mode is the WKUP1 pin (PA0).

All timings are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 18: General operating conditions*..

| Symbol     | Parameter                           | Conditions                  | Typ @Vdd = Vdda |         |         |       |         | Max | Unit |

|------------|-------------------------------------|-----------------------------|-----------------|---------|---------|-------|---------|-----|------|

| Symbol     | Farameter                           |                             | = 2.0 V         | = 2.4 V | = 2.7 V | = 3 V | = 3.3 V |     | Unit |

| IMULOTOD   | Wakeup from Stop<br>mode            | Regulator in run<br>mode    | 3.2             | 3.1     | 2.9     | 2.9   | 2.8     | 5   |      |

|            |                                     | Regulator in low power mode | 7.0             | 5.8     | 5.2     | 4.9   | 4.6     | 9   |      |

| twustandby | Wakeup from<br>Standby mode         | -                           | 60.4            | 55.6    | 53.5    | 52    | 51      | -   | μs   |

| twusleep   | Wakeup from Sleep - 4 SYSCLK cycles |                             |                 |         |         |       | -       |     |      |

Table 30. Low-power mode wakeup timings

## 6.3.7 External clock source characteristics

## High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO.

The external clock signal has to respect the I/O characteristics in Section 6.3.14. However, the recommended clock input waveform is shown in *Figure 14: High-speed external clock source AC timing diagram*.

| Symbol                                       | Parameter <sup>(1)</sup>             | Min                    | Тур | Max                    | Unit |

|----------------------------------------------|--------------------------------------|------------------------|-----|------------------------|------|

| f <sub>HSE_ext</sub>                         | User external clock source frequency | -                      | 8   | 32                     | MHz  |

| V <sub>HSEH</sub>                            | OSC_IN input pin high level voltage  | 0.7 V <sub>DDIOx</sub> | -   | V <sub>DDIOx</sub>     | V    |

| V <sub>HSEL</sub>                            | OSC_IN input pin low level voltage   | V <sub>SS</sub>        | -   | 0.3 V <sub>DDIOx</sub> | v    |

| t <sub>w(HSEH)</sub><br>t <sub>w(HSEL)</sub> | OSC_IN high or low time              | 15                     | -   | -                      | ns   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub>   | OSC_IN rise or fall time             | -                      | -   | 20                     | 115  |

Table 31. High-speed external user clock characteristics

## Low-speed internal (LSI) RC oscillator

| Table 37. | LSI | oscillator | characteristics <sup>(1)</sup> |

|-----------|-----|------------|--------------------------------|

|-----------|-----|------------|--------------------------------|

| Symbol                               | Parameter                        | Min | Тур  | Max | Unit |

|--------------------------------------|----------------------------------|-----|------|-----|------|

| f <sub>LSI</sub>                     | Frequency                        | 30  | 40   | 50  | kHz  |

| t <sub>su(LSI)</sub> <sup>(2)</sup>  | LSI oscillator startup time      | -   | -    | 85  | μs   |

| I <sub>DDA(LSI)</sub> <sup>(2)</sup> | LSI oscillator power consumption | -   | 0.75 | 1.2 | μΑ   |

1. V<sub>DDA</sub> = 3.3 V, T<sub>A</sub> = –40 to 105  $^\circ\text{C}$  unless otherwise specified.

2. Guaranteed by design, not tested in production.

## 6.3.9 PLL characteristics

The parameters given in *Table 38* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 18: General operating conditions*.

| Symbol                | Parameter                      |                   | Unit |                    |      |  |

|-----------------------|--------------------------------|-------------------|------|--------------------|------|--|

| Symbol                | Faranieler                     | Min               | Тур  | Max                | Onit |  |

| f                     | PLL input clock <sup>(1)</sup> | 1 <sup>(2)</sup>  | 8.0  | 24 <sup>(2)</sup>  | MHz  |  |

| f <sub>PLL_IN</sub>   | PLL input clock duty cycle     | 40 <sup>(2)</sup> | -    | 60 <sup>(2)</sup>  | %    |  |

| f <sub>PLL_OUT</sub>  | PLL multiplier output clock    | 16 <sup>(2)</sup> | -    | 48                 | MHz  |  |

| t <sub>LOCK</sub>     | PLL lock time                  | -                 | -    | 200 <sup>(2)</sup> | μs   |  |

| Jitter <sub>PLL</sub> | Cycle-to-cycle jitter          | -                 | -    | 300 <sup>(2)</sup> | ps   |  |

Table 38. PLL characteristics

1. Take care to use the appropriate multiplier factors to obtain PLL input clock values compatible with the range defined by f<sub>PLL\_OUT</sub>.

2. Guaranteed by design, not tested in production.

## 6.3.10 Memory characteristics

## **Flash memory**

The characteristics are given at  $T_A = -40$  to 105 °C unless otherwise specified.

| Table 39. Flash memory characterist | cs |

|-------------------------------------|----|

|-------------------------------------|----|

| Symbol             | Parameter               | Conditions                       | Min | Тур  | Max <sup>(1)</sup> | Unit |

|--------------------|-------------------------|----------------------------------|-----|------|--------------------|------|

| t <sub>prog</sub>  | 16-bit programming time | T <sub>A</sub> = - 40 to +105 °C | 40  | 53.5 | 60                 | μs   |

| t <sub>ERASE</sub> | Page (1 KB) erase time  | T <sub>A</sub> = - 40 to +105 °C | 20  | -    | 40                 | ms   |

| t <sub>ME</sub>    | Mass erase time         | T <sub>A</sub> = - 40 to +105 °C | 20  | -    | 40                 | ms   |

|                    | Supply ourrant          | Write mode                       | -   | -    | 10                 | mA   |

| IDD                | Supply current          | Erase mode                       | -   | -    | 12                 | mA   |

1. Guaranteed by design, not tested in production.

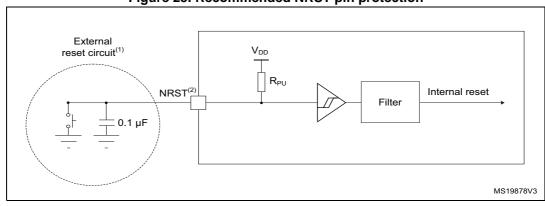

Figure 23. Recommended NRST pin protection

1. The external capacitor protects the device against parasitic resets.

The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 49: NRST pin characteristics. Otherwise the reset will not be taken into account by the device.

## 6.3.16 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 50* are derived from tests performed under the conditions summarized in *Table 18: General operating conditions*.

Note: It is recommended to perform a calibration after each power-up.

| Symbol                             | Parameter                                     | Conditions                                            | Min   | Тур | Max                | Unit               |

|------------------------------------|-----------------------------------------------|-------------------------------------------------------|-------|-----|--------------------|--------------------|

| V <sub>DDA</sub>                   | Analog supply voltage for ADC ON              | -                                                     | 2.4   | -   | 3.6                | V                  |

| I <sub>DDA (ADC)</sub>             | Current consumption of the ADC <sup>(1)</sup> | V <sub>DDA</sub> = 3.3 V                              | -     | 0.9 | -                  | mA                 |

| f <sub>ADC</sub>                   | ADC clock frequency                           | -                                                     | 0.6   | -   | 14                 | MHz                |

| f <sub>S</sub> <sup>(2)</sup>      | Sampling rate                                 | 12-bit resolution                                     | 0.043 | -   | 1                  | MHz                |

| f <sub>TRIG</sub> <sup>(2)</sup>   | External trigger frequency                    | f <sub>ADC</sub> = 14 MHz,<br>12-bit resolution       | -     | -   | 823                | kHz                |

|                                    |                                               | 12-bit resolution                                     | -     | -   | 17                 | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub>                   | Conversion voltage range                      | -                                                     | 0     | -   | V <sub>DDA</sub>   | V                  |

| R <sub>AIN</sub> <sup>(2)</sup>    | External input impedance                      | See <i>Equation 1</i> and <i>Table 51</i> for details | -     | -   | 50                 | kΩ                 |

| R <sub>ADC</sub> <sup>(2)</sup>    | Sampling switch resistance                    | -                                                     | -     | -   | 1                  | kΩ                 |

| C <sub>ADC</sub> <sup>(2)</sup>    | Internal sample and hold capacitor            | -                                                     | -     | -   | 8                  | pF                 |

| <b>↓</b> (2)(3)                    | Calibration time                              | f <sub>ADC</sub> = 14 MHz                             |       | 5.9 |                    | μs                 |

| t <sub>CAL</sub> <sup>(2)(3)</sup> |                                               | - 83                                                  |       |     | 1/f <sub>ADC</sub> |                    |

Table 50. ADC characteristics

| Prescaler divider | PR[2:0] bits | Min timeout RL[11:0]=<br>0x000 | Max timeout RL[11:0]=<br>0xFFF | Unit |  |  |  |  |

|-------------------|--------------|--------------------------------|--------------------------------|------|--|--|--|--|

| /4                | 0            | 0.1                            | 409.6                          |      |  |  |  |  |

| /8                | 1            | 0.2                            | 819.2                          |      |  |  |  |  |

| /16               | 2            | 0.4                            | 1638.4                         |      |  |  |  |  |

| /32               | 3            | 0.8                            | 3276.8                         | ms   |  |  |  |  |

| /64               | 4            | 1.6                            | 6553.6                         |      |  |  |  |  |

| /128              | 5            | 3.2                            | 13107.2                        |      |  |  |  |  |

| /256              | 6 or 7       | 6.4                            | 26214.4                        |      |  |  |  |  |

Table 56. IWDG min/max timeout period at 40 kHz (LSI)<sup>(1)</sup>

1. These timings are given for a 40 kHz clock but the microcontroller internal RC frequency can vary from 30 to 60 kHz. Moreover, given an exact RC oscillator frequency, the exact timings still depend on the phasing of the APB interface clock versus the LSI clock so that there is always a full RC period of uncertainty.

| Prescaler | WDGTB | Min timeout value | Max timeout value | Unit |

|-----------|-------|-------------------|-------------------|------|

| 1         | 0     | 0.0853            | 5.4613            |      |

| 2         | 1     | 0.1706 10.9226    |                   | me   |

| 4         | 2     | 0.3413 21.8453    |                   | ms   |

| 8         | 3     | 0.6826            | 43.6906           |      |

Table 57. WWDG min/max timeout value at 48 MHz (PCLK)

## 6.3.20 Communication interfaces

## I<sup>2</sup>C interface characteristics

The  $I^2C$  interface meets the timings requirements of the  $I^2C$ -bus specification and user manual rev. 03 for:

- Standard-mode (Sm): with a bit rate up to 100 kbit/s

- Fast-mode (Fm): with a bit rate up to 400 kbit/s

- Fast-mode Plus (Fm+): with a bit rate up to 1 Mbit/s.

The I<sup>2</sup>C timings requirements are guaranteed by design when the I2Cx peripheral is properly configured (refer to Reference manual).

The SDA and SCL I/O requirements are met with the following restrictions: the SDA and SCL I/O pins are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and  $V_{DDIOx}$  is disabled, but is still present. Only FTf I/O pins support Fm+ low level output current maximum requirement. Refer to Section 6.3.14: I/O port characteristics for the I<sup>2</sup>C I/Os characteristics.

All I<sup>2</sup>C SDA and SCL I/Os embed an analog filter. Refer to the table below for the analog filter characteristics:

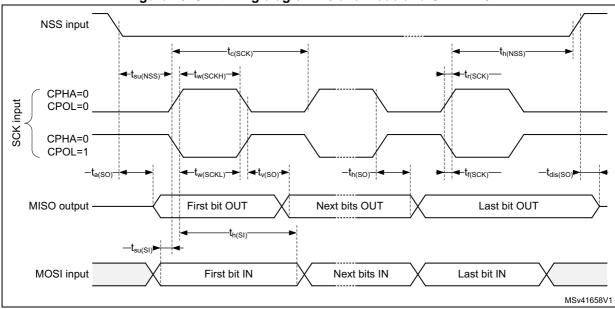

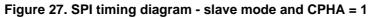

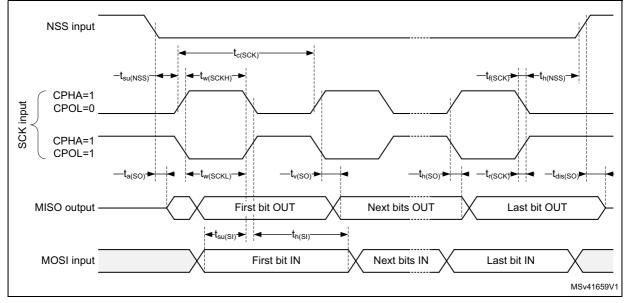

Figure 26. SPI timing diagram - slave mode and CPHA = 0

1. Measurement points are done at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}$

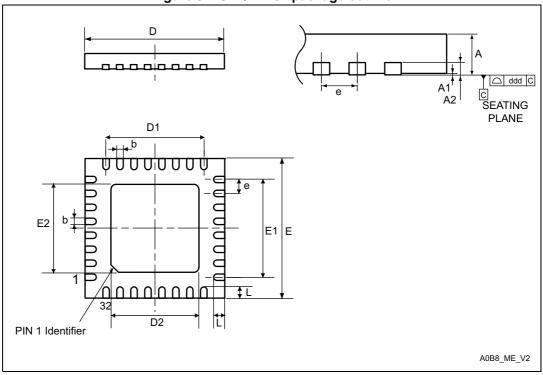

Figure 37. UFQFPN32 package outline

1. Drawing is not to scale.

- 2. All leads/pads should also be soldered to the PCB to improve the lead/pad solder joint life.

- 3. There is an exposed die pad on the underside of the UFQFPN package. This pad is used for the device ground and must be connected. It is referred to as pin 0 in *Table: Pin definitions*.

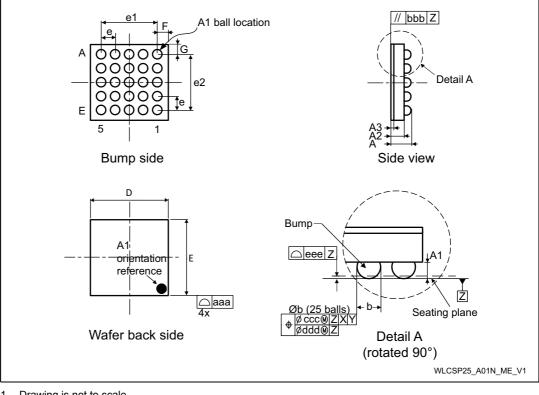

#### WLCSP25 package information 7.5

WLCSP25 is a 25-ball, 2.423 x 2.325 mm, 0.4 mm pitch wafer level chip scale package.

1. Drawing is not to scale.

| Symbol               |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|----------------------|-------|-------------|-------|--------|-----------------------|--------|

| Symbol               | Min   | Тур         | Max   | Min    | Тур                   | Max    |

| А                    | 0.525 | 0.555       | 0.585 | 0.0207 | 0.0219                | 0.0230 |

| A1                   | -     | 0.175       | -     | -      | 0.0069                | -      |

| A2                   | -     | 0.380       | -     | -      | 0.0150                | -      |

| A3 <sup>(2)</sup>    | -     | 0.025       | -     | -      | 0.0010                | -      |

| b <sup>(3) (4)</sup> | 0.220 | 0.250       | 0.280 | 0.0087 | 0.0098                | 0.0110 |

| D                    | 2.388 | 2.423       | 2.458 | 0.0940 | 0.0954                | 0.0968 |

| E                    | 2.29  | 2.325       | 2.36  | 0.0902 | 0.0915                | 0.0929 |

| е                    | -     | 0.400       | -     | -      | 0.0157                | -      |

| e1                   | -     | 1.600       | -     | -      | 0.0630                | -      |

| e2                   | -     | 1.600       | -     | -      | 0.0630                | -      |

| F                    | -     | 0.4115      | -     | -      | 0.0162                | -      |

| G                    | -     | 0.3625      | -     | -      | 0.0143                | -      |

| Table 05. WEOOT 25 package mechanical data (continued) |     |             |     |     |                       |     |

|--------------------------------------------------------|-----|-------------|-----|-----|-----------------------|-----|

| Symbol                                                 |     | millimeters |     |     | inches <sup>(1)</sup> |     |

| Symbol                                                 | Min | Тур         | Max | Min | Тур                   | Max |

| aaa                                                    | -   | 0.100       | -   | -   | 0.0039                | -   |

| bbb                                                    | -   | 0.100       | -   | -   | 0.0039                | -   |

| CCC                                                    | -   | 0.100       | -   | -   | 0.0039                | -   |

| ddd                                                    | -   | 0.050       | -   | -   | 0.0020                | -   |

| eee                                                    | -   | 0.050       | -   | -   | 0.0020                | -   |

#### Table 65. WLCSP25 package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Back side coating.

3. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

4. Primary datum Z and seating plane are defined by the spherical crowns of the bump.

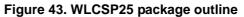

## Figure 44. Recommended footprint for WLCSP25 package

| 5                 |                                                                  |  |  |

|-------------------|------------------------------------------------------------------|--|--|

| Dimension         | Recommended values                                               |  |  |

| Pitch             | 0.4 mm                                                           |  |  |

| Dpad              | 0.225 mm                                                         |  |  |

| Dsm               | 0.290 mm typ. (depends on the soldermask registration tolerance) |  |  |

| Stencil opening   | 0.250 mm                                                         |  |  |

| Stencil thickness | 0.100 mm                                                         |  |  |

### Table 66. WLCSP25 recommended PCB design rules

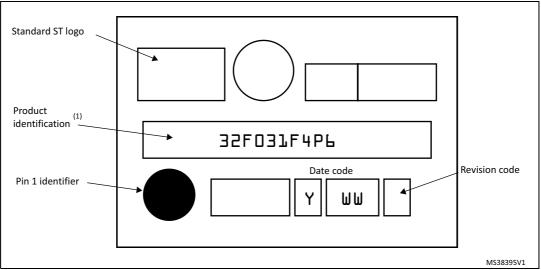

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

#### Figure 48. TSSOP20 package marking example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

| Date        | Revision         | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28-Aug-2015 | 3<br>(continued) | <ul> <li>Added WLCSP25 package, updates in the following:</li> <li>Table 1: Device summary,</li> <li>Section 2: Description,</li> <li>Table 2: STM32F031x4/x6 family device features and peripheral counts,</li> <li>Section 4: Pinouts and pin description: addition of Figure 7: WLCSP25 25-ball package ballout (bump side) and update of Table 11: Pin definitions,</li> <li>Table 18: General operating conditions,</li> <li>Section 7: Package information with the addition of Section 7.5: WLCSP25 package information,</li> <li>Table 68: Package thermal characteristics.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

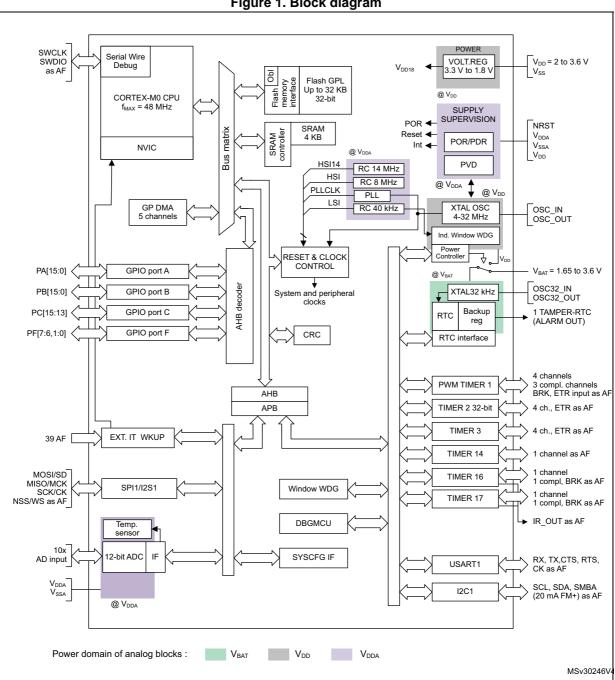

| 16-Dec-2015 | 4                | Cover page:<br>- number of timers added in the title<br>- Table 1: Device summary - STM32F031x4 added<br>Section 2: Description:<br>- Figure 1: Block diagram updated<br>Section 3: Functional overview:<br>- Figure 2: Clock tree updated<br>- Section 3.5.4: Low-power modes - added explicit inf.<br>on peripherals configurable to operate with HSI<br>- Section 3.10.2: Internal voltage reference (V <sub>REFINT</sub> ) -<br>removed information on comparators<br>- Section 3.10.2: Internal voltage reference (V <sub>REFINT</sub> ) -<br>removed information on comparators<br>- Section 3.11.2: General-purpose timers (TIM2, 3, 14,<br>16, 17) - number of gen-purpose timers corrected<br>- Section Table 7.: STM32F031x4/x6 I <sup>2</sup> C<br>implementation - added 20mA output drive current<br>Section 4: Pinouts and pin description:<br>- Package pinout figures updated (look and feel)<br>- Figure 7: WLCSP25 package pinout - now presented<br>in top view<br>- Table 11: Pin definitions - notes 3 and 6 added<br>Section 5: Memory mapping:<br>- added information on memory mapping difference of<br>STM32F031x4 from STM32F031x6<br>Section 6: Electrical characteristics:<br>- Table 22: Embedded internal reference voltage:<br>removed -40°-to-85° condition and associated note for<br>V <sub>REFINT</sub><br>- Table 25 and Table 26 values rounded to 1 decimal<br>- Table 46: I/O static characteristics - updated some<br>parameter values, test conditions and added<br>footnotes <sup>(3)</sup> and <sup>(4)</sup> |