# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 48MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                    |

| Number of I/O              | 15                                                                      |

| Program Memory Size        | 32KB (32K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 4K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                               |

| Data Converters            | A/D 12x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 20-TSSOP (0.173", 4.40mm Width)                                         |

| Supplier Device Package    | 20-TSSOP                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f031f6p6tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

In Standby mode, it is put in power down mode. In this mode, the regulator output is in high impedance and the kernel circuitry is powered down, inducing zero consumption (but the contents of the registers and SRAM are lost).

## 3.5.4 Low-power modes

The STM32F031x4/x6 microcontrollers support three low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

#### Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

#### Stop mode

Stop mode achieves very low power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low power mode.

The device can be woken up from Stop mode by any of the EXTI lines. The EXTI line source can be one of the 16 external lines, the PVD output, RTC, I2C1 or USART1.

USART1 and I2C1 peripherals can be configured to enable the HSI RC oscillator so as to get clock for processing incoming data. If this is used when the voltage regulator is put in low power mode, the regulator is first switched to normal mode before the clock is provided to the given peripheral.

#### • Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.8 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, SRAM and register contents are lost except for registers in the RTC domain and Standby circuitry.

The device exits Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pins, or an RTC event occurs.

Note: The RTC, the IWDG, and the corresponding clock sources are not stopped by entering Stop or Standby mode.

## 3.6 Clocks and startup

System clock selection is performed on startup, however the internal RC 8 MHz oscillator is selected as default CPU clock on reset. An external 4-32 MHz clock can be selected, in which case it is monitored for failure. If failure is detected, the system automatically switches back to the internal RC oscillator. A software interrupt is generated if enabled. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example on failure of an indirectly used external crystal, resonator or oscillator).

Several prescalers allow the application to configure the frequency of the AHB and the APB domains. The maximum frequency of the AHB and the APB domains is 48 MHz.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

## 3.10.1 Temperature sensor

The temperature sensor (TS) generates a voltage  $V_{\mbox{SENSE}}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode.

| Calibration value name | Description                                                                                                | Memory address            |

|------------------------|------------------------------------------------------------------------------------------------------------|---------------------------|

| TS_CAL1                | TS ADC raw data acquired at a temperature of 30 °C ( $\pm$ 5 °C), V <sub>DDA</sub> = 3.3 V ( $\pm$ 10 mV)  | 0x1FFF F7B8 - 0x1FFF F7B9 |

| TS_CAL2                | TS ADC raw data acquired at a temperature of 110 °C ( $\pm$ 5 °C), V <sub>DDA</sub> = 3.3 V ( $\pm$ 10 mV) | 0x1FFF F7C2 - 0x1FFF F7C3 |

Table 3. Temperature sensor calibration values

## 3.10.2 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. The precise voltage of  $V_{REFINT}$  is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode.

| Calibration value name | Description                                                                       | Memory address            |  |  |  |  |  |  |

|------------------------|-----------------------------------------------------------------------------------|---------------------------|--|--|--|--|--|--|

| VREFINT_CAL            | Raw data acquired at a temperature of 30 °C (± 5 °C), $V_{DDA}$ = 3.3 V (± 10 mV) | 0x1FFF F7BA - 0x1FFF F7BB |  |  |  |  |  |  |

| Table 4. Internal voltage reference calibration value | es |

|-------------------------------------------------------|----|

|-------------------------------------------------------|----|

## 3.10.3 V<sub>BAT</sub> battery voltage monitoring

This embedded hardware feature allows the application to measure the V<sub>BAT</sub> battery voltage using the internal ADC channel ADC\_IN18. As the V<sub>BAT</sub> voltage may be higher than V<sub>DDA</sub>, and thus outside the ADC input range, the V<sub>BAT</sub> pin is internally connected to a bridge divider by 2. As a consequence, the converted digital value is half the V<sub>BAT</sub> voltage.

# 3.16 Serial wire debug port (SW-DP)

An ARM SW-DP interface is provided to allow a serial wire debugging tool to be connected to the MCU.

| Na               | me                   | Abbreviation                                                                                                                          | Definition                                                  |  |  |  |  |

|------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|--|--|--|

| Pin n            | name                 | Unless otherwise specified in brackets below the pin name, the pin function during and after reset is the same as the actual pin name |                                                             |  |  |  |  |

|                  |                      | S                                                                                                                                     | Supply pin                                                  |  |  |  |  |

| Pin              | type                 | I                                                                                                                                     | Input-only pin                                              |  |  |  |  |

|                  |                      | I/O                                                                                                                                   | Input / output pin                                          |  |  |  |  |

|                  |                      | FT                                                                                                                                    | 5 V-tolerant I/O                                            |  |  |  |  |

|                  |                      | FTf                                                                                                                                   | 5 V-tolerant I/O, FM+ capable                               |  |  |  |  |

| I/O atr          |                      | TTa 3.3 V-tolerant I/O directly connected to AD                                                                                       |                                                             |  |  |  |  |

| i/O str          | ucture               | TC Standard 3.3V I/O                                                                                                                  |                                                             |  |  |  |  |

|                  |                      | B Dedicated BOOT0 pin                                                                                                                 |                                                             |  |  |  |  |

|                  |                      | RST                                                                                                                                   | Bidirectional reset pin with embedded weak pull-up resistor |  |  |  |  |

| No               | tes                  | Unless otherwise specified by a note, all I/Os are set as floating inputs during and after reset                                      |                                                             |  |  |  |  |

| 5.               | Alternate functions  | Functions select                                                                                                                      | ted through GPIOx_AFR registers                             |  |  |  |  |

| Pin<br>functions | Additional functions | Functions direct                                                                                                                      | ly selected/enabled through peripheral registers            |  |  |  |  |

#### Table 10. Legend/abbreviations used in the pinout table

|        | F      | Pin nu   | umbe     | r       |         |                                      |          |          |        | Pin fund            | ctions                                     |  |

|--------|--------|----------|----------|---------|---------|--------------------------------------|----------|----------|--------|---------------------|--------------------------------------------|--|

| LQFP48 | LQFP32 | UFQFPN32 | UFQFPN28 | WLCSP25 | TSSOP20 | Pin name<br>(function upon<br>reset) | Pin type | <u> </u> |        | Alternate functions | Additional<br>functions                    |  |

| 1      | -      | -        | -        | -       | -       | VBAT                                 | S        | -        | -      | Backup power supply |                                            |  |

| 2      | -      | -        | -        | -       | -       | PC13                                 | I/O      | тс       | (1)(2) | -                   | RTC_TAMP1,<br>RTC_TS,<br>RTC_OUT,<br>WKUP2 |  |

| 3      | -      | -        | -        | -       | -       | PC14-OSC32_IN<br>(PC14)              | I/O      | тс       | (1)(2) | -                   | OSC32_IN                                   |  |

| 4      | -      | -        | -        | -       | -       | PC15-<br>OSC32_OUT<br>(PC15)         | I/O      | тс       | (1)(2) | -                   | OSC32_OUT                                  |  |

| 5      | 2      | 2        | 2        | A5      | 2       | PF0-OSC_IN<br>(PF0)                  | I/O      | FT       | -      | -                   | OSC_IN                                     |  |

#### Table 11. Pin definitions

|        | I      | Pin nu   | umbe     | r       |         |                                      |          |               |       | Pin fund                                                        | ctions                  |

|--------|--------|----------|----------|---------|---------|--------------------------------------|----------|---------------|-------|-----------------------------------------------------------------|-------------------------|

| LQFP48 | LQFP32 | UFQFPN32 | UFQFPN28 | WLCSP25 | TSSOP20 | Pin name<br>(function upon<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                             | Additional<br>functions |

| 30     | 19     | 19       | 19       | C1      | 17      | PA9                                  | I/O      | FTf           | -     | USART1_TX,<br>TIM1_CH2,<br>I2C1_SCL                             | -                       |

| 31     | 20     | 20       | 20       | B1      | 18      | PA10                                 | I/O      | FTf           | -     | USART1_RX,<br>TIM1_CH3,<br>TIM17_BKIN,<br>I2C1_SDA              | -                       |

| 32     | 21     | 21       | -        | -       | -       | PA11                                 | I/O      | FT            | -     | USART1_CTS,<br>TIM1_CH4,<br>EVENTOUT                            | -                       |

| 33     | 22     | 22       | -        | -       | -       | PA12                                 | I/O      | FT            | -     | USART1_RTS,<br>TIM1_ETR,<br>EVENTOUT                            | -                       |

| 34     | 23     | 23       | 21       | A1      | 19      | PA13<br>(SWDIO)                      | I/O      | FT            | (5)   | ir_out,<br>Swdio                                                | -                       |

| 35     | -      | -        | -        | -       | -       | PF6                                  | I/O      | FTf           | -     | I2C1_SCL                                                        | -                       |

| 36     | -      | -        | -        | -       | -       | PF7                                  | I/O      | FTf           | -     | I2C1_SDA                                                        | -                       |

| 37     | 24     | 24       | 22       | A2      | 20      | PA14<br>(SWCLK)                      | I/O      | FT            | (5)   | USART1_TX,<br>SWCLK                                             | -                       |

| 38     | 25     | 25       | 23       | -       | -       | PA15                                 | I/O      | FT            | (6)   | SPI1_NSS,<br>I2S1_WS,<br>TIM2_CH_ETR,<br>EVENTOUT,<br>USART1_RX | -                       |

| 39     | 26     | 26       | 24       | -       | -       | PB3                                  | I/O      | FT            | (6)   | SPI1_SCK,<br>I2S1_CK,<br>TIM2_CH2,<br>EVENTOUT                  | -                       |

| 40     | 27     | 27       | 25       | -       | -       | PB4                                  | I/O      | FT            | (6)   | SPI1_MISO,<br>I2S1_MCK,<br>TIM3_CH1,<br>EVENTOUT                | -                       |

Table 11. Pin definitions (continued)

| Pin name | AF0                 | AF1      | AF2        | AF3       |

|----------|---------------------|----------|------------|-----------|

| PB0      | EVENTOUT            | TIM3_CH3 | TIM1_CH2N  | -         |

| PB1      | TIM14_CH1           | TIM3_CH4 | TIM1_CH3N  | -         |

| PB2      | -                   | -        | -          | -         |

| PB3      | SPI1_SCK, I2S1_CK   | EVENTOUT | TIM2_CH2   | -         |

| PB4      | SPI1_MISO, I2S1_MCK | TIM3_CH1 | EVENTOUT   | -         |

| PB5      | SPI1_MOSI, I2S1_SD  | TIM3_CH2 | TIM16_BKIN | I2C1_SMBA |

| PB6      | USART1_TX           | I2C1_SCL | TIM16_CH1N | -         |

| PB7      | USART1_RX           | I2C1_SDA | TIM17_CH1N | -         |

| PB8      | -                   | I2C1_SCL | TIM16_CH1  | -         |

| PB9      | IR_OUT              | I2C1_SDA | TIM17_CH1  | EVENTOUT  |

| PB10     | -                   | I2C1_SCL | TIM2_CH3   | _         |

| PB11     | EVENTOUT            | I2C1_SDA | TIM2_CH4   | -         |

| PB12     | SPI1_NSS            | EVENTOUT | TIM1_BKIN  | -         |

| PB13     | SPI1_SCK            | -        | TIM1_CH1N  | -         |

| PB14     | SPI1_MISO           | -        | TIM1_CH2N  | -         |

| PB15     | SPI1_MOSI           | -        | TIM1_CH3N  | -         |

32/106

DocID025743 Rev 5

5

STM32F031x4 STM32F031x6

| Bus | Boundary address          | Size | Peripheral |

|-----|---------------------------|------|------------|

|     | 0x4000 7400 - 0x4000 7FFF | 3KB  | Reserved   |

|     | 0x4000 7000 - 0x4000 73FF | 1KB  | PWR        |

|     | 0x4000 5800 - 0x4000 6FFF | 6KB  | Reserved   |

|     | 0x4000 5400 - 0x4000 57FF | 1KB  | I2C1       |

|     | 0x4000 3400 - 0x4000 53FF | 8KB  | Reserved   |

|     | 0x4000 3000 - 0x4000 33FF | 1KB  | IWDG       |

| APB | 0x4000 2C00 - 0x4000 2FFF | 1KB  | WWDG       |

|     | 0x4000 2800 - 0x4000 2BFF | 1KB  | RTC        |

|     | 0x4000 2400 - 0x4000 27FF | 1KB  | Reserved   |

|     | 0x4000 2000 - 0x4000 23FF | 1KB  | TIM14      |

|     | 0x4000 0800 - 0x4000 1FFF | 6KB  | Reserved   |

|     | 0x4000 0400 - 0x4000 07FF | 1KB  | TIM3       |

|     | 0x4000 0000 - 0x4000 03FF | 1KB  | TIM2       |

## Table 14. STM32F031x4/x6 peripheral register boundary addresses (continued)

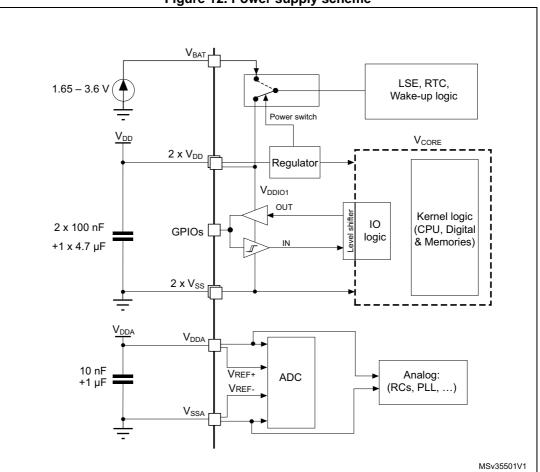

## 6.1.6 Power supply scheme

Figure 12. Power supply scheme

**Caution:** Each power supply pair (V<sub>DD</sub>/V<sub>SS</sub>, V<sub>DDA</sub>/V<sub>SSA</sub> etc.) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below, the appropriate pins on the underside of the PCB to ensure the good functionality of the device.

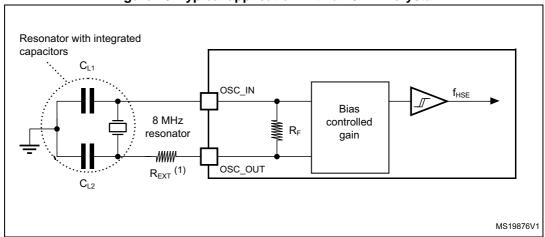

Figure 16. Typical application with an 8 MHz crystal

1.  $R_{EXT}$  value depends on the crystal characteristics.

## Low-speed external clock generated from a crystal resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 34*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter               | Conditions <sup>(1)</sup>        | Min <sup>(2)</sup> | Тур | Max <sup>(2)</sup> | Unit |

|-------------------------------------|-------------------------|----------------------------------|--------------------|-----|--------------------|------|

| I <sub>DD</sub>                     |                         | low drive capability             | -                  | 0.5 | 0.9                |      |

|                                     | LSE current consumption | medium-low drive capability      | -                  | -   | 1                  |      |

|                                     | LSE current consumption | medium-high drive capability     | -                  | -   | 1.3                | μA   |

|                                     |                         | high drive capability            | -                  | -   | 1.6                |      |

|                                     |                         | low drive capability             | 5                  | -   | -                  |      |

| g <sub>m</sub> tran                 | Oscillator              | medium-low drive capability      | 8                  | -   | -                  |      |

|                                     | transconductance        | medium-high drive capability     | 15                 | -   | -                  | μA/V |

|                                     |                         | high drive capability            | 25                 | -   | -                  |      |

| t <sub>SU(LSE)</sub> <sup>(3)</sup> | Startup time            | V <sub>DDIOx</sub> is stabilized | -                  | 2   | -                  | S    |

| Table 34. LSE oscillator characteristics | (f <sub>LSE</sub> = 32.768 kHz) |

|------------------------------------------|---------------------------------|

|------------------------------------------|---------------------------------|

1. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

2. Guaranteed by design, not tested in production.

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer

## High-speed internal (HSI) RC oscillator

| Symbol                | Parameter                         | Conditions                    | Min                 | Тур | Мах                | Unit |

|-----------------------|-----------------------------------|-------------------------------|---------------------|-----|--------------------|------|

| f <sub>HSI</sub>      | Frequency                         | -                             | -                   | 8   | -                  | MHz  |

| TRIM                  | HSI user trimming step            | -                             | -                   | -   | 1 <sup>(2)</sup>   | %    |

| DuCy <sub>(HSI)</sub> | Duty cycle                        | -                             | 45 <sup>(2)</sup>   | -   | 55 <sup>(2)</sup>  | %    |

|                       |                                   | T <sub>A</sub> = -40 to 105°C | -2.8 <sup>(3)</sup> | -   | 3.8 <sup>(3)</sup> |      |

|                       | Accuracy of the HSI<br>oscillator | T <sub>A</sub> = -10 to 85°C  | -1.9 <sup>(3)</sup> | -   | 2.3 <sup>(3)</sup> | %    |

| 100                   |                                   | $T_A = 0$ to $85^{\circ}C$    | -1.9 <sup>(3)</sup> | -   | 2 <sup>(3)</sup>   |      |

| ACC <sub>HSI</sub>    |                                   | $T_A = 0$ to $70^{\circ}C$    | -1.3 <sup>(3)</sup> | -   | 2 <sup>(3)</sup>   |      |

|                       |                                   | $T_A = 0$ to 55°C             | -1 <sup>(3)</sup>   | -   | 2 <sup>(3)</sup>   |      |

|                       |                                   | $T_A = 25^{\circ}C^{(4)}$     | -1                  | -   | 1                  |      |

| t <sub>su(HSI)</sub>  | HSI oscillator startup time       | -                             | 1 <sup>(2)</sup>    | -   | 2 <sup>(2)</sup>   | μs   |

| I <sub>DDA(HSI)</sub> | HSI oscillator power consumption  | -                             | -                   | 80  | 100 <sup>(2)</sup> | μA   |

| Table 35. HSI oscillator characteristics <sup>(*</sup> | Table 35. | oscillator ch | haracteristics <sup>(1)</sup> |

|--------------------------------------------------------|-----------|---------------|-------------------------------|

|--------------------------------------------------------|-----------|---------------|-------------------------------|

1.  $V_{DDA}$  = 3.3 V,  $T_A$  = -40 to 105°C unless otherwise specified.

2. Guaranteed by design, not tested in production.

3. Data based on characterization results, not tested in production.

4. Factory calibrated, parts not soldered.

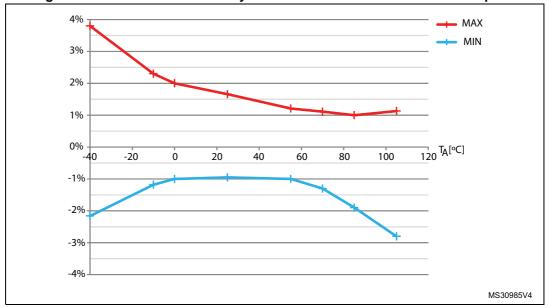

## Figure 18. HSI oscillator accuracy characterization results for soldered parts

## Low-speed internal (LSI) RC oscillator

| Table 37. | LSI | oscillator | characteristics <sup>(1)</sup> |

|-----------|-----|------------|--------------------------------|

|-----------|-----|------------|--------------------------------|

| Symbol                               | Parameter                        | Min | Тур  | Max | Unit |

|--------------------------------------|----------------------------------|-----|------|-----|------|

| f <sub>LSI</sub>                     | Frequency                        | 30  | 40   | 50  | kHz  |

| t <sub>su(LSI)</sub> <sup>(2)</sup>  | LSI oscillator startup time      | -   | -    | 85  | μs   |

| I <sub>DDA(LSI)</sub> <sup>(2)</sup> | LSI oscillator power consumption | -   | 0.75 | 1.2 | μA   |

1. V<sub>DDA</sub> = 3.3 V, T<sub>A</sub> = –40 to 105  $^\circ\text{C}$  unless otherwise specified.

2. Guaranteed by design, not tested in production.

## 6.3.9 PLL characteristics

The parameters given in *Table 38* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 18: General operating conditions*.

| Symbol                | Parameter                      |                   | Value |                    |      |  |

|-----------------------|--------------------------------|-------------------|-------|--------------------|------|--|

| Symbol                | Falameter                      | Min               | Тур   | Max                | Unit |  |

| f                     | PLL input clock <sup>(1)</sup> | 1 <sup>(2)</sup>  | 8.0   | 24 <sup>(2)</sup>  | MHz  |  |

| f <sub>PLL_IN</sub>   | PLL input clock duty cycle     | 40 <sup>(2)</sup> | -     | 60 <sup>(2)</sup>  | %    |  |

| f <sub>PLL_OUT</sub>  | PLL multiplier output clock    | 16 <sup>(2)</sup> | -     | 48                 | MHz  |  |

| t <sub>LOCK</sub>     | PLL lock time                  | -                 | -     | 200 <sup>(2)</sup> | μs   |  |

| Jitter <sub>PLL</sub> | Cycle-to-cycle jitter          | -                 | _     | 300 <sup>(2)</sup> | ps   |  |

Table 38. PLL characteristics

1. Take care to use the appropriate multiplier factors to obtain PLL input clock values compatible with the range defined by f<sub>PLL\_OUT</sub>.

2. Guaranteed by design, not tested in production.

## 6.3.10 Memory characteristics

## **Flash memory**

The characteristics are given at  $T_A = -40$  to 105 °C unless otherwise specified.

| Table 39. Flash memory characterist | CS |

|-------------------------------------|----|

|-------------------------------------|----|

| Symbol             | Parameter               | Conditions                       | Min | Тур  | Max <sup>(1)</sup> | Unit |

|--------------------|-------------------------|----------------------------------|-----|------|--------------------|------|

| t <sub>prog</sub>  | 16-bit programming time | T <sub>A</sub> = - 40 to +105 °C | 40  | 53.5 | 60                 | μs   |

| t <sub>ERASE</sub> | Page (1 KB) erase time  | T <sub>A</sub> = - 40 to +105 °C | 20  | -    | 40                 | ms   |

| t <sub>ME</sub>    | Mass erase time         | T <sub>A</sub> = - 40 to +105 °C | 20  | -    | 40                 | ms   |

|                    | Supply ourrant          | Write mode                       | -   | -    | 10                 | mA   |

| IDD                | Supply current          | Erase mode                       | -   | -    | 12                 | mA   |

1. Guaranteed by design, not tested in production.

| Symbol           | Parameter      | Conditions                                         | Min <sup>(1)</sup> | Unit   |  |  |

|------------------|----------------|----------------------------------------------------|--------------------|--------|--|--|

| N <sub>END</sub> | Endurance      | T <sub>A</sub> = -40 to +105 °C                    | 10                 | kcycle |  |  |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C  | 30                 | 1      |  |  |

| t <sub>RET</sub> | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C | 10                 | Year   |  |  |

|                  |                | 10 kcycle <sup>(2)</sup> at T <sub>A</sub> = 55 °C | 20                 |        |  |  |

Table 40. Flash memory endurance and data retention

1. Data based on characterization results, not tested in production.

2. Cycling performed over the whole temperature range.

## 6.3.11 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

## Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- **FTB**: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 41*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                      | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 3.3 V, LQFP48, $T_A$ = +25 °C,<br>f <sub>HCLK</sub> = 48 MHz,<br>conforming to IEC 61000-4-2         | 2B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD}$ = 3.3 V, LQFP48, T <sub>A</sub> = +25°C,<br>f <sub>HCLK</sub> = 48 MHz,<br>conforming to IEC 61000-4-4 | 4B              |

## Table 41. EMS characteristics

### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

| Symbol          | Parameter                                               | Conditions                             | Min | Тур | Max | Unit |  |  |

|-----------------|---------------------------------------------------------|----------------------------------------|-----|-----|-----|------|--|--|

| R <sub>PU</sub> | Weak pull-up<br>equivalent resistor<br>(3)              | V <sub>IN</sub> = V <sub>SS</sub>      | 25  | 40  | 55  | kΩ   |  |  |

| R <sub>PD</sub> | Weak pull-down<br>equivalent<br>resistor <sup>(3)</sup> | V <sub>IN</sub> = - V <sub>DDIOx</sub> | 25  | 40  | 55  | kΩ   |  |  |

| C <sub>IO</sub> | I/O pin capacitance                                     | -                                      | -   | 5   | -   | pF   |  |  |

Table 46. I/O static characteristics (continued)

1. Data based on design simulation only. Not tested in production.

2. The leakage could be higher than the maximum value, if negative current is injected on adjacent pins. Refer to *Table 45: I/O current injection susceptibility.*

3. Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This PMOS/NMOS contribution to the series resistance is minimal (~10% order).

All I/Os are CMOS- and TTL-compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements is shown in *Figure 20* for standard I/Os, and in *Figure 21* for 5 V-tolerant I/Os. The following curves are design simulation results, not tested in production.

### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to +/-8 mA, and sink or source up to +/- 20 mA (with a relaxed  $V_{OL}/V_{OH}$ ).

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in Section 6.2:

- The sum of the currents sourced by all the I/Os on V<sub>DDIOx</sub>, plus the maximum consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating ΣI<sub>VDD</sub> (see *Table 15: Voltage characteristics*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub>, plus the maximum consumption of the MCU sunk on V<sub>SS</sub>, cannot exceed the absolute maximum rating ΣI<sub>VSS</sub> (see *Table 15: Voltage characteristics*).

## **Output voltage levels**

Unless otherwise specified, the parameters given in the table below are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 18: General operating conditions*. All I/Os are CMOS- and TTL-compliant (FT, TTa or TC unless otherwise specified).

| Symbol                            | Parameter                                                  | Conditions                                              | Min                     | Max | Unit |

|-----------------------------------|------------------------------------------------------------|---------------------------------------------------------|-------------------------|-----|------|

| V <sub>OL</sub>                   | Output low level voltage for an I/O pin                    | CMOS port <sup>(2)</sup>                                | -                       | 0.4 |      |

| V <sub>OH</sub>                   | Output high level voltage for an I/O pin                   | I <sub>IO</sub>   = 8 mA<br>V <sub>DDIOx</sub> ≥ 2.7 V  | V <sub>DDIOx</sub> -0.4 | -   | V    |

| V <sub>OL</sub>                   | Output low level voltage for an I/O pin                    | TTL port <sup>(2)</sup>                                 | -                       | 0.4 |      |

| V <sub>OH</sub>                   | Output high level voltage for an I/O pin                   | I <sub>IO</sub>   = 8 mA<br>V <sub>DDIOx</sub> ≥ 2.7 V  | 2.4                     | -   | V    |

| V <sub>OL</sub> <sup>(3)</sup>    | Output low level voltage for an I/O pin                    | I <sub>IO</sub>   = 20 mA                               | -                       | 1.3 | V    |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin                   | V <sub>DDIOx</sub> ≥ 2.7 V                              | V <sub>DDIOx</sub> -1.3 | -   | v    |

| V <sub>OL</sub> <sup>(3)</sup>    | Output low level voltage for an I/O pin                    | l <sub>IO</sub>   = 6 mA                                | -                       | 0.4 | V    |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin                   | 1101 - 0 MA                                             | V <sub>DDIOx</sub> -0.4 | -   | v    |

| V <sub>OLFm+</sub> <sup>(3)</sup> | Output low level voltage for an FTf I/O pin in<br>Fm+ mode | I <sub>IO</sub>   = 20 mA<br>V <sub>DDIOx</sub> ≥ 2.7 V | -                       | 0.4 | V    |

|                                   |                                                            | I <sub>IO</sub>   = 10 mA                               | -                       | 0.4 | V    |

## Table 47. Output voltage characteristics<sup>(1)</sup>

1. The I<sub>IO</sub> current sourced or sunk by the device must always respect the absolute maximum rating specified in Table 15: Voltage characteristics, and the sum of the currents sourced or sunk by all the I/Os (I/O ports and control pins) must always respect the absolute maximum ratings  $\Sigma I_{IO}$ .

2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

3. Data based on characterization results. Not tested in production.

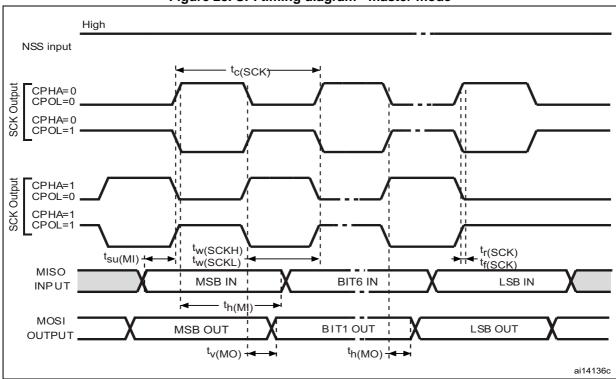

Figure 28. SPI timing diagram - master mode

1. Measurement points are done at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}.$

| Table 6 | 60. I <sup>2</sup> S | characteristics <sup>(1)</sup> |

|---------|----------------------|--------------------------------|

|---------|----------------------|--------------------------------|

| Symbol               | Parameter                                     | Conditions                                               | Min   | Мах   | Unit |

|----------------------|-----------------------------------------------|----------------------------------------------------------|-------|-------|------|

| f <sub>CK</sub>      | I <sup>2</sup> S clock frequency              | Master mode (data: 16 bits, Audio<br>frequency = 48 kHz) | 1.597 | 1.601 | MHz  |

| 1/t <sub>c(CK)</sub> |                                               | Slave mode                                               | 0     | 6.5   |      |

| t <sub>r(CK)</sub>   | I <sup>2</sup> S clock rise time              | Conscitive load C = 15 pE                                | -     | 10    |      |

| t <sub>f(CK)</sub>   | I <sup>2</sup> S clock fall time              | Capacitive load C <sub>L</sub> = 15 pF                   | -     | 12    |      |

| t <sub>w(CKH)</sub>  | I <sup>2</sup> S clock high time              | Master f <sub>PCLK</sub> = 16 MHz, audio                 | 306   | -     |      |

| t <sub>w(CKL)</sub>  | I <sup>2</sup> S clock low time               | frequency = 48 kHz                                       | 312   | -     | ns   |

| t <sub>v(WS)</sub>   | WS valid time                                 | Master mode                                              | 2     | -     | 115  |

| t <sub>h(WS)</sub>   | WS hold time                                  | Master mode                                              | 2     | -     |      |

| t <sub>su(WS)</sub>  | WS setup time                                 | Slave mode                                               | 7     | -     |      |

| t <sub>h(WS)</sub>   | WS hold time                                  | Slave mode                                               | 0     | -     |      |

| DuCy(SCK)            | I <sup>2</sup> S slave input clock duty cycle | Slave mode                                               | 25    | 75    | %    |

# 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

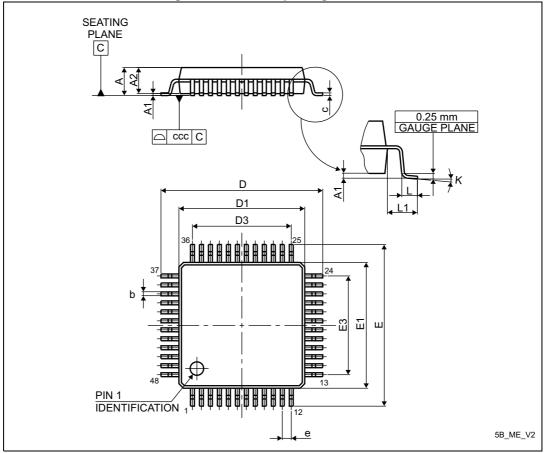

## 7.1 LQFP48 package information

LQFP48 is a 48-pin, 7 x 7 mm low-profile quad flat package.

Figure 31. LQFP48 package outline

1. Drawing is not to scale.

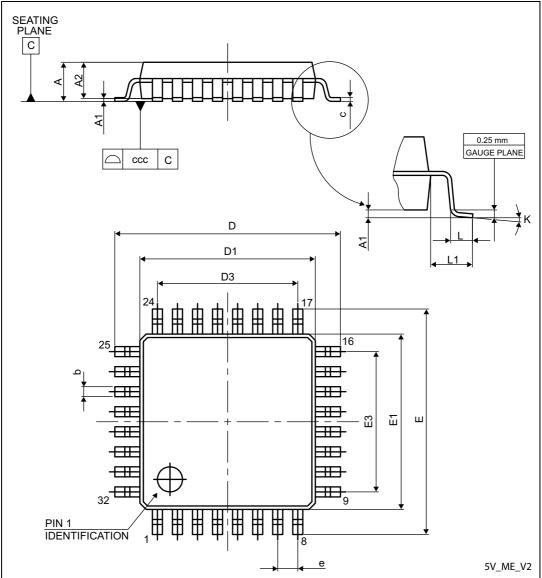

## 7.2 LQFP32 package information

LQFP32 is a 32-pin, 7 x 7 mm low-profile quad flat package.

Figure 34. LQFP32 package outline

1. Drawing is not to scale.

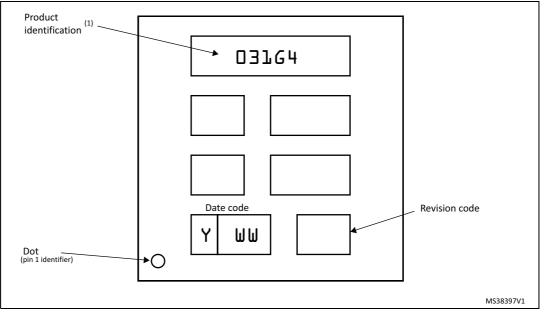

## **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

#### Figure 42. UFQFPN28 package marking example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

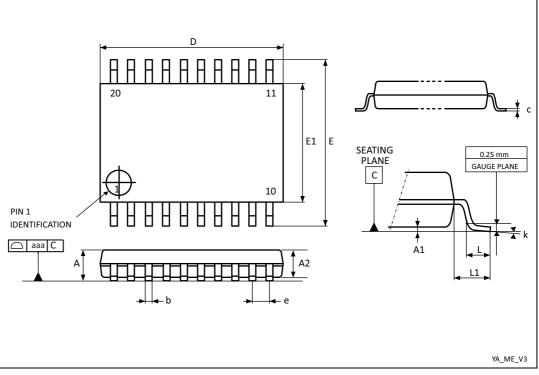

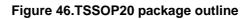

# 7.6 TSSOP20 package information

TSSOP20 is a 20-lead thin shrink small-outline, 6.5 x 4.4 mm, 0.65 mm pitch, package.

1. Drawing is not to scale.

| Symbol            | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|-------------------|-------------|-------|-------|-----------------------|--------|--------|

|                   | Min.        | Тур.  | Max.  | Min.                  | Тур.   | Max.   |

| А                 | -           | -     | 1.200 | -                     | -      | 0.0472 |

| A1                | 0.050       | -     | 0.150 | 0.0020                | -      | 0.0059 |

| A2                | 0.800       | 1.000 | 1.050 | 0.0315                | 0.0394 | 0.0413 |

| b                 | 0.190       | -     | 0.300 | 0.0075                | -      | 0.0118 |

| с                 | 0.090       | -     | 0.200 | 0.0035                | -      | 0.0079 |

| D <sup>(2)</sup>  | 6.400       | 6.500 | 6.600 | 0.2520                | 0.2559 | 0.2598 |

| E                 | 6.200       | 6.400 | 6.600 | 0.2441                | 0.2520 | 0.2598 |

| E1 <sup>(3)</sup> | 4.300       | 4.400 | 4.500 | 0.1693                | 0.1732 | 0.1772 |

| е                 | -           | 0.650 | -     | -                     | 0.0256 | -      |

| L                 | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |

| L1                | -           | 1.000 | -     | -                     | 0.0394 | -      |

| Table 67. | TSSOP20  | package | mechanical | data |

|-----------|----------|---------|------------|------|

|           | 10001 20 | puonugo | meenamear  | autu |

#### IMPORTANT NOTICE – PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics – All rights reserved

DocID025743 Rev 5