Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M0                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 48MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | DMA, I²S, POR, PWM, WDT                                                 |

| Number of I/O              | 23                                                                      |

| Program Memory Size        | 16KB (16K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 4K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                               |

| Data Converters            | A/D 13x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 28-UFQFN                                                                |

| Supplier Device Package    | 28-UFQFPN (4x4)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f031g4u7tr |

## **Contents**

| 1 | Intro | duction                                |                                                           | 8  |  |  |  |  |

|---|-------|----------------------------------------|-----------------------------------------------------------|----|--|--|--|--|

| 2 | Desc  | ription                                |                                                           | 9  |  |  |  |  |

| 3 | Fund  | tional o                               | verview                                                   | 11 |  |  |  |  |

| 2 | 3.1   | ARM®-                                  | Cortex®-M0 core                                           | 11 |  |  |  |  |

|   | 3.2   | Memor                                  | ies                                                       | 11 |  |  |  |  |

|   | 3.3   | Boot m                                 | odes                                                      | 11 |  |  |  |  |

|   | 3.4   | Cyclic ı                               | redundancy check calculation unit (CRC)                   | 12 |  |  |  |  |

| 2 | 3.5   | Power                                  | management                                                | 12 |  |  |  |  |

|   |       | 3.5.1                                  | Power supply schemes                                      | 12 |  |  |  |  |

|   |       | 3.5.2                                  | Power supply supervisors                                  | 12 |  |  |  |  |

|   |       | 3.5.3                                  | Voltage regulator                                         | 12 |  |  |  |  |

|   |       | 3.5.4                                  | Low-power modes                                           | 13 |  |  |  |  |

|   | 3.6   | Clocks                                 | and startup                                               | 13 |  |  |  |  |

|   | 3.7   | General-purpose inputs/outputs (GPIOs) |                                                           |    |  |  |  |  |

|   | 3.8   | Direct memory access controller (DMA)  |                                                           |    |  |  |  |  |

|   | 3.9   | Interrup                               | ots and events                                            | 15 |  |  |  |  |

|   |       | 3.9.1                                  | Nested vectored interrupt controller (NVIC)               | 15 |  |  |  |  |

|   |       | 3.9.2                                  | Extended interrupt/event controller (EXTI)                | 15 |  |  |  |  |

|   | 3.10  | Analog                                 | -to-digital converter (ADC)                               | 15 |  |  |  |  |

|   |       | 3.10.1                                 | Temperature sensor                                        | 16 |  |  |  |  |

|   |       | 3.10.2                                 | Internal voltage reference (V <sub>REFINT</sub> )         | 16 |  |  |  |  |

|   |       | 3.10.3                                 | V <sub>BAT</sub> battery voltage monitoring               | 16 |  |  |  |  |

|   | 3.11  | Timers                                 | and watchdogs                                             | 17 |  |  |  |  |

|   |       | 3.11.1                                 | Advanced-control timer (TIM1)                             |    |  |  |  |  |

|   |       | 3.11.2                                 | General-purpose timers (TIM2, 3, 14, 16, 17)              |    |  |  |  |  |

|   |       | 3.11.3                                 | Independent watchdog (IWDG)                               |    |  |  |  |  |

|   |       | 3.11.4                                 | System window watchdog (WWDG)                             |    |  |  |  |  |

|   |       | 3.11.5                                 | SysTick timer                                             |    |  |  |  |  |

|   | 3.12  |                                        | me clock (RTC) and backup registers                       |    |  |  |  |  |

|   | 3.13  | Inter-in                               | tegrated circuit interface (I <sup>2</sup> C)             | 19 |  |  |  |  |

|   | 3.14  | Univers                                | sal synchronous/asynchronous receiver/transmitter (USART) | 20 |  |  |  |  |

# List of tables

| Table 1.  | Device summary                                                           | 1  |

|-----------|--------------------------------------------------------------------------|----|

| Table 2.  | STM32F031x4/x6 family device features and peripheral counts              |    |

| Table 3.  | Temperature sensor calibration values                                    | 16 |

| Table 4.  | Internal voltage reference calibration values                            | 16 |

| Table 5.  | Timer feature comparison                                                 | 17 |

| Table 6.  | Comparison of I <sup>2</sup> C analog and digital filters                | 20 |

| Table 7.  | STM32F031x4/x6 I <sup>2</sup> C implementation                           | 20 |

| Table 8.  | STM32F031x4/x6 USART implementation                                      |    |

| Table 9.  | STM32F031x4/x6 SPI/I2S implementation                                    | 21 |

| Table 10. | Legend/abbreviations used in the pinout table                            |    |

| Table 11. | Pin definitions                                                          |    |

| Table 12. | Alternate functions selected through GPIOA AFR registers for port A      | 31 |

| Table 13. | Alternate functions selected through GPIOB_AFR registers for port B      | 32 |

| Table 14. | STM32F031x4/x6 peripheral register boundary addresses                    |    |

| Table 15. | Voltage characteristics                                                  |    |

| Table 16. | Current characteristics                                                  |    |

| Table 17. | Thermal characteristics                                                  | 40 |

| Table 18. | General operating conditions                                             |    |

| Table 19. | Operating conditions at power-up / power-down                            | 42 |

| Table 20. | Embedded reset and power control block characteristics                   | 42 |

| Table 21. | Programmable voltage detector characteristics                            |    |

| Table 22. | Embedded internal reference voltage                                      |    |

| Table 23. | Typical and maximum current consumption from V <sub>DD</sub> at 3.6 V    |    |

| Table 24. | Typical and maximum current consumption from the V <sub>DDA</sub> supply |    |

| Table 25. | Typical and maximum current consumption in Stop and Standby modes        |    |

| Table 26. | Typical and maximum current consumption from the V <sub>BAT</sub> supply | 47 |

| Table 27. | Typical current consumption, code executing from Flash memory,           |    |

|           | running from HSE 8 MHz crystal                                           | 48 |

| Table 28. | Switching output I/O current consumption                                 |    |

| Table 29. | Peripheral current consumption                                           | 51 |

| Table 30. | Low-power mode wakeup timings                                            | 53 |

| Table 31. | High-speed external user clock characteristics                           | 53 |

| Table 32. | Low-speed external user clock characteristics                            | 54 |

| Table 33. | HSE oscillator characteristics                                           | 55 |

| Table 34. | LSE oscillator characteristics (f <sub>LSE</sub> = 32.768 kHz)           | 56 |

| Table 35. | HSI oscillator characteristics                                           | 58 |

| Table 36. | HSI14 oscillator characteristics                                         |    |

| Table 37. | LSI oscillator characteristics                                           | 60 |

| Table 38. | PLL characteristics                                                      | 60 |

| Table 39. | Flash memory characteristics                                             | 60 |

| Table 40. | Flash memory endurance and data retention                                | 61 |

| Table 41. | EMS characteristics                                                      |    |

| Table 42. | EMI characteristics                                                      | 62 |

| Table 43. | ESD absolute maximum ratings                                             | 63 |

| Table 44. | Electrical sensitivities                                                 | 63 |

| Table 45. | I/O current injection susceptibility                                     | 64 |

| Table 46. | I/O static characteristics                                               |    |

| Table 47. | Output voltage characteristics                                           | 67 |

## 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of the STM32F031x4/x6 microcontrollers.

This document should be read in conjunction with the STM32F0xxxx reference manual (RM0091). The reference manual is available from the STMicroelectronics website <a href="https://www.st.com">www.st.com</a>.

For information on the ARM<sup>®</sup> Cortex<sup>®</sup>-M0 core, please refer to the Cortex<sup>®</sup>-M0 Technical Reference Manual, available from the www.arm.com website.

SWCLK SWDIO as AF POWER Serial Wire Debug V<sub>DD</sub> = 2 to 3.6 V V<sub>SS</sub> VOLT.REG 3.3 V to 1.8 V ldo Flash GPL Flash Ol memory interface Up to 32 KB CORTEX-M0 CPU 32-bit f<sub>MAX</sub> = 48 MHz SUPPLY SUPERVISION POR ◀ NRST SRAM 4 KB SRAM controller matrix Reset ◀  $V_{DDA} \ V_{SSA}$ POR/PDR Int 🗲 NVIC Bus HSI14 PVD RC 14 MHz HSI RC 8 MHz **♦** @ V<sub>DD</sub> PLLCLK PLL LSI RC 40 kHz GP DMA 5 channels XTAL OSC 4-32 MHz OSC\_IN OSC\_OUT Ind. Window WDG RESET & CLOCK CONTROL ₹. PA[15:0] GPIO port A  $V_{BAT}$  = 1.65 to 3.6 V @ V<sub>BAT</sub> OSC32\_IN OSC32\_OUT GPIO port B AHB decoder System and peripheral clocks XTAL32 kHz PB[15:0] 1 TAMPER-RTC (ALARM OUT) PC[15:13] GPIO port C Backup RTC reg PF[7:6,1:0] < GPIO port F CRC RTC interface 4 channels 3 compl. channels BRK, ETR input as AF PWM TIMER 1 AHB 4 ch., ETR as AF APB TIMER 2 32-bit 4 ch., ETR as AF TIMER 3 EXT. IT WKUP 39 AF TIMER 14 1 channel as AF MOSI/SD 1 channel TIMER 16 1 compl, BRK as AF MISO/MCK SCK/CK NSS/WS as AF SPI1/I2S1 Window WDG 1 channel 1 compl, BRK as AF TIMER 17 → IR\_OUT as AF DBGMCU Temp. sensor 10x SYSCFG IF 12-bit ADC RX, TX,CTS, RTS, CK as AF AD input USART1  $V_{DDA}$   $V_{SSA}$ SCL, SDA, SMBA (20 mA FM+) as AF I2C1 @ V<sub>DDA</sub> Power domain of analog blocks :  $V_{DDA}$  $V_{BAT}$  $V_{DD}$ MSv30246V4

Figure 1. Block diagram

## 4 Pinouts and pin description

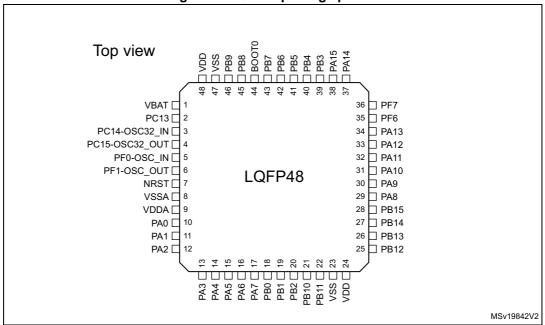

Figure 3. LQFP48 package pinout

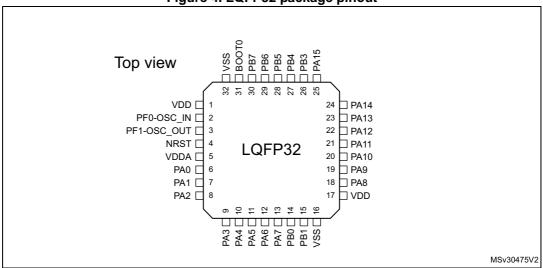

Figure 4. LQFP32 package pinout

Table 13. Alternate functions selected through GPIOB\_AFR registers for port B

| Pin name | AF0                 | AF1      | AF2        | AF3       |

|----------|---------------------|----------|------------|-----------|

| PB0      | EVENTOUT            | TIM3_CH3 | TIM1_CH2N  | -         |

| PB1      | TIM14_CH1           | TIM3_CH4 | TIM1_CH3N  | -         |

| PB2      | -                   | -        | -          | -         |

| PB3      | SPI1_SCK, I2S1_CK   | EVENTOUT | TIM2_CH2   | -         |

| PB4      | SPI1_MISO, I2S1_MCK | TIM3_CH1 | EVENTOUT   | -         |

| PB5      | SPI1_MOSI, I2S1_SD  | TIM3_CH2 | TIM16_BKIN | I2C1_SMBA |

| PB6      | USART1_TX           | I2C1_SCL | TIM16_CH1N | -         |

| PB7      | USART1_RX           | I2C1_SDA | TIM17_CH1N | -         |

| PB8      | -                   | I2C1_SCL | TIM16_CH1  | -         |

| PB9      | IR_OUT              | I2C1_SDA | TIM17_CH1  | EVENTOUT  |

| PB10     | -                   | I2C1_SCL | TIM2_CH3   | -         |

| PB11     | EVENTOUT            | I2C1_SDA | TIM2_CH4   | -         |

| PB12     | SPI1_NSS            | EVENTOUT | TIM1_BKIN  | -         |

| PB13     | SPI1_SCK            | -        | TIM1_CH1N  | -         |

| PB14     | SPI1_MISO           | -        | TIM1_CH2N  | -         |

| PB15     | SPI1_MOSI           | -        | TIM1_CH3N  | -         |

**Table 16. Current characteristics**

| Symbol                 | Ratings                                                                         | Max.                 | Unit |

|------------------------|---------------------------------------------------------------------------------|----------------------|------|

| $\Sigma I_{VDD}$       | Total current into sum of all VDD power lines (source) <sup>(1)</sup>           | 120                  |      |

| ΣI <sub>VSS</sub>      | Total current out of sum of all VSS ground lines (sink) <sup>(1)</sup>          | -120                 |      |

| I <sub>VDD(PIN)</sub>  | Maximum current into each VDD power pin (source) <sup>(1)</sup>                 | 100                  |      |

| I <sub>VSS(PIN)</sub>  | Maximum current out of each VSS ground pin (sink) <sup>(1)</sup>                | -100                 |      |

|                        | Output current sunk by any I/O and control pin                                  | 25                   |      |

| I <sub>IO(PIN)</sub>   | Output current source by any I/O and control pin                                | -25                  |      |

| 71                     | Total output current sunk by sum of all I/Os and control pins <sup>(2)</sup>    | 80                   |      |

| $\Sigma I_{IO(PIN)}$   | Total output current sourced by sum of all I/Os and control pins <sup>(2)</sup> | -80                  | mA   |

|                        | Injected current on B, FT and FTf pins                                          | -5/+0 <sup>(4)</sup> |      |

| $I_{INJ(PIN)}^{(3)}$   | Injected current on TC and RST pin                                              | ± 5                  |      |

|                        | Injected current on TTa pins <sup>(5)</sup>                                     | ± 5                  | 1    |

| ΣΙ <sub>ΙΝJ(PIN)</sub> | Total injected current (sum of all I/O and control pins) <sup>(6)</sup>         | ± 25                 |      |

- All main power (VDD, VDDA) and ground (VSS, VSSA) pins must always be connected to the external power supply, in the

permitted range.

- 2. This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count QFP packages.

- 3. A positive injection is induced by V<sub>IN</sub> > V<sub>DDIOx</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 15: Voltage characteristics* for the maximum allowed input voltage values.

- 4. Positive injection is not possible on these I/Os and does not occur for input voltages lower than the specified maximum value.

- On these I/Os, a positive injection is induced by V<sub>IN</sub> > V<sub>DDA</sub>. Negative injection disturbs the analog performance of the device. See note <sup>(2)</sup> below *Table 52: ADC accuracy*.

- When several inputs are submitted to a current injection, the maximum ΣI<sub>INJ(PIN)</sub> is the absolute sum of the positive and negative injected currents (instantaneous values).

**Table 17. Thermal characteristics**

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | -65 to +150 | °C   |

| $T_J$            | Maximum junction temperature | 150         | °C   |

Table 25. Typical and maximum current consumption in Stop and Standby modes

| Sum              | Para-                                |                                                         |                                                         |                                                         | Typ @V <sub>DD</sub> (V <sub>DD</sub> = V <sub>DDA</sub> ) |                                                  |       |       |       | Max <sup>(1)</sup>     | )                      |                         |                    |     |                    |  |

|------------------|--------------------------------------|---------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------|-------|-------|-------|------------------------|------------------------|-------------------------|--------------------|-----|--------------------|--|

| Sym-<br>bol      |                                      |                                                         | Conditions                                              |                                                         | 2.4 V                                                      | 2.7 V                                            | 3.0 V | 3.3 V | 3.6 V | T <sub>A</sub> = 25 °C | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit               |     |                    |  |

|                  | Supply current                       |                                                         | gulator in run<br>de, all oscillators<br>F              | 15                                                      | 15.1                                                       | 15.3                                             | 15.5  | 15.7  | 16    | 18 <sup>(2)</sup>      | 38                     | 55 <sup>(2)</sup>       |                    |     |                    |  |

| I <sub>DD</sub>  | in Stop<br>mode                      | Regulator in low-<br>power mode, all<br>oscillators OFF |                                                         | 3.2                                                     | 3.3                                                        | 3.4                                              | 3.5   | 3.7   | 4     | 5.5 <sup>(2)</sup>     | 22                     | 41 <sup>(2)</sup>       |                    |     |                    |  |

|                  | Supply current                       | LSI<br>ON                                               | ON and IWDG                                             | 0.8                                                     | 1.0                                                        | 1.1                                              | 1.2   | 1.4   | 1.5   | -                      | -                      | -                       |                    |     |                    |  |

|                  | in<br>Standby<br>mode                | Standby                                                 | LSI<br>OF                                               | OFF and IWDG<br>F                                       | 0.7                                                        | 0.8                                              | 0.9   | 1.0   | 1.1   | 1.3                    | 2 <sup>(2)</sup>       | 2.5                     | 3 <sup>(2)</sup>   |     |                    |  |

|                  | Supply<br>current<br>in Stop<br>mode | current                                                 | current                                                 | current                                                 | NO                                                         | Regulator in run<br>mode, all<br>oscillators OFF | 1.9   | 2     | 2.2   | 2.3                    | 2.5                    | 2.6                     | 3.5 <sup>(2)</sup> | 3.5 | 4.5 <sup>(2)</sup> |  |

|                  |                                      |                                                         | monitoring (                                            | Regulator in low-<br>power mode, all<br>oscillators OFF | 1.9                                                        | 2                                                | 2.2   | 2.3   | 2.5   | 2.6                    | 3.5 <sup>(2)</sup>     | 3.5                     | 4.5 <sup>(2)</sup> | μA  |                    |  |

|                  | Supply current in Standby mode       | Supply current                                          | V <sub>DDA</sub> m                                      | LSI ON and<br>IWDG ON                                   | 2.3                                                        | 2.5                                              | 2.7   | 2.9   | 3.1   | 3.3                    | -                      | -                       | -                  |     |                    |  |

|                  |                                      |                                                         | LSI OFF and<br>IWDG OFF                                 | 1.8                                                     | 1.9                                                        | 2                                                | 2.2   | 2.3   | 2.5   | 3.5 <sup>(2)</sup>     | 3.5                    | 4.5 <sup>(2)</sup>      |                    |     |                    |  |

| I <sub>DDA</sub> | Supply<br>current<br>in Stop<br>mode |                                                         |                                                         | )FF                                                     | Regulator in run<br>mode, all<br>oscillators OFF           | 1.1                                              | 1.2   | 1.2   | 1.2   | 1.3                    | 1.4                    | -                       | -                  | -   |                    |  |

|                  |                                      | monitoring O                                            | Regulator in low-<br>power mode, all<br>oscillators OFF | 1.1                                                     | 1.2                                                        | 1.2                                              | 1.2   | 1.3   | 1.4   | -                      | -                      | -                       |                    |     |                    |  |

|                  | Supply                               | V <sub>DDA</sub> mc                                     | LSI ON and<br>IWDG ON                                   | 1.5                                                     | 1.6                                                        | 1.7                                              | 1.8   | 1.9   | 2.0   | -                      | i                      | -                       |                    |     |                    |  |

|                  | in<br>Standby<br>mode                | Λ                                                       | LSI OFF and<br>IWDG OFF                                 | 1                                                       | 1.0                                                        | 1.1                                              | 1.1   | 1.2   | 1.2   | -                      | -                      | -                       |                    |     |                    |  |

<sup>1.</sup> Data based on characterization results, not tested in production unless otherwise specified.

<sup>2.</sup> Data based on characterization results and tested in production (using one common test limit for sum of  $I_{DD}$  and  $I_{DDA}$ ).

Table 27. Typical current consumption, code executing from Flash memory, running from HSE 8 MHz crystal

|                  |                                  |                   | Typical ı               | run mode              | Typical S               | unit                     |      |

|------------------|----------------------------------|-------------------|-------------------------|-----------------------|-------------------------|--------------------------|------|

| Symbol           | Parameter                        | f <sub>HCLK</sub> | Peripheral<br>s enabled | Peripheral s disabled | Peripheral<br>s enabled | Peripheral<br>s disabled | -    |

|                  |                                  | 48MHz             | 20.2                    | 12.3                  | 11.1                    | 2.9                      |      |

|                  |                                  | 36 MHz            | 15.3                    | 9.5                   | 8.4                     | 2.4                      |      |

|                  |                                  | 32 MHz            | 13.6                    | 8.6                   | 7.5                     | 2.2                      |      |

|                  |                                  | 24 MHz            | 10.5                    | 6.7                   | 5.9                     | 1.8                      |      |

| ,                | Current<br>from V <sub>DD</sub>  | 16 MHz            | 7.2                     | 4.7                   | 4.1                     | 1.4                      | mA   |

| I <sub>DD</sub>  | supply                           | 8 MHz             | 3.8                     | 2.7                   | 2.3                     | 0.9                      | IIIA |

|                  |                                  | 4 MHz             | 2.4                     | 1.8                   | 1.7                     | 0.9                      |      |

|                  |                                  | 2 MHz             | 1.6                     | 1.3                   | 1.2                     | 0.8                      |      |

|                  |                                  | 1 MHz             | 1.2                     | 1.1                   | 1.0                     | 0.8                      |      |

|                  |                                  | 500 kHz           | 1.0                     | 1.0                   | 0.9                     | 0.8                      |      |

|                  |                                  | 48MHz             |                         | 15                    | 55                      |                          |      |

|                  |                                  | 36 MHz            |                         | 1′                    | 17                      |                          |      |

|                  |                                  | 32 MHz            |                         | 10                    | 05                      |                          |      |

|                  |                                  | 24 MHz            |                         | 8                     | 3                       |                          |      |

| ١,               | Current<br>from V <sub>DDA</sub> | 16 MHz            |                         | 6                     | 0                       |                          | uA   |

| I <sub>DDA</sub> | supply                           | 8 MHz             |                         | 2                     | .2                      |                          | uA   |

|                  |                                  | 4 MHz             |                         | 2                     | .2                      |                          |      |

|                  |                                  | 2 MHz             |                         | 2                     | .2                      |                          |      |

|                  |                                  | 1 MHz             |                         | 2                     | .2                      | _                        |      |

|                  |                                  | 500 kHz           |                         | 2                     | .2                      |                          |      |

## I/O system current consumption

The current consumption of the I/O system has two components: static and dynamic.

#### I/O static current consumption

All the I/Os used as inputs with pull-up generate current consumption when the pin is externally held low. The value of this current consumption can be simply computed by using the pull-up/pull-down resistors values given in *Table 46: I/O static characteristics*.

For the output pins, any external pull-down or external load must also be considered to estimate the current consumption.

Additional I/O current consumption is due to I/Os configured as inputs if an intermediate voltage level is externally applied. This current consumption is caused by the input Schmitt

Table 28. Switching output I/O current consumption

| Symbol          | Parameter                  | Conditions <sup>(1)</sup>                                                             | I/O toggling frequency (f <sub>SW</sub> ) | Тур   | Unit |

|-----------------|----------------------------|---------------------------------------------------------------------------------------|-------------------------------------------|-------|------|

|                 |                            |                                                                                       | 4 MHz                                     | 0.07  |      |

|                 |                            | V <sub>DDIOx</sub> = 3.3 V                                                            | 8 MHz                                     | 0.15  |      |

|                 |                            | $C = C_{INT}$                                                                         | 16 MHz                                    | 0.31  |      |

|                 |                            |                                                                                       | 24 MHz                                    | 0.53  |      |

|                 |                            |                                                                                       | 48 MHz                                    | 0.92  |      |

|                 |                            |                                                                                       | 4 MHz                                     | 0.18  |      |

|                 |                            | V <sub>DDIOx</sub> = 3.3 V                                                            | 8 MHz                                     | 0.37  |      |

|                 |                            | C <sub>EXT</sub> = 0 pF                                                               | 16 MHz                                    | 0.76  |      |

|                 |                            | $C = C_{INT} + C_{EXT} + C_{S}$                                                       | 24 MHz                                    | 1.39  |      |

|                 | I/O current<br>consumption |                                                                                       | 48 MHz                                    | 2.188 |      |

|                 |                            |                                                                                       | 4 MHz                                     | 0.32  | mA   |

|                 |                            | $V_{DDIOx} = 3.3 \text{ V}$ $C_{EXT} = 10 \text{ pF}$ $C = C_{INT} + C_{EXT} + C_{S}$ | 8 MHz                                     | 0.64  |      |

|                 |                            |                                                                                       | 16 MHz                                    | 1.25  |      |

|                 |                            |                                                                                       | 24 MHz                                    | 2.23  |      |

| I <sub>SW</sub> |                            |                                                                                       | 48 MHz                                    | 4.442 |      |

| '500            |                            | $V_{DDIOx} = 3.3 \text{ V}$ $C_{EXT} = 22 \text{ pF}$ $C = C_{INT} + C_{EXT} + C_{S}$ | 4 MHz                                     | 0.49  |      |

|                 |                            |                                                                                       | 8 MHz                                     | 0.94  |      |

|                 |                            |                                                                                       | 16 MHz                                    | 2.38  |      |

|                 |                            |                                                                                       | 24 MHz                                    | 3.99  |      |

|                 |                            |                                                                                       | 4 MHz                                     | 0.64  |      |

|                 |                            | $V_{DDIOx} = 3.3 \text{ V}$                                                           | 8 MHz                                     | 1.25  |      |

|                 |                            | $C_{EXT} = 33 \text{ pF}$<br>$C = C_{INT} + C_{EXT} + C_{S}$                          | 16 MHz                                    | 3.24  |      |

|                 |                            | INT EXT 0                                                                             | 24 MHz                                    | 5.02  |      |

|                 |                            | V <sub>DDIOx</sub> = 3.3 V                                                            | 4 MHz                                     | 0.81  |      |

|                 |                            | $C_{EXT} = 47 \text{ pF}$                                                             | 8 MHz                                     | 1.7   |      |

|                 |                            | $C = C_{INT} + C_{EXT} + C_{S}$ $C = C_{int}$                                         | 16 MHz                                    | 3.67  |      |

|                 |                            | V <sub>DDIOx</sub> = 2.4 V                                                            | 4 MHz                                     | 0.66  |      |

|                 |                            | $C_{EXT} = 47 \text{ pF}$                                                             | 8 MHz                                     | 1.43  |      |

|                 |                            | $C = C_{INT} + C_{EXT} + C_{S}$                                                       | 16 MHz                                    | 2.45  |      |

|                 |                            | C = C <sub>int</sub>                                                                  | 24 MHz                                    | 4.97  |      |

<sup>1.</sup> C<sub>S</sub> = 7 pF (estimated value).

## On-chip peripheral current consumption

The current consumption of the on-chip peripherals is given in *Table 29*. The MCU is placed under the following conditions:

- All I/O pins are in analog mode

- All peripherals are disabled unless otherwise mentioned

- The given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- Ambient operating temperature and supply voltage conditions summarized in *Table 15: Voltage characteristics*

- The power consumption of the digital part of the on-chip peripherals is given in *Table 29*. The power consumption of the analog part of the peripherals (where applicable) is indicated in each related section of the datasheet.

Table 29. Peripheral current consumption

|     | Peripheral               | Typical consumption at 25 °C | Unit    |

|-----|--------------------------|------------------------------|---------|

|     | BusMatrix <sup>(1)</sup> | 3.8                          |         |

|     | DMA1                     | 6.3                          |         |

|     | SRAM                     | 0.7                          |         |

|     | Flash memory interface   | 15.2                         |         |

| AHB | CRC                      | 1.61                         | ∧ /٨/Ы⇒ |

| АПБ | GPIOA                    | 9.4                          | µA/MHz  |

|     | GPIOB                    | 11.6                         |         |

|     | GPIOC                    | 1.9                          |         |

|     | GPIOF                    | 0.8                          |         |

|     | All AHB peripherals      | 47.5                         |         |

| Symbol           | Parameter      | Conditions                                         | Min <sup>(1)</sup> | Unit   |

|------------------|----------------|----------------------------------------------------|--------------------|--------|

| N <sub>END</sub> | Endurance      | $T_A = -40 \text{ to } +105 ^{\circ}\text{C}$      | 10                 | kcycle |

| t <sub>RET</sub> | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C  | 30                 |        |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C | 10                 | Year   |

|                  |                | 10 kcycle <sup>(2)</sup> at T <sub>A</sub> = 55 °C | 20                 |        |

Table 40. Flash memory endurance and data retention

- 1. Data based on characterization results, not tested in production.

- 2. Cycling performed over the whole temperature range.

#### 6.3.11 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 41*. They are based on the EMS levels and classes defined in application note AN1709.

Level/ **Parameter Symbol Conditions Class**  $V_{DD} = 3.3 \text{ V, LQFP48, T}_{A} = +25 \text{ °C,}$ Voltage limits to be applied on any I/O pin  $f_{HCLK} = 48 \text{ MHz},$ 2B  $V_{\text{FESD}}$ to induce a functional disturbance conforming to IEC 61000-4-2 Fast transient voltage burst limits to be  $V_{DD} = 3.3 \text{ V, LQFP48, } T_A = +25^{\circ}\text{C,}$  $f_{HCLK}$  = 48 MHz, applied through 100 pF on  $V_{DD}$  and  $V_{SS}$ 4B  $V_{EFTB}$ pins to induce a functional disturbance conforming to IEC 61000-4-4

**Table 41. EMS characteristics**

## Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

## **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to +/-8 mA, and sink or source up to +/- 20 mA (with a relaxed  $V_{OL}/V_{OH}$ ).

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 6.2*:

- The sum of the currents sourced by all the I/Os on V<sub>DDIOX</sub>, plus the maximum consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating ΣI<sub>VDD</sub> (see *Table 15: Voltage characteristics*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub>, plus the maximum consumption of the MCU sunk on V<sub>SS</sub>, cannot exceed the absolute maximum rating ΣI<sub>VSS</sub> (see Table 15: Voltage characteristics).

## **Output voltage levels**

Unless otherwise specified, the parameters given in the table below are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 18: General operating conditions*. All I/Os are CMOS- and TTL-compliant (FT, TTa or TC unless otherwise specified).

Table 47. Output voltage characteristics<sup>(1)</sup>

| Symbol                            | Parameter                                               | Conditions                                                  | Min                     | Max | Unit  |

|-----------------------------------|---------------------------------------------------------|-------------------------------------------------------------|-------------------------|-----|-------|

| V <sub>OL</sub>                   | Output low level voltage for an I/O pin                 | CMOS port <sup>(2)</sup>                                    | -                       | 0.4 | .,    |

| V <sub>OH</sub>                   | Output high level voltage for an I/O pin                | I <sub>IO</sub>   = 8 mA<br>V <sub>DDIOx</sub> ≥ 2.7 V      | V <sub>DDIOx</sub> -0.4 | -   | V     |

| V <sub>OL</sub>                   | Output low level voltage for an I/O pin                 | TTL port <sup>(2)</sup>                                     | -                       | 0.4 | .,    |

| V <sub>OH</sub>                   | Output high level voltage for an I/O pin                | I <sub>IO</sub>   = 8 mA<br>V <sub>DDIOx</sub> ≥ 2.7 V      | 2.4                     | -   | V     |

| V <sub>OL</sub> <sup>(3)</sup>    | Output low level voltage for an I/O pin                 | I <sub>IO</sub>   = 20 mA                                   | -                       | 1.3 | V     |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin                | V <sub>DDIOx</sub> ≥ 2.7 V                                  | V <sub>DDIOx</sub> -1.3 | -   | \ \ \ |

| V <sub>OL</sub> <sup>(3)</sup>    | Output low level voltage for an I/O pin                 | I <sub>IO</sub>   = 6 mA                                    | -                       | 0.4 | V     |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin                | IIIOI – O IIIA                                              | V <sub>DDIOx</sub> -0.4 | -   | V     |

| V <sub>OLFm+</sub> <sup>(3)</sup> | Output low level voltage for an FTf I/O pin in Fm+ mode | $ I_{IO}  = 20 \text{ mA}$<br>$V_{DDIOx} \ge 2.7 \text{ V}$ | -                       | 0.4 | V     |

| 02                                | Tim mode                                                | I <sub>IO</sub>   = 10 mA                                   | -                       | 0.4 | V     |

The I<sub>IO</sub> current sourced or sunk by the device must always respect the absolute maximum rating specified in Table 15:

Voltage characteristics, and the sum of the currents sourced or sunk by all the I/Os (I/O ports and control pins) must always respect the absolute maximum ratings ΣI<sub>IO</sub>.

<sup>2.</sup> TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

<sup>3.</sup> Data based on characterization results. Not tested in production.

Table 58. I<sup>2</sup>C analog filter characteristics<sup>(1)</sup>

| Symbol          | Parameter                                                        | Min               | Max                | Unit |  |

|-----------------|------------------------------------------------------------------|-------------------|--------------------|------|--|

| t <sub>AF</sub> | Maximum width of spikes that are suppressed by the analog filter | 50 <sup>(2)</sup> | 260 <sup>(3)</sup> | ns   |  |

- 1. Guaranteed by design, not tested in production.

- 2. Spikes with widths below t<sub>AF(min)</sub> are filtered.

- 3. Spikes with widths above  $t_{\text{AF}(\text{max})}$  are not filtered

## SPI/I<sup>2</sup>S characteristics

Unless otherwise specified, the parameters given in *Table 59* for SPI or in *Table 60* for I<sup>2</sup>S are derived from tests performed under the ambient temperature, f<sub>PCLKx</sub> frequency and supply voltage conditions summarized in *Table 18: General operating conditions*.

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI and WS, CK, SD for I<sup>2</sup>S).

Table 59. SPI characteristics<sup>(1)</sup>

| Symbol                                    | Parameter                        | Conditions                                            | Min         | Max         | Unit  |  |

|-------------------------------------------|----------------------------------|-------------------------------------------------------|-------------|-------------|-------|--|

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub> | CDI alask fraguanav              | Master mode -                                         |             | 18          | MHz   |  |

|                                           | SPI clock frequency              | Slave mode -                                          |             | 18          | IVI□∠ |  |

| t <sub>r(SCK)</sub>                       | SPI clock rise and fall time     | Capacitive load: C = 15 pF                            | -           | 6           | ns    |  |

| t <sub>su(NSS)</sub>                      | NSS setup time                   | Slave mode                                            | 4Tpclk      | -           |       |  |

| t <sub>h(NSS)</sub>                       | NSS hold time                    | Slave mode                                            | 2Tpclk + 10 | -           |       |  |

| t <sub>w(SCKH)</sub>                      | SCK high and low time            | Master mode, f <sub>PCLK</sub> = 36 MHz,<br>presc = 4 | Tpclk/2 -2  | Tpclk/2 + 1 |       |  |

| t <sub>su(MI)</sub>                       | Data input setup time            | Master mode                                           | 4           | -           |       |  |

| t <sub>su(SI)</sub>                       |                                  | Slave mode                                            | 5           | -           |       |  |

| t <sub>h(MI)</sub>                        | Data input hold time             | Master mode                                           | 4           | -           |       |  |

| t <sub>h(SI)</sub>                        | Data input hold time             | Slave mode                                            | 5           | -           |       |  |

| t <sub>a(SO)</sub> <sup>(2)</sup>         | Data output access time          | Slave mode, f <sub>PCLK</sub> = 20 MHz                | 0           | 3Tpclk      |       |  |

| t <sub>dis(SO)</sub> (3)                  | Data output disable time         | Slave mode                                            | 0           | 18          |       |  |

| t <sub>v(SO)</sub>                        | Data output valid time           | Slave mode (after enable edge)                        | -           | 22.5        |       |  |

| t <sub>v(MO)</sub>                        | Data output valid time           | Master mode (after enable edge)                       | -           | 6           |       |  |

| t <sub>h(SO)</sub>                        | Data output hold time            | Slave mode (after enable edge)                        | 11.5        | -           |       |  |

| t <sub>h(MO)</sub>                        | Data output noid time            | Master mode (after enable edge)                       | 2           | -           |       |  |

| DuCy(SCK)                                 | SPI slave input clock duty cycle | Slave mode                                            | 25          | 75          | %     |  |

- 1. Data based on characterization results, not tested in production.

- 2. Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

- 3. Min time is for the minimum time to invalidate the output and the max time is for the maximum time to put the data in Hi-Z

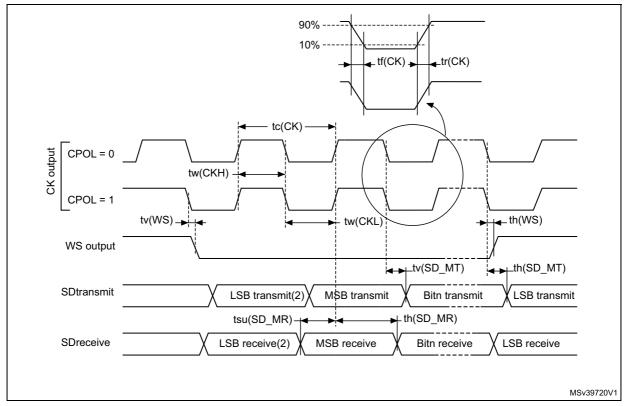

Figure 30. I<sup>2</sup>S master timing diagram (Philips protocol)

- 1. Data based on characterization results, not tested in production.

- LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

577

Table 63. UFQFPN32 package mechanical data

| Symbol | millimeters |       | inches <sup>(1)</sup> |        |        |        |

|--------|-------------|-------|-----------------------|--------|--------|--------|

|        | Min         | Тур   | Max                   | Min    | Тур    | Max    |

| Α      | 0.500       | 0.550 | 0.600                 | 0.0197 | 0.0217 | 0.0236 |

| A1     | 0.000       | 0.020 | 0.050                 | 0.0000 | 0.0008 | 0.0020 |

| A3     | -           | 0.152 | -                     | -      | 0.0060 | -      |

| b      | 0.180       | 0.230 | 0.280                 | 0.0071 | 0.0091 | 0.0110 |

| D      | 4.900       | 5.000 | 5.100                 | 0.1929 | 0.1969 | 0.2008 |

| D1     | 3.400       | 3.500 | 3.600                 | 0.1339 | 0.1378 | 0.1417 |

| D2     | 3.400       | 3.500 | 3.600                 | 0.1339 | 0.1378 | 0.1417 |

| Е      | 4.900       | 5.000 | 5.100                 | 0.1929 | 0.1969 | 0.2008 |

| E1     | 3.400       | 3.500 | 3.600                 | 0.1339 | 0.1378 | 0.1417 |

| E2     | 3.400       | 3.500 | 3.600                 | 0.1339 | 0.1378 | 0.1417 |

| е      | -           | 0.500 | -                     | -      | 0.0197 |        |

| L      | 0.300       | 0.400 | 0.500                 | 0.0118 | 0.0157 | 0.0197 |

| ddd    | -           | -     | 0.080                 | -      | -      | 0.0031 |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

5.30 3.80 3.80 3.80 3.80 3.80 3.80 AOB8\_FP\_V2

Figure 38. Recommended footprint for UFQFPN32 package

1. Dimensions are expressed in millimeters.

1. Values in inches are converted from mm and rounded to 4 decimal digits.

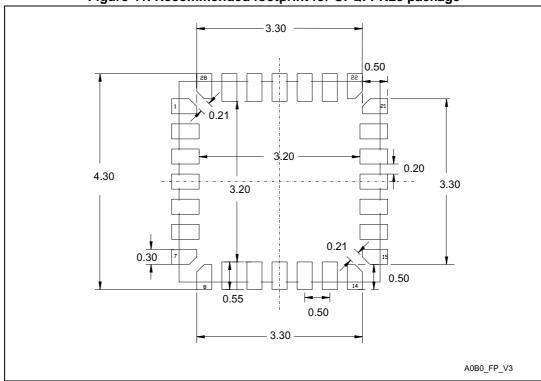

Figure 41. Recommended footprint for UFQFPN28 package

1. Dimensions are expressed in millimeters.

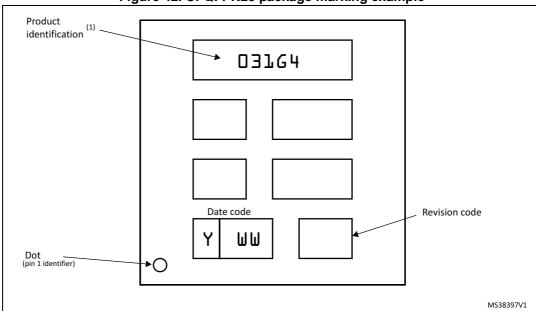

## **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Figure 42. UFQFPN28 package marking example

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

## 7.7.2 Selecting the product temperature range

When ordering the microcontroller, the temperature range is specified in the ordering information scheme shown in *Section 8: Ordering information*.

Each temperature range suffix corresponds to a specific guaranteed ambient temperature at maximum dissipation and, to a specific maximum junction temperature.

As applications do not commonly use the STM32F031x4/x6 at maximum dissipation, it is useful to calculate the exact power consumption and junction temperature to determine which temperature range will be best suited to the application.

The following examples show how to calculate the temperature range needed for a given application.

#### **Example 1: High-performance application**

Assuming the following application conditions:

Maximum ambient temperature  $T_{Amax}$  = 80 °C (measured according to JESD51-2),  $I_{DDmax}$  = 50 mA,  $V_{DD}$  = 3.5 V, maximum 20 I/Os used at the same time in output at low level with  $I_{OL}$  = 8 mA,  $V_{OL}$ = 0.4 V and maximum 8 I/Os used at the same time in output at low level with  $I_{OL}$  = 20 mA,  $V_{OL}$ = 1.3 V

```

P_{INTmax} = 50 \text{ mA} \times 3.5 \text{ V} = 175 \text{ mW}

```

$P_{IOmax = 20} \times 8 \text{ mA} \times 0.4 \text{ V} + 8 \times 20 \text{ mA} \times 1.3 \text{ V} = 272 \text{ mW}$

This gives: P<sub>INTmax</sub> = 175 mW and P<sub>IOmax</sub> = 272 mW:

$$P_{Dmax} = 175 + 272 = 447 \text{ mW}$$

Using the values obtained in *Table 68* T<sub>Jmax</sub> is calculated as follows:

```

For LQFP48, 55 °C/W

```

$$T_{\text{lmax}} = 80 \,^{\circ}\text{C} + (55 \,^{\circ}\text{C/W} \times 447 \,^{\circ}\text{mW}) = 80 \,^{\circ}\text{C} + 24.585 \,^{\circ}\text{C} = 104.585 \,^{\circ}\text{C}$$

This is within the range of the suffix 6 version parts ( $-40 < T_J < 105$  °C) see *Table 18: General operating conditions*.

In this case, parts must be ordered at least with the temperature range suffix 6 (see Section 8: Ordering information).

Note:

With this given  $P_{Dmax we}$  can find the TAmax allowed for a given device temperature range (order code suffix 6 or 7).

```

Suffix 6: T_{Amax} = T_{Jmax} - (55^{\circ}\text{C/W} \times 447 \text{ mW}) = 105\text{-}24.585 = 80.415 ^{\circ}\text{C}

Suffix 7: T_{Amax} = T_{Jmax} - (55^{\circ}\text{C/W} \times 447 \text{ mW}) = 125\text{-}24.585 = 100.415 ^{\circ}\text{C}

```

## **Example 2: High-temperature application**

Using the same rules, it is possible to address applications that run at high ambient temperatures with a low dissipation, as long as junction temperature  $T_J$  remains within the specified range.

57

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics - All rights reserved