Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | I²C, IrDA, LINbus, SPI, UART/USART                                    |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 23                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 4K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 13x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 28-UFQFN                                                              |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f031g6u6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

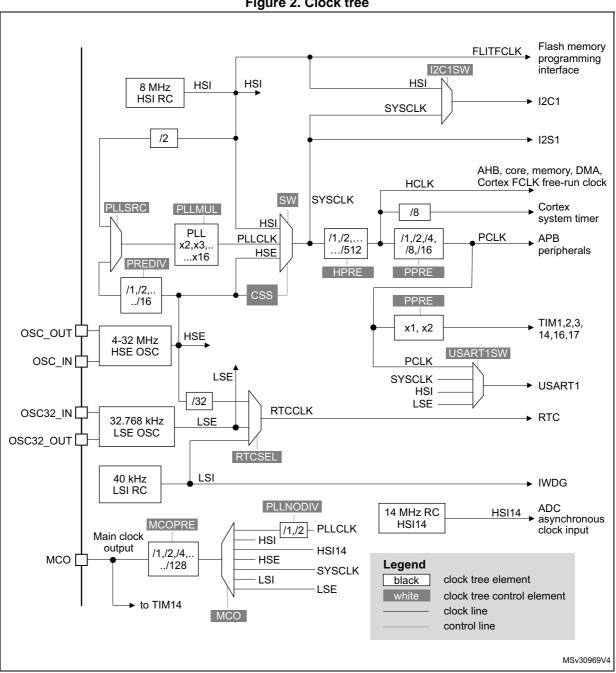

Figure 2. Clock tree

#### 3.7 General-purpose inputs/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions.

The I/O configuration can be locked if needed following a specific sequence in order to avoid spurious writing to the I/Os registers.

DocID025743 Rev 5

## 3.16 Serial wire debug port (SW-DP)

An ARM SW-DP interface is provided to allow a serial wire debugging tool to be connected to the MCU.

## 6 Electrical characteristics

## 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

### 6.1.1 Minimum and maximum values

Unless otherwise specified, the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean  $\pm 3\sigma$ ).

## 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = V_{DDA} = 3.3$  V. They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean  $\pm 2\sigma$ ).

### 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

## 6.1.4 Loading capacitor

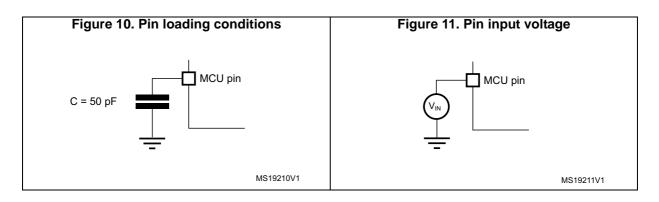

The loading conditions used for pin parameter measurement are shown in *Figure 10*.

### 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 11*.

DocID025743 Rev 5

## 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 15: Voltage characteristics*, *Table 16: Current characteristics* and *Table 17: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                             | Ratings                                               | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Max                                     | Unit |

|------------------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------|

| V <sub>DD</sub> -V <sub>SS</sub>   | External main supply voltage                          | - 0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4.0                                     | V    |

| $V_{DDA} - V_{SS}$                 | External analog supply voltage                        | - 0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4.0                                     | V    |

| V <sub>DD</sub> -V <sub>DDA</sub>  | Allowed voltage difference for $V_{DD} > V_{DDA}$     | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0.4                                     | V    |

| V <sub>BAT</sub> –V <sub>SS</sub>  | External backup supply voltage                        | - 0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4.0                                     | V    |

|                                    | Input voltage on FT and FTf pins                      | rnal main supply voltage- 0.34.0rnal analog supply voltage- 0.34.0ved voltage difference for $V_{DD} > V_{DDA}$ -0.4rnal backup supply voltage- 0.34.0t voltage on FT and FTf pins $V_{SS} - 0.3$ $V_{DDIOx} + 4.0^{(3)}$ t voltage on TTa pins $V_{SS} - 0.3$ 4.009.09.0t voltage on any other pin $V_{SS} - 0.3$ 4.0ations between different $V_{DD}$ power pins-50ations between all the different ground-50trostatic discharge voltagesee Section 6.3.12: Electrical | V <sub>DDIOx</sub> + 4.0 <sup>(3)</sup> | V    |

| V <sub>IN</sub> <sup>(2)</sup>     | Input voltage on TTa pins                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | V                                       |      |

| VIN Ý                              | BOOT0                                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9.0                                     | V    |

|                                    | Input voltage on any other pin                        | V <sub>SS</sub> - 0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4.0                                     | V    |

| ΔV <sub>DDx</sub>                  | Variations between different $V_{DD}$ power pins      | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 50                                      | mV   |

| V <sub>SSx</sub> - V <sub>SS</sub> | Variations between all the different ground pins      | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 50                                      | mV   |

| V <sub>ESD(HBM)</sub>              | Electrostatic discharge voltage<br>(human body model) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                         | -    |

| Table 15. | Voltage | characteristics <sup>(1)</sup> |

|-----------|---------|--------------------------------|

|-----------|---------|--------------------------------|

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2. V<sub>IN</sub> maximum must always be respected. Refer to *Table 16: Current characteristics* for the maximum allowed injected current values.

3. Valid only if the internal pull-up/pull-down resistors are disabled. If internal pull-up or pull-down resistor is enabled, the maximum limit is 4 V.

| Cu m            | Doro                                                              |                     |                                                         |                    | Тур          | @V <sub>DD</sub> (                                      | V <sub>DD</sub> = V | ' <sub>DDA</sub> ) | -     |                           | Max <sup>(1)</sup>       | )                          |                    |     |                    |    |

|-----------------|-------------------------------------------------------------------|---------------------|---------------------------------------------------------|--------------------|--------------|---------------------------------------------------------|---------------------|--------------------|-------|---------------------------|--------------------------|----------------------------|--------------------|-----|--------------------|----|

| bol             | Sym- Para-<br>bol meter                                           |                     | Conditions                                              |                    | 2.4 V        | 2.7 V                                                   | 3.0 V               | 3.3 V              | 3.6 V | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 ℃ | T <sub>A</sub> =<br>105 °C | Unit               |     |                    |    |

|                 | Supply current                                                    |                     | gulator in run<br>de, all oscillators<br>F              | 15                 | 15.1         | 15.3                                                    | 15.5                | 15.7               | 16    | 18 <sup>(2)</sup>         | 38                       | 55 <sup>(2)</sup>          |                    |     |                    |    |

| I <sub>DD</sub> | in Stop<br>mode                                                   | pov                 | gulator in low-<br>wer mode, all<br>cillators OFF       | 3.2                | 3.3          | 3.4                                                     | 3.5                 | 3.7                | 4     | 5.5 <sup>(2)</sup>        | 22                       | 41 <sup>(2)</sup>          |                    |     |                    |    |

|                 | Supply<br>current                                                 | LSI<br>ON           | l ON and IWDG                                           | 0.8                | 1.0          | 1.1                                                     | 1.2                 | 1.4                | 1.5   | -                         | -                        | -                          |                    |     |                    |    |

|                 |                                                                   | LSI<br>OF           | I OFF and IWDG<br>F                                     | 0.7                | 0.8          | 0.9                                                     | 1.0                 | 1.1                | 1.3   | 2 <sup>(2)</sup>          | 2.5                      | 3 <sup>(2)</sup>           |                    |     |                    |    |

|                 | mode                                                              | current             | current<br>in Stop                                      | current<br>in Stop | NO           | Regulator in run<br>mode, all<br>oscillators OFF        | 1.9                 | 2                  | 2.2   | 2.3                       | 2.5                      | 2.6                        | 3.5 <sup>(2)</sup> | 3.5 | 4.5 <sup>(2)</sup> |    |

|                 |                                                                   |                     |                                                         |                    | monitoring C | Regulator in low-<br>power mode, all<br>oscillators OFF | 1.9                 | 2                  | 2.2   | 2.3                       | 2.5                      | 2.6                        | 3.5 <sup>(2)</sup> | 3.5 | 4.5 <sup>(2)</sup> | μA |

|                 |                                                                   | V <sub>DDA</sub> m  | LSI ON and<br>IWDG ON                                   | 2.3                | 2.5          | 2.7                                                     | 2.9                 | 3.1                | 3.3   | -                         | -                        | -                          |                    |     |                    |    |

|                 | in<br>Standby<br>mode                                             | -                   | LSI OFF and<br>IWDG OFF                                 | 1.8                | 1.9          | 2                                                       | 2.2                 | 2.3                | 2.5   | 3.5 <sup>(2)</sup>        | 3.5                      | 4.5 <sup>(2)</sup>         |                    |     |                    |    |

| IDDA            | IDDA<br>Supply<br>current<br>in Stop<br>mode<br>Supply<br>current | Ц                   | Regulator in run<br>mode, all<br>oscillators OFF        | 1.1                | 1.2          | 1.2                                                     | 1.2                 | 1.3                | 1.4   | -                         | -                        | -                          |                    |     |                    |    |

|                 |                                                                   | 0                   | Regulator in low-<br>power mode, all<br>oscillators OFF | 1.1                | 1.2          | 1.2                                                     | 1.2                 | 1.3                | 1.4   | -                         | -                        | -                          |                    |     |                    |    |

|                 |                                                                   | V <sub>DDA</sub> mo | LSI ON and<br>IWDG ON                                   | 1.5                | 1.6          | 1.7                                                     | 1.8                 | 1.9                | 2.0   | -                         | -                        | -                          |                    |     |                    |    |

|                 | in<br>Standby<br>mode                                             | >                   | LSI OFF and<br>IWDG OFF                                 | 1                  | 1.0          | 1.1                                                     | 1.1                 | 1.2                | 1.2   | -                         | -                        | -                          |                    |     |                    |    |

| Table 25. Typical and maximum current consum | pption in Stop and Standby modes |

|----------------------------------------------|----------------------------------|

|                                              |                                  |

1. Data based on characterization results, not tested in production unless otherwise specified.

2. Data based on characterization results and tested in production (using one common test limit for sum of I<sub>DD</sub> and I<sub>DDA</sub>).

#### **On-chip peripheral current consumption**

The current consumption of the on-chip peripherals is given in *Table 29*. The MCU is placed under the following conditions:

- All I/O pins are in analog mode

- All peripherals are disabled unless otherwise mentioned

- The given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- Ambient operating temperature and supply voltage conditions summarized in *Table 15: Voltage characteristics*

- The power consumption of the digital part of the on-chip peripherals is given in *Table 29*. The power consumption of the analog part of the peripherals (where applicable) is indicated in each related section of the datasheet.

|     | Peripheral               | Typical consumption at 25 °C | Unit   |

|-----|--------------------------|------------------------------|--------|

|     | BusMatrix <sup>(1)</sup> | 3.8                          |        |

| АНВ | DMA1                     | 6.3                          |        |

|     | SRAM                     | 0.7                          |        |

|     | Flash memory interface   | 15.2                         |        |

|     | CRC                      | 1.61                         |        |

| АПБ | GPIOA                    | 9.4                          | µA/MHz |

|     | GPIOB                    | 11.6                         |        |

|     | GPIOC                    | 1.9                          |        |

|     | GPIOF                    | 0.8                          |        |

|     | All AHB peripherals      | 47.5                         |        |

#### Table 29. Peripheral current consumption

## Low-speed internal (LSI) RC oscillator

| Table 37. | LSI | oscillator | characteristics <sup>(1)</sup> |

|-----------|-----|------------|--------------------------------|

|-----------|-----|------------|--------------------------------|

| Symbol                               | Parameter                        | Min | Тур  | Max | Unit |

|--------------------------------------|----------------------------------|-----|------|-----|------|

| f <sub>LSI</sub>                     | Frequency                        | 30  | 40   | 50  | kHz  |

| t <sub>su(LSI)</sub> <sup>(2)</sup>  | LSI oscillator startup time      | -   | -    | 85  | μs   |

| I <sub>DDA(LSI)</sub> <sup>(2)</sup> | LSI oscillator power consumption | -   | 0.75 | 1.2 | μA   |

1. V<sub>DDA</sub> = 3.3 V, T<sub>A</sub> = –40 to 105  $^\circ\text{C}$  unless otherwise specified.

2. Guaranteed by design, not tested in production.

## 6.3.9 PLL characteristics

The parameters given in *Table 38* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 18: General operating conditions*.

| Symbol                | Parameter                      |                   | Value |                    |      |  |  |

|-----------------------|--------------------------------|-------------------|-------|--------------------|------|--|--|

| Symbol                | Falameter                      | Min               | Тур   | Max                | Unit |  |  |

| f                     | PLL input clock <sup>(1)</sup> | 1 <sup>(2)</sup>  | 8.0   | 24 <sup>(2)</sup>  | MHz  |  |  |

| f <sub>PLL_IN</sub>   | PLL input clock duty cycle     | 40 <sup>(2)</sup> | -     | 60 <sup>(2)</sup>  | %    |  |  |

| f <sub>PLL_OUT</sub>  | PLL multiplier output clock    | 16 <sup>(2)</sup> | -     | 48                 | MHz  |  |  |

| t <sub>LOCK</sub>     | PLL lock time                  | -                 | -     | 200 <sup>(2)</sup> | μs   |  |  |

| Jitter <sub>PLL</sub> | Cycle-to-cycle jitter          | -                 | _     | 300 <sup>(2)</sup> | ps   |  |  |

Table 38. PLL characteristics

1. Take care to use the appropriate multiplier factors to obtain PLL input clock values compatible with the range defined by f<sub>PLL\_OUT</sub>.

2. Guaranteed by design, not tested in production.

## 6.3.10 Memory characteristics

### **Flash memory**

The characteristics are given at  $T_A = -40$  to 105 °C unless otherwise specified.

| Table 39. Flash memory characterist | CS |

|-------------------------------------|----|

|-------------------------------------|----|

| Symbol             | Parameter               | Conditions                       | Min | Тур  | Max <sup>(1)</sup> | Unit |

|--------------------|-------------------------|----------------------------------|-----|------|--------------------|------|

| t <sub>prog</sub>  | 16-bit programming time | T <sub>A</sub> = - 40 to +105 °C | 40  | 53.5 | 60                 | μs   |

| t <sub>ERASE</sub> | Page (1 KB) erase time  | T <sub>A</sub> = - 40 to +105 °C | 20  | -    | 40                 | ms   |

| t <sub>ME</sub>    | Mass erase time         | T <sub>A</sub> = - 40 to +105 °C | 20  | -    | 40                 | ms   |

|                    |                         | Write mode                       | -   | -    | 10                 | mA   |

| IDD                | Supply current          | Erase mode                       | -   | -    | 12                 | mA   |

1. Guaranteed by design, not tested in production.

#### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to +/-8 mA, and sink or source up to +/- 20 mA (with a relaxed  $V_{OL}/V_{OH}$ ).

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in Section 6.2:

- The sum of the currents sourced by all the I/Os on V<sub>DDIOx</sub>, plus the maximum consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating ΣI<sub>VDD</sub> (see *Table 15: Voltage characteristics*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub>, plus the maximum consumption of the MCU sunk on V<sub>SS</sub>, cannot exceed the absolute maximum rating ΣI<sub>VSS</sub> (see *Table 15: Voltage characteristics*).

#### **Output voltage levels**

Unless otherwise specified, the parameters given in the table below are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 18: General operating conditions*. All I/Os are CMOS- and TTL-compliant (FT, TTa or TC unless otherwise specified).

| Symbol                            | Parameter                                                  | Conditions                                              | Min                     | Max | Unit |

|-----------------------------------|------------------------------------------------------------|---------------------------------------------------------|-------------------------|-----|------|

| V <sub>OL</sub>                   | Output low level voltage for an I/O pin                    | CMOS port <sup>(2)</sup>                                | -                       | 0.4 |      |

| V <sub>OH</sub>                   | Output high level voltage for an I/O pin                   | I <sub>IO</sub>   = 8 mA<br>V <sub>DDIOx</sub> ≥ 2.7 V  | V <sub>DDIOx</sub> -0.4 | -   | V    |

| V <sub>OL</sub>                   | Output low level voltage for an I/O pin                    | TTL port <sup>(2)</sup>                                 | -                       | 0.4 |      |

| V <sub>OH</sub>                   | Output high level voltage for an I/O pin                   | I <sub>IO</sub>   = 8 mA<br>V <sub>DDIOx</sub> ≥ 2.7 V  | 2.4                     | -   | V    |

| V <sub>OL</sub> <sup>(3)</sup>    | Output low level voltage for an I/O pin                    | I <sub>IO</sub>   = 20 mA                               | -                       | 1.3 | V    |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin                   | V <sub>DDIOx</sub> ≥ 2.7 V                              | V <sub>DDIOx</sub> -1.3 | -   | v    |

| V <sub>OL</sub> <sup>(3)</sup>    | Output low level voltage for an I/O pin                    | l <sub>IO</sub>   = 6 mA                                | -                       | 0.4 | V    |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin                   | 1101 - 0 MA                                             | V <sub>DDIOx</sub> -0.4 | -   | v    |

| V <sub>OLFm+</sub> <sup>(3)</sup> | Output low level voltage for an FTf I/O pin in<br>Fm+ mode | I <sub>IO</sub>   = 20 mA<br>V <sub>DDIOx</sub> ≥ 2.7 V | -                       | 0.4 | V    |

|                                   |                                                            | I <sub>IO</sub>   = 10 mA                               | -                       | 0.4 | V    |

#### Table 47. Output voltage characteristics<sup>(1)</sup>

1. The I<sub>IO</sub> current sourced or sunk by the device must always respect the absolute maximum rating specified in Table 15: Voltage characteristics, and the sum of the currents sourced or sunk by all the I/Os (I/O ports and control pins) must always respect the absolute maximum ratings  $\Sigma I_{IO}$ .

2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

3. Data based on characterization results. Not tested in production.

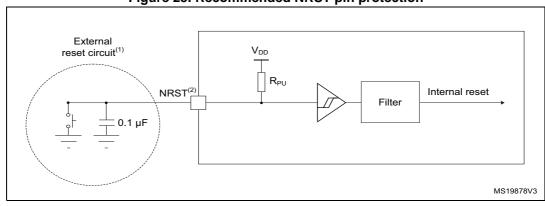

Figure 23. Recommended NRST pin protection

1. The external capacitor protects the device against parasitic resets.

The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 49: NRST pin characteristics. Otherwise the reset will not be taken into account by the device.

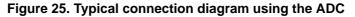

## 6.3.16 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 50* are derived from tests performed under the conditions summarized in *Table 18: General operating conditions*.

Note: It is recommended to perform a calibration after each power-up.

| Symbol                             | Parameter                                     | Conditions                                            | Min   | Тур | Max              | Unit               |

|------------------------------------|-----------------------------------------------|-------------------------------------------------------|-------|-----|------------------|--------------------|

| V <sub>DDA</sub>                   | Analog supply voltage for ADC ON              | -                                                     | 2.4   | -   | 3.6              | V                  |

| I <sub>DDA (ADC)</sub>             | Current consumption of the ADC <sup>(1)</sup> | V <sub>DDA</sub> = 3.3 V                              | -     | 0.9 | -                | mA                 |

| f <sub>ADC</sub>                   | ADC clock frequency                           | -                                                     | 0.6   | -   | 14               | MHz                |

| f <sub>S</sub> <sup>(2)</sup>      | Sampling rate                                 | 12-bit resolution                                     | 0.043 | -   | 1                | MHz                |

| f <sub>TRIG</sub> <sup>(2)</sup>   | External trigger frequency                    | f <sub>ADC</sub> = 14 MHz,<br>12-bit resolution       | -     | -   | 823              | kHz                |

|                                    |                                               | 12-bit resolution                                     | -     | -   | 17               | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub>                   | Conversion voltage range                      | -                                                     | 0     | -   | V <sub>DDA</sub> | V                  |

| R <sub>AIN</sub> <sup>(2)</sup>    | External input impedance                      | See <i>Equation 1</i> and <i>Table 51</i> for details | -     | -   | 50               | kΩ                 |

| R <sub>ADC</sub> <sup>(2)</sup>    | Sampling switch resistance                    | -                                                     | -     | -   | 1                | kΩ                 |

| C <sub>ADC</sub> <sup>(2)</sup>    | Internal sample and hold capacitor            | -                                                     | -     | -   | 8                | pF                 |

| <b>↓</b> (2)(3)                    | Calibration time                              | f <sub>ADC</sub> = 14 MHz                             |       | 5.9 |                  | μs                 |

| t <sub>CAL</sub> <sup>(2)(3)</sup> |                                               | -                                                     | 83    |     |                  | 1/f <sub>ADC</sub> |

Table 50. ADC characteristics

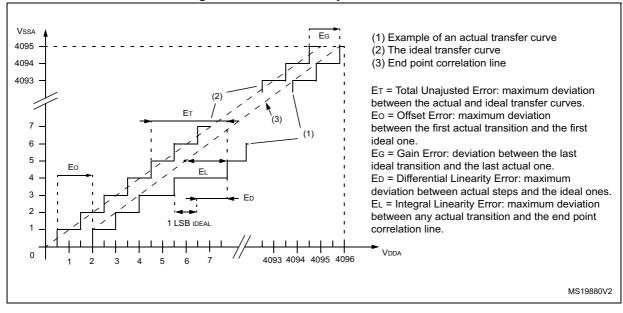

#### Figure 24. ADC accuracy characteristics

Refer to Table 50: ADC characteristics for the values of  $\mathsf{R}_{AIN},\,\mathsf{R}_{ADC}$  and  $\mathsf{C}_{ADC}.$ 1.

$C_{parasitic}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high  $C_{parasitic}$  value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced. 2.

#### **General PCB design guidelines**

Power supply decoupling should be performed as shown in Figure 12: Power supply scheme. The 10 nF capacitor should be ceramic (good quality) and it should be placed as close as possible to the chip.

## 6.3.17 Temperature sensor characteristics

| Table | 53. | ΤS | characteristics |

|-------|-----|----|-----------------|

| TUDIC |     |    |                 |

| Symbol                             | Parameter                                      | Min  | Тур  | Max  | Unit  |

|------------------------------------|------------------------------------------------|------|------|------|-------|

| T <sub>L</sub> <sup>(1)</sup>      | V <sub>SENSE</sub> linearity with temperature  | -    | ± 1  | ± 2  | °C    |

| Avg_Slope <sup>(1)</sup>           | Average slope                                  | 4.0  | 4.3  | 4.6  | mV/°C |

| V <sub>30</sub>                    | Voltage at 30 °C (± 5 °C) <sup>(2)</sup>       | 1.34 | 1.43 | 1.52 | V     |

| t <sub>START</sub> <sup>(1)</sup>  | ADC_IN16 buffer startup time                   | -    | -    | 10   | μs    |

| t <sub>S_temp</sub> <sup>(1)</sup> | ADC sampling time when reading the temperature | 4    | -    | -    | μs    |

1. Guaranteed by design, not tested in production.

2. Measured at  $V_{DDA}$  = 3.3 V ± 10 mV. The  $V_{30}$  ADC conversion result is stored in the TS\_CAL1 byte. Refer to Table 3: Temperature sensor calibration values.

## 6.3.18 V<sub>BAT</sub> monitoring characteristics

| Symbol                             | Parameter                                    |    | Тур    | Max | Unit |

|------------------------------------|----------------------------------------------|----|--------|-----|------|

| R                                  | Resistor bridge for V <sub>BAT</sub>         | -  | 2 x 50 | -   | kΩ   |

| Q                                  | Ratio on V <sub>BAT</sub> measurement        | -  | 2      | -   | -    |

| Er <sup>(1)</sup>                  | Error on Q                                   | -1 | -      | +1  | %    |

| t <sub>S_vbat</sub> <sup>(1)</sup> | ADC sampling time when reading the $V_{BAT}$ | 4  | -      | -   | μs   |

#### Table 54. V<sub>BAT</sub> monitoring characteristics

1. Guaranteed by design, not tested in production.

## 6.3.19 Timer characteristics

The parameters given in the following tables are guaranteed by design.

Refer to Section 6.3.14: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                                       | Parameter                  | Conditions                    | Min | Тур                     | Max | Unit                 |

|----------------------------------------------|----------------------------|-------------------------------|-----|-------------------------|-----|----------------------|

| t <sub>res/TIM</sub> ) Timer resolution time |                            | -                             | -   | 1                       | -   | t <sub>TIMxCLK</sub> |

| t <sub>res(TIM)</sub>                        |                            | f <sub>TIMxCLK</sub> = 48 MHz | -   | 20.8                    | -   | ns                   |

| f                                            | Timer external clock       | -                             | -   | f <sub>TIMxCLK</sub> /2 | -   | MHz                  |

| f <sub>EXT</sub>                             | frequency on CH1 to<br>CH4 | f <sub>TIMxCLK</sub> = 48 MHz | -   | 24                      | -   | MHz                  |

|                                              | 16-bit timer maximum       | -                             | -   | 2 <sup>16</sup>         | -   | t <sub>TIMxCLK</sub> |

| t <sub>MAX_COUNT</sub>                       | period                     | f <sub>TIMxCLK</sub> = 48 MHz | -   | 1365                    | -   | μs                   |

|                                              | 32-bit counter             | -                             | -   | 2 <sup>32</sup>         | -   | t <sub>TIMxCLK</sub> |

|                                              | maximum period             | f <sub>TIMxCLK</sub> = 48 MHz | -   | 89.48                   | -   | S                    |

| Table | 55. | TIMx | characteristics |

|-------|-----|------|-----------------|

|-------|-----|------|-----------------|

| Symbol          | Parameter                                                        | Parameter Min     |                    | Unit |

|-----------------|------------------------------------------------------------------|-------------------|--------------------|------|

| t <sub>AF</sub> | Maximum width of spikes that are suppressed by the analog filter | 50 <sup>(2)</sup> | 260 <sup>(3)</sup> | ns   |

| Table 58. I <sup>2</sup> C analog filter characteris | stics <sup>(1)</sup> |  |

|------------------------------------------------------|----------------------|--|

|------------------------------------------------------|----------------------|--|

1. Guaranteed by design, not tested in production.

2. Spikes with widths below  $t_{AF(min)}$  are filtered.

3. Spikes with widths above  $t_{AF(max)}$  are not filtered

.

## SPI/I<sup>2</sup>S characteristics

Unless otherwise specified, the parameters given in *Table 59* for SPI or in *Table 60* for  $I^2S$  are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and supply voltage conditions summarized in *Table 18: General operating conditions*.

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI and WS, CK, SD for I<sup>2</sup>S).

| Symbol                                       | Parameter                           | Conditions                                            | Min         | Max         | Unit   |

|----------------------------------------------|-------------------------------------|-------------------------------------------------------|-------------|-------------|--------|

| f <sub>SCK</sub>                             | SPI clock frequency                 | Master mode                                           | -           | 18          | MHz    |

| 1/t <sub>c(SCK)</sub>                        | SPI Clock frequency                 | Slave mode                                            | -           | 18          | IVITIZ |

| t <sub>r(SCK)</sub><br>t <sub>f(SCK)</sub>   | SPI clock rise and fall time        | Capacitive load: C = 15 pF                            | -           | 6           | ns     |

| t <sub>su(NSS)</sub>                         | NSS setup time                      | Slave mode                                            | 4Tpclk      | -           |        |

| t <sub>h(NSS)</sub>                          | NSS hold time                       | Slave mode                                            | 2Tpclk + 10 | -           |        |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time               | Master mode, f <sub>PCLK</sub> = 36 MHz,<br>presc = 4 | Tpclk/2 -2  | Tpclk/2 + 1 |        |

| t <sub>su(MI)</sub>                          | Data input sotup timo               | Master mode                                           | 4           | -           |        |

| t <sub>su(SI)</sub>                          |                                     | Slave mode                                            | 5           | -           |        |

| t <sub>h(MI)</sub>                           | Data input hold time                | Master mode                                           | 4           | -           |        |

| t <sub>h(SI)</sub>                           | Data input hold time                | Slave mode                                            | 5           | -           | ns     |

| t <sub>a(SO)</sub> <sup>(2)</sup>            | Data output access time             | Slave mode, f <sub>PCLK</sub> = 20 MHz                | 0           | 3Tpclk      |        |

| t <sub>dis(SO)</sub> <sup>(3)</sup>          | Data output disable time            | Slave mode                                            | 0           | 18          |        |

| t <sub>v(SO)</sub>                           | Data output valid time              | Slave mode (after enable edge)                        | -           | 22.5        |        |

| t <sub>v(MO)</sub>                           | Data output valid time              | Master mode (after enable edge)                       | -           | 6           |        |

| t <sub>h(SO)</sub>                           | Data output hold time               | Slave mode (after enable edge)                        | 11.5        | -           |        |

| t <sub>h(MO)</sub>                           |                                     | Master mode (after enable edge)                       | 2           | -           |        |

| DuCy(SCK)                                    | SPI slave input clock<br>duty cycle | Slave mode                                            | 25          | 75          | %      |

| Table 5 | 59. SPI | characteristics( | 1) |

|---------|---------|------------------|----|

|---------|---------|------------------|----|

1. Data based on characterization results, not tested in production.

2. Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

3. Min time is for the minimum time to invalidate the output and the max time is for the maximum time to put the data in Hi-Z

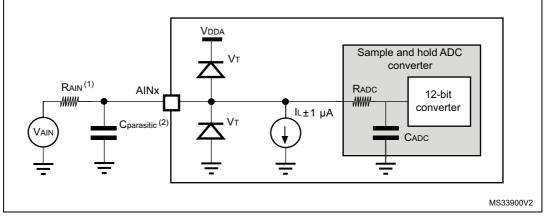

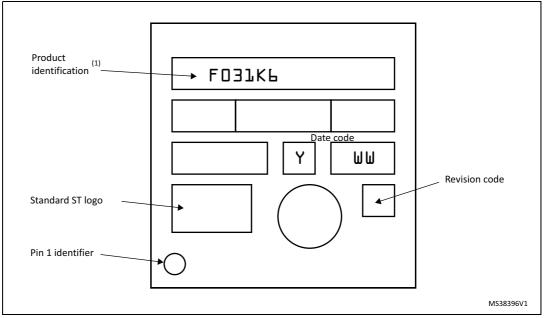

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

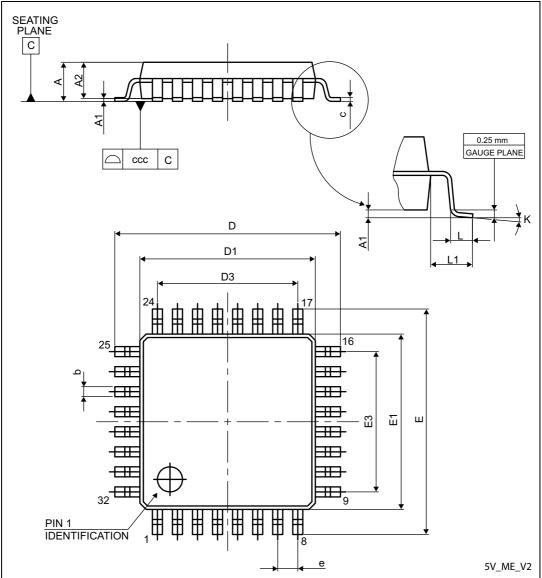

## 7.2 LQFP32 package information

LQFP32 is a 32-pin, 7 x 7 mm low-profile quad flat package.

Figure 34. LQFP32 package outline

1. Drawing is not to scale.

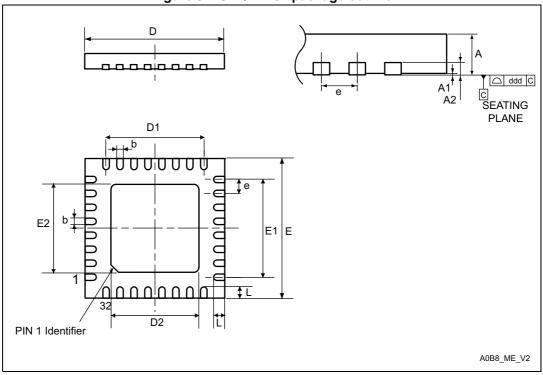

Figure 37. UFQFPN32 package outline

1. Drawing is not to scale.

- 2. All leads/pads should also be soldered to the PCB to improve the lead/pad solder joint life.

- 3. There is an exposed die pad on the underside of the UFQFPN package. This pad is used for the device ground and must be connected. It is referred to as pin 0 in *Table: Pin definitions*.

|        | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|-------|-------|-----------------------|--------|--------|--|

| Symbol | Min         | Тур   | Мах   | Min                   | Тур    | Мах    |  |

| А      | 0.500       | 0.550 | 0.600 | 0.0197                | 0.0217 | 0.0236 |  |

| A1     | 0.000       | 0.020 | 0.050 | 0.0000                | 0.0008 | 0.0020 |  |

| A3     | -           | 0.152 | -     | -                     | 0.0060 | -      |  |

| b      | 0.180       | 0.230 | 0.280 | 0.0071                | 0.0091 | 0.0110 |  |

| D      | 4.900       | 5.000 | 5.100 | 0.1929                | 0.1969 | 0.2008 |  |

| D1     | 3.400       | 3.500 | 3.600 | 0.1339                | 0.1378 | 0.1417 |  |

| D2     | 3.400       | 3.500 | 3.600 | 0.1339                | 0.1378 | 0.1417 |  |

| E      | 4.900       | 5.000 | 5.100 | 0.1929                | 0.1969 | 0.2008 |  |

| E1     | 3.400       | 3.500 | 3.600 | 0.1339                | 0.1378 | 0.1417 |  |

| E2     | 3.400       | 3.500 | 3.600 | 0.1339                | 0.1378 | 0.1417 |  |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |  |

| L      | 0.300       | 0.400 | 0.500 | 0.0118                | 0.0157 | 0.0197 |  |

| ddd    | -           | -     | 0.080 | -                     | -      | 0.0031 |  |

Table 63. UFQFPN32 package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

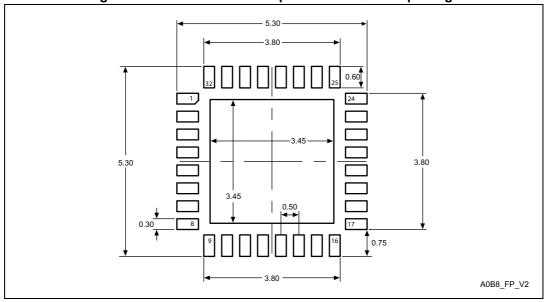

#### Figure 38. Recommended footprint for UFQFPN32 package

1. Dimensions are expressed in millimeters.

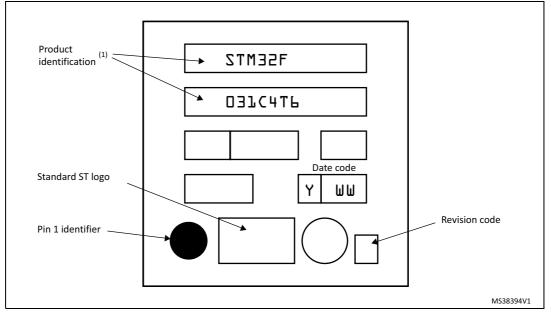

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

#### Figure 39. UFQFPN32 package marking example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

# 8 Ordering information

For a list of available options (memory, package, and so on) or for further information on any aspect of this device, please contact your nearest ST sales office.

| Example:                             | STM32 | F | 031 | G | 6 | Т | 6 | > |

|--------------------------------------|-------|---|-----|---|---|---|---|---|

|                                      |       |   |     |   |   |   |   |   |

| Device family                        |       |   |     |   |   |   |   |   |

| STM32 = ARM-based 32-bit microcontro | oller |   |     |   |   |   |   |   |

| Product type                         |       |   |     |   |   |   |   |   |

| F = General-purpose                  |       |   |     |   |   |   |   |   |

|                                      |       |   |     |   |   |   |   |   |

| Sub-family                           |       |   |     |   |   |   |   |   |

| 031 = STM32F031xx                    |       |   |     |   |   |   |   |   |

| Pin count                            |       |   |     |   |   |   |   |   |

| F = 20 pins                          |       |   |     |   |   |   |   |   |

| E = 25 pins                          |       |   |     |   |   |   |   |   |

| G = 28 pins                          |       |   |     |   |   |   |   |   |

| K = 32 pins                          |       |   |     |   |   |   |   |   |

| C = 48 pins                          |       |   |     |   |   |   |   |   |

| User code memory size                |       |   |     |   |   |   |   |   |

| 4 = 16 Kbyte                         |       |   |     |   |   |   |   |   |

| 6 = 32 Kbyte                         |       |   |     |   |   |   |   |   |

| Package                              |       |   |     |   |   |   |   |   |

| P = TSSOP                            |       |   |     |   |   |   |   |   |

| U = UFQFPN                           |       |   |     |   |   |   |   |   |

| T = LQFP                             |       |   |     |   |   |   |   |   |

| Y = WLCSP                            |       |   |     |   |   |   |   |   |

| Temperature range                    |       |   |     |   |   |   |   |   |

| 6 = -40 °C to +85 °C                 |       |   |     |   |   |   |   |   |

| 7 = -40 °C to +105 °C                |       |   |     |   |   |   |   |   |

| Options                              |       |   |     |   |   |   |   |   |

xxx = code ID of programmed parts (includes packing type) TR = tape and reel packing blank = tray packing

# 9 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13-Jan-2014 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 11-Jul-2014 | 2        | <ul> <li>Changed the document status to Datasheet - production data.</li> <li>Updated the following: <ul> <li>Table: STM32F031x4/6 family device features and peripheral counts,</li> <li>Figure: Clock tree,</li> <li>Figure: Power supply scheme,</li> <li>Table: Peripheral current consumption.</li> </ul> </li> <li>Replaced Table Typical current consumption in Run mode, code with data processing running from Flash and Table Typical current consumption in Sleep mode, code running from Flash or RAM with Table: Typical current consumption from Flash, running from HSE 8 MHz crystal.</li> <li>Added the LQFP32 package: updates in Section: Description, Section: Pinouts and pin description and Section: Package information.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                      |

| 28-Aug-2015 | 3        | <ul> <li>Updated:</li> <li><i>Figure 9:</i> STM32F031x6 memory map</li> <li>AF1 alternate functions for PA0, PA1, PA2, PA3 and PA4 in Table 12: Alternate functions selected through <i>GPIOA_AFR</i> registers for port A</li> <li>the footnote for V<sub>IN</sub> max value in Table 15: Voltage characteristics</li> <li>the footnote for max V<sub>IN</sub> in Table 18: General operating conditions</li> <li>Table 22: Embedded internal reference voltage with the addition of t<sub>START</sub> parameter</li> <li>Table 50: ADC characteristics</li> <li>Table 53: TS characteristics: removed the min. value for t<sub>START</sub> parameter</li> <li>the typical value for R parameter in Table 54: VBAT monitoring characteristics</li> <li>the structure of Section 7: Package information.</li> <li>Added:</li> <li>Figure 33: LQFP48 marking example (package top view), Figure 39: UFQFPN32 marking example (package top view), Figure 39: UFQFPN32 marking example (package top view), Figure 42: UFQFPN28 marking example (package top view), Figure 42: TSSOP20 marking example (package top view)</li> </ul> |

| Date        | Revision         | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16-Dec-2015 | 4<br>(continued) | <ul> <li>Section 6.3.16: 12-bit ADC characteristics - changed introductory sentence</li> <li>Table 60: I<sup>2</sup>S characteristics: table reorganized, t<sub>v(SD_ST)</sub> max value updated</li> <li>Section 7: Package information:</li> <li>Figure 41: Recommended footprint for UFQFPN28 package updated</li> <li>Section 8: Part numbering:</li> <li>added tray packing to options</li> </ul>                                                                                                                                                                                                              |

| 06-Jan-2017 | 5                | <ul> <li>Section 6: Electrical characteristics:</li> <li>Table 34: LSE oscillator characteristics (f<sub>LSE</sub> = 32.768 kHz) - information on configuring different drive capabilities removed. See the corresponding reference manual.</li> <li>Table 22: Embedded internal reference voltage - V<sub>REFINT</sub> values</li> <li>Figure 26: SPI timing diagram - slave mode and CPHA = 0 and Figure 27: SPI timing diagram - slave mode and CPHA = 1 enhanced and corrected</li> <li>Section 8: Ordering information:</li> <li>The name of the section changed from the previous "Part numbering"</li> </ul> |

Table 70. Document revision history (continued)