Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

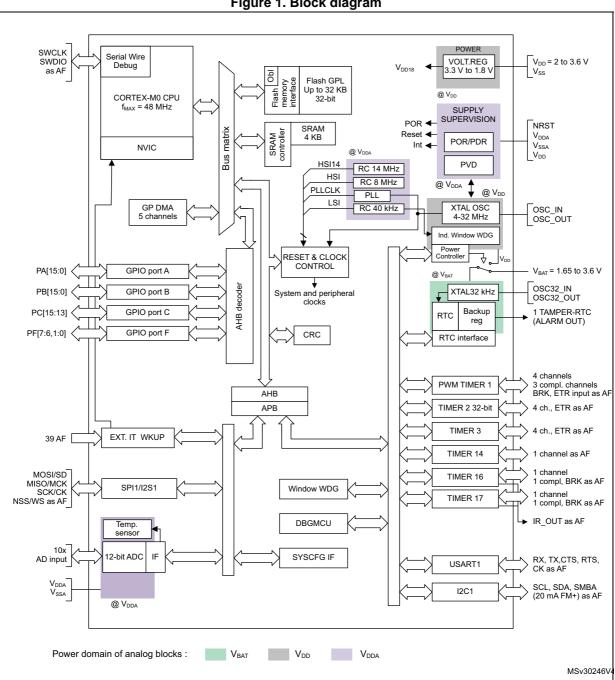

| Core Processor             | ARM® Cortex®-M0                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                       |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 27                                                                    |

| Program Memory Size        | 16KB (16K × 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 4K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 13x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-UFQFN Exposed Pad                                                  |

| Supplier Device Package    | 32-UFQFPN (5x5)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f031k4u6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|   | 3.15   | Serial pe | eripheral interface (SPI) / Inter-integrated sound interface ( $I^2S$ ) . | 21   |

|---|--------|-----------|---------------------------------------------------------------------------|------|

|   | 3.16   | Serial w  | ire debug port (SW-DP)                                                    | 22   |

|   |        |           |                                                                           |      |

| 4 | Pinou  | its and p | oin description                                                           | 23   |

| 5 | Memo   | ory map   | ping                                                                      | 33   |

| 6 | Electr | ical cha  | aracteristics                                                             | 36   |

|   | 6.1    | Parame    | ter conditions                                                            | 36   |

|   |        | 6.1.1     | Minimum and maximum values                                                | . 36 |

|   |        | 6.1.2     | Typical values                                                            | . 36 |

|   |        | 6.1.3     | Typical curves                                                            | . 36 |

|   |        | 6.1.4     | Loading capacitor                                                         | . 36 |

|   |        | 6.1.5     | Pin input voltage                                                         | . 36 |

|   |        | 6.1.6     | Power supply scheme                                                       | . 37 |

|   |        | 6.1.7     | Current consumption measurement                                           | . 38 |

|   | 6.2    | Absolute  | e maximum ratings                                                         | 39   |

|   | 6.3    | Operatir  | ng conditions                                                             | 41   |

|   |        | 6.3.1     | General operating conditions                                              | . 41 |

|   |        | 6.3.2     | Operating conditions at power-up / power-down                             | . 41 |

|   |        | 6.3.3     | Embedded reset and power control block characteristics                    | . 42 |

|   |        | 6.3.4     | Embedded reference voltage                                                | . 43 |

|   |        | 6.3.5     | Supply current characteristics                                            | . 43 |

|   |        | 6.3.6     | Wakeup time from low-power mode                                           | . 53 |

|   |        | 6.3.7     | External clock source characteristics                                     | . 53 |

|   |        | 6.3.8     | Internal clock source characteristics                                     | . 57 |

|   |        | 6.3.9     | PLL characteristics                                                       | . 60 |

|   |        | 6.3.10    | Memory characteristics                                                    | . 60 |

|   |        | 6.3.11    | EMC characteristics                                                       | . 61 |

|   |        | 6.3.12    | Electrical sensitivity characteristics                                    | . 62 |

|   |        | 6.3.13    | I/O current injection characteristics                                     | . 63 |

|   |        | 6.3.14    | I/O port characteristics                                                  | . 64 |

|   |        | 6.3.15    | NRST pin characteristics                                                  | . 69 |

|   |        | 6.3.16    | 12-bit ADC characteristics                                                | . 70 |

|   |        | 6.3.17    | Temperature sensor characteristics                                        | . 74 |

|   |        | 6.3.18    | V <sub>BAT</sub> monitoring characteristics                               | . 74 |

|   |        | 6.3.19    | Timer characteristics                                                     | . 74 |

DocID025743 Rev 5

# 3.4 Cyclic redundancy check calculation unit (CRC)

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a CRC-32 (Ethernet) polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

## 3.5 **Power management**

### 3.5.1 **Power supply schemes**

- $V_{DD} = V_{DDIO1} = 2.0$  to 3.6 V: external power supply for I/Os ( $V_{DDIO1}$ ) and the internal regulator. It is provided externally through VDD pins.

- $V_{DDA}$  = from  $V_{DD}$  to 3.6 V: external analog power supply for ADC, Reset blocks, RCs and PLL (minimum voltage to be applied to  $V_{DDA}$  is 2.4 V when the ADC is used). It is provided externally through VDDA pin. The  $V_{DDA}$  voltage level must be always greater or equal to the  $V_{DD}$  voltage level and must be established first.

- V<sub>BAT</sub> = 1.65 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

For more details on how to connect power pins, refer to *Figure 12: Power supply scheme*.

## 3.5.2 Power supply supervisors

The device has integrated power-on reset (POR) and power-down reset (PDR) circuits. They are always active, and ensure proper operation above a threshold of 2 V. The device remains in reset mode when the monitored supply voltage is below a specified threshold,  $V_{POR/PDR}$ , without the need for an external reset circuit.

- The POR monitors only the V<sub>DD</sub> supply voltage. During the startup phase it is required that V<sub>DDA</sub> should arrive first and be greater than or equal to V<sub>DD</sub>.

- The PDR monitors both the V<sub>DD</sub> and V<sub>DDA</sub> supply voltages, however the V<sub>DDA</sub> power supply supervisor can be disabled (by programming a dedicated Option bit) to reduce the power consumption if the application design ensures that V<sub>DDA</sub> is higher than or equal to V<sub>DD</sub>.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

## 3.5.3 Voltage regulator

The regulator has two operating modes and it is always enabled after reset.

- Main (MR) is used in normal operating mode (Run).

- Low power (LPR) can be used in Stop mode where the power demand is reduced.

#### TIM2, TIM3

STM32F031x4/x6 devices feature two synchronizable 4-channel general-purpose timers. TIM2 is based on a 32-bit auto-reload up/downcounter and a 16-bit prescaler. TIM3 is based on a 16-bit auto-reload up/downcounter and a 16-bit prescaler. They feature 4 independent channels each for input capture/output compare, PWM or one-pulse mode output. This gives up to 12 input captures/output compares/PWMs on the largest packages.

The TIM2 and TIM3 general-purpose timers can work together or with the TIM1 advancedcontrol timer via the Timer Link feature for synchronization or event chaining.

TIM2 and TIM3 both have independent DMA request generation.

These timers are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors.

Their counters can be frozen in debug mode.

#### TIM14

This timer is based on a 16-bit auto-reload upcounter and a 16-bit prescaler.

TIM14 features one single channel for input capture/output compare, PWM or one-pulse mode output.

Its counter can be frozen in debug mode.

#### TIM16 and TIM17

Both timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler.

They each have a single channel for input capture/output compare, PWM or one-pulse mode output.

TIM16 and TIM17 have a complementary output with dead-time generation and independent DMA request generation.

Their counters can be frozen in debug mode.

#### 3.11.3 Independent watchdog (IWDG)

The independent watchdog is based on an 8-bit prescaler and 12-bit downcounter with user-defined refresh window. It is clocked from an independent 40 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free running timer for application timeout management. It is hardware or software configurable through the option bytes. The counter can be frozen in debug mode.

### 3.11.4 System window watchdog (WWDG)

The system window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the APB clock (PCLK). It has an early warning interrupt capability and the counter can be frozen in debug mode.

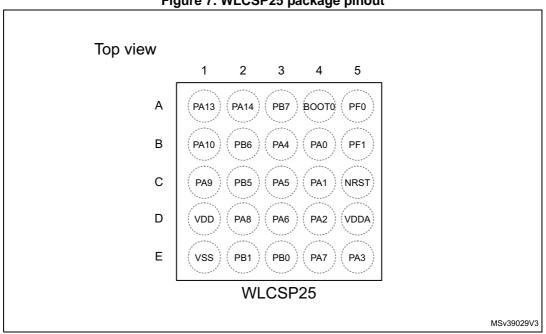

Figure 7. WLCSP25 package pinout

1. The above figure shows the package in top view, changing from bottom view in the previous document versions.

| Pin name | AF0                 | AF1      | AF2        | AF3       |

|----------|---------------------|----------|------------|-----------|

| PB0      | EVENTOUT            | TIM3_CH3 | TIM1_CH2N  | -         |

| PB1      | TIM14_CH1           | TIM3_CH4 | TIM1_CH3N  | -         |

| PB2      | -                   | -        | -          | -         |

| PB3      | SPI1_SCK, I2S1_CK   | EVENTOUT | TIM2_CH2   | -         |

| PB4      | SPI1_MISO, I2S1_MCK | TIM3_CH1 | EVENTOUT   | -         |

| PB5      | SPI1_MOSI, I2S1_SD  | TIM3_CH2 | TIM16_BKIN | I2C1_SMBA |

| PB6      | USART1_TX           | I2C1_SCL | TIM16_CH1N | -         |

| PB7      | USART1_RX           | I2C1_SDA | TIM17_CH1N | -         |

| PB8      | -                   | I2C1_SCL | TIM16_CH1  | -         |

| PB9      | IR_OUT              | I2C1_SDA | TIM17_CH1  | EVENTOUT  |

| PB10     | -                   | I2C1_SCL | TIM2_CH3   | _         |

| PB11     | EVENTOUT            | I2C1_SDA | TIM2_CH4   | -         |

| PB12     | SPI1_NSS            | EVENTOUT | TIM1_BKIN  | -         |

| PB13     | SPI1_SCK            | -        | TIM1_CH1N  | -         |

| PB14     | SPI1_MISO           | -        | TIM1_CH2N  | -         |

| PB15     | SPI1_MOSI           | -        | TIM1_CH3N  | -         |

32/106

DocID025743 Rev 5

5

STM32F031x4 STM32F031x6

# 6 Electrical characteristics

## 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

## 6.1.1 Minimum and maximum values

Unless otherwise specified, the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean  $\pm 3\sigma$ ).

## 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = V_{DDA} = 3.3$  V. They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean  $\pm 2\sigma$ ).

### 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

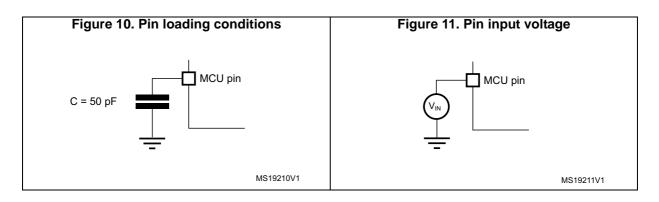

## 6.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 10*.

### 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 11*.

DocID025743 Rev 5

# 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 15: Voltage characteristics*, *Table 16: Current characteristics* and *Table 17: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                                                                      | Ratings                                           | Min                               | Max                                     | Unit |

|-----------------------------------------------------------------------------|---------------------------------------------------|-----------------------------------|-----------------------------------------|------|

| V <sub>DD</sub> -V <sub>SS</sub>                                            | External main supply voltage                      | - 0.3                             | 4.0                                     | V    |

| $V_{DDA} - V_{SS}$                                                          | External analog supply voltage                    | - 0.3                             | 4.0                                     | V    |

| V <sub>DD</sub> -V <sub>DDA</sub>                                           | Allowed voltage difference for $V_{DD} > V_{DDA}$ | -                                 | 0.4                                     | V    |

| V <sub>BAT</sub> –V <sub>SS</sub>                                           | External backup supply voltage                    | - 0.3                             | 4.0                                     | V    |

|                                                                             | Input voltage on FT and FTf pins                  | V <sub>SS</sub> - 0.3             | V <sub>DDIOx</sub> + 4.0 <sup>(3)</sup> | V    |

| V <sub>IN</sub> <sup>(2)</sup>                                              | Input voltage on TTa pins                         | V <sub>SS</sub> - 0.3             | 4.0                                     | V    |

| VIN Ý                                                                       | BOOT0                                             | 0                                 | 9.0                                     | V    |

|                                                                             | Input voltage on any other pin                    | V <sub>SS</sub> - 0.3             | 4.0                                     | V    |

| ΔV <sub>DDx</sub>                                                           | Variations between different $V_{DD}$ power pins  | -                                 | 50                                      | mV   |

| V <sub>SSx</sub> - V <sub>SS</sub>                                          | Variations between all the different ground       |                                   | 50                                      | mV   |

| V <sub>ESD(HBM)</sub> Electrostatic discharge voltage<br>(human body model) |                                                   | see Section 6.3 sensitivity chara |                                         | -    |

| Table 15. | Voltage | characteristics <sup>(1)</sup> |

|-----------|---------|--------------------------------|

|-----------|---------|--------------------------------|

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2. V<sub>IN</sub> maximum must always be respected. Refer to *Table 16: Current characteristics* for the maximum allowed injected current values.

3. Valid only if the internal pull-up/pull-down resistors are disabled. If internal pull-up or pull-down resistor is enabled, the maximum limit is 4 V.

|                 |                     |                           |                   | All peripherals enabled |                     |          |                     | All peripherals disabled |                    |          |                    |      |

|-----------------|---------------------|---------------------------|-------------------|-------------------------|---------------------|----------|---------------------|--------------------------|--------------------|----------|--------------------|------|

| Symbol          | Parameter           | Conditions                | f <sub>HCLK</sub> | Tun                     | N                   | lax @ T, | A <sup>(1)</sup>    | Тур                      | N                  | lax @ T, | A <sup>(1)</sup>   | Unit |

|                 |                     |                           |                   | Тур                     | 25 °C               | 85 °C    | 105 °C              | тур                      | 25 °C              | 85 °C    | 105 °C             |      |

|                 |                     | HSE                       | 48 MHz            | 10.7                    | 11.7 <sup>(2)</sup> | 11.9     | 12.5 <sup>(2)</sup> | 2.4                      | 2.6 <sup>(2)</sup> | 2.7      | 2.9 <sup>(2)</sup> |      |

|                 |                     | bypass,                   | 32 MHz            | 7.1                     | 7.8                 | 8.1      | 8.2                 | 1.6                      | 1.7                | 1.9      | 1.9                |      |

|                 |                     | PLL on                    | 24 MHz            | 5.5                     | 6.3                 | 6.4      | 6.4                 | 1.3                      | 1.4                | 1.5      | 1.5                | 1    |

|                 | Supply              | HSE<br>bypass,<br>PLL off | 8 MHz             | 1.8                     | 2.0                 | 2.0      | 2.1                 | 0.4                      | 0.4                | 0.5      | 0.5                |      |

| I <sub>DD</sub> | current in<br>Sleep |                           | 1 MHz             | 0.2                     | 0.5                 | 0.5      | 0.5                 | 0.1                      | 0.1                | 0.1      | 0.1                | mA   |

|                 | mode                |                           | 48 MHz            | 10.8                    | 11.9                | 12.1     | 12.6                | 2.4                      | 2.7                | 2.7      | 2.9                |      |

|                 |                     | HSI clock,<br>PLL on      | 32 MHz            | 7.3                     | 8.0                 | 8.4      | 8.5                 | 1.7                      | 1.9                | 1.9      | 2.0                |      |

|                 |                     |                           | 24 MHz            | 5.5                     | 6.2                 | 6.5      | 6.5                 | 1.3                      | 1.5                | 1.5      | 1.6                | 1    |

|                 |                     | HSI clock,<br>PLL off     | 8 MHz             | 1.9                     | 2.2                 | 2.3      | 2.4                 | 0.5                      | 0.5                | 0.5      | 0.6                |      |

Table 23. Typical and maximum current consumption from  $V_{DD}$  at 3.6 V (continued)

1. Data based on characterization results, not tested in production unless otherwise specified.

2. Data based on characterization results and tested in production (using one common test limit for sum of  $I_{DD}$  and  $I_{DDA}$ ).

|                  |                         |                           |                   |      | V <sub>DDA</sub>   | = 2.4 V             |                    |      | V <sub>DDA</sub>   | = 3.6 V             | ,                  |      |

|------------------|-------------------------|---------------------------|-------------------|------|--------------------|---------------------|--------------------|------|--------------------|---------------------|--------------------|------|

| Symbol Parameter | Parameter               | Conditions<br>(1)         | f <sub>HCLK</sub> | Turn | М                  | ax @ T <sub>A</sub> | (2)                | Turn | М                  | ax @ T <sub>A</sub> | (2)                | Unit |

|                  |                         |                           |                   | Тур  | 25 °C              | 85 °C               | 105 °C             | Тур  | 25 °C              | 85 °C               | 105 °C             |      |

|                  |                         | HSE                       | 48 MHz            | 150  | 170 <sup>(3)</sup> | 178                 | 182 <sup>(3)</sup> | 164  | 183 <sup>(3)</sup> | 195                 | 198 <sup>(3)</sup> |      |

|                  | Ourselu                 | bypass,                   | 32 MHz            | 104  | 121                | 126                 | 128                | 113  | 129                | 135                 | 138                |      |

|                  | Supply<br>current in    | PLL on                    | 24 MHz            | 82   | 96                 | 100                 | 103                | 88   | 102                | 106                 | 108                |      |

|                  | Run or<br>Sleep         | HSE<br>bypass,<br>PLL off | 8 MHz             | 2.0  | 2.7                | 3.1                 | 3.3                | 3.5  | 3.8                | 4.1                 | 4.4                |      |

| I <sub>DDA</sub> | bypass,                 |                           | 1 MHz             | 2.0  | 2.7                | 3.1                 | 3.3                | 3.5  | 3.8                | 4.1                 | 4.4                | μA   |

|                  | executing               |                           | 48 MHz            | 220  | 240                | 248                 | 252                | 244  | 263                | 275                 | 278                |      |

|                  | from Flash<br>memory or | HSI clock,<br>PLL on      | 32 MHz            | 174  | 191                | 196                 | 198                | 193  | 209                | 215                 | 218                |      |

| RAM              |                         | 24 MHz                    | 152               | 167  | 173                | 174                 | 168                | 183  | 190                | 192                 |                    |      |

|                  |                         | HSI clock,<br>PLL off     | 8 MHz             | 72   | 79                 | 82                  | 83                 | 83.5 | 91                 | 94                  | 95                 |      |

Table 24. Typical and maximum current consumption from the  $\rm V_{DDA}$  supply

Current consumption from the V<sub>DDA</sub> supply is independent of whether the digital peripherals are enabled or disabled, being in Run or Sleep mode or executing from Flash memory or RAM. Furthermore, when the PLL is off, I<sub>DDA</sub> is independent of clock frequencies.

2. Data based on characterization results, not tested in production unless otherwise specified.

3. Data based on characterization results and tested in production (using one common test limit for sum of  $I_{DD}$  and  $I_{DDA}$ ).

#### **Electrical characteristics**

| Symbol          | Parameter   | Conditions <sup>(1)</sup>                                                             | I/O toggling<br>frequency (f <sub>SW</sub> ) | Тур   | Unit |

|-----------------|-------------|---------------------------------------------------------------------------------------|----------------------------------------------|-------|------|

|                 |             |                                                                                       | 4 MHz                                        | 0.07  |      |

|                 |             | V <sub>DDIOx</sub> = 3.3 V                                                            | 8 MHz                                        | 0.15  |      |

|                 |             | C =C <sub>INT</sub>                                                                   | 16 MHz                                       | 0.31  |      |

|                 |             |                                                                                       | 24 MHz                                       | 0.53  |      |

|                 |             |                                                                                       | 48 MHz                                       | 0.92  |      |

|                 |             |                                                                                       | 4 MHz                                        | 0.18  |      |

|                 |             | V <sub>DDIOx</sub> = 3.3 V                                                            | 8 MHz                                        | 0.37  |      |

|                 |             | C <sub>EXT</sub> = 0 pF                                                               | 16 MHz                                       | 0.76  |      |

|                 |             | $C = C_{INT} + C_{EXT} + C_S$                                                         | 24 MHz                                       | 1.39  |      |

|                 |             |                                                                                       | 48 MHz                                       | 2.188 |      |

|                 |             |                                                                                       | 4 MHz                                        | 0.32  |      |

|                 |             | $V_{DDIOx} = 3.3 V$<br>$C_{EXT} = 10 pF$<br>$C = C_{INT} + C_{EXT} + C_S$             | 8 MHz                                        | 0.64  |      |

|                 |             |                                                                                       | 16 MHz                                       | 1.25  |      |

|                 |             |                                                                                       | 24 MHz                                       | 2.23  | mA   |

| I <sub>SW</sub> | I/O current |                                                                                       | 48 MHz                                       | 4.442 |      |

| 'SW             | consumption |                                                                                       | 4 MHz                                        | 0.49  | ША   |

|                 |             | $V_{DDIOx} = 3.3 V$<br>$C_{EXT} = 22 pF$<br>$C = C_{INT} + C_{EXT} + C_S$             | 8 MHz                                        | 0.94  |      |

|                 |             |                                                                                       | 16 MHz                                       | 2.38  |      |

|                 |             |                                                                                       | 24 MHz                                       | 3.99  |      |

|                 |             |                                                                                       | 4 MHz                                        | 0.64  |      |

|                 |             | $V_{\text{DDIOx}} = 3.3 \text{ V}$                                                    | 8 MHz                                        | 1.25  |      |

|                 |             | $C_{EXT} = 33 \text{ pF}$<br>C = C <sub>INT</sub> + C <sub>EXT</sub> + C <sub>S</sub> | 16 MHz                                       | 3.24  |      |

|                 |             |                                                                                       | 24 MHz                                       | 5.02  |      |

|                 |             | V <sub>DDIOx</sub> = 3.3 V                                                            | 4 MHz                                        | 0.81  |      |

|                 |             | C <sub>EXT</sub> = 47 pF                                                              | 8 MHz                                        | 1.7   |      |

|                 |             | $C = C_{INT} + C_{EXT} + C_S$ $C = C_{int}$                                           | 16 MHz                                       | 3.67  |      |

|                 |             | V <sub>DDIOx</sub> = 2.4 V                                                            | 4 MHz                                        | 0.66  |      |

|                 |             | V <sub>DDIOx</sub> = 2.4 V<br>C <sub>EXT</sub> = 47 pF                                | 8 MHz                                        | 1.43  |      |

|                 |             | $C = C_{INT} + C_{EXT} + C_S$                                                         | 16 MHz                                       | 2.45  |      |

|                 |             | $C = C_{int}$                                                                         | 24 MHz                                       | 4.97  |      |

Table 28. Switching output I/O current consumption

1. C<sub>S</sub> = 7 pF (estimated value).

| Symbol           | Parameter      | Conditions                                         | Min <sup>(1)</sup> | Unit   |  |  |  |

|------------------|----------------|----------------------------------------------------|--------------------|--------|--|--|--|

| N <sub>END</sub> | Endurance      | T <sub>A</sub> = -40 to +105 °C                    | 10                 | kcycle |  |  |  |

|                  | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C  | 30                 |        |  |  |  |

| t <sub>RET</sub> |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C | 10                 | Year   |  |  |  |

|                  |                | 10 kcycle <sup>(2)</sup> at T <sub>A</sub> = 55 °C | 20                 |        |  |  |  |

Table 40. Flash memory endurance and data retention

1. Data based on characterization results, not tested in production.

2. Cycling performed over the whole temperature range.

## 6.3.11 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- **FTB**: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 41*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                      |    |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 3.3 V, LQFP48, $T_A$ = +25 °C,<br>f <sub>HCLK</sub> = 48 MHz,<br>conforming to IEC 61000-4-2         | 2B |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD}$ = 3.3 V, LQFP48, T <sub>A</sub> = +25°C,<br>f <sub>HCLK</sub> = 48 MHz,<br>conforming to IEC 61000-4-4 | 4B |

### Table 41. EMS characteristics

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

| Symbol                | Ratings Conditions Pac                                |                                                             | Packages | Class | Maximum<br>value <sup>(1)</sup> | Unit |  |  |  |

|-----------------------|-------------------------------------------------------|-------------------------------------------------------------|----------|-------|---------------------------------|------|--|--|--|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)    | $T_A = +25 \degree C$ , conforming<br>to JESD22-A114        | All      | 2     | 2000                            | ۷    |  |  |  |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model) | T <sub>A</sub> = +25 °C, conforming<br>to ANSI/ESD STM5.3.1 | All      | C3    | 250                             | V    |  |  |  |

Table 43. ESD absolute maximum ratings

1. Data based on characterization results, not tested in production.

#### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin.

- A current injection is applied to each input, output and configurable I/O pin.

These tests are compliant with EIA/JESD 78A IC latch-up standard.

#### Table 44. Electrical sensitivities

| Symbol | Parameter             | Conditions                                    | Class      |

|--------|-----------------------|-----------------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +105 \text{ °C conforming to JESD78A}$ | II level A |

### 6.3.13 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DDIOx}$  (for standard, 3.3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (higher than 5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of the -5  $\mu$ A/+0  $\mu$ A range) or other functional failure (for example reset occurrence or oscillator frequency deviation).

The characterization results are given in Table 45.

Negative induced leakage current is caused by negative injection and positive induced leakage current is caused by positive injection.

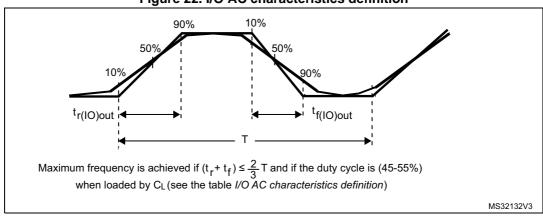

### Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 22* and *Table 48*, respectively. Unless otherwise specified, the parameters given are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 18: General operating conditions*.

| OSPEEDRy<br>[1:0]<br>value <sup>(1)</sup> | Symbol                   | Parameter                                                       | Conditions                                         | Min | Мах | Unit |  |

|-------------------------------------------|--------------------------|-----------------------------------------------------------------|----------------------------------------------------|-----|-----|------|--|

|                                           | f <sub>max(IO)out</sub>  | Maximum frequency <sup>(3)</sup>                                |                                                    | -   | 2   | MHz  |  |

| x0                                        | t <sub>f(IO)out</sub>    | Output fall time                                                | C <sub>L</sub> = 50 pF                             | -   | 125 | ns   |  |

|                                           | t <sub>r(IO)out</sub>    | Output rise time                                                |                                                    | -   | 125 | 113  |  |

|                                           | f <sub>max(IO)out</sub>  | Maximum frequency <sup>(3)</sup>                                |                                                    | -   | 10  | MHz  |  |

| 01                                        | t <sub>f(IO)out</sub>    | Output fall time                                                | C <sub>L</sub> = 50 pF                             | -   | 25  | ns   |  |

|                                           | t <sub>r(IO)out</sub>    | Output rise time                                                |                                                    | -   | 25  |      |  |

|                                           |                          |                                                                 | $C_L$ = 30 pF, $V_{DDIOx} \ge 2.7 V$               | -   | 50  | MHz  |  |

|                                           | f <sub>max(IO)</sub> out | Maximum frequency <sup>(3)</sup>                                | $C_L = 50 \text{ pF}, V_{DDIOx} \ge 2.7 \text{ V}$ | -   | 30  |      |  |

|                                           |                          |                                                                 | $C_L$ = 50 pF, $V_{DDIOx}$ < 2.7 V                 | -   | 20  |      |  |

|                                           |                          |                                                                 | $C_L$ = 30 pF, $V_{DDIOx} \ge 2.7 V$               | -   | 5   |      |  |

| 11                                        | t <sub>f(IO)out</sub>    | Output fall time                                                | $C_L = 50 \text{ pF}, V_{DDIOx} \ge 2.7 \text{ V}$ | -   | 8   |      |  |

|                                           |                          |                                                                 | $C_L$ = 50 pF, $V_{DDIOx}$ < 2.7 V                 | -   | 12  |      |  |

|                                           |                          |                                                                 | $C_L = 30 \text{ pF}, V_{DDIOx} \ge 2.7 \text{ V}$ | -   | 5   | ns   |  |

|                                           | t <sub>r(IO)out</sub>    | Output rise time                                                | $C_L = 50 \text{ pF}, V_{DDIOx} \ge 2.7 \text{ V}$ | -   | 8   |      |  |

|                                           |                          |                                                                 | $C_L$ = 50 pF, $V_{DDIOx}$ < 2.7 V                 | -   | 12  |      |  |

| Fm+                                       | f <sub>max(IO)out</sub>  | Maximum frequency <sup>(3)</sup>                                |                                                    | -   | 2   | MHz  |  |

| configuration                             | t <sub>f(IO)out</sub>    | Output fall time                                                | C <sub>L</sub> = 50 pF                             | -   | 12  |      |  |

| (4)                                       | t <sub>r(IO)out</sub>    | Output rise time                                                |                                                    | -   | 34  | ns   |  |

| -                                         | t <sub>EXTIpw</sub>      | Pulse width of external signals detected by the EXTI controller | -                                                  | 10  | -   | ns   |  |

| Table 48 | . I/O AC | characteristics <sup>(1)(2)</sup> | ļ |

|----------|----------|-----------------------------------|---|

|----------|----------|-----------------------------------|---|

1. The I/O speed is configured using the OSPEEDRx[1:0] bits. Refer to the STM32F0xxxx RM0091 reference manual for a description of GPIO Port configuration register.

2. Guaranteed by design, not tested in production.

3. The maximum frequency is defined in *Figure 22*.

4. When Fm+ configuration is set, the I/O speed control is bypassed. Refer to the STM32F0xxxx reference manual RM0091 for a detailed description of Fm+ I/O configuration.

#### Figure 22. I/O AC characteristics definition

## 6.3.15 NRST pin characteristics

The NRST pin input driver uses the CMOS technology. It is connected to a permanent pull-up resistor,  $\mathsf{R}_{\mathsf{PU}}.$

Unless otherwise specified, the parameters given in the table below are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 18: General operating conditions*.

| Symbol                 | Parameter                                       | Conditions                        | Min                                         | Тур | Мах                                      | Unit |

|------------------------|-------------------------------------------------|-----------------------------------|---------------------------------------------|-----|------------------------------------------|------|

| V <sub>IL(NRST)</sub>  | NRST input low level voltage                    | -                                 | -                                           | -   | 0.3 V <sub>DD</sub> +0.07 <sup>(1)</sup> | v    |

| V <sub>IH(NRST)</sub>  | NRST input high level voltage                   | -                                 | 0.445 V <sub>DD</sub> +0.398 <sup>(1)</sup> | -   | -                                        | v    |

| V <sub>hys(NRST)</sub> | NRST Schmitt trigger voltage<br>hysteresis      | -                                 | -                                           | 200 | -                                        | mV   |

| R <sub>PU</sub>        | Weak pull-up equivalent resistor <sup>(2)</sup> | V <sub>IN</sub> = V <sub>SS</sub> | 25                                          | 40  | 55                                       | kΩ   |

| V <sub>F(NRST)</sub>   | NRST input filtered pulse                       | -                                 | -                                           | -   | 100 <sup>(1)</sup>                       | ns   |

| V                      | NRST input not filtered pulse                   | $2.7 < V_{DD} < 3.6$              | 300 <sup>(3)</sup>                          | -   | -                                        | ns   |

| V <sub>NF(NRST)</sub>  |                                                 | $2.0 < V_{DD} < 3.6$              | 500 <sup>(3)</sup>                          | -   | -                                        | 115  |

Table 49. NRST pin characteristics

1. Data based on design simulation only. Not tested in production.

2. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimal (~10% order).

3. Data based on design simulation only. Not tested in production.

| Symbol          | Parameter                                                        | Min               | Мах                | Unit |

|-----------------|------------------------------------------------------------------|-------------------|--------------------|------|

| t <sub>AF</sub> | Maximum width of spikes that are suppressed by the analog filter | 50 <sup>(2)</sup> | 260 <sup>(3)</sup> | ns   |

| Table 58. I <sup>2</sup> C analog filter characteris | stics <sup>(1)</sup> |  |

|------------------------------------------------------|----------------------|--|

|------------------------------------------------------|----------------------|--|

1. Guaranteed by design, not tested in production.

2. Spikes with widths below  $t_{AF(min)}$  are filtered.

3. Spikes with widths above  $t_{AF(max)}$  are not filtered

.

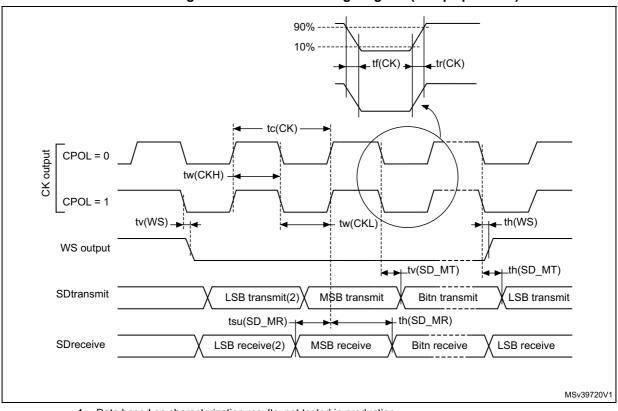

# SPI/I<sup>2</sup>S characteristics

Unless otherwise specified, the parameters given in *Table 59* for SPI or in *Table 60* for  $I^2S$  are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and supply voltage conditions summarized in *Table 18: General operating conditions*.

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI and WS, CK, SD for I<sup>2</sup>S).

| Symbol                                       | Parameter                           | Conditions                                            | Min         | Max         | Unit   |

|----------------------------------------------|-------------------------------------|-------------------------------------------------------|-------------|-------------|--------|

| f <sub>SCK</sub>                             | SPI clock frequency                 | SBI cleak frequency                                   |             | 18          | MHz    |

| 1/t <sub>c(SCK)</sub>                        | SPI Clock frequency                 | Slave mode                                            | -           | 18          | IVITIZ |

| t <sub>r(SCK)</sub><br>t <sub>f(SCK)</sub>   | SPI clock rise and fall time        | Capacitive load: C = 15 pF                            | -           | 6           | ns     |

| t <sub>su(NSS)</sub>                         | NSS setup time                      | Slave mode                                            | 4Tpclk      | -           |        |

| t <sub>h(NSS)</sub>                          | NSS hold time                       | Slave mode                                            | 2Tpclk + 10 | -           |        |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time               | Master mode, f <sub>PCLK</sub> = 36 MHz,<br>presc = 4 | Tpclk/2 -2  | Tpclk/2 + 1 |        |

| t <sub>su(MI)</sub>                          | Data input setup time               | Master mode                                           | 4           | -           |        |

| t <sub>su(SI)</sub>                          | Data input setup time               | Slave mode                                            | 5           | -           |        |

| t <sub>h(MI)</sub>                           | Data input hold time                | Master mode                                           | 4           | -           |        |

| t <sub>h(SI)</sub>                           | Data input hold time                | Slave mode                                            | 5           | -           | ns     |

| t <sub>a(SO)</sub> <sup>(2)</sup>            | Data output access time             | Slave mode, f <sub>PCLK</sub> = 20 MHz                | 0           | 3Tpclk      |        |

| t <sub>dis(SO)</sub> <sup>(3)</sup>          | Data output disable time            | Slave mode                                            | 0           | 18          |        |

| t <sub>v(SO)</sub>                           | Data output valid time              | Slave mode (after enable edge)                        | -           | 22.5        |        |

| t <sub>v(MO)</sub>                           | Data output valid time              | Master mode (after enable edge)                       | -           | 6           |        |

| t <sub>h(SO)</sub>                           | Data output hold time               | Slave mode (after enable edge)                        | 11.5        | -           |        |

| t <sub>h(MO)</sub>                           |                                     | Master mode (after enable edge)                       | 2           | -           |        |

| DuCy(SCK)                                    | SPI slave input clock<br>duty cycle | Slave mode                                            | 25          | 75          | %      |

| Table 5 | 59. SPI | characteristics( | 1) |

|---------|---------|------------------|----|

|---------|---------|------------------|----|

1. Data based on characterization results, not tested in production.

2. Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

3. Min time is for the minimum time to invalidate the output and the max time is for the maximum time to put the data in Hi-Z

## Figure 30. I<sup>2</sup>S master timing diagram (Philips protocol)

- 1. Data based on characterization results, not tested in production.

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

|        | millimeters |       |       | meenamea | inches <sup>(1)</sup> |        |

|--------|-------------|-------|-------|----------|-----------------------|--------|

| Symbol | Min         | Тур   | Мах   | Min      | Тур                   | Мах    |

| А      | 0.500       | 0.550 | 0.600 | 0.0197   | 0.0217                | 0.0236 |

| A1     | 0.000       | 0.020 | 0.050 | 0.0000   | 0.0008                | 0.0020 |

| A3     | -           | 0.152 | -     | -        | 0.0060                | -      |

| b      | 0.180       | 0.230 | 0.280 | 0.0071   | 0.0091                | 0.0110 |

| D      | 4.900       | 5.000 | 5.100 | 0.1929   | 0.1969                | 0.2008 |

| D1     | 3.400       | 3.500 | 3.600 | 0.1339   | 0.1378                | 0.1417 |

| D2     | 3.400       | 3.500 | 3.600 | 0.1339   | 0.1378                | 0.1417 |

| E      | 4.900       | 5.000 | 5.100 | 0.1929   | 0.1969                | 0.2008 |

| E1     | 3.400       | 3.500 | 3.600 | 0.1339   | 0.1378                | 0.1417 |

| E2     | 3.400       | 3.500 | 3.600 | 0.1339   | 0.1378                | 0.1417 |

| е      | -           | 0.500 | -     | -        | 0.0197                | -      |

| L      | 0.300       | 0.400 | 0.500 | 0.0118   | 0.0157                | 0.0197 |

| ddd    | -           | -     | 0.080 | -        | -                     | 0.0031 |

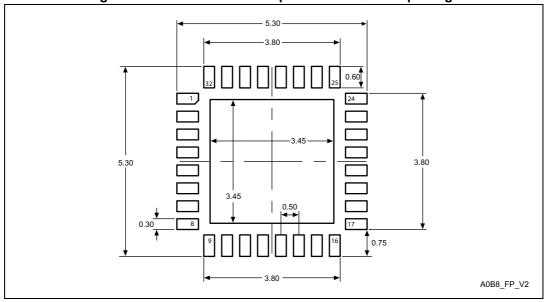

Table 63. UFQFPN32 package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

#### Figure 38. Recommended footprint for UFQFPN32 package

1. Dimensions are expressed in millimeters.

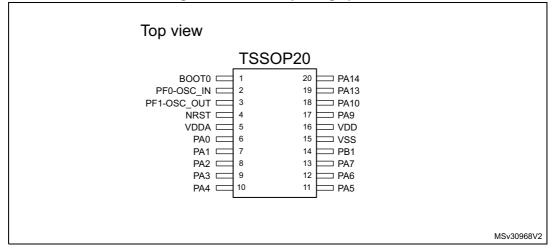

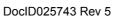

# 7.6 TSSOP20 package information

TSSOP20 is a 20-lead thin shrink small-outline, 6.5 x 4.4 mm, 0.65 mm pitch, package.

1. Drawing is not to scale.

| Symbol            |       | millimeters |       |        | inches <sup>(1)</sup> |        |  |

|-------------------|-------|-------------|-------|--------|-----------------------|--------|--|

| Symbol            | Min.  | Тур.        | Max.  | Min.   | Тур.                  | Max.   |  |

| А                 | -     | -           | 1.200 | -      | -                     | 0.0472 |  |

| A1                | 0.050 | -           | 0.150 | 0.0020 | -                     | 0.0059 |  |

| A2                | 0.800 | 1.000       | 1.050 | 0.0315 | 0.0394                | 0.0413 |  |

| b                 | 0.190 | -           | 0.300 | 0.0075 | -                     | 0.0118 |  |

| с                 | 0.090 | -           | 0.200 | 0.0035 | -                     | 0.0079 |  |

| D <sup>(2)</sup>  | 6.400 | 6.500       | 6.600 | 0.2520 | 0.2559                | 0.2598 |  |

| E                 | 6.200 | 6.400       | 6.600 | 0.2441 | 0.2520                | 0.2598 |  |

| E1 <sup>(3)</sup> | 4.300 | 4.400       | 4.500 | 0.1693 | 0.1732                | 0.1772 |  |

| е                 | -     | 0.650       | -     | -      | 0.0256                | -      |  |

| L                 | 0.450 | 0.600       | 0.750 | 0.0177 | 0.0236                | 0.0295 |  |

| L1                | -     | 1.000       | -     | -      | 0.0394                | -      |  |

## 7.7 Thermal characteristics

The maximum chip junction temperature (T<sub>J</sub>max) must never exceed the values given in *Table 18: General operating conditions*.

The maximum chip-junction temperature,  $\mathsf{T}_{\mathsf{J}}$  max, in degrees Celsius, may be calculated using the following equation:

$$T_J max = T_A max + (P_D max x \Theta_{JA})$$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in °C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

$P_{I/O}$  max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I/O}}\max=\Sigma\;(\mathsf{V}_{\mathsf{OL}}\times\mathsf{I}_{\mathsf{OL}})+\Sigma\;((\mathsf{V}_{\mathsf{DDIOx}}-\mathsf{V}_{\mathsf{OH}})\times\mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V<sub>OL</sub> / I<sub>OL</sub> and V<sub>OH</sub> / I<sub>OH</sub> of the I/Os at low and high level in the application.

| Symbol        | Parameter                                                       | Value | Unit |

|---------------|-----------------------------------------------------------------|-------|------|

|               | Thermal resistance junction-ambient<br>LQFP48 - 7 × 7 mm        | 55    |      |

|               | Thermal resistance junction-ambient<br>UFQFPN32 - 5 × 5 mm      | 38    |      |

| 0             | Thermal resistance junction-ambient<br>LQFP32 - 7 × 7 mm        | 56    | °C/W |

| $\Theta_{JA}$ | Thermal resistance junction-ambient<br>UFQFPN28 - 4 × 4 mm      | 118   | 0/00 |

|               | Thermal resistance junction-ambient<br>WLCSP25 - 2.13 x 2.07 mm | 74    |      |

|               | Thermal resistance junction-ambient<br>TSSOP20 - 6.5 x 4.4 mm   | 110   |      |

Table 68. Package thermal characteristics

### 7.7.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org

| Date        | Revision         | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28-Aug-2015 | 3<br>(continued) | <ul> <li>Added WLCSP25 package, updates in the following:</li> <li>Table 1: Device summary,</li> <li>Section 2: Description,</li> <li>Table 2: STM32F031x4/x6 family device features and peripheral counts,</li> <li>Section 4: Pinouts and pin description: addition of Figure 7: WLCSP25 25-ball package ballout (bump side) and update of Table 11: Pin definitions,</li> <li>Table 18: General operating conditions,</li> <li>Section 7: Package information with the addition of Section 7.5: WLCSP25 package information,</li> <li>Table 68: Package thermal characteristics.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 16-Dec-2015 | 4                | Cover page:<br>- number of timers added in the title<br>- Table 1: Device summary - STM32F031x4 added<br>Section 2: Description:<br>- Figure 1: Block diagram updated<br>Section 3: Functional overview:<br>- Figure 2: Clock tree updated<br>- Section 3.5.4: Low-power modes - added explicit inf.<br>on peripherals configurable to operate with HSI<br>- Section 3.10.2: Internal voltage reference (V <sub>REFINT</sub> ) -<br>removed information on comparators<br>- Section 3.10.2: Internal voltage reference (V <sub>REFINT</sub> ) -<br>removed information on comparators<br>- Section 3.11.2: General-purpose timers (TIM2, 3, 14,<br>16, 17) - number of gen-purpose timers corrected<br>- Section Table 7.: STM32F031x4/x6 I <sup>2</sup> C<br>implementation - added 20mA output drive current<br>Section 4: Pinouts and pin description:<br>- Package pinout figures updated (look and feel)<br>- Figure 7: WLCSP25 package pinout - now presented<br>in top view<br>- Table 11: Pin definitions - notes 3 and 6 added<br>Section 5: Memory mapping:<br>- added information on memory mapping difference of<br>STM32F031x4 from STM32F031x6<br>Section 6: Electrical characteristics:<br>- Table 22: Embedded internal reference voltage:<br>removed -40°-to-85° condition and associated note for<br>V <sub>REFINT</sub><br>- Table 25 and Table 26 values rounded to 1 decimal<br>- Table 46: I/O static characteristics - updated some<br>parameter values, test conditions and added<br>footnotes <sup>(3)</sup> and <sup>(4)</sup> |