Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

|                            | Antico                                                                |

| Product Status             | Active                                                                |

| Core Processor             | ARM® Cortex®-M0                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                       |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 4K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 13x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-LQFP                                                               |

| Supplier Device Package    | 32-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f031k6t7 |

# List of tables

| Table 1.  | Device summary                                                           | 1  |

|-----------|--------------------------------------------------------------------------|----|

| Table 2.  | STM32F031x4/x6 family device features and peripheral counts              |    |

| Table 3.  | Temperature sensor calibration values                                    | 16 |

| Table 4.  | Internal voltage reference calibration values                            | 16 |

| Table 5.  | Timer feature comparison                                                 | 17 |

| Table 6.  | Comparison of I <sup>2</sup> C analog and digital filters                | 20 |

| Table 7.  | STM32F031x4/x6 I <sup>2</sup> C implementation                           | 20 |

| Table 8.  | STM32F031x4/x6 USART implementation                                      |    |

| Table 9.  | STM32F031x4/x6 SPI/I2S implementation                                    | 21 |

| Table 10. | Legend/abbreviations used in the pinout table                            |    |

| Table 11. | Pin definitions                                                          |    |

| Table 12. | Alternate functions selected through GPIOA AFR registers for port A      | 31 |

| Table 13. | Alternate functions selected through GPIOB_AFR registers for port B      | 32 |

| Table 14. | STM32F031x4/x6 peripheral register boundary addresses                    |    |

| Table 15. | Voltage characteristics                                                  |    |

| Table 16. | Current characteristics                                                  |    |

| Table 17. | Thermal characteristics                                                  | 40 |

| Table 18. | General operating conditions                                             |    |

| Table 19. | Operating conditions at power-up / power-down                            | 42 |

| Table 20. | Embedded reset and power control block characteristics                   | 42 |

| Table 21. | Programmable voltage detector characteristics                            |    |

| Table 22. | Embedded internal reference voltage                                      |    |

| Table 23. | Typical and maximum current consumption from V <sub>DD</sub> at 3.6 V    |    |

| Table 24. | Typical and maximum current consumption from the V <sub>DDA</sub> supply |    |

| Table 25. | Typical and maximum current consumption in Stop and Standby modes        |    |

| Table 26. | Typical and maximum current consumption from the V <sub>BAT</sub> supply | 47 |

| Table 27. | Typical current consumption, code executing from Flash memory,           |    |

|           | running from HSE 8 MHz crystal                                           | 48 |

| Table 28. | Switching output I/O current consumption                                 |    |

| Table 29. | Peripheral current consumption                                           | 51 |

| Table 30. | Low-power mode wakeup timings                                            | 53 |

| Table 31. | High-speed external user clock characteristics                           | 53 |

| Table 32. | Low-speed external user clock characteristics                            | 54 |

| Table 33. | HSE oscillator characteristics                                           | 55 |

| Table 34. | LSE oscillator characteristics (f <sub>LSE</sub> = 32.768 kHz)           | 56 |

| Table 35. | HSI oscillator characteristics                                           | 58 |

| Table 36. | HSI14 oscillator characteristics                                         | 59 |

| Table 37. | LSI oscillator characteristics                                           | 60 |

| Table 38. | PLL characteristics                                                      | 60 |

| Table 39. | Flash memory characteristics                                             | 60 |

| Table 40. | Flash memory endurance and data retention                                | 61 |

| Table 41. | EMS characteristics                                                      | 61 |

| Table 42. | EMI characteristics                                                      | 62 |

| Table 43. | ESD absolute maximum ratings                                             |    |

| Table 44. | Electrical sensitivities                                                 |    |

| Table 45. | I/O current injection susceptibility                                     | 64 |

| Table 46. | I/O static characteristics                                               | 64 |

| Table 47. | Output voltage characteristics                                           |    |

In Standby mode, it is put in power down mode. In this mode, the regulator output is in high impedance and the kernel circuitry is powered down, inducing zero consumption (but the contents of the registers and SRAM are lost).

## 3.5.4 Low-power modes

The STM32F031x4/x6 microcontrollers support three low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

### Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

## • Stop mode

Stop mode achieves very low power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low power mode.

The device can be woken up from Stop mode by any of the EXTI lines. The EXTI line source can be one of the 16 external lines, the PVD output, RTC, I2C1 or USART1. USART1 and I2C1 peripherals can be configured to enable the HSI RC oscillator so as to get clock for processing incoming data. If this is used when the voltage regulator is put in low power mode, the regulator is first switched to normal mode before the clock is provided to the given peripheral.

## Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.8 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, SRAM and register contents are lost except for registers in the RTC domain and Standby circuitry.

The device exits Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pins, or an RTC event occurs.

Note: The RTC, the IWDG, and the corresponding clock sources are not stopped by entering Stop or Standby mode.

## 3.6 Clocks and startup

System clock selection is performed on startup, however the internal RC 8 MHz oscillator is selected as default CPU clock on reset. An external 4-32 MHz clock can be selected, in which case it is monitored for failure. If failure is detected, the system automatically switches back to the internal RC oscillator. A software interrupt is generated if enabled. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example on failure of an indirectly used external crystal, resonator or oscillator).

Several prescalers allow the application to configure the frequency of the AHB and the APB domains. The maximum frequency of the AHB and the APB domains is 48 MHz.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

## 3.10.1 Temperature sensor

The temperature sensor (TS) generates a voltage  $V_{\mbox{\footnotesize SENSE}}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode.

| Calibration value name | Description                                                                                      | Memory address            |

|------------------------|--------------------------------------------------------------------------------------------------|---------------------------|

| TS_CAL1                | TS ADC raw data acquired at a temperature of 30 °C (± 5 °C), V <sub>DDA</sub> = 3.3 V (± 10 mV)  | 0x1FFF F7B8 - 0x1FFF F7B9 |

| TS_CAL2                | TS ADC raw data acquired at a temperature of 110 °C (± 5 °C), V <sub>DDA</sub> = 3.3 V (± 10 mV) | 0x1FFF F7C2 - 0x1FFF F7C3 |

Table 3. Temperature sensor calibration values

# 3.10.2 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. The precise voltage of  $V_{REFINT}$  is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode.

| Calibration value name | Description                                                                              | Memory address            |  |  |  |  |  |  |  |

|------------------------|------------------------------------------------------------------------------------------|---------------------------|--|--|--|--|--|--|--|

| VREFINT_CAL            | Raw data acquired at a temperature of 30 °C (± 5 °C), V <sub>DDA</sub> = 3.3 V (± 10 mV) | 0x1FFF F7BA - 0x1FFF F7BB |  |  |  |  |  |  |  |

Table 4. Internal voltage reference calibration values

## 3.10.3 V<sub>BAT</sub> battery voltage monitoring

This embedded hardware feature allows the application to measure the  $V_{BAT}$  battery voltage using the internal ADC channel ADC\_IN18. As the  $V_{BAT}$  voltage may be higher than  $V_{DDA}$ , and thus outside the ADC input range, the  $V_{BAT}$  pin is internally connected to a bridge divider by 2. As a consequence, the converted digital value is half the  $V_{BAT}$  voltage.

Table 11. Pin definitions (continued)

|        | i      | Pin nı   | umbe     | r       |         |                                      |          |               |       | Pin fund                                                        | etions                  |

|--------|--------|----------|----------|---------|---------|--------------------------------------|----------|---------------|-------|-----------------------------------------------------------------|-------------------------|

| LQFP48 | LQFP32 | UFQFPN32 | UFQFPN28 | WLCSP25 | TSSOP20 | Pin name<br>(function upon<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                             | Additional<br>functions |

| 30     | 19     | 19       | 19       | C1      | 17      | PA9                                  | I/O      | FTf           | -     | USART1_TX,<br>TIM1_CH2,<br>I2C1_SCL                             | -                       |

| 31     | 20     | 20       | 20       | B1      | 18      | PA10                                 | I/O      | FTf           | -     | USART1_RX,<br>TIM1_CH3,<br>TIM17_BKIN,<br>I2C1_SDA              | -                       |

| 32     | 21     | 21       | -        | -       | -       | PA11                                 | I/O      | FT            | -     | USART1_CTS,<br>TIM1_CH4,<br>EVENTOUT                            | -                       |

| 33     | 22     | 22       | -        | -       | -       | PA12                                 | I/O      | FT            | -     | USART1_RTS,<br>TIM1_ETR,<br>EVENTOUT                            | -                       |

| 34     | 23     | 23       | 21       | A1      | 19      | PA13<br>(SWDIO)                      | I/O      | FT            | (5)   | IR_OUT,<br>SWDIO                                                | -                       |

| 35     | -      | -        | -        | -       | -       | PF6                                  | I/O      | FTf           | -     | I2C1_SCL                                                        | -                       |

| 36     | -      | -        | -        | -       | -       | PF7                                  | I/O      | FTf           | -     | I2C1_SDA                                                        | -                       |

| 37     | 24     | 24       | 22       | A2      | 20      | PA14<br>(SWCLK)                      | I/O      | FT            | (5)   | USART1_TX,<br>SWCLK                                             | -                       |

| 38     | 25     | 25       | 23       | -       | -       | PA15                                 | I/O      | FT            | (6)   | SPI1_NSS,<br>I2S1_WS,<br>TIM2_CH_ETR,<br>EVENTOUT,<br>USART1_RX | -                       |

| 39     | 26     | 26       | 24       | -       | -       | PB3                                  | I/O      | FT            | (6)   | SPI1_SCK,<br>I2S1_CK,<br>TIM2_CH2,<br>EVENTOUT                  | -                       |

| 40     | 27     | 27       | 25       | 1       | -       | PB4                                  | I/O      | FT            | (6)   | SPI1_MISO,<br>I2S1_MCK,<br>TIM3_CH1,<br>EVENTOUT                | -                       |

Table 14. STM32F031x4/x6 peripheral register boundary addresses

| Bus   | Boundary address          | Size    | Peripheral                                                                                      |

|-------|---------------------------|---------|-------------------------------------------------------------------------------------------------|

|       | 0x4800 1800 - 0x5FFF FFFF | ~384 MB | Reserved                                                                                        |

|       | 0x4800 1400 - 0x4800 17FF | 1KB     | GPIOF                                                                                           |

|       | 0x4800 0C00 - 0x4800 13FF | 2KB     | Reserved                                                                                        |

| AHB2  | 0x4800 0800 - 0x4800 0BFF | 1KB     | GPIOC                                                                                           |

|       | 0x4800 0400 - 0x4800 07FF | 1KB     | GPIOB                                                                                           |

|       | 0x4800 0000 - 0x4800 03FF | 1KB     | GPIOA                                                                                           |

|       | 0x4002 4400 - 0x47FF FFFF | ~128 MB | Reserved                                                                                        |

|       | 0x4002 3400 - 0x4002 3FFF | 3 KB    | Reserved                                                                                        |

|       | 0x4002 3000 - 0x4002 33FF | 1 KB    | CRC                                                                                             |

|       | 0x4002 2400 - 0x4002 2FFF | 3 KB    | Reserved                                                                                        |

| ALID4 | 0x4002 2000 - 0x4002 23FF | 1 KB    | Flash memory interface                                                                          |

| AHB1  | 0x4002 1400 - 0x4002 1FFF | 3 KB    | Reserved                                                                                        |

|       | 0x4002 1000 - 0x4002 13FF | 1 KB    | RCC                                                                                             |

|       | 0x4002 0400 - 0x4002 0FFF | 3 KB    | Reserved GPIOF Reserved GPIOC GPIOB GPIOA Reserved CRC Reserved Flash memory interface Reserved |

|       | 0x4002 0000 - 0x4002 03FF | 1 KB    | DMA                                                                                             |

|       | 0x4001 8000 - 0x4001 FFFF | 32 KB   | Reserved                                                                                        |

|       | 0x4001 5C00 - 0x4001 7FFF | 9KB     | Reserved                                                                                        |

|       | 0x4001 5800 - 0x4001 5BFF | 1KB     | DBGMCU                                                                                          |

|       | 0x4001 4C00 - 0x4001 57FF | 3KB     | Reserved                                                                                        |

|       | 0x4001 4800 - 0x4001 4BFF | 1KB     | TIM17                                                                                           |

|       | 0x4001 4400 - 0x4001 47FF | 1KB     | TIM16                                                                                           |

|       | 0x4001 3C00 - 0x4001 43FF | 2KB     | Reserved                                                                                        |

|       | 0x4001 3800 - 0x4001 3BFF | 1KB     | USART1                                                                                          |

| APB   | 0x4001 3400 - 0x4001 37FF | 1KB     | Reserved                                                                                        |

|       | 0x4001 3000 - 0x4001 33FF | 1KB     | SPI1/I2S1                                                                                       |

|       | 0x4001 2C00 - 0x4001 2FFF | 1KB     | TIM1                                                                                            |

|       | 0x4001 2800 - 0x4001 2BFF | 1KB     | Reserved                                                                                        |

|       | 0x4001 2400 - 0x4001 27FF | 1KB     | ADC                                                                                             |

|       | 0x4001 0800 - 0x4001 23FF | 7KB     | Reserved                                                                                        |

|       | 0x4001 0400 - 0x4001 07FF | 1KB     | EXTI                                                                                            |

|       | 0x4001 0000 - 0x4001 03FF | 1KB     | SYSCFG                                                                                          |

|       | 0x4000 8000 - 0x4000 FFFF | 32 KB   | Reserved                                                                                        |

# 6.1.7 Current consumption measurement

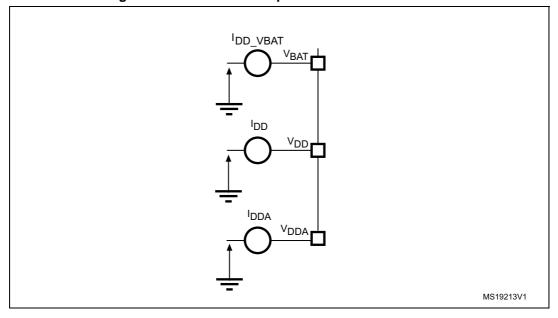

Figure 13. Current consumption measurement scheme

Table 23. Typical and maximum current consumption from  $V_{DD}$  at 3.6 V (continued)

|                 |                   |                       |                   | All peripherals enabled |                     |          |                     |     | All peripherals disabled            |       |                    |      |

|-----------------|-------------------|-----------------------|-------------------|-------------------------|---------------------|----------|---------------------|-----|-------------------------------------|-------|--------------------|------|

| Symbol          | Parameter         | Conditions            | f <sub>HCLK</sub> | Tun                     | N                   | lax @ T, | A <sup>(1)</sup>    | Tvn | Max @ T <sub>A</sub> <sup>(1)</sup> |       |                    | Unit |

|                 |                   |                       |                   | Тур                     | 25 °C               | 85 °C    | 105 °C              | Тур | 25 °C                               | 85 °C | 105 °C             |      |

|                 |                   | HSE                   | 48 MHz            | 10.7                    | 11.7 <sup>(2)</sup> | 11.9     | 12.5 <sup>(2)</sup> | 2.4 | 2.6 <sup>(2)</sup>                  | 2.7   | 2.9 <sup>(2)</sup> |      |

|                 | Supply current in | bypass,               | 32 MHz            | 7.1                     | 7.8                 | 8.1      | 8.2                 | 1.6 | 1.7                                 | 1.9   | 1.9                |      |

|                 |                   | PLL on                | 24 MHz            | 5.5                     | 6.3                 | 6.4      | 6.4                 | 1.3 | 1.4                                 | 1.5   | 1.5                |      |

|                 |                   | t in PLL off          | 8 MHz             | 1.8                     | 2.0                 | 2.0      | 2.1                 | 0.4 | 0.4                                 | 0.5   | 0.5                |      |

| I <sub>DD</sub> |                   |                       | 1 MHz             | 0.2                     | 0.5                 | 0.5      | 0.5                 | 0.1 | 0.1                                 | 0.1   | 0.1                | mA   |

|                 | Sleep<br>mode     |                       | 48 MHz            | 10.8                    | 11.9                | 12.1     | 12.6                | 2.4 | 2.7                                 | 2.7   | 2.9                |      |

|                 |                   | HSI clock,<br>PLL on  | 32 MHz            | 7.3                     | 8.0                 | 8.4      | 8.5                 | 1.7 | 1.9                                 | 1.9   | 2.0                |      |

|                 |                   | 0                     | 24 MHz            | 5.5                     | 6.2                 | 6.5      | 6.5                 | 1.3 | 1.5                                 | 1.5   | 1.6                |      |

|                 |                   | HSI clock,<br>PLL off | 8 MHz             | 1.9                     | 2.2                 | 2.3      | 2.4                 | 0.5 | 0.5                                 | 0.5   | 0.6                |      |

<sup>1.</sup> Data based on characterization results, not tested in production unless otherwise specified.

Table 24. Typical and maximum current consumption from the  $V_{\text{DDA}}$  supply

|                  |                                         |                       |                       |     | $V_{DDA}$          | = 2.4 V             |                    |      | $V_{DDA}$                           | = 3.6 V | 1                  |      |

|------------------|-----------------------------------------|-----------------------|-----------------------|-----|--------------------|---------------------|--------------------|------|-------------------------------------|---------|--------------------|------|

| Symbol           | Parameter                               | Conditions (1)        | ons f <sub>HCLK</sub> | Tun | М                  | ах @ Т <sub>А</sub> | (2)                | Tun  | Max @ T <sub>A</sub> <sup>(2)</sup> |         |                    | Unit |

|                  |                                         |                       |                       | Тур | 25 °C              | 85 °C               | 105 °C             | Тур  | 25 °C                               | 85 °C   | 105 °C             |      |

|                  |                                         | HSE                   | 48 MHz                | 150 | 170 <sup>(3)</sup> | 178                 | 182 <sup>(3)</sup> | 164  | 183 <sup>(3)</sup>                  | 195     | 198 <sup>(3)</sup> |      |

|                  | Cummbu                                  | bypass,               | 32 MHz                | 104 | 121                | 126                 | 128                | 113  | 129                                 | 135     | 138                |      |

|                  | Supply<br>current in<br>Run or<br>Sleep | PLL on                | 24 MHz                | 82  | 96                 | 100                 | 103                | 88   | 102                                 | 106     | 108                |      |

|                  |                                         | HSE                   | 8 MHz                 | 2.0 | 2.7                | 3.1                 | 3.3                | 3.5  | 3.8                                 | 4.1     | 4.4                |      |

| I <sub>DDA</sub> | mode,                                   | mode, PLL off         | 1 MHz                 | 2.0 | 2.7                | 3.1                 | 3.3                | 3.5  | 3.8                                 | 4.1     | 4.4                | μΑ   |

|                  | executing                               |                       | 48 MHz                | 220 | 240                | 248                 | 252                | 244  | 263                                 | 275     | 278                |      |

|                  | from Flash<br>memory or                 | HSI clock,<br>PLL on  | 32 MHz                | 174 | 191                | 196                 | 198                | 193  | 209                                 | 215     | 218                |      |

|                  | RAM                                     |                       | 24 MHz                | 152 | 167                | 173                 | 174                | 168  | 183                                 | 190     | 192                |      |

|                  |                                         | HSI clock,<br>PLL off | 8 MHz                 | 72  | 79                 | 82                  | 83                 | 83.5 | 91                                  | 94      | 95                 |      |

Current consumption from the V<sub>DDA</sub> supply is independent of whether the digital peripherals are enabled or disabled, being in Run or Sleep mode or executing from Flash memory or RAM. Furthermore, when the PLL is off, I<sub>DDA</sub> is independent of clock frequencies.

<sup>2.</sup> Data based on characterization results and tested in production (using one common test limit for sum of I<sub>DD</sub> and I<sub>DDA</sub>).

<sup>2.</sup> Data based on characterization results, not tested in production unless otherwise specified.

<sup>3.</sup> Data based on characterization results and tested in production (using one common test limit for sum of  $I_{DD}$  and  $I_{DDA}$ ).

Max<sup>(1)</sup> Typ @ V<sub>BAT</sub> **Symbol Conditions** Unit **Parameter** 1.8 V 3.3 V T<sub>A</sub> = 85 °C T<sub>A</sub> = 105 °C 1.65  $T_A =$ 3.6 25°C LSE & RTC ON; "Xtal mode": lower driving 0.5 0.5 0.6 0.7 8.0 0.9 1.0 1.3 1.7 capability; RTC LSEDRV[1:0] = '00' domain μΑ I<sub>DD\_VBAT</sub> supply LSE & RTC ON; "Xtal current mode" higher driving 8.0 8.0 0.9 1.0 1.1 1.2 1.3 1.6 2.1 capability; LSEDRV[1:0] = '11'

Table 26. Typical and maximum current consumption from the V<sub>BAT</sub> supply

## **Typical current consumption**

The MCU is placed under the following conditions:

- V<sub>DD</sub> = V<sub>DDA</sub> = 3.3 V

- All I/O pins are in analog input configuration

- The Flash memory access time is adjusted to f<sub>HCLK</sub> frequency:

- 0 wait state and Prefetch OFF from 0 to 24 MHz

- 1 wait state and Prefetch ON above 24 MHz

- When the peripherals are enabled, f<sub>PCLK</sub> = f<sub>HCLK</sub>

- PLL is used for frequencies greater than 8 MHz

- AHB prescaler of 2, 4, 8 and 16 is used for the frequencies 4 MHz, 2 MHz, 1 MHz and 500 kHz respectively

<sup>1.</sup> Data based on characterization results, not tested in production.

trigger circuits used to discriminate the input value. Unless this specific configuration is required by the application, this supply current consumption can be avoided by configuring these I/Os in analog mode. This is notably the case of ADC input pins which should be configured as analog inputs.

Caution:

Any floating input pin can also settle to an intermediate voltage level or switch inadvertently, as a result of external electromagnetic noise. To avoid current consumption related to floating pins, they must either be configured in analog mode, or forced internally to a definite digital value. This can be done either by using pull-up/down resistors or by configuring the pins in output mode.

### I/O dynamic current consumption

In addition to the internal peripheral current consumption measured previously (see *Table 29: Peripheral current consumption*), the I/Os used by an application also contribute to the current consumption. When an I/O pin switches, it uses the current from the I/O supply voltage to supply the I/O pin circuitry and to charge/discharge the capacitive load (internal or external) connected to the pin:

$$I_{SW} = V_{DDIOx} \times f_{SW} \times C$$

where

$I_{\mbox{\scriptsize SW}}$  is the current sunk by a switching I/O to charge/discharge the capacitive load

V<sub>DDIOx</sub> is the I/O supply voltage

f<sub>SW</sub> is the I/O switching frequency

C is the total capacitance seen by the I/O pin:  $C = C_{INT} + C_{EXT} + C_{S}$

C<sub>S</sub> is the PCB board capacitance including the pad pin.

The test pin is configured in push-pull output mode and is toggled by software at a fixed frequency.

## Low-speed internal (LSI) RC oscillator

Table 37. LSI oscillator characteristics<sup>(1)</sup>

| Symbol                               | Parameter                        | Min | Тур  | Max | Unit |

|--------------------------------------|----------------------------------|-----|------|-----|------|

| f <sub>LSI</sub>                     | Frequency                        | 30  | 40   | 50  | kHz  |

| t <sub>su(LSI)</sub> <sup>(2)</sup>  | LSI oscillator startup time      | -   | -    | 85  | μs   |

| I <sub>DDA(LSI)</sub> <sup>(2)</sup> | LSI oscillator power consumption | -   | 0.75 | 1.2 | μΑ   |

<sup>1.</sup>  $V_{DDA}$  = 3.3 V,  $T_A$  = -40 to 105 °C unless otherwise specified.

## 6.3.9 PLL characteristics

The parameters given in *Table 38* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 18: General operating conditions*.

Table 38. PLL characteristics

| Symbol                | Parameter                      |                   | Unit |                    |       |

|-----------------------|--------------------------------|-------------------|------|--------------------|-------|

| Symbol                | Farameter                      | Min               | Тур  | Max                | Offic |

| £                     | PLL input clock <sup>(1)</sup> | 1 <sup>(2)</sup>  | 8.0  | 24 <sup>(2)</sup>  | MHz   |

| f <sub>PLL_IN</sub>   | PLL input clock duty cycle     | 40 <sup>(2)</sup> | -    | 60 <sup>(2)</sup>  | %     |

| f <sub>PLL_OUT</sub>  | PLL multiplier output clock    | 16 <sup>(2)</sup> | -    | 48                 | MHz   |

| t <sub>LOCK</sub>     | PLL lock time                  | -                 | -    | 200 <sup>(2)</sup> | μs    |

| Jitter <sub>PLL</sub> | Cycle-to-cycle jitter          | -                 | -    | 300 <sup>(2)</sup> | ps    |

Take care to use the appropriate multiplier factors to obtain PLL input clock values compatible with the range defined by f<sub>PLL OUT</sub>.

## 6.3.10 Memory characteristics

## Flash memory

The characteristics are given at  $T_A$  = -40 to 105 °C unless otherwise specified.

Table 39. Flash memory characteristics

| Symbol             | Parameter               | Parameter Conditions             |    | Тур  | Max <sup>(1)</sup> | Unit |

|--------------------|-------------------------|----------------------------------|----|------|--------------------|------|

| t <sub>prog</sub>  | 16-bit programming time | T <sub>A</sub> = - 40 to +105 °C | 40 | 53.5 | 60                 | μs   |

| t <sub>ERASE</sub> | Page (1 KB) erase time  | T <sub>A</sub> = - 40 to +105 °C | 20 | -    | 40                 | ms   |

| t <sub>ME</sub>    | Mass erase time         | T <sub>A</sub> = - 40 to +105 °C | 20 | -    | 40                 | ms   |

|                    | 0                       | Write mode                       | -  | -    | 10                 | mA   |

| IDD                | Supply current          | Erase mode                       | -  | -    | 12                 | mA   |

<sup>1.</sup> Guaranteed by design, not tested in production.

<sup>2.</sup> Guaranteed by design, not tested in production.

<sup>2.</sup> Guaranteed by design, not tested in production.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (for example control registers)

#### **Prequalification trials**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

Max vs. [fHSE/fHCLK] **Monitored** Conditions Unit Symbol Parameter frequency band 8/48 MHz 0.1 to 30 MHz -11  $V_{DD} = 3.6 \text{ V}, T_A = 25 ^{\circ}\text{C},$ 30 to 130 MHz 21 dBuV LQFP48 package Peak level  $S_{EMI}$ compliant with 130 MHz to 1 GHz 21 IEC 61967-2 **EMI Level** 4

Table 42. EMI characteristics

## 6.3.12 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

## Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts × (n+1) supply pins). This test conforms to the JESD22-A114/C101 standard.

## Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 22* and *Table 48*, respectively. Unless otherwise specified, the parameters given are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 18: General operating conditions*.

Table 48. I/O AC characteristics<sup>(1)(2)</sup>

| OSPEEDRy<br>[1:0]<br>value <sup>(1)</sup> | Symbol                  | Parameter                                                       | Conditions                                         | Min | Max | Unit |  |

|-------------------------------------------|-------------------------|-----------------------------------------------------------------|----------------------------------------------------|-----|-----|------|--|

|                                           | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup>                                |                                                    | İ   | 2   | MHz  |  |

| x0                                        | $t_{f(IO)out}$          | Output fall time                                                | C <sub>L</sub> = 50 pF                             | ı   | 125 | ns   |  |

|                                           | t <sub>r(IO)out</sub>   | Output rise time                                                |                                                    | -   | 125 | 113  |  |

|                                           | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup>                                |                                                    | -   | 10  | MHz  |  |

| 01                                        | t <sub>f(IO)out</sub>   | Output fall time                                                | C <sub>L</sub> = 50 pF                             | -   | 25  | ns   |  |

|                                           | t <sub>r(IO)out</sub>   | Output rise time                                                |                                                    | -   | 25  | 115  |  |

|                                           |                         |                                                                 | C <sub>L</sub> = 30 pF, V <sub>DDIOx</sub> ≥ 2.7 V | -   | 50  |      |  |

|                                           | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup>                                | C <sub>L</sub> = 50 pF, V <sub>DDIOx</sub> ≥ 2.7 V | -   | 30  | MHz  |  |

|                                           |                         |                                                                 | C <sub>L</sub> = 50 pF, V <sub>DDIOx</sub> < 2.7 V | -   | 20  |      |  |

|                                           |                         |                                                                 | $C_L = 30 \text{ pF}, V_{DDIOX} \ge 2.7 \text{ V}$ | -   | 5   |      |  |

| 11                                        | $t_{f(IO)out}$          | Output fall time                                                | C <sub>L</sub> = 50 pF, V <sub>DDIOx</sub> ≥ 2.7 V | -   | 8   | ns   |  |

|                                           |                         |                                                                 | C <sub>L</sub> = 50 pF, V <sub>DDIOX</sub> < 2.7 V | -   | 12  |      |  |

|                                           |                         |                                                                 | C <sub>L</sub> = 30 pF, V <sub>DDIOx</sub> ≥ 2.7 V | -   | 5   |      |  |

|                                           | $t_{r(IO)out}$          | Output rise time                                                | C <sub>L</sub> = 50 pF, V <sub>DDIOx</sub> ≥ 2.7 V | -   | 8   |      |  |

|                                           |                         |                                                                 | C <sub>L</sub> = 50 pF, V <sub>DDIOX</sub> < 2.7 V | -   | 12  |      |  |

| Fm+                                       | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup>                                |                                                    | -   | 2   | MHz  |  |

| configuration                             | t <sub>f(IO)out</sub>   | Output fall time                                                | C <sub>L</sub> = 50 pF                             | -   | 12  |      |  |

| (4)                                       | t <sub>r(IO)out</sub>   | Output rise time                                                |                                                    | -   | 34  | ns   |  |

| -                                         | t <sub>EXTIpw</sub>     | Pulse width of external signals detected by the EXTI controller | -                                                  | 10  | -   | ns   |  |

<sup>1.</sup> The I/O speed is configured using the OSPEEDRx[1:0] bits. Refer to the STM32F0xxxx RM0091 reference manual for a description of GPIO Port configuration register.

<sup>2.</sup> Guaranteed by design, not tested in production.

<sup>3.</sup> The maximum frequency is defined in Figure 22.

<sup>4.</sup> When Fm+ configuration is set, the I/O speed control is bypassed. Refer to the STM32F0xxxx reference manual RM0091 for a detailed description of Fm+ I/O configuration.

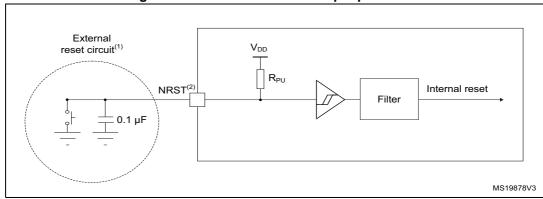

Figure 23. Recommended NRST pin protection

- 1. The external capacitor protects the device against parasitic resets.

- 2. The user must ensure that the level on the NRST pin can go below the  $V_{IL(NRST)}$  max level specified in *Table 49: NRST pin characteristics*. Otherwise the reset will not be taken into account by the device.

## 6.3.16 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 50* are derived from tests performed under the conditions summarized in *Table 18: General operating conditions*.

Note: It is recommended to perform a calibration after each power-up.

Table 50. ADC characteristics

| Symbol                           | Parameter                                     | Conditions                                      | Min   | Тур | Max       | Unit               |

|----------------------------------|-----------------------------------------------|-------------------------------------------------|-------|-----|-----------|--------------------|

| $V_{DDA}$                        | Analog supply voltage for ADC ON              | -                                               | 2.4   | -   | 3.6       | V                  |

| I <sub>DDA (ADC)</sub>           | Current consumption of the ADC <sup>(1)</sup> | V <sub>DDA</sub> = 3.3 V                        | -     | 0.9 | -         | mA                 |

| f <sub>ADC</sub>                 | ADC clock frequency                           | -                                               | 0.6   | -   | 14        | MHz                |

| f <sub>S</sub> <sup>(2)</sup>    | Sampling rate                                 | 12-bit resolution                               | 0.043 | -   | 1         | MHz                |

| f <sub>TRIG</sub> <sup>(2)</sup> | External trigger frequency                    | f <sub>ADC</sub> = 14 MHz,<br>12-bit resolution | -     | -   | 823       | kHz                |

|                                  |                                               | 12-bit resolution                               | -     | -   | 17        | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub>                 | Conversion voltage range                      | -                                               | 0     | -   | $V_{DDA}$ | V                  |

| R <sub>AIN</sub> <sup>(2)</sup>  | External input impedance                      | See Equation 1 and Table 51 for details         | -     | -   | 50        | kΩ                 |

| R <sub>ADC</sub> <sup>(2)</sup>  | Sampling switch resistance                    | -                                               | -     | -   | 1         | kΩ                 |

| C <sub>ADC</sub> <sup>(2)</sup>  | Internal sample and hold capacitor            | -                                               | -     | -   | 8         | pF                 |

| + (2)(3)                         | Calibration time                              | f <sub>ADC</sub> = 14 MHz                       |       | 5.9 |           | μs                 |

| $t_{CAL}^{(2)(3)}$               | Calibration tille                             | -                                               |       | 83  |           | 1/f <sub>ADC</sub> |

## 6.3.17 Temperature sensor characteristics

Table 53. TS characteristics

| Symbol                             | Parameter                                      | Min  | Тур  | Max  | Unit  |

|------------------------------------|------------------------------------------------|------|------|------|-------|

| T <sub>L</sub> <sup>(1)</sup>      | V <sub>SENSE</sub> linearity with temperature  | -    | ± 1  | ± 2  | °C    |

| Avg_Slope <sup>(1)</sup>           | Average slope                                  | 4.0  | 4.3  | 4.6  | mV/°C |

| V <sub>30</sub>                    | Voltage at 30 °C (± 5 °C) <sup>(2)</sup>       | 1.34 | 1.43 | 1.52 | V     |

| t <sub>START</sub> <sup>(1)</sup>  | ADC_IN16 buffer startup time                   | -    | -    | 10   | μs    |

| t <sub>S_temp</sub> <sup>(1)</sup> | ADC sampling time when reading the temperature | 4    | -    | -    | μs    |

<sup>1.</sup> Guaranteed by design, not tested in production.

## 6.3.18 V<sub>BAT</sub> monitoring characteristics

Table 54. V<sub>BAT</sub> monitoring characteristics

| Symbol                             | Parameter                                           | Min | Тур    | Max | Unit |

|------------------------------------|-----------------------------------------------------|-----|--------|-----|------|

| R                                  | Resistor bridge for V <sub>BAT</sub>                | -   | 2 x 50 | -   | kΩ   |

| Q                                  | Ratio on V <sub>BAT</sub> measurement               | -   | 2      | -   | -    |

| Er <sup>(1)</sup>                  | Error on Q                                          |     | -      | +1  | %    |

| t <sub>S_vbat</sub> <sup>(1)</sup> | ADC sampling time when reading the V <sub>BAT</sub> | 4   | -      | -   | μs   |

<sup>1.</sup> Guaranteed by design, not tested in production.

## 6.3.19 Timer characteristics

The parameters given in the following tables are guaranteed by design.

Refer to Section 6.3.14: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

Table 55. TIMx characteristics

| Symbol                 | Parameter                  | Conditions                    | Min | Тур                     | Max | Unit                 |

|------------------------|----------------------------|-------------------------------|-----|-------------------------|-----|----------------------|

| t =====                | Timer resolution time      | -                             | -   | 1                       | -   | t <sub>TIMxCLK</sub> |

| <sup>t</sup> res(TIM)  | Time resolution time       | f <sub>TIMxCLK</sub> = 48 MHz | -   | 20.8                    | -   | ns                   |

| f                      | Timer external clock       | -                             | -   | f <sub>TIMxCLK</sub> /2 | -   | MHz                  |

| f <sub>EXT</sub>       | frequency on CH1 to<br>CH4 | f <sub>TIMxCLK</sub> = 48 MHz | -   | 24                      | -   | MHz                  |

|                        | 16-bit timer maximum       | -                             | ı   | 2 <sup>16</sup>         | ı   | t <sub>TIMxCLK</sub> |

| t <sub>MAX_COUNT</sub> | period                     | f <sub>TIMxCLK</sub> = 48 MHz | -   | 1365                    | ı   | μs                   |

|                        | 32-bit counter             | -                             | -   | 2 <sup>32</sup>         | -   | t <sub>TIMxCLK</sub> |

|                        | maximum period             | f <sub>TIMxCLK</sub> = 48 MHz | -   | 89.48                   | -   | s                    |

Measured at V<sub>DDA</sub> = 3.3 V ± 10 mV. The V<sub>30</sub> ADC conversion result is stored in the TS\_CAL1 byte. Refer to Table 3: Temperature sensor calibration values.

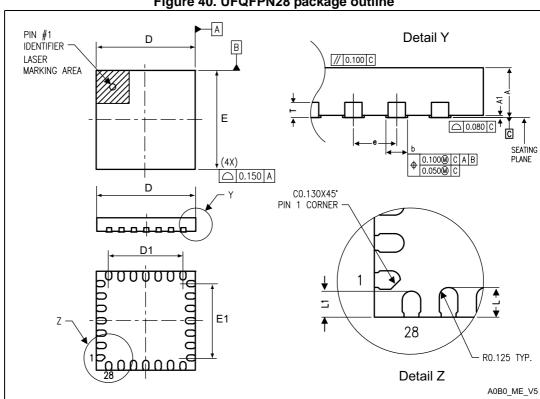

#### 7.4 **UFQFPN28** package information

UFQFPN28 is a 28-lead, 4x4 mm, 0.5 mm pitch, ultra-thin fine-pitch quad flat package.

Figure 40. UFQFPN28 package outline

1. Drawing is not to scale.

Table 64. UFQFPN28 package mechanical data<sup>(1)</sup>

| Symbol | millimeters |       |       | inches |        |        |

|--------|-------------|-------|-------|--------|--------|--------|

| Symbol | Min         | Тур   | Max   | Min    | Тур    | Max    |

| А      | 0.500       | 0.550 | 0.600 | 0.0197 | 0.0217 | 0.0236 |

| A1     | -           | 0.000 | 0.050 | -      | 0.0000 | 0.0020 |

| D      | 3.900       | 4.000 | 4.100 | 0.1535 | 0.1575 | 0.1614 |

| D1     | 2.900       | 3.000 | 3.100 | 0.1142 | 0.1181 | 0.1220 |

| Е      | 3.900       | 4.000 | 4.100 | 0.1535 | 0.1575 | 0.1614 |

| E1     | 2.900       | 3.000 | 3.100 | 0.1142 | 0.1181 | 0.1220 |

| L      | 0.300       | 0.400 | 0.500 | 0.0118 | 0.0157 | 0.0197 |

| L1     | 0.250       | 0.350 | 0.450 | 0.0098 | 0.0138 | 0.0177 |

| Т      | -           | 0.152 | -     | -      | 0.0060 | -      |

| b      | 0.200       | 0.250 | 0.300 | 0.0079 | 0.0098 | 0.0118 |

| е      | -           | 0.500 | -     | -      | 0.0197 | -      |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

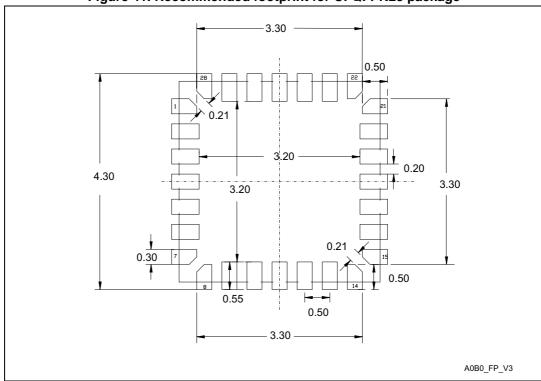

Figure 41. Recommended footprint for UFQFPN28 package

1. Dimensions are expressed in millimeters.

# 7.5 WLCSP25 package information

WLCSP25 is a 25-ball, 2.423 x 2.325 mm, 0.4 mm pitch wafer level chip scale package.

// bbb Z A1 ball location Detail A e2 Bump side Side view D Bump-Α1 □ eee Z orientation reference Seating plane Wafer back side Detail A (rotated 90°) WLCSP25\_A01N\_ME\_V1

Figure 43. WLCSP25 package outline

1. Drawing is not to scale.

Table 65. WLCSP25 package mechanical data

| Symbol               | millimeters |        |       | inches <sup>(1)</sup> |        |        |  |

|----------------------|-------------|--------|-------|-----------------------|--------|--------|--|

| Symbol               | Min         | Тур    | Max   | Min                   | Тур    | Max    |  |

| А                    | 0.525       | 0.555  | 0.585 | 0.0207                | 0.0219 | 0.0230 |  |

| A1                   | -           | 0.175  | -     | -                     | 0.0069 | -      |  |

| A2                   | -           | 0.380  | -     | -                     | 0.0150 | -      |  |

| A3 <sup>(2)</sup>    | -           | 0.025  | -     | -                     | 0.0010 | -      |  |

| b <sup>(3) (4)</sup> | 0.220       | 0.250  | 0.280 | 0.0087                | 0.0098 | 0.0110 |  |

| D                    | 2.388       | 2.423  | 2.458 | 0.0940                | 0.0954 | 0.0968 |  |

| Е                    | 2.29        | 2.325  | 2.36  | 0.0902                | 0.0915 | 0.0929 |  |

| е                    | -           | 0.400  | -     | -                     | 0.0157 | -      |  |

| e1                   | -           | 1.600  | -     | -                     | 0.0630 | -      |  |

| e2                   | -           | 1.600  | -     | -                     | 0.0630 | -      |  |

| F                    | -           | 0.4115 | -     | -                     | 0.0162 | -      |  |

| G                    | -           | 0.3625 | -     | -                     | 0.0143 | -      |  |

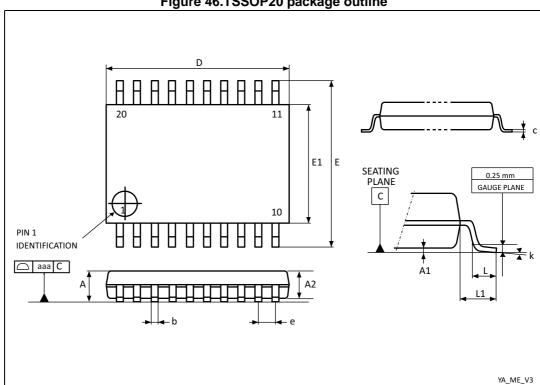

#### 7.6 **TSSOP20** package information

TSSOP20 is a 20-lead thin shrink small-outline, 6.5 x 4.4 mm, 0.65 mm pitch, package.

Figure 46.TSSOP20 package outline

1. Drawing is not to scale.

Table 67. TSSOP20 package mechanical data

| Symbol            | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|-------------------|-------------|-------|-------|-----------------------|--------|--------|

|                   | Min.        | Тур.  | Max.  | Min.                  | Тур.   | Max.   |

| Α                 | -           | -     | 1.200 | -                     | -      | 0.0472 |

| A1                | 0.050       | -     | 0.150 | 0.0020                | -      | 0.0059 |

| A2                | 0.800       | 1.000 | 1.050 | 0.0315                | 0.0394 | 0.0413 |

| b                 | 0.190       | -     | 0.300 | 0.0075                | -      | 0.0118 |

| С                 | 0.090       | -     | 0.200 | 0.0035                | -      | 0.0079 |

| D <sup>(2)</sup>  | 6.400       | 6.500 | 6.600 | 0.2520                | 0.2559 | 0.2598 |

| E                 | 6.200       | 6.400 | 6.600 | 0.2441                | 0.2520 | 0.2598 |

| E1 <sup>(3)</sup> | 4.300       | 4.400 | 4.500 | 0.1693                | 0.1732 | 0.1772 |

| е                 | -           | 0.650 | -     | -                     | 0.0256 | -      |

| L                 | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |

| L1                | -           | 1.000 | -     | -                     | 0.0394 | -      |

DocID025743 Rev 5 96/106

Table 70. Document revision history (continued)

| Date                      | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28-Aug-2015 3 (continued) |          | Added WLCSP25 package, updates in the following:  - Table 1: Device summary,  - Section 2: Description,  - Table 2: STM32F031x4/x6 family device features and peripheral counts,  - Section 4: Pinouts and pin description: addition of Figure 7: WLCSP25 25-ball package ballout (bump side) and update of Table 11: Pin definitions,  - Table 18: General operating conditions,  - Section 7: Package information with the addition of Section 7.5: WLCSP25 package information,  - Table 68: Package thermal characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 16-Dec-2015               | 4        | Cover page:  - number of timers added in the title  - Table 1: Device summary - STM32F031x4 added Section 2: Description:  - Figure 1: Block diagram updated Section 3: Functional overview:  - Figure 2: Clock tree updated  - Section 3.5.4: Low-power modes - added explicit inf. on peripherals configurable to operate with HSI  - Section 3.10.2: Internal voltage reference (V <sub>REFINT</sub> ) - removed information on comparators  - Section 3.11.2: General-purpose timers (TIM2, 3, 14, 16, 17) - number of gen-purpose timers corrected  - Section Table 7.: STM32F031x4/x6 PC implementation - added 20mA output drive current Section 4: Pinouts and pin description:  - Package pinout figures updated (look and feel)  - Figure 7: WLCSP25 package pinout - now presented in top view  - Table 11: Pin definitions - notes 3 and 6 added Section 5: Memory mapping:  - added information on memory mapping difference of STM32F031x4 from STM32F031x6 Section 6: Electrical characteristics:  - Table 22: Embedded internal reference voltage: removed -40°-to-85° condition and associated note for V <sub>REFINT</sub> - Table 25 and Table 26 values rounded to 1 decimal  - Table 46: I/O static characteristics - removed note  - Table 50: ADC characteristics - updated some parameter values, test conditions and added footnotes (3) and (4) |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics - All rights reserved