Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | ARM® Cortex®-M3                                                                 |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | CSIO, EBI/EMI, I <sup>2</sup> C, LINbus, UART/USART, USB                        |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 83                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                     |

| Data Converters            | A/D 16x12b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-LQFP                                                                        |

| Supplier Device Package    | 100-LQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb9af311napmc-g-jne2 |

|                            |                                                                                 |

#### **Multi-function Timer (Max 2units)**

The Multi-function timer is composed of the following blocks.

- ■16-bit free-run timer × 3ch/unit

- ■Input capture × 4ch/unit

- ■Output compare × 6ch/unit

- ■A/D activation compare × 3ch/unit

- ■Waveform generator × 3ch/unit

- ■16-bit PPG timer x 3ch/unit

The following function can be used to achieve the motor control.

- ■PWM signal output function

- ■DC chopper waveform output function

- ■Dead time function

- ■Input capture function

- ■A/D converter activate function

- ■DTIF (Motor emergency stop) interrupt function

# Quadrature Position/Revolution Counter (QPRC) (Max 2units)

The Quadrature Position/Revolution Counter (QPRC) is used to measure the position of the position encoder. Moreover, it is possible to use up/down counter.

- ■The detection edge of the three external event input pins AIN, BIN and ZIN is configurable.

- ■16-bit position counter

- ■16-bit revolution counter

- ■Two 16-bit compare registers

#### **Dual Timer (32/16bit Down Counter)**

The Dual Timer consists of two programmable 32/16-bit down counters.

Operation mode is selectable from the followings for each timer channel.

- ■Free-running

- ■Periodic (=Reload)

- ■One-shot

#### **Watch Counter**

The Watch counter is used for wake up from Low-Power Consumption mode.

Interval timer: up to 64s (Max) @ Sub Clock: 32.768kHz

#### Watch dog Timer (2channels)

A watchdog timer can generate interrupts or a reset when a time-out value is reached.

This series consists of two different watchdogs, a "Hardware" watchdog and a, "Software" watchdog.

The "Hardware" watchdog timer is clocked by the built-in low speed CR oscillator. Therefore, the "Hardware" watchdog is active in any low-power consumption modes except STOP mode.

#### **External Interrupt Controller Unit**

- ■Up to 16 external interrupt input pins.

- ■Include one non-maskable interrupt (NMI) input pin.

#### **General-Purpose I/O Port**

This series can use its pins as general-purpose I/O ports when they are not used for external bus or peripherals. Moreover, the port relocate function is built in. It can set which I/O port the peripheral function can be allocated to.

- ■Capable of pull-up control per pin

- ■Capable of reading pin level directly

- ■Built-in the port relocate function

- ■Up to 83 fast General Purpose I/O Ports @ 100pin Package

- ■Some ports are 5V tolerant I/O (MB9AF315MA/NA, MB9AF316MA/NA only)

Please see "Pin Description" to confirm the corresponding pins.

#### CRC (Cyclic Redundancy Check) Accelerator

CCITT CRC16 and IEEE-802.3 CRC32 are supported.

The CRC accelerator calculates the CRC which has a heavy software processing load, and achieves a reduction of the integrity check processing load for reception data and storage.

- ■CCITT CRC16 Generator Polynomial: 0x1021

- ■IEEE-802.3 CRC32 Generator Polynomial: 0x04C11DB7

|          |         | Pin No  |         |                   |                      | I/O circuit    | Pin state |

|----------|---------|---------|---------|-------------------|----------------------|----------------|-----------|

| LQFP-100 | QFP-100 | BGA-112 | LQFP-80 | LQFP-64<br>QFN-64 | Pin name             | type           | type      |

|          |         |         |         |                   | P55                  |                |           |

|          |         |         |         |                   | SCK6_0               |                |           |

| _        |         |         | 1_      |                   | (SCL6_0)             |                |           |

| 7        | 85      | D3      | 7       | -                 | ADTG_1               | E              | I         |

|          |         |         |         |                   | RTO15_0<br>(PPG14_0) |                |           |

|          |         |         |         |                   | MADATA05_1           |                |           |

|          |         |         |         |                   | P56                  |                |           |

| 8        | 86      | D5      | 8       | _                 | INT08_2              | E              | Н         |

| O        | 00      | 53      |         |                   | DTTI1X_0             | 7              | ' '       |

|          |         |         |         |                   | MADATA06_1           |                |           |

|          |         |         |         |                   | P30                  |                |           |

|          |         |         |         | 5                 | AIN0_0               |                |           |

| 9        | 87      | E1      | 9       | 5                 | TIOB0_1              | E              | Н         |

|          |         |         |         |                   | INT03_2              |                |           |

|          |         |         |         | -                 | MADATA07_1           |                |           |

|          |         |         |         |                   | P31                  |                |           |

|          |         |         |         |                   | BIN0_0               |                |           |

|          |         |         |         | 6                 | TIOB1_1              |                |           |

| 10       | 88      | E2      | 10      |                   | SCK6_1               | E              | Н         |

|          |         |         |         |                   | (SCL6_1)<br>INT04_2  | _              |           |

|          |         |         |         | -                 | MADATA08_1           | _              |           |

|          |         |         |         | -                 | P32                  |                |           |

|          |         |         |         |                   | ZIN0_0               |                |           |

|          |         |         |         |                   | TIOB2_1              | _              |           |

| 11       | 89      | E3      | 11      | 7                 | SOT6_1               | ⊢ <sub>E</sub> | Н         |

|          |         |         | ''      |                   | (SDA6_1)             | -              | ' '       |

|          |         |         |         |                   | INT05_2              |                |           |

|          |         |         |         | -                 | MADATA09_1           |                |           |

|          |         |         |         |                   | P33                  |                |           |

|          |         |         |         |                   | INT04_0              |                |           |

|          |         |         |         | 8                 | TIOB3_1              |                |           |

| 12       | 90      | E4      | 12      |                   | SIN6_1               | ⊢ E            | Н         |

|          |         |         |         |                   | ADTG_6               |                |           |

|          |         |         |         | -                 | MADATA10_1           |                |           |

|          |         |         |         |                   | P34                  |                |           |

|          |         |         |         |                   | FRCK0_0              | $\dashv$ _     |           |

| 13       | 91      | F1      | -       | -                 | TIOB4_1              | ⊢ E            | I         |

|          |         |         |         |                   | MADATA11_1           | =              |           |

|          |         | Pin No  |         |                   |          | I/O circuit | Pin state |

|----------|---------|---------|---------|-------------------|----------|-------------|-----------|

| LQFP-100 | QFP-100 | BGA-112 | LQFP-80 | LQFP-64<br>QFN-64 | Pin name | type        | type      |

|          |         |         |         |                   | P4D      |             |           |

|          |         |         |         |                   | TIOB4_0  |             |           |

|          |         |         |         | 26                | SOT7_1   |             |           |

| 44       | 22      | J7      | 34      |                   | (SDA7_1) | E / I*      | 1         |

|          |         |         |         |                   | BIN1_2   |             |           |

|          |         |         |         | _                 | FRCK1_1  |             |           |

|          |         |         |         |                   | MAD07_1  |             |           |

|          |         |         |         |                   | P4E      |             |           |

|          |         |         |         |                   | TIOB5_0  |             |           |

| 45       | 23      | K8      | 35      | 27                | INT06_2  | E / I*      | 1         |

| 45       | 23      | No      | 33      |                   | SIN7_1   |             | '         |

|          |         |         |         |                   | ZIN1_2   |             |           |

|          |         |         |         | -                 | MAD08_1  |             |           |

| 46       | 24      | K9      | 36      | 28                | MD1      | С           | Р         |

| 46       | 24      | N9      | 30      | 20                | PE0      |             |           |

| 47       | 25      | L8      | 37      | 29                | MD0      | J           | D         |

| 48       | 26      | L9      | 20      | 30                | X0       | Δ.          | Δ         |

| 40       | 26      | L9      | 38      | 30                | PE2      | A           | A         |

| 49       | 27      | L10     | 39      | 31                | X1       | A           | В         |

| 49       | 21      | LIU     | 39      | 31                | PE3      | A           | В         |

| 50       | 28      | L11     | 40      | 32                | VSS      | -           |           |

| 51       | 29      | K11     | 41      | 33                | VCC      | -           |           |

| 52       | 30      | J11     | 42      | 34                | P10      | F           | K         |

| 52       | 30      | 311     | 42      | 34                | AN00     |             | K         |

|          |         |         |         |                   | P11      |             |           |

|          |         |         |         |                   | AN01     |             |           |

| 53       | 31      | J10     | 43      | 35                | SIN1_1   | F           | ,         |

| 53       | 31      | 310     | 43      |                   | INT02_1  | F           | L         |

|          |         |         |         |                   | FRCK0_2  |             |           |

|          |         |         |         | -                 | MAD09_1  |             |           |

|          |         |         |         |                   | P12      |             |           |

|          |         |         |         |                   | AN02     |             |           |

| 54       | 22      | 10      | 144     | 36                | SOT1_1   | F           | К         |

| 54       | 32 J8   | Jo      | 44      |                   | (SDA1_1) | ۲           | ^         |

|          |         |         |         |                   | IC00_2   |             |           |

|          |         |         |         | -                 | MAD10_1  |             |           |

| -        | -       | K10     | -       | -                 | VSS      | -           | •         |

| -        | -       | J9      | -       | -                 | VSS      | -           |           |

|          |          |                                                 |          |         | Pin No  |         |                   |

|----------|----------|-------------------------------------------------|----------|---------|---------|---------|-------------------|

| Module   | Pin name | Function                                        | LQFP-100 | QFP-100 | BGA-112 | LQFP-80 | LQFP-64<br>QFN-64 |

| Debugger | SWCLK    | Serial wire debug interface clock input         | 78       | 56      | В9      | 62      | 50                |

|          | SWDIO    | Serial wire debug interface data input / output | 80       | 58      | A8      | 64      | 52                |

|          | SWO      | Serial wire viewer output                       | 81       | 59      | B8      | 65      | 53                |

|          | TCK      | J-TAG test clock input                          | 78       | 56      | B9      | 62      | 50                |

|          | TDI      | J-TAG test data input                           | 79       | 57      | B11     | 63      | 51                |

|          | TDO      | J-TAG debug data output                         | 81       | 59      | B8      | 65      | 53                |

|          | TMS      | J-TAG test mode state input/output              | 80       | 58      | A8      | 64      | 52                |

|          | TRACECLK | Trace CLK output of ETM                         | 86       | 64      | C7      | -       | -                 |

|          | TRACED0  |                                                 | 82       | 60      | C8      | -       | -                 |

|          | TRACED1  | To an electric section of ETM                   | 83       | 61      | D9      | -       | -                 |

|          | TRACED2  | Trace data output of ETM                        | 84       | 62      | A7      | -       | -                 |

|          | TRACED3  | ]                                               | 85       | 63      | B7      | -       | -                 |

|          | TRSTX    | J-TAG test reset Input                          | 77       | 55      | A9      | 61      | 49                |

| External | MAD00_1  |                                                 | 31       | 9       | H5      | 21      | -                 |

| Bus      | MAD01_1  | 7                                               | 32       | 10      | L6      | 22      | -                 |

|          | MAD02_1  |                                                 | 39       | 17      | K6      | 29      | -                 |

|          | MAD03_1  | 7                                               | 40       | 18      | J6      | 30      | -                 |

|          | MAD04_1  | 1                                               | 41       | 19      | L7      | 31      | -                 |

|          | MAD05_1  | 1                                               | 42       | 20      | K7      | 32      | -                 |

|          | MAD06_1  | 1                                               | 43       | 21      | H6      | 33      | -                 |

|          | MAD07_1  | 7                                               | 44       | 22      | J7      | 34      | -                 |

|          | MAD08_1  | 1                                               | 45       | 23      | K8      | 35      | -                 |

|          | MAD09_1  | 1                                               | 53       | 31      | J10     | 43      | -                 |

|          | MAD10_1  | 1                                               | 54       | 32      | J8      | 44      | -                 |

|          | MAD11_1  |                                                 | 55       | 33      | H10     | 45      | -                 |

|          | MAD12_1  | External bus interface address bus              | 56       | 34      | H9      | 46      | -                 |

|          | MAD13_1  | 1                                               | 57       | 35      | H7      | 47      | -                 |

|          | MAD14_1  |                                                 | 58       | 36      | G10     | 48      | -                 |

|          | MAD15_1  | 1                                               | 59       | 37      | G9      | 49      | -                 |

|          | MAD16_1  | 1                                               | 63       | 41      | G8      | 53      | -                 |

|          | MAD17_1  | 1                                               | 64       | 42      | F10     | 54      | -                 |

|          | MAD18_1  | 1                                               | 65       | 43      | F9      | 55      | -                 |

|          | MAD19_1  | 1                                               | 66       | 44      | E11     | 56      | -                 |

|          | MAD20_1  | 1                                               | 67       | 45      | E10     | -       | -                 |

|          | MAD21_1  | 1                                               | 68       | 46      | F8      | -       | -                 |

|          | MAD22_1  | 1                                               | 69       | 47      | E9      | -       | -                 |

|          | MAD23_1  | 1                                               | 70       | 48      | D11     | -       | -                 |

|          | MAD24_1  | 1                                               | 74       | 52      | C10     | 60      | -                 |

|                          |          |                                         |          |         | Pin No  |         |                   |

|--------------------------|----------|-----------------------------------------|----------|---------|---------|---------|-------------------|

| Module                   | Pin name | Function                                | LQFP-100 | QFP-100 | BGA-112 | LQFP-80 | LQFP-64<br>QFN-64 |

| GPIO                     | P00      |                                         | 77       | 55      | A9      | 61      | 49                |

|                          | P01      |                                         | 78       | 56      | B9      | 62      | 50                |

|                          | P02      |                                         | 79       | 57      | B11     | 63      | 51                |

|                          | P03      |                                         | 80       | 58      | A8      | 64      | 52                |

|                          | P04      |                                         | 81       | 59      | B8      | 65      | 53                |

|                          | P05      |                                         | 82       | 60      | C8      | =       | -                 |

|                          | P06      |                                         | 83       | 61      | D9      | -       | -                 |

|                          | P07      | 2                                       | 84       | 62      | A7      | 66      | -                 |

|                          | P08      | General-purpose I/O port 0              | 85       | 63      | B7      | -       | -                 |

|                          | P09      |                                         | 86       | 64      | C7      | -       | -                 |

| POA<br>POB<br>POC<br>POD | P0A      |                                         | 87       | 65      | D7      | 67      | 54                |

|                          |          | 88                                      | 66       | A6      | 68      | 55      |                   |

|                          | P0C      |                                         | 89       | 67      | B6      | 69      | 56                |

|                          | P0D      |                                         | 90       | 68      | C6      | 70      | -                 |

|                          | P0E      |                                         | 91       | 69      | A5      | 71      | -                 |

|                          | P0F      |                                         | 92       | 70      | B5      | 72      | 57                |

|                          | P10      |                                         | 52       | 30      | J11     | 42      | 34                |

|                          | P11      |                                         | 53       | 31      | J10     | 43      | 35                |

|                          | P12      |                                         | 54       | 32      | J8      | 44      | 36                |

|                          | P13      |                                         | 55       | 33      | H10     | 45      | 37                |

|                          | P14      |                                         | 56       | 34      | H9      | 46      | 38                |

|                          | P15      |                                         | 57       | 35      | H7      | 47      | 39                |

|                          | P16      |                                         | 58       | 36      | G10     | 48      | -                 |

|                          | P17      | 7                                       | 59       | 37      | G9      | 49      | 40                |

|                          | P18      | General-purpose I/O port 1              | 63       | 41      | G8      | 53      | 44                |

|                          | P19      |                                         | 64       | 42      | F10     | 54      | 45                |

|                          | P1A      |                                         | 65       | 43      | F9      | 55      | -                 |

|                          | P1B      |                                         | 66       | 44      | E11     | 56      | -                 |

|                          | P1C      |                                         | 67       | 45      | E10     | -       | -                 |

|                          | P1D      |                                         | 68       | 46      | F8      | -       | -                 |

|                          | P1E      |                                         | 69       | 47      | E9      | -       | -                 |

|                          | P1F      |                                         | 70       | 48      | D11     | -       | -                 |

|                          | P20      |                                         | 74       | 52      | C10     | 60      | -                 |

|                          | P21      | ] , , , , , , , , , , , , , , , , , , , | 73       | 51      | C11     | 59      | 48                |

|                          | P22      | General-purpose I/O port 2              | 72       | 50      | E8      | 58      | 47                |

|                          | P23      |                                         | 71       | 49      | D10     | 57      | 46                |

|                          |          |                                         |          |         |         |         |                   |

|                    |                                                   |                                                                                                                                                                              | Pin No   |         |         |         |                   |  |  |

|--------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------|---------|---------|-------------------|--|--|

| Module             | Pin name                                          | Function                                                                                                                                                                     | LQFP-100 | QFP-100 | BGA-112 | LQFP-80 | LQFP-64<br>QFN-64 |  |  |

| Multi              | SIN4_0                                            |                                                                                                                                                                              | 87       | 65      | D7      | 67      | 54                |  |  |

| Function<br>Serial | SIN4_1                                            | Multifunction serial interface ch.4 input pin                                                                                                                                | 65       | 43      | F9      | 55      | -                 |  |  |

| 4                  | SIN4_2                                            |                                                                                                                                                                              | 82       | 60      | C8      | -       | -                 |  |  |

|                    | SOT4_0<br>(SDA4_0)                                | Multifunction serial interface ch.4                                                                                                                                          | 88       | 66      | A6      | 68      | 55                |  |  |

|                    | SOT4_1<br>(SDA4_1)<br>SOT4_2<br>(SDA4_2)          | This pin operates as SOT4 when it is used in a UART/CSIO/LIN (operation modes 0 to 3) and as SDA4 when it is                                                                 | 66       | 44      | E11     | 56      | -                 |  |  |

|                    |                                                   | used in an I <sup>2</sup> C (operation mode 4).                                                                                                                              | 83       | 61      | D9      | -       | -                 |  |  |

|                    | SCK4_0<br>(SCL4_0) Multifunction serial interface |                                                                                                                                                                              | 89       | 67      | B6      | 69      | 56                |  |  |

|                    | SCK4_1<br>(SCL4_1)                                | <ul> <li>clock I/O pin</li> <li>This pin operates as SCK4 when it is used in a CSIO (operation modes 2)</li> <li>and as SCL4 when it is used in an I<sup>2</sup>C</li> </ul> | 67       | 45      | E10     | -       | -                 |  |  |

|                    | SCK4_2<br>(SCL4_2)                                | (operation mode 4).                                                                                                                                                          | 84       | 62      | A7      | -       | -                 |  |  |

|                    | RTS4_0                                            |                                                                                                                                                                              | 90       | 68      | C6      | 70      | -                 |  |  |

|                    | RTS4_1                                            | Multifunction serial interface ch.4  RTS output pin                                                                                                                          | 69       | 47      | E9      | -       | -                 |  |  |

|                    | RTS4_2                                            | - Tere output piir                                                                                                                                                           | 86       | 64      | C7      | -       | -                 |  |  |

|                    | CTS4_0                                            |                                                                                                                                                                              | 91       | 69      | A5      | 71      | -                 |  |  |

|                    | CTS4_1                                            | Multifunction serial interface ch.4  CTS input pin                                                                                                                           | 68       | 46      | F8      | -       | -                 |  |  |

|                    | CTS4_2                                            |                                                                                                                                                                              | 85       | 63      | B7      | =       | =                 |  |  |

| Multi              | SIN5_0                                            | Multifunction serial interface ch.5                                                                                                                                          | 96       | 74      | C4      | 76      | 60                |  |  |

| Function<br>Serial | SIN5_2                                            | input pin                                                                                                                                                                    | 15       | 93      | F3      | -       | -                 |  |  |

| 5                  | SOT5_0<br>(SDA5_0)                                | Multifunction serial interface ch.5 output pin  This pin operates as SOT5 when it is                                                                                         | 95       | 73      | B4      | 75      | 59                |  |  |

|                    | SOT5_2<br>(SDA5_2)                                | used in a UART/CSIO/LIN (operation modes 0 to 3) and as SDA5 when it is used in an I <sup>2</sup> C (operation mode 4).                                                      | 16       | 94      | G1      | -       | -                 |  |  |

|                    | SCK5_0<br>(SCL5_0)                                | Multifunction serial interface ch.5 clock I/O pin  This pin operates as SCK5 when it is                                                                                      | 94       | 72      | C5      | 74      | 58                |  |  |

|                    | SCK5_2<br>(SCL5_2)                                | used in a CSIO (operation modes 2) and as SCL5 when it is used in an I <sup>2</sup> C (operation mode 4).                                                                    | 17       | 95      | G2      | -       | -                 |  |  |

|                   |                      |                                                                   |          |         | Pin No  |         |                   |

|-------------------|----------------------|-------------------------------------------------------------------|----------|---------|---------|---------|-------------------|

| Module            | Pin name             | Function                                                          | LQFP-100 | QFP-100 | BGA-112 | LQFP-80 | LQFP-64<br>QFN-64 |

| Multi             | DTTI1X_0             | Input signal of wave form generator to                            | 8        | 86      | D5      | 8       | -                 |

| Function<br>Timer | DTTI1X_1             | control outputs RTO10 to RTO15 of multi-function timer 1          | 39       | 17      | K6      | 29      | -                 |

| 1                 | FRCK1_0              | 16-bit free-run timer ch.1 external                               | 87       | 65      | D7      | 67      | -                 |

|                   | FRCK1_1              | clock input pin                                                   | 44       | 22      | J7      | 34      | -                 |

|                   | IC10_0               |                                                                   | 88       | 66      | A6      | 68      | -                 |

|                   | IC10_1               |                                                                   | 40       | 18      | J6      | 30      | -                 |

|                   | IC11_0               |                                                                   | 89       | 67      | B6      | 69      | -                 |

|                   | 1011_1               | 16-bit input capture input pin of                                 | 41       | 19      | L7      | 31      | -                 |

|                   |                      | multi-function timer 1 ICxx describes channel number.             | 90       | 68      | C6      | 70      | -                 |

|                   |                      |                                                                   | 42       | 20      | K7      | 32      | -                 |

|                   |                      |                                                                   | 91       | 69      | A5      | 71      | -                 |

|                   |                      |                                                                   | 43       | 21      | H6      | 33      | -                 |

|                   | RTO10_0<br>(PPG10_0) | Wave form generator output of multi-function timer 1              | 2        | 80      | C1      | 2       | -                 |

|                   | RTO10_1<br>(PPG10_1) | This pin operates as PPG10 when it is used in PPG 1 output modes. | 27       | 5       | J4      | -       | -                 |

|                   | RTO11_0<br>(PPG10_0) | Wave form generator output of multi-function timer 1              | 3        | 81      | C2      | 3       | -                 |

|                   | RTO11_1<br>(PPG10_1) | This pin operates as PPG10 when it is used in PPG 1 output modes. | 28       | 6       | L5      | -       | -                 |

|                   | RTO12_0<br>(PPG12_0) | Wave form generator output of multi-function timer 1              | 4        | 82      | В3      | 4       | -                 |

|                   | RTO12_1<br>(PPG12_1) | This pin operates as PPG12 when it is used in PPG 1 output modes. | 29       | 7       | K5      | -       | -                 |

|                   | RTO13_0<br>(PPG12_0) | Wave form generator output of multi-function timer 1              | 5        | 83      | D1      | 5       | -                 |

|                   | RTO13_1<br>(PPG12_1) | This pin operates as PPG12 when it is used in PPG 1 output modes. | 30       | 8       | J5      | -       | -                 |

|                   | RTO14_0<br>(PPG14_0) | Wave form generator output of multi-function timer 1              | 6        | 84      | D2      | 6       | -                 |

|                   | RTO14_1<br>(PPG14_1) | This pin operates as PPG14 when it is used in PPG 1 output modes. | 31       | 9       | H5      | 21      | -                 |

|                   | RTO15_0<br>(PPG14_0) | Wave form generator output of multi-function timer 1              | 7        | 85      | D3      | 7       | -                 |

|                   | RTO15_1<br>(PPG14_1) | This pin operates as PPG14 when it is used in PPG 1 output modes. | 32       | 10      | L6      | 22      | -                 |

|                         |                             |                                  |          |         | Pin No  |         |                   |

|-------------------------|-----------------------------|----------------------------------|----------|---------|---------|---------|-------------------|

| Module                  | Pin name                    | Function                         | LQFP-100 | QFP-100 | BGA-112 | LQFP-80 | LQFP-64<br>QFN-64 |

| Quadrature              | AIN0_0                      |                                  | 9        | 87      | E1      | 9       | 5                 |

| Position/<br>Revolution | AIN0_1                      | QPRC ch.0 AIN input pin          | 40       | 18      | J6      | 30      | 22                |

| Counter                 | BIN0_0 BIN0_1 BIN0_2 ZIN0_0 |                                  | 2        | 80      | C1      | 2       | 2                 |

| 0                       |                             |                                  | 10       | 88      | E2      | 10      | 6                 |

|                         |                             | QPRC ch.0 BIN input pin          | 41       | 19      | L7      | 31      | 23                |

|                         |                             | ]                                | 3        | 81      | C2      | 3       | 3                 |

|                         |                             |                                  | 11       | 89      | E3      | 11      | 7                 |

|                         |                             | QPRC ch.0 ZIN input pin          | 42       | 20      | K7      | 32      | 24                |

|                         | ZIN0_2                      | ]                                | 4        | 82      | B3      | 4       | 4                 |

| Quadrature              | AIN1_1                      | ODDC ab 4 AIN input air          | 74       | 52      | C10     | 60      | -                 |

| Position/<br>Revolution | AIN1_2                      | - QPRC ch.1 AIN input pin        | 43       | 21      | H6      | 33      | 25                |

| Counter                 | BIN1_1                      | ODDC ab 4 DIN input pin          | 73       | 51      | C11     | 59      | -                 |

| 1                       | BIN1_2                      | - QPRC ch.1 BIN input pin        | 44       | 22      | J7      | 34      | 26                |

|                         | ZIN1_1                      | ODDC als 4 7IN input pin         | 72       | 50      | E8      | 58      | -                 |

|                         | ZIN1_2                      | QPRC ch.1 ZIN input pin          | 45       | 23      | K8      | 35      | 27                |

| USB                     | UDM0                        | USB Function / HOST D – pin      | 98       | 76      | А3      | 78      | 62                |

|                         | UDP0                        | USB Function / HOST D + pin      | 99       | 77      | A2      | 79      | 63                |

|                         | UHCONX                      | USB external pull-up control pin | 95       | 73      | B4      | 75      | 59                |

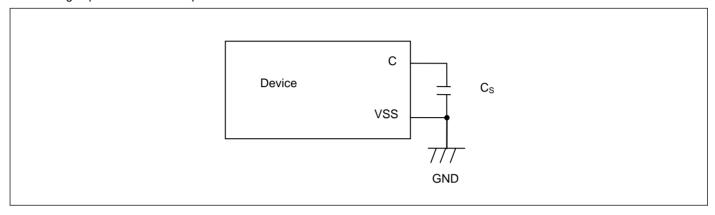

#### C Pin

This series contains the regulator. Be sure to connect a smoothing capacitor ( $C_s$ ) for the regulator between the C pin and the GND pin. Please use a ceramic capacitor or a capacitor of equivalent frequency characteristics as a smoothing capacitor. However, some laminated ceramic capacitors have the characteristics of capacitance variation due to thermal fluctuation (F characteristics and Y5V characteristics). Please select the capacitor that meets the specifications in the operating conditions to use by evaluating the temperature characteristics of a capacitor.

A smoothing capacitor of about 4.7µF would be recommended for this series.

#### Mode pins (MD0)

Connect the MD pin (MD0) directly to VCC or VSS pins. Design the printed circuit board such that the pull-up/down resistor stays low, as well as the distance between the mode pins and VCC pins or VSS pins is as short as possible and the connection impedance is low, when the pins are pulled-up/down such as for switching the pin level and rewriting the Flash memory data. It is because of preventing the device erroneously switching to test mode due to noise.

#### Notes on power-on

Turn power on/off in the following order or at the same time.

If not using the A/D converter, connect AVCC = VCC and AVSS = VSS.

Turning on: VCC → USBVCC

$VCC \rightarrow AVCC \rightarrow AVRH$

Turning off:  $USBVCC \rightarrow VCC$

$AVRH \rightarrow AVCC \rightarrow VCC$

#### **Serial Communication**

There is a possibility to receive wrong data due to the noise or other causes on the serial communication.

Therefore, design a printed circuit board so as to avoid noise.

Consider the case of receiving wrong data due to noise, perform error detection such as by applying a checksum of data at the end. If an error is detected, retransmit the data.

# Differences in features among the products with different memory sizes and between Flash products and MASK products

The electric characteristics including power consumption, ESD, latch-up, noise characteristics, and oscillation characteristics among the products with different memory sizes and between Flash products and MASK products are different because chip layout and memory structures are different.

If you are switching to use a different product of the same series, please make sure to evaluate the electric characteristics.

#### 12.3 DC Characteristics

## 12.3.1 Current rating

(Vcc = AVcc = 2.7V to 5.5V, USBVcc = 3.0V to 3.6V, Vss = AVss = 0V, Ta = -40°C to + 105°C)

| Davamatar                  | Cumpleal | Pin        |                                | Canditions                                                                        |       | lue   | 11:0:4 | Domorko |

|----------------------------|----------|------------|--------------------------------|-----------------------------------------------------------------------------------|-------|-------|--------|---------|

| Parameter                  | Symbol   | name       |                                | Conditions                                                                        | Typ*3 | Max*4 | Unit   | Remarks |

|                            |          |            | PLL                            | CPU: 40MHz, Peripheral: 40MHz, Flash 0Wait FRWTR.RWT = 00 FSYNDN.SD = 000 *5      | 32    | 41    | mA     | *1      |

| RUN<br>mode Icc<br>current |          | lcc<br>VCC | RUN mode                       | CPU: 40MHz, Peripheral: 40MHz, Flash 3Wait FRWTR.RWT = 00 FSYNDN.SD = 011 *5      | 21    | 28    | mA     | *1      |

|                            | Icc      |            | High-speed<br>CR<br>RUN mode   | CPU/ Peripheral : 4MHz*2 Flash 0Wait FRWTR.RWT = 00 FSYNDN.SD = 000               | 3.9   | 7.7   | mA     | *1      |

|                            |          |            | Sub<br>RUN mode                | CPU/ Peripheral : 32kHz<br>Flash 0Wait<br>FRWTR.RWT = 00<br>FSYNDN.SD = 000<br>*6 | 0.15  | 3.2   | mA     | *1      |

|                            |          |            | Low-speed<br>CR<br>RUN mode    | CPU/ Peripheral : 100kHz<br>Flash 0Wait<br>FRWTR.RWT = 00<br>FSYNDN.SD = 000      | 0.2   | 3.3   | mA     | *1      |

|                            |          |            | PLL<br>SLEEP mode              | Peripheral : 40MHz<br>*5                                                          | 10    | 15    | mA     | *1      |

| SLEEP<br>mode<br>current   | loop     | ccs        | High-speed<br>CR<br>SLEEP mode | Peripheral : 4MHz*2                                                               | 1.2   | 4.4   | mA     | *1      |

|                            | ICCS     |            | Sub<br>SLEEP mode              | Peripheral : 32kHz<br>*6                                                          | 0.1   | 3.1   | mA     | *1      |

|                            |          |            | Low-speed<br>CR<br>SLEEP mode  | Peripheral : 100kHz                                                               | 0.1   | 3.1   | mA     | *1      |

<sup>\*1:</sup> When all ports are fixed.

<sup>\*2:</sup> When setting it to 4MHz by trimming.

<sup>\*3:</sup> Ta=+25°C, V<sub>CC</sub>=5.5V

<sup>\*4:</sup> Ta=+105°C, V<sub>CC</sub>=5.5V

<sup>\*5:</sup> When using the crystal oscillator of 4 MHz (Including the current consumption of the oscillation circuit)

<sup>\*6:</sup> When using the crystal oscillator of 32 kHz (Including the current consumption of the oscillation circuit)

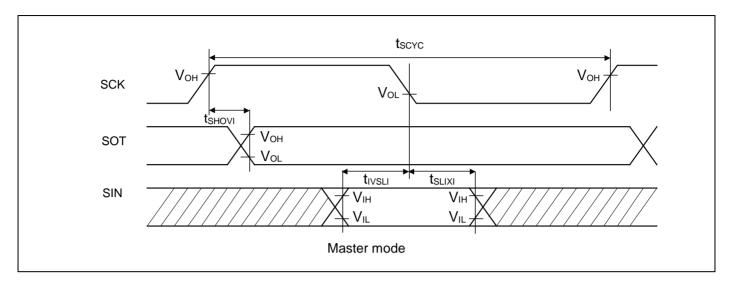

# 12.4.10 CSIO/UART Timing

CSIO (SPI = 0, SCINV = 0)

$(Vcc = 2.7V to 5.5V, Vss = 0V, Ta = -40^{\circ}C to + 105^{\circ}C)$

| Parameter                                   | Symbol             | Pin          | Conditions  | Vcc <       | Vcc < 4.5V |             | Vcc ≥ 4.5V |      |  |

|---------------------------------------------|--------------------|--------------|-------------|-------------|------------|-------------|------------|------|--|

| Parameter                                   | Symbol             | name         | Conditions  | Min         | Max        | Min         | Max        | Unit |  |

| Serial clock cycle time                     | t <sub>SCYC</sub>  | SCKx         |             | 4tcycp      | -          | 4tcycp      | -          | ns   |  |

| $SCK \downarrow \rightarrow SOT$ delay time | t <sub>SLOVI</sub> | SCKx<br>SOTx |             | - 30        | + 30       | - 20        | + 20       | ns   |  |

| SIN → SCK ↑ setup time                      | t <sub>IVSHI</sub> | SCKx<br>SINx | Master mode | 50          | -          | 30          | -          | ns   |  |

| $SCK \uparrow \rightarrow SIN$ hold time    | t <sub>SHIXI</sub> | SCKx<br>SINx |             | 0           | -          | 0           | -          | ns   |  |

| Serial clock "L" pulse width                | t <sub>SLSH</sub>  | SCKx         |             | 2tcycp - 10 | -          | 2tcycp - 10 | -          | ns   |  |

| Serial clock "H" pulse width                | t <sub>SHSL</sub>  | SCKx         |             | tcycp + 10  | -          | tcycp + 10  | -          | ns   |  |

| $SCK \downarrow \rightarrow SOT$ delay time | t <sub>SLOVE</sub> | SCKx<br>SOTx |             | -           | 50         | -           | 30         | ns   |  |

| SIN → SCK ↑ setup time                      | t <sub>IVSHE</sub> | SCKx<br>SINx | Slave mode  | 10          | -          | 10          | -          | ns   |  |

| SCK ↑→ SIN hold time                        | t <sub>SHIXE</sub> | SCKx<br>SINx |             | 20          | -          | 20          | -          | ns   |  |

| SCK falling time                            | tF                 | SCKx         |             | -           | 5          | -           | 5          | ns   |  |

| SCK rising time                             | tR                 | SCKx         |             | -           | 5          | -           | 5          | ns   |  |

#### Notes:

- ■The above characteristics apply to CLK synchronous mode.

- ■t<sub>CYCP</sub> indicates the APB bus clock cycle time.

About the APB bus number which Multi-function Serial is connected to, see "8. Block Diagram" in this datasheet.

- ■These characteristics only guarantee the same relocate port number.

For example, the combination of SCKx\_0 and SOTx\_1 is not guaranteed.

- ■When the external load capacitance  $C_L = 30 pF$ .

Document Number: 002-04674 Rev.\*A

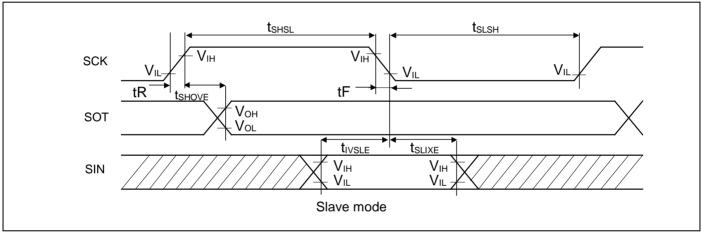

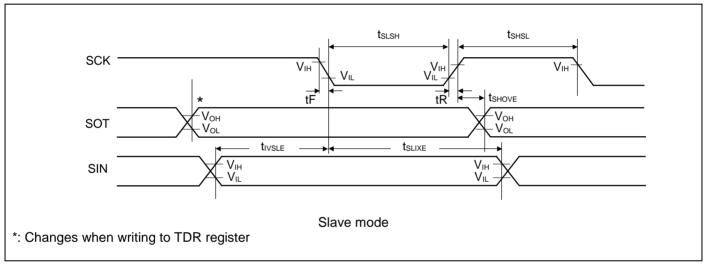

### CSIO (SPI = 1, SCINV = 0)

$(Vcc = 2.7V to 5.5V, Vss = 0V, Ta = -40^{\circ}C to + 105^{\circ}C)$

| Parameter                                          | Cumbal             | Pin             | Conditions  | Vcc -       | < 4.5V | Vcc ≥       | ≥ 4.5V | Unit |

|----------------------------------------------------|--------------------|-----------------|-------------|-------------|--------|-------------|--------|------|

| Parameter                                          | Symbol             | name Conditions |             | Min         | Max    | Min         | Max    | Onit |

| Serial clock cycle time                            | t <sub>SCYC</sub>  | SCKx            |             | 4tcycp      | -      | 4tcycp      | -      | ns   |

| $SCK \uparrow \to SOT \ delay\ time$               | t <sub>SHOVI</sub> | SCKx<br>SOTx    |             | - 30        | + 30   | - 20        | + 20   | ns   |

| $SIN \to SCK \downarrow setup \ time$              | t <sub>IVSLI</sub> | SCKx<br>SINx    | Master mode | 50          | -      | 30          | -      | ns   |

| $SCK\downarrow\toSIN\;hold\;time$                  | t <sub>SLIXI</sub> | SCKx<br>SINx    |             | 0           | -      | 0           | -      | ns   |

| $SOT \to SCK \downarrow delay time$                | t <sub>SOVLI</sub> | SCKx<br>SOTx    |             | 2tcycp - 30 | -      | 2tcycp - 30 | -      | ns   |

| Serial clock "L" pulse width                       | t <sub>SLSH</sub>  | SCKx            |             | 2tcycp - 10 | -      | 2tcycp - 10 | -      | ns   |

| Serial clock "H" pulse width                       | t <sub>SHSL</sub>  | SCKx            |             | tcycp + 10  | -      | tcycp + 10  | -      | ns   |

| $SCK \uparrow \to SOT \ delay \ time$              | t <sub>SHOVE</sub> | SCKx<br>SOTx    |             | -           | 50     | -           | 30     | ns   |

| $SIN \rightarrow SCK \downarrow setup time$        | t <sub>IVSLE</sub> | SCKx<br>SINx    | Slave mode  | 10          | -      | 10          | -      | ns   |

| $SCK \downarrow \rightarrow SIN \text{ hold time}$ | t <sub>SLIXE</sub> | SCKx<br>SINx    |             | 20          | -      | 20          | -      | ns   |

| SCK falling time                                   | tF                 | SCKx            |             | -           | 5      | -           | 5      | ns   |

| SCK rising time                                    | tR                 | SCKx            |             | -           | 5      | -           | 5      | ns   |

#### Notes:

- ■The above characteristics apply to CLK synchronous mode.

- ■t<sub>CYCP</sub> indicates the APB bus clock cycle time.

About the APB bus number which Multi-function Serial is connected to, see "8. Block Diagram" in this datasheet.

- ■These characteristics only guarantee the same relocate port number. For example, the combination of SCKx\_0 and SOTx\_1 is not guaranteed.

- ■When the external load capacitance  $C_L = 30 pF$ .

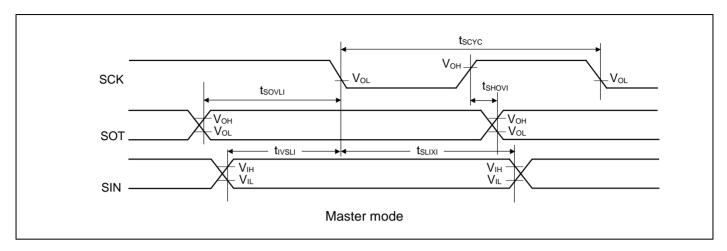

### CSIO (SPI = 1, SCINV = 1)

$(Vcc = 2.7V to 5.5V, Vss = 0V, Ta = -40^{\circ}C to + 105^{\circ}C)$

| Parameter                                 | Symbol             | Pin          | Conditions  | Vcc <       | 4.5V | Vcc ≥       | 4.5V | Unit |

|-------------------------------------------|--------------------|--------------|-------------|-------------|------|-------------|------|------|

| Parameter                                 | Symbol             | name         | Conditions  | Min         | Max  | Min         | Max  | Unit |

| Serial clock cycle time                   | t <sub>scyc</sub>  | SCKx         |             | 4tcycp      | -    | 4tcycp      | -    | ns   |

| SCK ↓→ SOT delay time                     | t <sub>SLOVI</sub> | SCKx<br>SOTx |             | - 30        | + 30 | - 20        | + 20 | ns   |

| SIN → SCK ↑ setup time                    | t <sub>IVSHI</sub> | SCKx<br>SINx | Master mode | 50          | -    | 30          | -    | ns   |

| SCK ↑ →SIN hold time                      | t <sub>SHIXI</sub> | SCKx<br>SINx |             | 0           | -    | 0           | =    | ns   |

| SOT → SCK ↑ delay time                    | t <sub>SOVHI</sub> | SCKx<br>SOTx |             | 2tcycp - 30 | -    | 2tcycp - 30 | -    | ns   |

| Serial clock "L" pulse width              | t <sub>SLSH</sub>  | SCKx         |             | 2tcycp - 10 | -    | 2tcycp - 10 | -    | ns   |

| Serial clock "H" pulse width              | t <sub>SHSL</sub>  | SCKx         |             | tcycp + 10  | -    | tcycp + 10  | -    | ns   |

| $SCK\downarrow \to SOT \; delay \; time$  | t <sub>SLOVE</sub> | SCKx<br>SOTx |             | -           | 50   | -           | 30   | ns   |

| $SIN \rightarrow SCK \uparrow setup time$ | t <sub>IVSHE</sub> | SCKx<br>SINx | Slave mode  | 10          | -    | 10          | -    | ns   |

| $SCK \uparrow \rightarrow SIN$ hold time  | t <sub>SHIXE</sub> | SCKx<br>SINx |             | 20          | -    | 20          | -    | ns   |

| SCK falling time                          | tF                 | SCKx         | 1           | -           | 5    | -           | 5    | ns   |

| SCK rising time                           | tR                 | SCKx         |             | -           | 5    | -           | 5    | ns   |

#### Notes:

- ■The above characteristics apply to CLK synchronous mode.

- ■t<sub>CYCP</sub> indicates the APB bus clock cycle time.

About the APB bus number which Multi-function Serial is connected to, see "8. Block Diagram" in this datasheet.

- ■These characteristics only guarantee the same relocate port number. For example, the combination of SCKx\_0 and SOTx\_1 is not guaranteed.

- ■When the external load capacitance  $C_L = 30pF$ .

#### 12.6 USB characteristics

(Vcc = 2.7V to 5.5V, USBVcc = 3.0V to 3.6V, Vss = 0V, Ta = -40°C to + 105°C)

| Davamatan                      |                                | Symbol            | Pin<br>name   | Conditions                           | Value     |              | I Imit | D       |

|--------------------------------|--------------------------------|-------------------|---------------|--------------------------------------|-----------|--------------|--------|---------|

|                                | Parameter                      |                   |               |                                      | Min       | Max          | Unit   | Remarks |

| Input<br>charact-<br>eristics  | Input High level voltage       | $V_{IH}$          | UDPO,<br>UDMO | -                                    | 2.0       | USBVcc + 0.3 | V      | *1      |

|                                | Input Low level voltage        | V <sub>IL</sub>   |               | -                                    | Vss - 0.3 | 0.8          | ٧      | *1      |

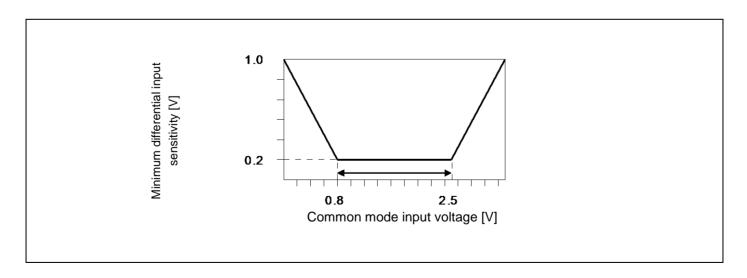

|                                | Differential input sensitivity | V <sub>DI</sub>   |               | -                                    | 0.2       | -            | ٧      | *2      |

|                                | Different common mode range    | V <sub>CM</sub>   |               | -                                    | 0.8       | 2.5          | ٧      | *2      |

| Output<br>charact-<br>eristics | Output High level voltage      | V <sub>ОН</sub>   |               | External pull-down resistance = 15kΩ | 2.8       | 3.6          | V      | *3      |

|                                | Output Low level voltage       | V <sub>OL</sub>   |               | External pull-up resistance = 1.5kΩ  | 0.0       | 0.3          | V      | *3      |

|                                | Crossover voltage              | $V_{CRS}$         | 1             | -                                    | 1.3       | 2.0          | V      | *4      |

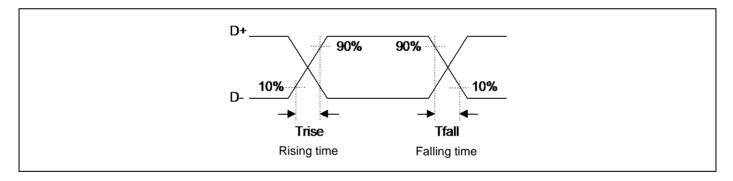

|                                | Rising time                    | t <sub>FR</sub>   |               | Full Speed                           | 4         | 20           | ns     | *5      |

|                                | Falling time                   | t <sub>FF</sub>   |               | Full Speed                           | 4         | 20           | ns     | *5      |

|                                | Rise/fall time matching        | t <sub>FRFM</sub> |               | Full Speed                           | 90        | 111.11       | %      | *5      |

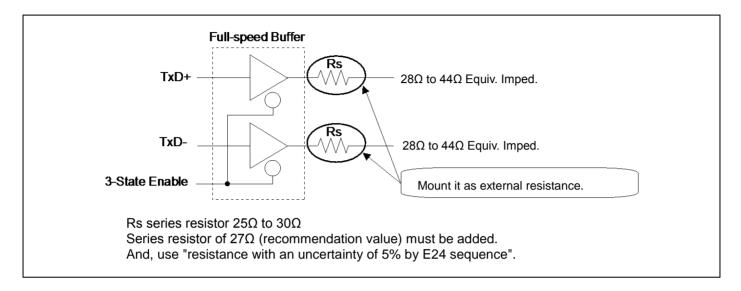

|                                | Output impedance               | $Z_{DRV}$         | 1             | Full Speed                           | 28        | 44           | Ω      | *6      |

|                                | Rising time                    | t <sub>LR</sub>   |               | Low Speed                            | 75        | 300          | ns     | *7      |

|                                | Falling time                   | t <sub>LF</sub>   |               | Low Speed                            | 75        | 300          | ns     | *7      |

|                                | Rise/fall time matching        | t <sub>LRFM</sub> |               | Low Speed                            | 80        | 125          | %      | *7      |

<sup>\*1:</sup> The switching threshold voltage of Single-End-Receiver of USB I/O buffer is set as within VIL (Max) = 0.8V,  $V_{IH}$  (Min) = 2.0 V (TTL input standard). There are some hystereses to lower noise sensitivity.

Differential-Receiver has 200 mV of differential input sensitivity when the differential data input is within 0.8 V to 2.5 V to the local ground reference level.

Above voltage range is the common mode input voltage range.

<sup>\*2:</sup> Use differential-Receiver to receive USB differential data signal.

\*6: USB Full-speed connection is performed via twist pair cable shield with  $90\Omega \pm 15\%$  characteristic impedance(Differential Mode). USB standard defines that output impedance of USB driver must be in range from  $28\Omega$ to  $44\Omega$ . So, discrete series resistor (Rs) addition is defined in order to satisfy the above definition and keep balance. When using this USB I/O, use it with  $25\Omega$  to  $30\Omega$  (recommendation value  $27\Omega$ ) series resistor Rs.

\*7: They indicate rising time (Trise) and falling time (Tfall) of the low-speed differential data signal. They are defined by the time between 10% and 90% of the output signal voltage.

See "Low-Speed Load (Compliance Load)" for conditions of external load.

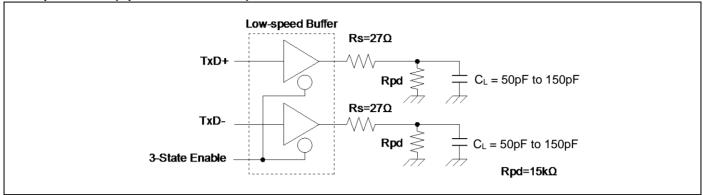

Low-Speed Load (Upstream Port Load) - Reference 1

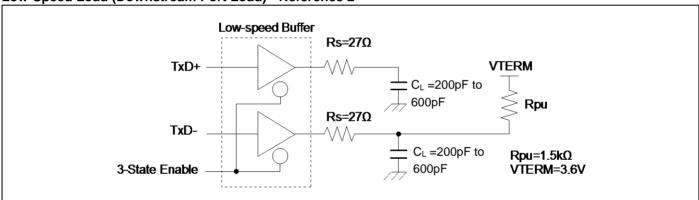

Low-Speed Load (Downstream Port Load) - Reference 2

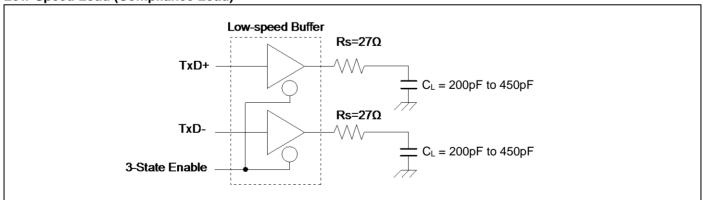

Low-Speed Load (Compliance Load)

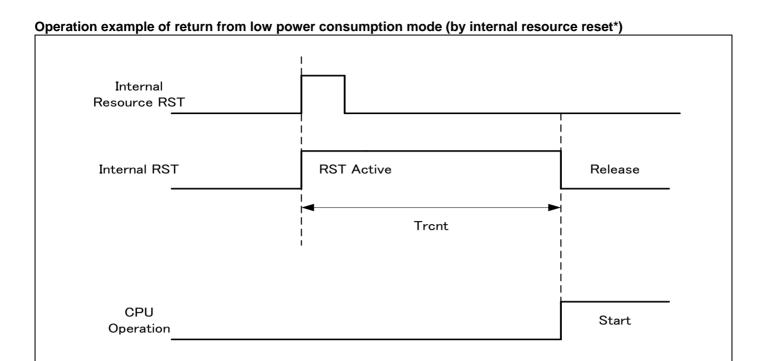

<sup>\*:</sup> Internal resource reset is not included in return factor by the kind of Low-Power consumption mode.

#### Notes:

- The return factor is different in each Low-Power consumption modes.

See "Chapter 6: Low Power Consumption Mode" and "Operations of Standby Modes" in FM3 Family Peripheral Manual.

- ■When interrupt recoveries, the operation mode that CPU recoveries depends on the state before the Low-Power consumption mode transition. See "Chapter 6: Low Power Consumption Mode" in "FM3 Family Peripheral Manual".

- ■The time during the power-on reset/low-voltage detection reset is excluded. See "12.4.7. Power-on Reset Timing in 12.4. AC Characteristics in 12Electrical Characteristics. Electrical Characteristics" for the detail on the time during the power-on reset/low-voltage detection reset.

- ■When in recovery from reset, CPU changes to the high-speed CR run mode. When using the main clock or the PLL clock, it is necessary to add the main clock oscillation stabilization wait time or the Main PLL clock stabilization wait time.

- ■The internal resource reset means the watchdog reset and the CSV reset.

## **Document History**

Document Title: MB9A310A Series 32-Bit ARM® Cortex®-M3, FM3 Microcontroller

Document Number: 002-04674

| Revision | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                  |  |

|----------|---------|--------------------|--------------------|--------------------------------------------------------------------------------------------------------|--|

| **       | -       | AKIH               | 12/16/2014         | Migrated to Cypress and assigned document number 002-04674.  No change to document contents or format. |  |

| *A       | 5198894 | AKIH               | 04/06/2016         | Updated to Cypress format.                                                                             |  |