# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4F                                                         |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 112MHz                                                                   |

| Connectivity               | CANbus, FlexIO, I <sup>2</sup> C, LINbus, SPI, UART/USART                |

| Peripherals                | POR, PWM, WDT                                                            |

| Number of I/O              | 89                                                                       |

| Program Memory Size        | 256KB (256K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 4K x 8                                                                   |

| RAM Size                   | 32K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| Data Converters            | A/D 16x12b SAR; D/A1x8b                                                  |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 100-LQFP                                                                 |

| Supplier Device Package    | 100-LQFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/fs32k142uat0vllt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **3** Ordering information

## 3.1 Selecting orderable part number

Not all part number combinations are available. See the attachment *S32K1xx\_Orderable\_Part\_Number\_List.xlsx* attached with the Datasheet for a list of standard orderable part numbers.

# 4 General

## 4.1 Absolute maximum ratings

### NOTE

- Functional operating conditions appear in the DC electrical characteristics. Absolute maximum ratings are stress ratings only, and functional operation at the maximum values is not guaranteed. See footnotes in the following table for specific conditions.

- Stress beyond the listed maximum values may affect device reliability or cause permanent damage to the device.

- All the limits defined in the datasheet specification must be honored together and any violation to any one or more will not guarantee desired operation.

- Unless otherwise specified, all maximum and minimum values in the datasheet are across process, voltage, and temperature.

| Symbol                             | Parameter                                                                              | Conditions <sup>1</sup> | Min       | Max              | Unit |

|------------------------------------|----------------------------------------------------------------------------------------|-------------------------|-----------|------------------|------|

| V <sub>DD</sub> <sup>2</sup>       | 2.7 V - 5. 5V input supply voltage                                                     | —                       | -0.3      | 5.8 <sup>3</sup> | V    |

| V <sub>REFH</sub>                  | 3.3 V / 5.0 V ADC high reference voltage                                               |                         | -0.3      | 5.8 <sup>3</sup> | V    |

| I <sub>INJPAD_DC_ABS</sub> 4       | Continuous DC input current (positive / negative) that can be injected into an I/O pin | _                       | -3        | +3               | mA   |

| V <sub>IN_DC</sub>                 | Continuous DC Voltage on any I/O pin with respect to $\rm V_{SS}$                      |                         | -0.8      | 5.8 <sup>5</sup> | V    |

| INJSUM_DC_ABS                      | Sum of absolute value of injected currents on all the pins (Continuous DC limit)       | —                       | —         | 30               | mA   |

| T <sub>ramp</sub> <sup>6</sup>     | ECU supply ramp rate                                                                   | —                       | 0.5 V/min | 500 V/ms         | —    |

| T <sub>ramp_MCU</sub> <sup>7</sup> | MCU supply ramp rate                                                                   |                         | 0.5 V/min | 100 V/ms         | —    |

| T <sub>A</sub> <sup>8</sup>        | Ambient temperature                                                                    | —                       | -40       | 125              | °C   |

| T <sub>STG</sub>                   | Storage temperature                                                                    | —                       | -55       | 165              | °C   |

| V <sub>IN_TRANSIENT</sub>          | Transient overshoot voltage allowed on I/O pin beyond $V_{IN\_DC\ limit}$              |                         |           | 6.8 <sup>9</sup> | V    |

#### Table 1. Absolute maximum ratings

1. All voltages are referred to  $V_{\text{SS}}$  unless otherwise specified.

- As V<sub>DD</sub> varies between the minimum value and the absolute maximum value the analog characteristics of the I/O and the ADC will both change. See section I/O parameters and ADC electrical specifications respectively for details.

- 3. 60 s lifetime No restrictions i.e. The part can switch.

10 hours lifetime - Device in reset i.e. The part cannot switch.

#### Table 4. Supplies decoupling capacitors 1, 2

| Symbol                                                      | Description                               | Min. <sup>3</sup> | Тур. | Max. | Unit |

|-------------------------------------------------------------|-------------------------------------------|-------------------|------|------|------|

| C <sub>REF</sub> <sup>, 4</sup> , <sup>5</sup>              | ADC reference high decoupling capacitance | 70                | 100  |      | nF   |

| C <sub>DEC</sub> <sup>5</sup> , <sup>6</sup> , <sup>7</sup> | Recommended decoupling capacitance        | 70                | 100  |      | nF   |

V<sub>DD</sub> and V<sub>DDA</sub> must be shorted to a common source on PCB. The differential voltage between V<sub>DD</sub> and V<sub>DDA</sub> is for RF-AC only. Appropriate decoupling capacitors to be used to filter noise on the supplies. See application note AN5032 for reference supply design for SAR ADC. All V<sub>SS</sub> pins should be connected to common ground at the PCB level.

2. All decoupling capacitors must be low ESR ceramic capacitors (for example X7R type).

3. Minimum recommendation is after considering component aging and tolerance.

4. For improved performance, it is recommended to use 10 µF, 0.1 µF and 1 nF capacitors in parallel.

5. All decoupling capacitors should be placed as close as possible to the corresponding supply and ground pins.

6. Contact your local Field Applications Engineer for details on best analog routing practices.

7. The filtering used for decoupling the device supplies must comply with the following best practices rules:

• The protection/decoupling capacitors must be on the path of the trace connected to that component.

• No trace exceeding 1 mm from the protection to the trace or to the ground.

• The protection/decoupling capacitors must be as close as possible to the input pin of the device (maximum 2 mm).

• The ground of the protection is connected as short as possible to the ground plane under the integrated circuit.

| Symbol                | Description                           | Min. | Тур.  | Max. | Unit | Notes |

|-----------------------|---------------------------------------|------|-------|------|------|-------|

| V <sub>LVW</sub>      | Falling low-voltage warning threshold | 4.19 | 4.305 | 4.5  | V    |       |

| V <sub>LVW_HYST</sub> | LVW hysteresis                        | —    | 75    | —    | mV   | 1     |

| V <sub>BG</sub>       | Bandgap voltage reference             | 0.97 | 1.00  | 1.03 | V    |       |

Table 5. V<sub>DD</sub> supply LVR, LVD and POR operating requirements (continued)

1. Rising threshold is the sum of falling threshold and hysteresis voltage.

## 4.6 Power mode transition operating behaviors

All specifications in the following table assume this clock configuration:

- RUN Mode:

- Clock source: FIRC

- SYS\_CLK/CORE\_CLK = 48 MHz

- $BUS_CLK = 48 MHz$

- FLASH\_CLK = 24 MHz

- HSRUN Mode:

- Clock source: SPLL

- SYS\_CLK/CORE\_CLK = 112 MHz

- BUS\_CLK = 56 MHz

- FLASH\_CLK = 28 MHz

- VLPR Mode:

- Clock source: SIRC

- SYS\_CLK/CORE\_CLK = 4 MHz

- $BUS_CLK = 4 MHz$

- FLASH\_CLK = 1 MHz

- STOP1/STOP2 Mode:

- Clock source: FIRC

- SYS\_CLK/CORE\_CLK = 48 MHz

- $BUS\_CLK = 48 MHz$

- FLASH\_CLK = 24 MHz

- VLPS Mode: All clock sources disabled <sup>1</sup>

#### Table 6. Power mode transition operating behaviors

| Symbol           | Description                                                                                                                                                       | Min. | Тур. | Max. | Unit |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| t <sub>POR</sub> | After a POR event, amount of time from the point $V_{DD}$ reaches 2.7 V to execution of the first instruction across the operating temperature range of the chip. | —    | 325  | _    | μs   |

Table continues on the next page...

- 1. For S32K11x FIRC/SOSC

- For S32K14x FIRC/SOSC/SPLL

S32K1xx Data Sheet, Rev. 8, 06/2018

The following table shows the power consumption targets for S32K148 in various mode of operations measure at 3.3 V.

| Chip/Device | Ambient             |     | RUN@80                           | MHz (mA)                               | HSRUN@112 MHz (mA) <sup>1</sup>  |                                        |  |

|-------------|---------------------|-----|----------------------------------|----------------------------------------|----------------------------------|----------------------------------------|--|

|             | Temperature<br>(°C) |     | Peripherals<br>enabled +<br>QSPI | Peripherals<br>enabled +<br>ENET + SAI | Peripherals<br>enabled +<br>QSPI | Peripherals<br>enabled +<br>ENET + SAI |  |

| S32K148     | 25                  | Тур | 67.3                             | 79.1                                   | 89.8                             | 105.5                                  |  |

|             | 85                  | Тур | 67.4                             | 79.2                                   | 95.6                             | 105.9                                  |  |

|             |                     | Max | 82.5                             | 88.2                                   | 109.7                            | 117.4                                  |  |

|             | 105                 | Тур | 68.0                             | 79.8                                   | 96.6                             | 106.7                                  |  |

|             |                     | Max | 80.3                             | 89.1                                   | 109.0                            | 119.0                                  |  |

|             | 125                 | Max | 83.5                             | 94.7                                   | N                                | İA                                     |  |

Table 9.Power consumption at 3.3 V

1. HSRUN mode must not be used at 125°C. Max ambient temperature for HSRUN mode is 105°C.

# 4.8 ESD handling ratings

| Symbol           | Description                                           | Min.   | Max. | Unit | Notes |

|------------------|-------------------------------------------------------|--------|------|------|-------|

| V <sub>HBM</sub> | Electrostatic discharge voltage, human body model     | - 4000 | 4000 | V    | 1     |

| V <sub>CDM</sub> | Electrostatic discharge voltage, charged-device model |        |      |      | 2     |

|                  | All pins except the corner pins                       | - 500  | 500  | V    |       |

|                  | Corner pins only                                      | - 750  | 750  | V    |       |

| I <sub>LAT</sub> | Latch-up current at ambient temperature of 125 °C     | - 100  | 100  | mA   | 3     |

1. Determined according to JEDEC Standard JESD22-A114, *Electrostatic Discharge (ESD) Sensitivity Testing Human Body Model (HBM)*.

2. Determined according to JEDEC Standard JESD22-C101, Field-Induced Charged-Device Model Test Method for Electrostatic-Discharge-Withstand Thresholds of Microelectronic Components.

3. Determined according to JEDEC Standard JESD78, IC Latch-Up Test.

# 4.9 EMC radiated emissions operating behaviors

EMC measurements to IC-level IEC standards are available from NXP on request.

|                       | Table 18.                                    | External S | ystem Osc | illator frequ | lency spec | ifications |         |      |        | Clock    |

|-----------------------|----------------------------------------------|------------|-----------|---------------|------------|------------|---------|------|--------|----------|

| Symbol                | Description                                  | м          | in.       | Тур.          |            | Max.       |         | Unit | Notes  | ck inte  |

|                       |                                              | S32K14x    | S32K11x   | S32K14x       | S32K11x    | S32K14x    | S32K11x | 1    |        | <b>_</b> |

| f <sub>osc_hi</sub>   | Oscillator crystal or resonator<br>frequency | 4          |           |               |            | 40         |         | MHz  |        | face mo  |

| f <sub>ec_extal</sub> | Input clock frequency (external clock mode)  | _          |           |               | 50         | 48         | MHz     | 1    | odules |          |

| t <sub>dc_extal</sub> | Input clock duty cycle (external clock mode) | 4          | 8         | 50            |            | 52         |         | %    | 1      |          |

| t <sub>cst</sub>      | Crystal Start-up Time                        |            |           |               |            |            |         |      |        |          |

|                       | 8 MHz low-gain mode (HGO=0)                  | -          | _         | 1.            | 5          | -          | _       | ms   | 2      |          |

|                       | 8 MHz high-gain mode (HGO=1)                 | -          | - 2.5     |               | -          | _          |         |      |        |          |

|                       | 40 MHz low-gain mode (HGO=0)                 | -          | _         | 2             | 2          | -          | _       | 1    |        |          |

|                       | 40 MHz high-gain mode (HGO=1)                | -          | _         | 2             | 2 —        |            |         |      |        |          |

### Table 18. External System Oscillator frequency specifications

Frequencies below 40 MHz can be used for degraded duty cycle upto 40-60% Proper PC board layout procedures must be followed to achieve specifications. 1.

2.

| Symbol                     | Description <sup>1</sup>                                              |                                                                        | S32 | K142                                | S3  | 2K144                               | S32 | K146                                | S32 | K148                                |      |       |

|----------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------|-----|-------------------------------------|-----|-------------------------------------|-----|-------------------------------------|-----|-------------------------------------|------|-------|

|                            |                                                                       |                                                                        | Тур | Max                                 | Тур | Max                                 | Тур | Max                                 | Тур | Max                                 | Unit | Notes |

|                            | setting (32-bit<br>write complete,<br>ready for next<br>32-bit write) | Last (Nth)<br>32-bit write<br>(time for<br>write only,<br>not cleanup) | 200 | 550                                 | 200 | 550                                 | 200 | 550                                 | 200 | 550                                 |      |       |

| t <sub>quickwr</sub> Clnup | Quick Write<br>Cleanup<br>execution time                              |                                                                        | —   | (# of<br>Quick<br>Writes<br>) * 2.0 |     | (# of<br>Quick<br>Writes )<br>* 2.0 |     | (# of<br>Quick<br>Writes<br>) * 2.0 |     | (# of<br>Quick<br>Writes<br>) * 2.0 | ms   | 7     |

Table 23. Flash command timing specifications for S32K14x (continued)

- 1. All command times assumes 25 MHz or greater flash clock frequency (for synchronization time between internal/external clocks).

- 2. Maximum times for erase parameters based on expectations at cycling end-of-life.

- For all EEPROM Emulation terms, the specified timing shown assumes previous record cleanup has occurred. This may be verified by executing FCCOB Command 0x77, and checking FCCOB number 5 contents show 0x00 - No EEPROM issues detected.

- 4. 1st time EERAM writes after a Reset or SETRAM may incur additional overhead for EEE cleanup, resulting in up to 2× the times shown.

- 5. Only after the Nth write completes will any data be valid. Emulated EEPROM record scheme cleanup overhead may occur after this point even after a brownout or reset. If power on reset occurs before the Nth write completes, the last valid record set will still be valid and the new records will be discarded.

- 6. Quick Write times may take up to 550 µs, as additional cleanup may occur when crossing sector boundaries.

- 7. Time for emulated EEPROM record scheme overhead cleanup. Automatically done after last (Nth) write completes, assuming still powered. Or via SETRAM cleanup execution command is requested at a later point.

#### Table 24. Flash command timing specifications for S32K11x

| Symbol              | Descripti                        | on <sup>1</sup> | S32 | 2K116 | S   | 32K118 |      |       |

|---------------------|----------------------------------|-----------------|-----|-------|-----|--------|------|-------|

|                     |                                  |                 | Тур | Max   | Тур | Max    | Unit | Notes |

| t <sub>rd1blk</sub> | Read 1 Block execution           | 32 KB flash     | —   | 0.36  | —   | 0.36   | ms   |       |

|                     | time                             | 64 KB flash     | —   | —     | —   | _      |      |       |

|                     |                                  | 128 KB flash    | —   | 1.2   | —   | —      |      |       |

|                     |                                  | 256 KB flash    | —   | —     | —   | 2      |      |       |

|                     |                                  | 512 KB flash    | _   | —     | —   | _      |      |       |

| t <sub>rd1sec</sub> | Read 1 Section                   | 2 KB flash      |     | 75    | —   | 75     | μs   |       |

|                     | execution time                   | 4 KB flash      | —   | 100   | —   | 100    |      |       |

| t <sub>pgmchk</sub> | Program Check<br>execution time  | —               | —   | 100   | -   | 100    | μs   |       |

| t <sub>pgm8</sub>   | Program Phrase<br>execution time | -               | 90  | 225   | 90  | 225    | μs   |       |

| t <sub>ersblk</sub> | Erase Flash Block                | 32 KB flash     | 15  | 300   | 15  | 300    | ms   | 2     |

|                     | execution time                   | 64 KB flash     | —   | —     | —   | _      |      |       |

|                     |                                  | 128 KB flash    | 120 | 1100  | —   | —      |      |       |

|                     |                                  | 256 KB flash    | _   | —     | 250 | 2125   |      |       |

|                     |                                  | 512 KB flash    | _   | —     | —   | —      |      |       |

Table continues on the next page ...

| Symbol                    | Description                                                                                         | Description <sup>1</sup>                                            |     |                                     | s   | 32K118                        |      |                  |

|---------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----|-------------------------------------|-----|-------------------------------|------|------------------|

|                           |                                                                                                     |                                                                     | Тур | Max                                 | Тур | Max                           | Unit | Notes            |

| t <sub>eewr32b</sub>      | 32-bit write to FlexRAM<br>execution time                                                           | 32 KB EEPROM<br>backup                                              | 630 | 2000                                | 630 | 2000                          | μs   | 3 <sup>,</sup> 4 |

|                           |                                                                                                     | 48 KB EEPROM<br>backup                                              | -   | —                                   | —   | —                             |      |                  |

|                           |                                                                                                     | 64 KB EEPROM<br>backup                                              | -   | —                                   | —   | —                             |      |                  |

| t <sub>quickwr</sub>      | 32-bit Quick Write                                                                                  | 1st 32-bit write                                                    | 200 | 550                                 | 200 | 550                           | μs   | 4.2.6            |

| e<br>f<br>t<br>s<br>c     | execution time: Time<br>from CCIF clearing (start<br>the write) until CCIF<br>setting (32-bit write | 2nd through Next<br>to Last (Nth-1)<br>32-bit write                 | 150 | 550                                 | 150 | 550                           |      |                  |

|                           | complete, ready for next<br>32-bit write)                                                           | Last (Nth) 32-bit<br>write (time for<br>write only, not<br>cleanup) | 200 | 550                                 | 200 | 550                           |      |                  |

| t <sub>quickwrClnup</sub> | Quick Write Cleanup<br>execution time                                                               | _                                                                   |     | (# of<br>Quick<br>Writes ) *<br>2.0 | —   | (# of Quick<br>Writes ) * 2.0 | ms   | 7                |

#### Table 24. Flash command timing specifications for S32K11x (continued)

- 1. All command times assume 25 MHz or greater flash clock frequency (for synchronization time between internal/external clocks).

- 2. Maximum times for erase parameters based on expectations at cycling end-of-life.

- For all EEPROM Emulation terms, the specified timing shown assumes previous record cleanup has occurred. This may be verified by executing FCCOB Command 0x77, and checking FCCOB number 5 contents show 0x00 - No EEPROM issues detected.

- 4. 1st time EERAM writes after a Reset or SETRAM may incur additional overhead for EEE cleanup, resulting in up to 2x the times shown.

- 5. Only after the Nth write completes will any data be valid. Emulated EEPROM record scheme cleanup overhead may occur after this point even after a brownout or reset. If power on reset occurs before the Nth write completes, the last valid record set will still be valid and the new records will be discarded.

- 6. Quick Write times may take up to 550 µs, as additional cleanup may occur when crossing sector boundaries.

- 7. Time for emulated EEPROM record scheme overhead cleanup. Automatically done after last (Nth) write completes, assuming still powered. Or via SETRAM cleanup execution command is requested at a later point.

### NOTE

Under certain circumstances FlexMEM maximum times may be exceeded. In this case the user or application may wait, or assert reset to the FTFC macro to stop the operation.

### 6.3.1.2 Reliability specifications

#### Table 25. NVM reliability specifications

| Symbol                               | Description                           | Min. | Тур. | Max. | Unit   | Notes |  |  |

|--------------------------------------|---------------------------------------|------|------|------|--------|-------|--|--|

| When using as Program and Data Flash |                                       |      |      |      |        |       |  |  |

| t <sub>nvmretp1k</sub>               | Data retention after up to 1 K cycles | 20   |      | _    | years  | 1     |  |  |

| n <sub>nvmcycp</sub>                 | Cycling endurance                     | 1 K  | _    | _    | cycles | 2, 3  |  |  |

Table continues on the next page...

S32K1xx Data Sheet, Rev. 8, 06/2018

| Table 25. | NVM reliability | y s | pecifications | (continued) | ) |

|-----------|-----------------|-----|---------------|-------------|---|

|-----------|-----------------|-----|---------------|-------------|---|

| Symbol                  | Description                                                             | Min.      | Тур.         | Max. | Unit   | Notes   |

|-------------------------|-------------------------------------------------------------------------|-----------|--------------|------|--------|---------|

|                         | When using FlexMemory feature : Fle                                     | xRAM as E | Emulated EEP | ROM  |        |         |

| t <sub>nvmretee</sub>   | Data retention                                                          | 5         | —            | _    | years  | 4       |

| n <sub>nvmwree16</sub>  | Write endurance <ul> <li>EEPROM backup to FlexRAM ratio = 16</li> </ul> | 100 K     | _            | _    | writes | 5, 6, 7 |

| n <sub>nvmwree256</sub> | <ul> <li>EEPROM backup to FlexRAM ratio = 256</li> </ul>                | 1.6 M     | —            | —    | writes |         |

- 1. Data retention period per block begins upon initial user factory programming or after each subsequent erase.

- 2. Program and Erase for PFlash and DFlash are supported across product temperature specification in Normal Mode (not supported in HSRUN mode).

- 3. Cycling endurance is per DFlash or PFlash Sector.

- 4. Data retention period per block begins upon initial user factory programming or after each subsequent erase. Background maintenance operations during normal FlexRAM usage extend effective data retention life beyond 5 years.

- FlexMemory write endurance specified for 16-bit and/or 32-bit writes to FlexRAM and is supported across product temperature specification in Normal Mode (not supported in HSRUN mode). Greater write endurance may be achieved with larger ratios of EEPROM backup to FlexRAM.

- 6. For usage of any EEE driver other than the FlexMemory feature, the endurance spec will fall back to the specified endurance value of the D-Flash specification (1K).

- 7. FlexMemory calculator tool is available at NXP web site for help in estimation of the maximum write endurance achievable at specific EEPROM/FlexRAM ratios. The "In Spec" portions of the online calculator refer to the NVM reliability specifications section of data sheet. This calculator is only applies to the FlexMemory feature.

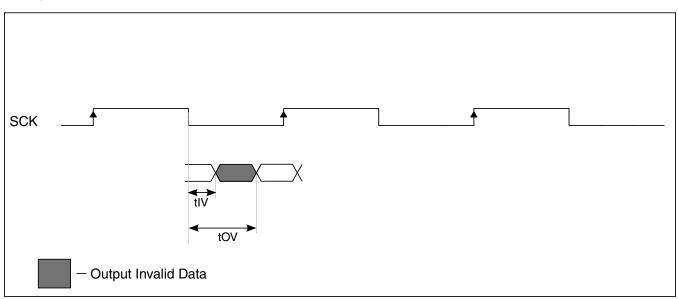

### 6.3.2 QuadSPI AC specifications

The following table describes the QuadSPI electrical characteristics.

- Measurements are with maximum output load of 25 pF, input transition of 1 ns and pad configured with fastest slew settings (DSE = 1'b1).

- I/O operating voltage ranges from 2.97 V to 3.6 V

- While doing the mode transition (RUN -> HSRUN or HSRUN -> RUN ), the interface should be OFF.

- Add 50 ohm series termination on board in QuadSPI SCK for Flash A to avoid loop back reflection when using in Internal DQS (PAD Loopback) mode.

- QuadSPI trace length should be 3 inches.

- For non-Quad mode of operation if external device doesn't have pull-up feature, external pull-up needs to be added at board level for non-used pads.

- With external pull-up, performance of the interface may degrade based on load associated with external pull-up.

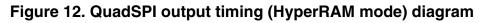

# 6.4 Analog modules

### 6.4.1 ADC electrical specifications

### 6.4.1.1 12-bit ADC operating conditions Table 27. 12-bit ADC operating conditions

| Symbol            | Description                           | Conditions                | Min.                                                                  | Typ. <sup>1</sup> | Max.                                                                  | Unit | Notes |

|-------------------|---------------------------------------|---------------------------|-----------------------------------------------------------------------|-------------------|-----------------------------------------------------------------------|------|-------|

| V <sub>REFH</sub> | ADC reference voltage high            |                           | See Voltage<br>and current<br>operating<br>requirements<br>for values | V <sub>DDA</sub>  | See Voltage<br>and current<br>operating<br>requirements<br>for values | V    | 2     |

| V <sub>REFL</sub> | ADC reference voltage low             |                           | See Voltage<br>and current<br>operating<br>requirements<br>for values | 0                 | See Voltage<br>and current<br>operating<br>requirements<br>for values | mV   | 2     |

| V <sub>ADIN</sub> | Input voltage                         |                           | V <sub>REFL</sub>                                                     | —                 | V <sub>REFH</sub>                                                     | V    |       |

| R <sub>S</sub>    | Source impedendance                   | f <sub>ADCK</sub> < 4 MHz | —                                                                     | —                 | 5                                                                     | kΩ   |       |

| R <sub>SW1</sub>  | Channel Selection Switch<br>Impedance |                           | —                                                                     | 0.75              | 1.2                                                                   | kΩ   |       |

| R <sub>AD</sub>   | Sampling Switch Impedance             |                           | —                                                                     | 2                 | 5                                                                     | kΩ   |       |

| C <sub>P1</sub>   | Pin Capacitance                       |                           | —                                                                     | 10                |                                                                       | pF   |       |

| C <sub>P2</sub>   | Analog Bus Capacitance                |                           | —                                                                     |                   | 4                                                                     | pF   |       |

| Cs                | Sampling capacitance                  |                           | —                                                                     | 4                 | 5                                                                     | pF   |       |

Table continues on the next page...

| Symbol            | Description                       | Conditions                                                                                                            | Min. | Typ. <sup>1</sup> | Max.  | Unit | Notes |

|-------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------|------|-------------------|-------|------|-------|

| <b>f</b> ADCK     | ADC conversion clock<br>frequency | Normal usage                                                                                                          | 2    | 40                | 50    | MHz  | 3, 4  |

| f <sub>CONV</sub> | ADC conversion frequency          | No ADC hardware<br>averaging. <sup>5</sup> Continuous<br>conversions enabled,<br>subsequent conversion<br>time        | 46.4 | 928               | 1160  | Ksps | 6, 7  |

|                   |                                   | ADC hardware averaging<br>set to 32. <sup>5</sup> Continuous<br>conversions enabled,<br>subsequent conversion<br>time | 1.45 | 29                | 36.25 | Ksps | 6, 7  |

Table 27. 12-bit ADC operating conditions (continued)

- 1. Typical values assume  $V_{DDA} = 5 V$ , Temp = 25 °C,  $f_{ADCK} = 40 \text{ MHz}$ ,  $R_{AS}=20 \Omega$ , and  $C_{AS}=10 \text{ nF}$  unless otherwise stated. Typical values are for reference only, and are not tested in production.

- For packages without dedicated V<sub>REFH</sub> and V<sub>REFL</sub> pins, V<sub>REFH</sub> is internally tied to V<sub>DDA</sub>, and V<sub>REFL</sub> is internally tied to V<sub>SS</sub>. To get maximum performance, reference supply quality should be better than SAR ADC. See application note AN5032 for details.

- 3. Clock and compare cycle need to be set according to the guidelines mentioned in the Reference Manual .

- 4. ADC conversion will become less reliable above maximum frequency.

- 5. When using ADC hardware averaging, see the *Reference Manual* to determine the most appropriate setting for AVGS.

- 6. Numbers based on the minimum sampling time of 275 ns.

- 7. For guidelines and examples of conversion rate calculation, see the Reference Manual section 'Calibration function'

Figure 13. ADC input impedance equivalency diagram

### 6.4.2 CMP with 8-bit DAC electrical specifications Table 31. Comparator with 8-bit DAC electrical specifications

| Symbol             | Description                                          | Min. | Тур.                 | Max.             | Unit |

|--------------------|------------------------------------------------------|------|----------------------|------------------|------|

| I <sub>DDHS</sub>  | Supply current, High-speed mode <sup>1</sup>         |      |                      |                  | μA   |

|                    | -40 - 125 ℃                                          | _    | 230                  | 300              |      |

| I <sub>DDLS</sub>  | Supply current, Low-speed mode <sup>1</sup>          |      |                      |                  | μA   |

|                    | -40 - 105 °C                                         | _    | 6                    | 11               |      |

|                    | -40 - 125 ℃                                          | -    | 6                    | 13               |      |

| V <sub>AIN</sub>   | Analog input voltage                                 | 0    | 0 - V <sub>DDA</sub> | V <sub>DDA</sub> | V    |

| V <sub>AIO</sub>   | Analog input offset voltage, High-speed mode         |      |                      |                  | mV   |

|                    | -40 - 125 °C                                         | -25  | ±1                   | 25               |      |

| V <sub>AIO</sub>   | Analog input offset voltage, Low-speed mode          |      |                      |                  | mV   |

|                    | -40 - 125 °C                                         | -40  | ±4                   | 40               |      |

| t <sub>DHSB</sub>  | Propagation delay, High-speed mode <sup>2</sup>      |      |                      |                  | ns   |

|                    | -40 - 105 °C                                         | _    | 35                   | 200              |      |

|                    | -40 - 125 °C                                         | _    | 35                   | 300              |      |

| t <sub>DLSB</sub>  | Propagation delay, Low-speed mode <sup>2</sup>       |      | -                    |                  | μs   |

|                    | -40 - 105 °C                                         | _    | 0.5                  | 2                |      |

|                    | -40 - 125 ℃                                          | _    | 0.5                  | 3                |      |

| t <sub>DHSS</sub>  | Propagation delay, High-speed mode <sup>3</sup>      |      |                      |                  | ns   |

|                    | -40 - 105 °C                                         | _    | 70                   | 400              |      |

|                    | -40 - 125 ℃                                          | _    | 70                   | 500              |      |

| t <sub>DLSS</sub>  | Propagation delay, Low-speed mode <sup>3</sup>       |      |                      |                  | μs   |

|                    | -40 - 105 °C                                         | _    | 1                    | 5                |      |

|                    | -40 - 125 ℃                                          | _    | 1                    | 5                |      |

| t <sub>IDHS</sub>  | Initialization delay, High-speed mode <sup>4</sup>   |      |                      |                  | μs   |

|                    | -40 - 125 °C                                         |      | 1.5                  | 3                |      |

| t <sub>IDLS</sub>  | Initialization delay, Low-speed mode <sup>4</sup>    |      |                      |                  | μs   |

|                    | -40 - 125 °C                                         | _    | 10                   | 30               |      |

| V <sub>HYST0</sub> | Analog comparator hysteresis, Hyst0                  |      |                      |                  | mV   |

|                    | -40 - 125 °C                                         | _    | 0                    | _                |      |

| V <sub>HYST1</sub> | Analog comparator hysteresis, Hyst1, High-speed mode |      | -                    |                  | mV   |

|                    | -40 - 125 °C                                         | _    | 19                   | 66               |      |

|                    | Analog comparator hysteresis, Hyst1, Low-speed mode  |      |                      |                  |      |

|                    | -40 - 125 °C                                         | _    | 15                   | 40               |      |

| V <sub>HYST2</sub> | Analog comparator hysteresis, Hyst2, High-speed mode |      |                      |                  | mV   |

|                    | -40 - 125 °C                                         | _    | 34                   | 133              |      |

Table continues on the next page ...

**ADC electrical specifications**

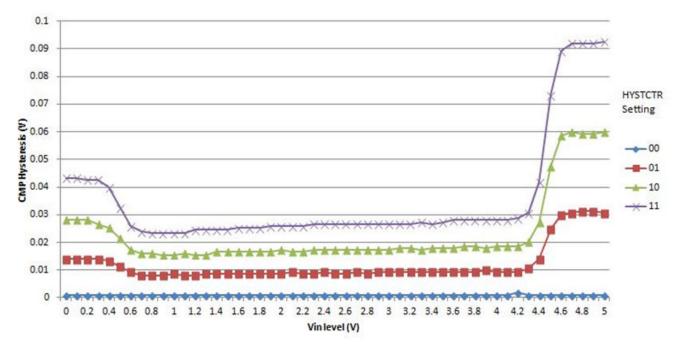

Figure 16. Typical hysteresis vs. Vin level (VDDA = 5 V, PMODE = 0)

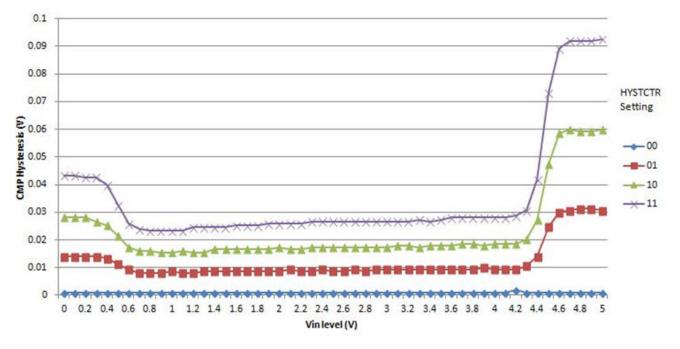

Figure 17. Typical hysteresis vs. Vin level (VDDA = 5 V, PMODE = 1)

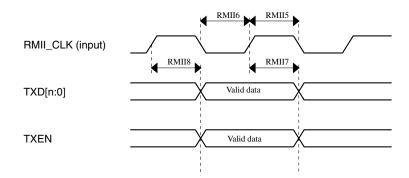

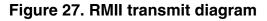

# Table 36. RMII signal switching specifications<br/>(continued)

| Symbol | Description                        | Min. | Max. | Unit |

|--------|------------------------------------|------|------|------|

| RMII7  | RMII_CLK to TXD[1:0], TXEN invalid | 2    | —    | ns   |

| RMII8  | RMII_CLK to TXD[1:0], TXEN valid   | —    | 15   | ns   |

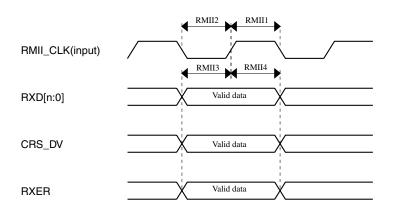

Figure 26. RMII receive diagram

The following table describes the MDIO electrical characteristics.

- Measurements are with maximum output load of 25 pF, input transition of 1 ns and pad configured with fastest slew settings (DSE = 1'b1).

- I/O operating voltage ranges from 2.97 V to 3.6 V

- While doing the mode transition (RUN -> HSRUN or HSRUN -> RUN ), the interface should be OFF.

- MDIO pin must have external Pull-up.

| Table 37. | MDIO | timing | specifications |

|-----------|------|--------|----------------|

|-----------|------|--------|----------------|

| Symbol | Description         | Min. | Max. | Unit |

|--------|---------------------|------|------|------|

| —      | MDC Clock Frequency | _    | 2.5  | MHz  |

Table continues on the next page...

S32K1xx Data Sheet, Rev. 8, 06/2018

| Symbol | Description                                        |          | Run      | Mode     |          |          | HSRU     | N Mode   |          |          | VLPR     | Mode     |          | Uni |

|--------|----------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|-----|

|        |                                                    | 5.0      | V IO     | 3.3      | V 10     | 5.0      | V IO     | 3.3      | V IO     | 5.0      | V IO     | 3.3      | V IO     | 1   |

|        |                                                    | Min.     | Max.     | 1   |

| S1     | SWD_CLK frequency of<br>operation                  | -        | 25       | -        | 25       | -        | 25       | -        | 25       | -        | 10       | -        | 10       | MHz |

| S2     | SWD_CLK cycle period                               | 1/S1     | -        | ns  |

| S3     | SWD_CLK clock pulse width                          | S2/2 - 5 | S2/2 + 5 | ns  |

| S4     | SWD_CLK rise and fall times                        | -        | 1        | -        | 1        | -        | 1        | -        | 1        | -        | 1        | -        | 1        | ns  |

| S9     | SWD_DIO input data setup time to SWD_CLK rise      | 4        | -        | 4        | -        | 4        | -        | 4        | -        | 16       | -        | 16       | -        | ns  |

| S10    | SWD_DIO input data hold time<br>after SWD_CLK rise | 3        | -        | 3        | -        | 3        | -        | 3        | -        | 10       | -        | 10       | -        | ns  |

| S11    | SWD_CLK high to SWD_DIO data valid                 | -        | 28       | -        | 38       | -        | 28       | -        | 38       | -        | 70       | -        | 77       | ns  |

| S12    | SWD_CLK high to SWD_DIO<br>high-Z                  | -        | 28       | -        | 38       | -        | 28       | -        | 38       | -        | 70       | -        | 77       | ns  |

| S13    | SWD_CLK high to SWD_DIO data invalid               | 0        | -        | 0        | -        | 0        | -        | 0        | -        | 0        | -        | 0        | -        | ns  |

## Table 38. SWD electrical specifications

|                    | Symbol             | Description         | F     | RUN Mode | 9  | HSRU   | N Mode | VLPR<br>Mode | Unit |

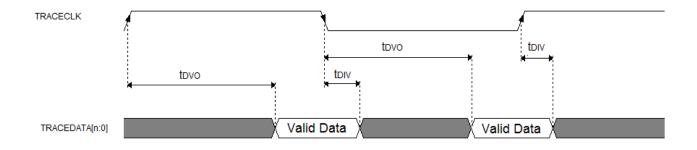

|--------------------|--------------------|---------------------|-------|----------|----|--------|--------|--------------|------|

|                    | f <sub>TRACE</sub> | Max Trace frequency | 80    | 48       | 40 | 74.667 | 80     | 4            | MHz  |

| ads                | t <sub>DVO</sub>   | Data Output Valid   | 4     | 4        | 4  | 4      | 4      | 20           | ns   |

| Trace on fast pads | t <sub>DIV</sub>   | Data Output Invalid | -2    | -2       | -2 | -2     | -2     | -10          | ns   |

|                    | f <sub>TRACE</sub> | Max Trace frequency | 22.86 | 24       | 20 | 22.4   | 22.86  | 4            | MHz  |

| ads                | t <sub>DVO</sub>   | Data Output Valid   | 8     | 8        | 8  | 8      | 8      | 20           | ns   |

| Trace on slow pads | t <sub>DIV</sub>   | Data Output Invalid | -4    | -4       | -4 | -4     | -4     | -10          | ns   |

Table 39.

Trace specifications (continued)

# 6.6.3 JTAG electrical specifications

66

# Table 40. JTAG electrical specifications

| Symbol | Description                                           |        | Rur    | n Mode |        |        | HSRU   | N Mode |        |        | VLPR   | Mode   |        | Unit |

|--------|-------------------------------------------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------|

|        |                                                       | 5.     | 0 V IO | 3.3    | V IO   | 5.0    | V IO   | 3.3    | V IO   | 5.0    | V IO   | 3.3    | V IO   |      |

|        |                                                       | Min.   | Max.   |      |

| JI     | TCLK frequency of operation                           | •      | •      | •      | •      |        |        |        | •      | •      | •      | -      | •      | MHz  |

|        | Boundary Scan                                         | -      | 20     | -      | 20     | -      | 20     | -      | 20     | -      | 10     | -      | 10     | 1    |

|        | JTAG                                                  | -      | 20     | -      | 20     | -      | 20     | -      | 20     | -      | 10     | -      | 10     | 1    |

| J2     | TCLK cycle period                                     | 1/JI   | -      | ns   |

| JЗ     | TCLK clock pulse width                                |        |        | ·      | •      | •      |        |        | •      |        |        | 1      | ·      | ns   |

|        | Boundary Scan                                         | 5      | 5      | 2      | 5      | 5      | 5      | 5      | 5      | 5      | 5      | 5      | 5      | 1    |

|        | JTAG                                                  | J2/2 - | J2/2 + |      |

| J4     | TCLK rise and fall times                              | -      | 1      | -      | 1      | -      | 1      | -      | 1      | -      | 1      | -      | 1      | ns   |

| J5     | Boundary scan input data setup time to TCLK rise      | 5      | -      | 5      | -      | 5      | -      | 5      | -      | 15     | -      | 15     | -      | ns   |

| J6     | Boundary scan input data<br>hold time after TCLK rise | 5      | -      | 5      | -      | 5      | -      | 5      | -      | 8      | -      | 8      | -      | ns   |

| J7     | TCLK low to boundary scan output data valid           | -      | 28     | -      | 32     | -      | 28     | -      | 32     | -      | 80     | -      | 80     | ns   |

| J8     | TCLK low to boundary scan output data invalid         | 0      | -      | 0      | -      | 0      | -      | 0      | -      | 0      | -      | 0      | -      |      |

| J9     | TCLK low to boundary scan<br>output high-Z            | -      | 28     | -      | 32     | -      | 28     | -      | 32     | -      | 80     | -      | 80     | ns   |

| J10    | TMS, TDI input data setup time to TCLK rise           | 3      | -      | 3      | -      | 3      | -      | 3      | -      | 15     | -      | 15     | -      | ns   |

| J11    | TMS, TDI input data hold time after TCLK rise         | 2      | -      | 2      | -      | 2      | -      | 2      | -      | 8      | -      | 8      | -      | ns   |

| J12    | TCLK low to TDO data valid                            | -      | 28     | -      | 32     | -      | 28     | -      | 32     | -      | 80     | -      | 80     | ns   |

| J13    | TCLK low to TDO data invalid                          | 0      | -      | 0      | -      | 0      | -      | 0      | -      | 0      | -      | 0      | -      | ns   |

| J14    | TCLK low to TDO high-Z                                | -      | 28     | -      | 32     | -      | 28     | -      | 32     | -      | 80     | -      | 80     | ns   |

Debug modules

| Rev. No. | Date          | Substantial Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |               | <ul> <li>Updated values for V<sub>REFH</sub> and V<sub>REFL</sub> to add refernce to the section<br/>"voltage and current operating requirments" for Min and Max valaues</li> <li>Updated footnote to Typ.</li> <li>Removed footnote from RAS Analog source resistance</li> <li>Updated figure: ADC input impedance equivalency diagram</li> <li>In table: 12-bit ADC characteristics (2.7 V to 3 V) (V<sub>REFH</sub> = V<sub>DDA</sub>, V<sub>REFL</sub> =<br/>V<sub>SS</sub>)</li> <li>Removed rows for V<sub>TEMP_S</sub> and V<sub>TEMP25</sub></li> <li>Updated footnote to Typ.</li> <li>In table: 12-bit ADC characteristics (3 V to 5.5 V)(V<sub>REFH</sub> = V<sub>DDA</sub>, V<sub>REFL</sub> =<br/>V<sub>SS</sub>)</li> <li>Removed rows for V<sub>TEMP_S</sub> and V<sub>TEMP25</sub></li> <li>Updated footnote to Typ.</li> <li>In table: 12-bit ADC characteristics (3 V to 5.5 V)(V<sub>REFH</sub> = V<sub>DDA</sub>, V<sub>REFL</sub> =<br/>V<sub>SS</sub>)</li> <li>Removed rows for V<sub>TEMP_S</sub> and V<sub>TEMP25</sub></li> <li>Updated footnote to Typ.</li> <li>In table: Comparator with 8-bit DAC electrical specifications</li> <li>Updated Typ. of I<sub>DDLS</sub> Supply current, Low-speed mode</li> <li>Updated Typ. of I<sub>DDLS</sub> Propagation delay, Low-speed mode</li> <li>Updated Typ. of I<sub>DDLS</sub> Propagation delay, High-speed mode</li> <li>Updated Typ. of I<sub>DDAC</sub> Initialization and switching settling time</li> <li>Updated footnote</li> <li>Updated footnote</li> <li>Updated footnote</li> <li>Updated section: LENE Propagation delay</li> <li>Added section: SAI electrical specifications</li> <li>Added section: Clockout frequency</li> <li>Added section: Trace electrical specifications</li> <li>Updated table: Table 41 : Updated numbers for S32K142 and S32K148</li> <li>Updated able: Table 42 : Updated numbers for S32K148</li> <li>Updated Document number for 32-pin QFN in topic Obtaining package dimensions</li> </ul> |

| 3        | 14 March 2017 | <ul> <li>In Table 2 <ul> <li>Updated min. value of V<sub>DD_OFF</sub></li> <li>Added parameter I<sub>INJSUM_AF</sub></li> </ul> </li> <li>Updated Power mode transition operating behaviors</li> <li>Updated Power consumption</li> <li>Updated footnote to T<sub>SPLL_LOCK</sub> in SPLL electrical specifications</li> <li>In 12-bit ADC electrical characteristics <ul> <li>Updated table: 12-bit ADC characteristics (2.7 V to 3 V) (VREFH = VDDA, VREFL = VSS)</li> <li>Added typ. value to I<sub>DDA_ADC</sub>, TUE, DNL, and INL</li> <li>Added min. value to SMPLTS</li> <li>Removed footnote 'All the parameters in this table '</li> <li>Updated table: 12-bit ADC characteristics (3 V to 5.5 V) (VREFH = VDDA, VREFL = VSS)</li> <li>Added typ. value to I<sub>DDA_ADC</sub></li> <li>Updated table: 12-bit ADC characteristics (3 V to 5.5 V) (VREFH = VDDA, VREFL = VSS)</li> <li>Added typ. value to I<sub>DDA_ADC</sub></li> <li>Removed footnote 'All the parameters in this table '</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4        | 02 June 2017  | <ul> <li>In section: Block diagram, added block diagram for S32K11x series.</li> <li>Updated figure: S32K1xx product series comparison.</li> <li>In section: Selecting orderable part number, added reference to attachemen <i>S32K_Part_Numbers.xlsx</i>.</li> <li>In section: Ordering information <ul> <li>Updated figure: Ordering information.</li> </ul> </li> <li>In Table 1,</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

### Table 43. Revision History (continued)

Table continues on the next page...

| Rev. No. | Date        | Substantial Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |             | <ul> <li>Updated note 'All the limits defined'</li> <li>Updated parameter 'I<sub>INJPAD_DC_ABS</sub>', 'VIN_DC', I<sub>INJSUM_DC_ABS</sub>.</li> <li>In Table 2,</li> <li>Updated parameter I<sub>INJPAD_DC_OP</sub> and I<sub>INJSUM_DC_OP</sub>.</li> <li>In Table 5, updated TBDs for V<sub>LVR_HYST</sub>, V<sub>LVD_HYST</sub>, and V<sub>LVW_HYST</sub></li> <li>Added VLPR → VLPS</li> <li>Added VLPR → VLPR</li> <li>Updated TBDs for VLPS → Asynchronous DMA Wakeup, STOP1 → Asynchronous DMA Wakeup</li> <li>In Table 7, updated the specifications for S32K144.</li> <li>Updated specificatins for g<sub>mXOSC</sub>.</li> <li>In Table 15, removed C<sub>IN_A</sub>.</li> <li>In Table 17,</li> <li>Updated specifications for g<sub>mXOSC</sub>.</li> <li>Removed I<sub>DDOSC</sub></li> <li>In Table 20,</li> <li>Added parameter ΔF125.</li> <li>Removed I<sub>DDFIRC</sub></li> <li>In Table 21, removed L<sub>IPO</sub></li> <li>Updated TBDs for I<sub>DDA_ADC</sub> and TUE in Table 28</li> <li>Updated TBDs for I<sub>DDA_ADC</sub> and TUE in Table 29</li> <li>In section: 12-bit ADC operating conditions, updated TBDs for I<sub>DDA_ADC</sub> and TUE in Table 27.</li> <li>In section: 12-bit ADC operating conditions, updated Table 27.</li> <li>In section: 12-bit ADC operating conditions, added note 'For comparator IN signals adjacent'</li> </ul> |

| 5        | 06 Dec 2017 | <ul> <li>Removed S32K148 from 'Caution'</li> <li>Updated figure: S32K1xx product series comparison for <ul> <li>'EEPROM emulated by FlexRAM' of S32K148 (Added content to footnote)</li> <li>Added support for LIN protocol version 2.2 A</li> </ul> </li> <li>In Absolute maximum ratings : <ul> <li>Added note 'Unless otherwise '</li> <li>Added parameter 'Added note 'T<sub>ramp_MCU</sub>'</li> <li>Updated footnote for 'T<sub>ramp</sub>'</li> </ul> </li> <li>In Voltage and current operating requirements : <ul> <li>Added footnote 'V<sub>DD</sub> and V<sub>DDA</sub> must be shorted ' against parameter 'V<sub>DD</sub>-V<sub>DDA</sub>'</li> <li>Updated footnote 'V<sub>DD</sub> and V<sub>DDA</sub> must be shorted'</li> </ul> </li> <li>In Power and ground pins <ul> <li>Added diagrams for 32-QFN and 48-LQFP and footnote below the diagrams.</li> <li>Updated footnote 'V<sub>DD</sub> and V<sub>DDA</sub> must be shorted'</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                            |

### Table 43. Revision History (continued)

Table continues on the next page ...

| Table 43. Revision Histor | y (continued) |

|---------------------------|---------------|

|---------------------------|---------------|

| Rev. No. | Date         | Substantial Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |              | <ul> <li>Fixed the typo in R<sub>SW1</sub></li> <li>In LPSPI electrical specifications : <ul> <li>Updated t<sub>Lead</sub> and t<sub>Lag</sub></li> <li>Added footnote in Figure: LPSPI slave mode timing (CPHA = 0) and Figure: LPSPI slave mode timing (CPHA = 1)</li> </ul> </li> <li>In Thermal characteristics : <ul> <li>Updated the name of table: Thermal characteristics for 32-pin QFN and 48/64/100/144/176-pin LQFP package</li> <li>Deleted specs for R<sub>BJC</sub> for 32 QFN package</li> <li>Added 'R<sub>BJCBottom</sub>'</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 8        | 18 June 2018 | <ul> <li>In attachement 'S32K1xx Power_Modes _Configuration':</li> <li>Updated VLPR peripherals disabled and Peripherals Enabled use case #1, using 4 Mhz for System clock, 2 Mhz for bus clock, and 1Mhz for flash.</li> <li>Removed S32K116 from Notes</li> <li>In figure: S32K1xx product series comparison : <ul> <li>Added note 'Availability of peripherals depends on the pin availability'</li> <li>Updated 'Ambient Operation Temperature' row</li> <li>Updated 'System RAM (including FlexRAM and MTB)' row for S32K144, S32K146, and S32K148</li> </ul> </li> <li>In Ordering information : <ul> <li>Updated figure for 'Y: Optional feature'</li> <li>Updated footnote 3</li> </ul> </li> <li>In Power and ground pins : <ul> <li>In figure 'Power diagram', updtaed V<sub>Flash</sub> frequency to 3.3 V</li> </ul> </li> <li>In Power mode transition operating behaviors : <ul> <li>Updated footnote for 'VLPS Mode: All clock sources disabled'</li> </ul> </li> <li>In Power consumption : <ul> <li>Added IDDs for S32K116</li> <li>Added footnote 'Data collected using RAM' to VLPR 'Peripherals enabled use case 1'</li> <li>Updated VLPR 'Peripherals enabled' to 'Peripherals enabled use case 1'</li> <li>Updated VLPS Peripherals enabled at 25 °C/Typicals for S32K142 and S32K144 to 40 µA and 42 µA respectively</li> <li>Added table 'VLPS additional use-case power consumption at typical conditions'</li> <li>In DC electrical specifications at 3.3 V Range : <ul> <li>Updated naming conventions</li> <li>Added specs for GPIO-FAST pad</li> </ul> </li> <li>In AC electrical specifications at 5.0 V Range : <ul> <li>Updated naming conventions</li> <li>Added specs for GPIO-FAST pad</li> </ul> </li> <li>In AC electrical specifications at 5.V range : <ul> <li>Updated naming conventions</li> <li>Added specs for GPIO-FAST pad</li> </ul> </li> <li>In AC electrical specifications at 5.V range : <ul> <li>Updated naming conventions</li> <li>Added specs for GPIO-FAST pad</li> </ul> </li> <li>In AC electrical specifications at 5.V range : <ul> <li>Updated naming conventions</li></ul></li></ul></li></ul> |