#### NXP USA Inc. - FS32K144HAT0VLHT Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4F                                                         |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 80MHz                                                                    |

| Connectivity               | CANbus, FlexIO, I <sup>2</sup> C, LINbus, SPI, UART/USART                |

| Peripherals                | POR, PWM, WDT                                                            |

| Number of I/O              | 58                                                                       |

| Program Memory Size        | 512KB (512K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 4K x 8                                                                   |

| RAM Size                   | 64K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| Data Converters            | A/D 16x12b SAR; D/A1x8b                                                  |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-LQFP                                                                  |

| Supplier Device Package    | 64-LQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/fs32k144hat0vlht |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Feature comparison

### 2 Feature comparison

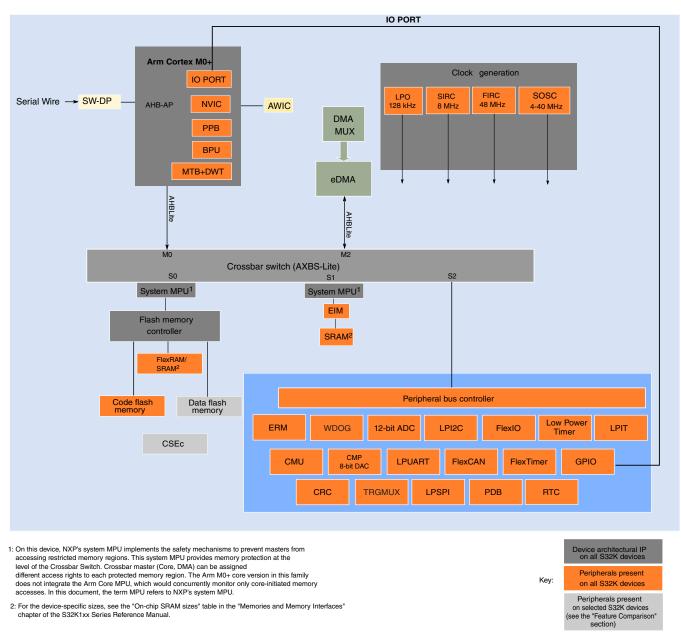

The following figure summarizes the memory, peripherals and packaging options for the S32K1xx devices. All devices which share a common package are pin-to-pin compatible.

### NOTE

Availability of peripherals depends on the pin availability in a particular package. For more information see *IO Signal*

# **3** Ordering information

# 3.1 Selecting orderable part number

Not all part number combinations are available. See the attachment *S32K1xx\_Orderable\_Part\_Number\_List.xlsx* attached with the Datasheet for a list of standard orderable part numbers.

- 5.  $V_{REFH}$  should always be equal to or less than  $V_{DDA}$  + 0.1 V and  $V_{DD}$  + 0.1 V

- 6. Open drain outputs must be pulled to  $V_{DD}$ .

- 7. When input pad voltage levels are close to  $V_{DD}$  or  $V_{SS}$ , practically no current injection is possible.

### 4.3 Thermal operating characteristics

# Table 3. Thermal operating characteristics for 64 LQFP, 100 LQFP, and 100 MAP-BGApackages.

| Symbol                      | Parameter                       |      | Value |                  | Unit |

|-----------------------------|---------------------------------|------|-------|------------------|------|

|                             |                                 | Min. | Тур.  | Max.             |      |

| T <sub>A C-Grade Part</sub> | Ambient temperature under bias  | -40  | —     | 85 <sup>1</sup>  | °C   |

| T <sub>J C-Grade Part</sub> | Junction temperature under bias | -40  | —     | 105 <sup>1</sup> | °C   |

| T <sub>A V-Grade Part</sub> | Ambient temperature under bias  | -40  | _     | 105 <sup>1</sup> | °C   |

| T <sub>J V-Grade Part</sub> | Junction temperature under bias | -40  | —     | 125 <sup>1</sup> | °C   |

| T <sub>A M-Grade Part</sub> | Ambient temperature under bias  | -40  | —     | 125 <sup>2</sup> | °C   |

| T <sub>J M-Grade Part</sub> | Junction temperature under bias | -40  | —     | 135 <sup>2</sup> | °C   |

1. Values mentioned are measured at  $\leq$  112 MHz in HSRUN mode.

2. Values mentioned are measured at  $\leq$  80 MHz in RUN mode.

### Table 7. Power consumption (Typicals unless stated otherwise) 1 (continued)

|             |                          |     |                                   | μΑ) <sup>2</sup>    | V                                 | LPR (m                                      | A)                                          | STOP1<br>(mA) | STOP2<br>(mA) |                      | l@48<br>(mA)        |                      | 64 MHz<br>nA)       |                      | 80 MHz<br>nA)       |                      | N@112<br>(mA) <sup>3</sup> |                               |

|-------------|--------------------------|-----|-----------------------------------|---------------------|-----------------------------------|---------------------------------------------|---------------------------------------------|---------------|---------------|----------------------|---------------------|----------------------|---------------------|----------------------|---------------------|----------------------|----------------------------|-------------------------------|

| Chip/Device | Ambient Temperature (°C) |     | Peripherals disabled <sup>5</sup> | Peripherals enabled | Peripherals disabled <sup>6</sup> | Peripherals enabled use case 1 <sup>6</sup> | Peripherals enabled use case 2 <sup>7</sup> |               |               | Peripherals disabled | Peripherals enabled        | IDD/MHz (µA/MHz) <sup>4</sup> |

|             |                          | Max | 1660                              | 1736                | 3.48                              | 3.55                                        | NA                                          | 14.5          | 15.6          | 34.8                 | 43.6                | 41.9                 | 53.9                | 48.7                 | 65.1                | 70.4                 | 96.1                       | 609                           |

|             | 105                      | Тур | 560                               | 577                 | 2.49                              | 2.54                                        | 4.03                                        | 10.9          | 11.9          | 29.8                 | 37.8                | 37.6                 | 47.5                | 45.2                 | 61.5                | 63.8                 | 89.1                       | 565                           |

|             |                          | Max | 2945                              | 2970                | 4.40                              | 4.47                                        | NA                                          | 18.0          | 19.0          | 38.4                 | 46.8                | 44.9                 | 55.3                | 51.6                 | 66.8                | 73.6                 | 97.4                       | 645                           |

|             | 125                      | Тур | NA                                | NA                  | NA                                | NA                                          | 4.85                                        | NA            | NA            | NA                   | NA                  | NA                   | NA                  | NA                   | NA                  | N                    | İA                         | NA                            |

|             |                          | Max | 3990                              | 4166                | 6.00                              | 6.08                                        | NA                                          | 23.4          | 24.5          | 44.3                 | 52.5                | 50.9                 | 61.3                | 57.5                 | 71.6                | N                    | IA                         | 719                           |

- Typical current numbers are indicative for typical silicon process and may vary based on the silicon distribution and user configuration. Typical conditions assumes

V<sub>DD</sub> = V<sub>DDA</sub> = V<sub>REFH</sub> = 5 V, temperature = 25 °C and typical silicon process unless otherwise stated. All output pins are floating and On-chip pulldown is enabled for

all unused input pins.

- 2. Current numbers are for reduced configuration and may vary based on user configuration and silicon process variation.

- 3. HSRUN mode must not be used at 125°C. Max ambient temperature for HSRUN mode is 105°C.

- 4. Values mentioned for S32K14x devices are measured at RUN@80 MHz with peripherals disabled and values mentioned for S32K11x devices are measured at RUN@48 MHz with peripherals disabled.

- 5. With PMC\_REGSC[CLKBIASDIS] set to 1. See Reference Manual for details.

- 6. Data collected using RAM

- 7. Numbers on limited samples size and data collected with Flash

- 8. The S32K148 data points assume that ENET/QuadSPI/SAI etc. are inactive.

# 5 I/O parameters

### 5.1 AC electrical characteristics

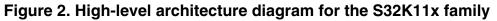

Unless otherwise specified, propagation delays are measured from the 50% to the 50% point, and rise and fall times are measured at the 20% and 80% points, as shown in the following figure.

The midpoint is  $V_{IL} + (V_{IH} - V_{IL})/2$ .

### Figure 7. Input signal measurement reference

## 5.2 General AC specifications

These general purpose specifications apply to all signals configured for GPIO, UART, and timers.

| Symbol | Description                                                                                                  | Min.                                        | Max. | Unit                | Notes |

|--------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------|------|---------------------|-------|

|        | GPIO pin interrupt pulse width (digital glitch filter disabled) — Synchronous path                           | 1.5                                         | —    | Bus clock<br>cycles | 1, 2  |

|        | GPIO pin interrupt pulse width (digital glitch filter disabled, passive filter disabled) — Asynchronous path | 50                                          | —    | ns                  | 3     |

| WFRST  | RESET input filtered pulse                                                                                   | —                                           | 10   | ns                  | 4     |

| WNFRST | RESET input not filtered pulse                                                                               | Maximum of<br>(100 ns, bus<br>clock period) | _    | ns                  | 5     |

Table 10. General switching specifications

- This is the minimum pulse width that is guaranteed to pass through the pin synchronization circuitry. Shorter pulses may or may not be recognized. In Stop and VLPS modes, the synchronizer is bypassed so shorter pulses can be recognized in that case.

- 2. The greater of synchronous and asynchronous timing must be met.

- 3. These pins do not have a passive filter on the inputs. This is the shortest pulse width that is guaranteed to be recognized.

- 4. Maximum length of RESET pulse which will be filtered by internal filter.

- 5. Minimum length of RESET pulse, guaranteed not to be filtered by the internal filter. This number depends on bus clock period also. For example, in VLPR mode bus clock is 4 MHz, which make clock period of 250 ns. In this case, minimum pulse width which will cause reset is 250 ns. For faster bus clock frequencies which have clock period less than 100 ns, the minimum pulse width not filtered will be 100 ns.

#### I/O parameters

- 6. Several I/O have both high drive and normal drive capability selected by the associated Portx\_PCRn[DSE] control bit. All other GPIOs are normal drive only. For details see IO Signal Description Input Multiplexing sheet(s) attached with the *Reference Manual*.

- 7. When using ENET and SAI on S32K148, the overall device limits associated with high drive pin configurations must be respected i.e. On 144-pin LQFP the general purpose pins: PTA10, PTD0, and PTE4 must be set to low drive.

- 8. Measured at input  $V = V_{SS}$

- 9. Measured at input  $V = V_{DD}$

# 5.4 DC electrical specifications at 5.0 V Range

| Symbol                                                                                                                                                                                                  | Parameter                                                                      |                           | Value                   |                        | Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Notes |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------|-------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|                                                                                                                                                                                                         |                                                                                | Min.                      | Тур.                    | Max.                   | Unit           V           V           V           MA           mA |       |

| V <sub>DD</sub>                                                                                                                                                                                         | I/O Supply Voltage                                                             | 4                         | _                       | 5.5                    | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

| V <sub>ih</sub>                                                                                                                                                                                         | Input Buffer High Voltage                                                      | 0.65 x<br>V <sub>DD</sub> | _                       | V <sub>DD</sub> + 0.3  | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1     |

| V <sub>il</sub>                                                                                                                                                                                         | Input Buffer Low Voltage                                                       | V <sub>SS</sub> – 0.3     | _                       | 0.35 x V <sub>DD</sub> | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2     |

| V <sub>hys</sub>                                                                                                                                                                                        | Input Buffer Hysteresis                                                        | 0.06 x<br>V <sub>DD</sub> | _                       | —                      | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

| loh <sub>GPIO</sub><br>loh <sub>GPIO-HD_DSE_0</sub>                                                                                                                                                     | I/O current source capability measured when pad $V_{oh}$ = ( $V_{DD}$ - 0.8 V) | 5                         | _                       | —                      | mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

| Iol <sub>GPIO</sub><br>Iol <sub>GPIO-HD_DSE_0</sub>                                                                                                                                                     | I/O current sink capability measured when pad $V_{\rm ol}{=}$ 0.8 V            | 5                         | _                       | —                      | mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

| Ioh <sub>GPIO-HD_DSE_1</sub>                                                                                                                                                                            | I/O current source capability measured when pad $V_{oh} = V_{DD} - 0.8 V$      | 20                        | _                       | —                      | mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3     |

| IOI <sub>GPIO-HD_DSE_1</sub>                                                                                                                                                                            | I/O current sink capability measured when pad $V_{ol} = 0.8 V$                 | 20                        | _                       | —                      | mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3     |

| Ioh <sub>GPIO-FAST_DSE_0</sub>                                                                                                                                                                          | I/O current sink capability measured when pad $V_{oh} = V_{DD} - 0.8 V$        | 14.0                      | —                       | —                      | mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4     |

| IOI <sub>GPIO-FAST_DSE_0</sub>                                                                                                                                                                          | I/O current sink capability measured when pad $V_{ol}$ = 0.8 V                 | 14.5                      | —                       | _                      | mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4     |

| loh <sub>GPIO-FAST_DSE_1</sub>                                                                                                                                                                          | I/O current sink capability measured when pad $V_{oh} = V_{DD} - 0.8 V$        | 21                        | —                       | —                      | mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4     |

| IOI <sub>GPIO-FAST_DSE_1</sub>                                                                                                                                                                          | I/O current sink capability measured when pad $V_{ol}$ = 0.8 V                 | 20.5                      | —                       | —                      | mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4     |

| IOHT                                                                                                                                                                                                    | Output high current total for all ports                                        | —                         |                         | 100                    | mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

| Vih<br>Vil<br>Vhys<br>IohgPIO<br>IohgPIO-HD_DSE_0<br>IolgPIO-HD_DSE_0<br>IohgPIO-HD_DSE_1<br>IohgPIO-FAST_DSE_0<br>IohgPIO-FAST_DSE_0<br>IohgPIO-FAST_DSE_1<br>IolgPIO-FAST_DSE_1<br>IOHT<br>IIN<br>IIN | Input leakage current (per pin) for full te                                    | mperature r               | ange at V <sub>DD</sub> | <sub>0</sub> = 5.5 V   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5     |

|                                                                                                                                                                                                         | All pins other than high drive port pins                                       |                           | 0.005                   | 0.5                    | μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

|                                                                                                                                                                                                         | High drive port pins                                                           |                           | 0.010                   | 0.5                    | μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

| R <sub>PU</sub>                                                                                                                                                                                         | Internal pullup resistors                                                      | 20                        |                         | 50                     | kΩ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6     |

| R <sub>PD</sub>                                                                                                                                                                                         | Internal pulldown resistors                                                    | 20                        |                         | 50                     | kΩ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7     |

Table 12. DC electrical specifications at 5.0 V Range

1. For reset pads, same V<sub>ih</sub> levels are applicable

2. For reset pads, same V<sub>il</sub> levels are applicable

- 3. The strong pad I/O pin is capable of switching a 50 pF load up to 40 MHz.

- 4. For refernce only. Run simulations with the IBIS model and custom board for accurate results.

| Symbol             | Description                      | Min. | Max.            | Unit |

|--------------------|----------------------------------|------|-----------------|------|

| f <sub>FLASH</sub> | Flash clock                      |      | 24              | MHz  |

|                    | Normal run mode (S32K14x series) | 3    | 1               |      |

| f <sub>SYS</sub>   | System and core clock            | _    | 80              | MHz  |

| f <sub>BUS</sub>   | Bus clock                        | _    | 40 <sup>4</sup> | MHz  |

| f <sub>FLASH</sub> | Flash clock                      | _    | 26.67           | MHz  |

|                    | VLPR mode <sup>5</sup>           |      |                 |      |

| f <sub>SYS</sub>   | System and core clock            |      | 4               | MHz  |

| f <sub>BUS</sub>   | Bus clock                        |      | 4               | MHz  |

| f <sub>FLASH</sub> | Flash clock                      | _    | 1               | MHz  |

| f <sub>ERCLK</sub> | External reference clock         | _    | 16              | MHz  |

1. Refer to the section Feature comparison for the availability of modes and other specifications.

- 2. Only available on some devices. See section Feature comparison.

- 3. With SPLL as system clock source.

- 4. 48 MHz when f<sub>SYS</sub> is 48 MHz

5. The frequency limitations in VLPR mode here override any frequency specification listed in the timing specification for any other module.

# 6 Peripheral operating requirements and behaviors

### 6.1 System modules

There are no electrical specifications necessary for the device's system modules.

### 6.2 Clock interface modules

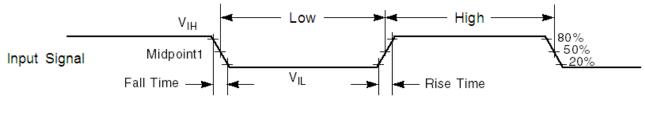

### 6.2.1 External System Oscillator electrical specifications

Figure 8. Oscillator connections scheme

| Table 17. External System Oscillator electrical specifications |

|----------------------------------------------------------------|

|----------------------------------------------------------------|

| Symbol                    | Description                                           | Min.                  | Тур. | Max.            | Unit | Notes |

|---------------------------|-------------------------------------------------------|-----------------------|------|-----------------|------|-------|

| <b>g</b> <sub>mXOSC</sub> | Crystal oscillator transconductance                   |                       |      |                 |      |       |

|                           | SCG_SOSCCFG[RANGE]=2'b10 for 4-8 MHz                  | 2.2                   | _    | 13.7            | mA/V |       |

|                           | SCG_SOSCCFG[RANGE]=2'b11 for 8-40 MHz                 | 16                    | _    | 47              | mA/V |       |

| V <sub>IL</sub>           | Input low voltage — EXTAL pin in external clock mode  | V <sub>SS</sub>       |      | 1.15            | V    |       |

| V <sub>IH</sub>           | Input high voltage — EXTAL pin in external clock mode | 0.7 * V <sub>DD</sub> | _    | V <sub>DD</sub> | V    |       |

| C <sub>1</sub>            | EXTAL load capacitance                                | _                     |      | _               |      | 1     |

| C <sub>2</sub>            | XTAL load capacitance                                 | _                     | _    | _               |      | 1     |

| R <sub>F</sub>            | Feedback resistor                                     |                       |      |                 |      | 2     |

|                           | Low-gain mode (HGO=0)                                 | _                     | _    | _               | MΩ   |       |

Table continues on the next page...

# 6.2.3 System Clock Generation (SCG) specifications

### 6.2.3.1 Fast internal RC Oscillator (FIRC) electrical specifications Table 19. Fast internal RC Oscillator electrical specifications

| Symbol                        | Parameter <sup>1</sup>                                               |      | Value |      | Unit               |

|-------------------------------|----------------------------------------------------------------------|------|-------|------|--------------------|

|                               |                                                                      | Min. | Тур.  | Max. |                    |

| F <sub>FIRC</sub>             | FIRC target frequency                                                | —    | 48    |      | MHz                |

| ΔF                            | Frequency deviation across process, voltage, and temperature < 105°C | —    | ±0.5  | ±1   | %F <sub>FIRC</sub> |

| ΔF125                         | Frequency deviation across process, voltage, and temperature < 125°C | —    | ±0.5  | ±1.1 | %F <sub>FIRC</sub> |

| T <sub>Startup</sub>          | Startup time                                                         |      | 3.4   | 5    | μs²                |

| T <sub>JIT</sub> , 3          | Cycle-to-Cycle jitter                                                | —    | 300   | 500  | ps                 |

| T <sub>JIT</sub> <sup>3</sup> | Long term jitter over 1000 cycles                                    | —    | 0.04  | 0.1  | %F <sub>FIRC</sub> |

1. With FIRC regulator enable

2. Startup time is defined as the time between clock enablement and clock availability for system use.

3. FIRC as system clock

### NOTE

Fast internal RC Oscillator is compliant with CAN and LIN standards.

### 6.2.3.2 Slow internal RC oscillator (SIRC) electrical specifications Table 20. Slow internal RC oscillator (SIRC) electrical specifications

| Symbol               | Parameter                                                                     |      | Value |      | Unit               |

|----------------------|-------------------------------------------------------------------------------|------|-------|------|--------------------|

|                      |                                                                               | Min. | Тур.  | Max. | 1                  |

| F <sub>SIRC</sub>    | SIRC target frequency                                                         | _    | 8     | —    | MHz                |

| ΔF                   | Frequency deviation across process, voltage, and temperature $< 105^{\circ}C$ | —    | —     | ±3   | %F <sub>SIRC</sub> |

| ΔF125                | Frequency deviation across process, voltage, and temperature < 125°C          | _    | _     | ±3.3 | %F <sub>SIRC</sub> |

| T <sub>Startup</sub> | Startup time                                                                  | _    | 9     | 12.5 | μs <sup>1</sup>    |

1. Startup time is defined as the time between clock enablement and clock availability for system use.

| Table 25. | NVM reliability | y s | pecifications | (continued) | ) |

|-----------|-----------------|-----|---------------|-------------|---|

|-----------|-----------------|-----|---------------|-------------|---|

| Symbol                  | Description                                              | Min.      | Тур.         | Max. | Unit   | Notes   |

|-------------------------|----------------------------------------------------------|-----------|--------------|------|--------|---------|

|                         | When using FlexMemory feature : Fle                      | xRAM as E | Emulated EEP | ROM  |        |         |

| t <sub>nvmretee</sub>   | Data retention                                           | 5         | —            | _    | years  | 4       |

| n <sub>nvmwree16</sub>  | Write endurance<br>• EEPROM backup to FlexRAM ratio = 16 |           | _            | _    | writes | 5, 6, 7 |

| n <sub>nvmwree256</sub> | <ul> <li>EEPROM backup to FlexRAM ratio = 256</li> </ul> | 1.6 M     | —            | —    | writes |         |

- 1. Data retention period per block begins upon initial user factory programming or after each subsequent erase.

- 2. Program and Erase for PFlash and DFlash are supported across product temperature specification in Normal Mode (not supported in HSRUN mode).

- 3. Cycling endurance is per DFlash or PFlash Sector.

- 4. Data retention period per block begins upon initial user factory programming or after each subsequent erase. Background maintenance operations during normal FlexRAM usage extend effective data retention life beyond 5 years.

- FlexMemory write endurance specified for 16-bit and/or 32-bit writes to FlexRAM and is supported across product temperature specification in Normal Mode (not supported in HSRUN mode). Greater write endurance may be achieved with larger ratios of EEPROM backup to FlexRAM.

- 6. For usage of any EEE driver other than the FlexMemory feature, the endurance spec will fall back to the specified endurance value of the D-Flash specification (1K).

- 7. FlexMemory calculator tool is available at NXP web site for help in estimation of the maximum write endurance achievable at specific EEPROM/FlexRAM ratios. The "In Spec" portions of the online calculator refer to the NVM reliability specifications section of data sheet. This calculator is only applies to the FlexMemory feature.

### 6.3.2 QuadSPI AC specifications

The following table describes the QuadSPI electrical characteristics.

- Measurements are with maximum output load of 25 pF, input transition of 1 ns and pad configured with fastest slew settings (DSE = 1'b1).

- I/O operating voltage ranges from 2.97 V to 3.6 V

- While doing the mode transition (RUN -> HSRUN or HSRUN -> RUN ), the interface should be OFF.

- Add 50 ohm series termination on board in QuadSPI SCK for Flash A to avoid loop back reflection when using in Internal DQS (PAD Loopback) mode.

- QuadSPI trace length should be 3 inches.

- For non-Quad mode of operation if external device doesn't have pull-up feature, external pull-up needs to be added at board level for non-used pads.

- With external pull-up, performance of the interface may degrade based on load associated with external pull-up.

| Symbol             | Description                                          | Min.  | Тур. | Max. | Unit             |

|--------------------|------------------------------------------------------|-------|------|------|------------------|

|                    | Analog comparator hysteresis, Hyst2, Low-speed mode  |       |      |      |                  |

|                    | -40 - 125 °C                                         | _     | 23   | 80   |                  |

| V <sub>HYST3</sub> | Analog comparator hysteresis, Hyst3, High-speed mode |       |      |      | mV               |

|                    | -40 - 125 °C                                         | _     | 46   | 200  |                  |

|                    | Analog comparator hysteresis, Hyst3, Low-speed mode  |       |      |      |                  |

|                    | -40 - 125 °C                                         | _     | 32   | 120  |                  |

| I <sub>DAC8b</sub> | 8-bit DAC current adder (enabled)                    |       |      |      |                  |

|                    | 3.3V Reference Voltage                               | _     | 6    | 9    | μA               |

|                    | 5V Reference Voltage                                 | _     | 10   | 16   | μA               |

| INL <sup>5</sup>   | 8-bit DAC integral non-linearity                     | -0.75 | —    | 0.75 | LSB <sup>6</sup> |

| DNL                | 8-bit DAC differential non-linearity                 | -0.5  | —    | 0.5  | LSB <sup>6</sup> |

| t <sub>DDAC</sub>  | AC Initialization and switching settling time        |       | —    | 30   | μs               |

Table 31. Comparator with 8-bit DAC electrical specifications (continued)

1. Difference at input > 200mV

2. Applied  $\pm$  (100 mV + V<sub>HYST0/1/2/3</sub>+ max. of V<sub>AIO</sub>) around switch point.

3. Applied ± (30 mV + 2 ×  $V_{HYST0/1/2/3}$ + max. of  $V_{AIO}$ ) around switch point.

4. Applied  $\pm$  (100 mV + V<sub>HYST0/1/2/3</sub>).

5. Calculation method used: Linear Regression Least Square Method

6. 1 LSB =  $V_{reference}/256$

### NOTE

For comparator IN signals adjacent to  $V_{DD}/V_{SS}$  or XTAL/ EXTAL or switching pins cross coupling may happen and hence hysteresis settings can be used to obtain the desired comparator performance. Additionally, an external capacitor (1nF) should be used to filter noise on input signal. Also, source drive should not be weak (Signal with < 50 K pull up/down is recommended).

### Table 32. LPSPI electrical specifications1

| Num | Symbol                         | Description                  | Conditions                            |                                       | Run  | Mode <sup>2</sup>                  |                    |                                    | HSRU               | N Mode <sup>2</sup>                |                  |                                    | VLPR | Mode                               |      | Uni |  |

|-----|--------------------------------|------------------------------|---------------------------------------|---------------------------------------|------|------------------------------------|--------------------|------------------------------------|--------------------|------------------------------------|------------------|------------------------------------|------|------------------------------------|------|-----|--|

|     |                                |                              |                                       | 5.0 V IO                              | V IO | 3.3 V IO                           | 5.0 V IO           | 3.3                                | 3 V IO             | 5.0 V IO                           | V IO             | 3.3                                | V 10 | 1                                  |      |     |  |

|     |                                |                              |                                       | Min.                                  | Max. | Min.                               | Max.               | Min.                               | Max.               | Min.                               | Max.             | Min.                               | Max. | Min.                               | Max. | 1   |  |

|     | f <sub>periph</sub> , 3, 4     | Peripheral                   | Slave                                 | -                                     | 40   | -                                  | 40                 | -                                  | 56                 | -                                  | 56               | -                                  | 4    | -                                  | 4    | MH  |  |

|     |                                | Frequency                    | Master                                | -                                     | 40   | -                                  | 40                 | -                                  | 56                 | -                                  | 56               | -                                  | 4    | -                                  | 4    | ]   |  |

|     |                                |                              | Master<br>Loopback <sup>5</sup>       | -                                     | 40   | -                                  | 48                 | -                                  | 48                 | -                                  | 48               | -                                  | 4    | -                                  | 4    |     |  |

|     |                                |                              | Master<br>Loopback(slow) <sup>6</sup> | -                                     | 48   | -                                  | 48                 | -                                  | 48                 | -                                  | 48               | -                                  | 4    | -                                  | 4    |     |  |

| 1   | f <sub>op</sub>                | Frequency of                 | Slave                                 | -                                     | 10   | -                                  | 10                 | -                                  | 14                 | -                                  | 14 <sup>7</sup>  | -                                  | 2    | -                                  | 2    | MH  |  |

|     |                                | operation                    | Master                                | -                                     | 10   | -                                  | 10                 | -                                  | 14                 | -                                  | 14 <sup>7</sup>  | -                                  | 2    | -                                  | 2    | 1   |  |

|     |                                |                              | Master<br>Loopback <sup>5</sup>       | -                                     | 20   | -                                  | 12                 | -                                  | 24                 | -                                  | 12               | -                                  | 2    | -                                  | 2    |     |  |

|     |                                |                              |                                       | Master<br>Loopback(slow) <sup>6</sup> | -    | 12                                 | -                  | 12                                 | -                  | 12                                 | -                | 12                                 | -    | 2                                  | -    | 2   |  |

| 2   | t <sub>SPSCK</sub>             | SPSCK SPSCK<br>period        | Slave                                 | 100                                   | -    | 100                                | -                  | 72                                 | -                  | 72                                 | -                | 500                                | -    | 500                                | -    | ns  |  |

|     |                                |                              | Master                                | 100                                   | -    | 100                                | -                  | 72                                 | -                  | 72                                 | -                | 500                                | -    | 500                                | -    |     |  |

|     |                                |                              | Master<br>Loopback <sup>5</sup>       | 50                                    | -    | 83                                 | -                  | 42                                 | -                  | 83                                 | -                | 500                                | -    | 500                                | -    |     |  |

|     |                                |                              | Master<br>Loopback(slow) <sup>6</sup> | 83                                    | -    | 83                                 | -                  | 83                                 | -                  | 83                                 | -                | 500                                | -    | 500                                | -    |     |  |

| 3   | t <sub>Lead</sub> <sup>8</sup> | Enable lead                  | Slave                                 | -                                     | -    | -                                  | -                  | -                                  | -                  | -                                  | -                | -                                  | -    | -                                  | -    | ns  |  |

|     |                                | time (PCS to<br>SPSCK delay) | Master                                |                                       | -    |                                    | -                  |                                    | -                  |                                    | -                |                                    | -    |                                    | -    |     |  |

|     |                                |                              |                                       | Master<br>Loopback <sup>5</sup>       | 1-25 |                                    | - <sup>-</sup> -25 |                                    | - <sup>-</sup> -25 |                                    | <sup>-</sup> -25 |                                    | -50  |                                    | -50  |     |  |

|     |                                |                              | Master<br>Loopback(slow) <sup>6</sup> | (PCSSCK+1)*t <sub>periph</sub> -25    |      | (PCSSCK+1)*t <sub>periph</sub> -25 |                    | (PCSSCK+1)*t <sub>periph</sub> -25 |                    | (PCSSCK+1)*t <sub>periph</sub> -25 |                  | (PCSSCK+1)*t <sub>periph</sub> -50 |      | (PCSSCK+1)*t <sub>periph</sub> -50 |      |     |  |

Table continues on the next page...

Communication modules

5

**Communication modules**

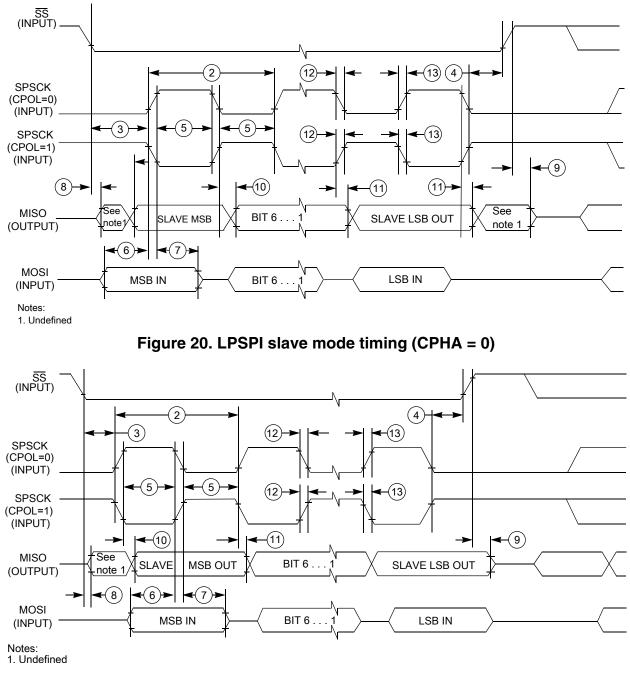

Figure 21. LPSPI slave mode timing (CPHA = 1)

# 6.5.3 LPI2C electrical specifications

See General AC specifications for LPI2C specifications.

For supported baud rate see section 'Chip-specific LPI2C information' of the *Reference Manual*.

#### **Communication modules**

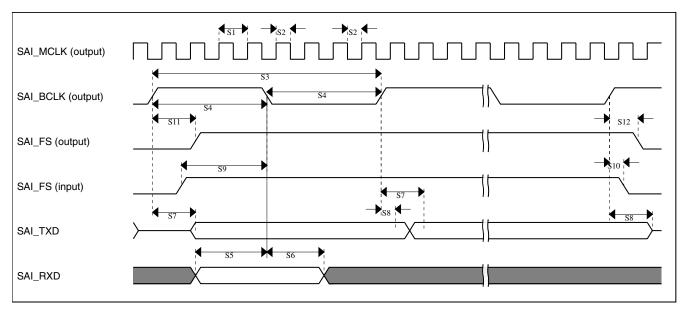

Figure 22. SAI Timing — Master modes

| Symbol           | Description                            | Min. | Max. | Unit        |

|------------------|----------------------------------------|------|------|-------------|

| _                | Operating voltage                      | 2.97 | 3.6  | V           |

| S13              | SAI_BCLK cycle time (input)            | 80   | _    | ns          |

| S14 <sup>1</sup> | SAI_BCLK pulse width high/low (input)  | 45%  | 55%  | BCLK period |

| S15              | SAI_RXD input setup before<br>SAI_BCLK | 8    | —    | ns          |

| S16              | SAI_RXD input hold after<br>SAI_BCLK   | 2    | —    | ns          |

| S17              | SAI_BCLK to SAI_TXD output valid       |      | 28   | ns          |

| S18              | SAI_BCLK to SAI_TXD output invalid     | 0    | _    | ns          |

| S19              | SAI_FS input setup before<br>SAI_BCLK  | 8    | —    | ns          |

| S20              | SAI_FS input hold after SAI_BCLK       | 2    | —    | ns          |

| S21              | SAI_BCLK to SAI_FS output valid        | _    | 28   | ns          |

| S22              | SAI_BCLK to SAI_FS output invalid      | 0    | _    | ns          |

### Table 34. Slave mode timing specifications

1. The slave mode parameters (S15 - S22) assume 50% duty cycle on SAI\_BCLK input. Any change in SAI\_BCLK duty cycle input must be taken care during the board design or by the master timing.

**Debug modules**

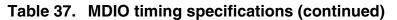

| Symbol | Description                                                                 | Min. | Max. | Unit       |

|--------|-----------------------------------------------------------------------------|------|------|------------|

| MDC1   | MDC pulse width high                                                        | 40%  | 60%  | MDC period |

| MDC2   | MDC pulse width low                                                         | 40%  | 60%  | MDC period |

| MDC3   | MDIO (input) to MDC rising edge setup                                       | 25   |      | ns         |

| MDC4   | MDIO (input) to MDC rising edge hold                                        | 0    |      | ns         |

| MDC5   | MDC falling edge to MDIO output valid (maximum propagation delay)           | —    | 25   | ns         |

| MDC6   | MDC6 MDC falling edge to MDIO output invalid<br>(minimum propagation delay) |      |      | ns         |

### 6.5.7 Clockout frequency

Maximum supported clock out frequency for this device is 20 MHz

# 6.6 Debug modules

### 6.6.1 SWD electrical specofications

# 7.3 General notes for specifications at maximum junction temperature

An estimation of the chip junction temperature, T<sub>J</sub>, can be obtained from this equation:

$$T_{J} = T_{A} + (R_{\theta JA} \times P_{D})$$

where:

- $T_A$  = ambient temperature for the package (°C)

- $R_{\theta JA}$  = junction to ambient thermal resistance (°C/W)

- $P_D$  = power dissipation in the package (W)

The junction to ambient thermal resistance is an industry standard value that provides a quick and easy estimation of thermal performance. Unfortunately, there are two values in common usage: the value determined on a single layer board and the value obtained on a board with two planes. For packages such as the PBGA, these values can be different by a factor of two. Which value is closer to the application depends on the power dissipated by other components on the board. The value obtained on a single layer board is appropriate for the tightly packed printed circuit board. The value obtained on the board with the internal planes is usually appropriate if the board has low power dissipation and the components are well separated.

When a heat sink is used, the thermal resistance is expressed in the following equation as the sum of a junction-to-case thermal resistance and a case-to-ambient thermal resistance:

# $R_{\theta JA} = R_{\theta JC} + R_{\theta CA}$

where:

- $R_{\theta JA}$  = junction to ambient thermal resistance (°C/W)

- $R_{\theta JC}$  = junction to case thermal resistance (°C/W)

- $R_{\theta CA}$  = case to ambient thermal resistance (°C/W)

$R_{\theta JC}$  is device related and cannot be influenced by the user. The user controls the thermal environment to change the case to ambient thermal resistance,  $R_{\theta CA}$ . For instance, the user can change the size of the heat sink, the air flow around the device, the interface material, the mounting arrangement on printed circuit board, or change the thermal dissipation on the printed circuit board surrounding the device.

#### Dimensions

To determine the junction temperature of the device in the application when heat sinks are not used, the Thermal Characterization Parameter ( $\Psi_{JT}$ ) can be used to determine the junction temperature with a measurement of the temperature at the top center of the package case using this equation:

$$T_J = T_T + (\Psi_{JT} \times P_D)$$

where:

- $T_T$  = thermocouple temperature on top of the package (°C)

- $\Psi_{JT}$  = thermal characterization parameter (°C/W)

- $P_D$  = power dissipation in the package (W)

The thermal characterization parameter is measured per JESD51-2 specification using a 40 gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over about 1 mm of wire extending from the junction. The thermocouple wire is placed flat against the package case to avoid measurement errors caused by cooling effects of the thermocouple wire.

# 8 Dimensions

# 8.1 Obtaining package dimensions

Package dimensions are provided in the package drawings.

To find a package drawing, go to http://www.nxp.com and perform a keyword search for the drawing's document number:

| Package option | Document Number       |

|----------------|-----------------------|

| 32-pin QFN     | SOT617-3 <sup>1</sup> |

| 48-pin LQFP    | 98ASH00962A           |

| 64-pin LQFP    | 98ASS23234W           |

| 100-pin LQFP   | 98ASS23308W           |

| 100-pin MAPBGA | 98ASA00802D           |

| 144-pin LQFP   | 98ASS23177W           |

| 176-pin LQFP   | 98ASS23479W           |

1. 5x5 mm package

| Rev. No. | Date          | Substantial Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |               | <ul> <li>Updated values for V<sub>REFH</sub> and V<sub>REFL</sub> to add refernce to the section<br/>"voltage and current operating requirments" for Min and Max valaues</li> <li>Updated footnote to Typ.</li> <li>Removed footnote from RAS Analog source resistance</li> <li>Updated figure: ADC input impedance equivalency diagram</li> <li>In table: 12-bit ADC characteristics (2.7 V to 3 V) (V<sub>REFH</sub> = V<sub>DDA</sub>, V<sub>REFL</sub> =<br/>V<sub>SS</sub>)</li> <li>Removed rows for V<sub>TEMP_S</sub> and V<sub>TEMP25</sub></li> <li>Updated footnote to Typ.</li> <li>In table: 12-bit ADC characteristics (3 V to 5.5 V)(V<sub>REFH</sub> = V<sub>DDA</sub>, V<sub>REFL</sub> =<br/>V<sub>SS</sub>)</li> <li>Removed rows for V<sub>TEMP_S</sub> and V<sub>TEMP25</sub></li> <li>Updated footnote to Typ.</li> <li>In table: 12-bit ADC characteristics (3 V to 5.5 V)(V<sub>REFH</sub> = V<sub>DDA</sub>, V<sub>REFL</sub> =<br/>V<sub>SS</sub>)</li> <li>Removed rows for V<sub>TEMP_S</sub> and V<sub>TEMP25</sub></li> <li>Removed number for TUE</li> <li>Updated footnote to Typ.</li> <li>In table: Comparator with 8-bit DAC electrical specifications</li> <li>Updated Typ. of I<sub>DDLS</sub> Supply current, Low-speed mode</li> <li>Updated Typ. of I<sub>DDLS</sub> Propagation delay, Low-speed mode</li> <li>Updated Typ. of I<sub>DDLS</sub> Propagation delay, High-speed mode</li> <li>Updated Typ. of I<sub>DDAC</sub> Initialization and switching settling time</li> <li>Updated footnote</li> <li>Updated footnote</li> <li>Updated section: LENE Propagation delay</li> <li>Added section: SAI electrical specifications</li> <li>Added section: Clockout frequency</li> <li>Added section: Clockout frequency</li> <li>Added section: Trace electrical specifications</li> <li>Updated table: Table 41 : Updated numbers for S32K142 and S32K148</li> <li>Updated Document number for 32-pin QFN in topic Obtaining package dimensions</li> </ul> |

| 3        | 14 March 2017 | <ul> <li>In Table 2 <ul> <li>Updated min. value of V<sub>DD_OFF</sub></li> <li>Added parameter I<sub>INJSUM_AF</sub></li> </ul> </li> <li>Updated Power mode transition operating behaviors</li> <li>Updated Power consumption</li> <li>Updated footnote to T<sub>SPLL_LOCK</sub> in SPLL electrical specifications</li> <li>In 12-bit ADC electrical characteristics <ul> <li>Updated table: 12-bit ADC characteristics (2.7 V to 3 V) (VREFH = VDDA, VREFL = VSS)</li> <li>Added typ. value to I<sub>DDA_ADC</sub>, TUE, DNL, and INL</li> <li>Added min. value to SMPLTS</li> <li>Removed footnote 'All the parameters in this table '</li> <li>Updated table: 12-bit ADC characteristics (3 V to 5.5 V) (VREFH = VDDA, VREFL = VSS)</li> <li>Added typ. value to I<sub>DDA_ADC</sub></li> <li>Removed footnote 'All the parameters in this table '</li> </ul> </li> <li>In Flash timing specifications — commands updated Max. value of t<sub>vfykey</sub> to 33 µs</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4        | 02 June 2017  | <ul> <li>In section: Block diagram, added block diagram for S32K11x series.</li> <li>Updated figure: S32K1xx product series comparison.</li> <li>In section: Selecting orderable part number, added reference to attachemen <i>S32K_Part_Numbers.xlsx</i>.</li> <li>In section: Ordering information <ul> <li>Updated figure: Ordering information.</li> </ul> </li> <li>In Table 1,</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

### Table 43. Revision History (continued)

Table continues on the next page...

Table continues on the next page...

| Rev. No. | Rev. No. Date Substantial Chan |                                                                                                                                     |

|----------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

|          |                                | <ul> <li>Updated specs for T<sub>JIT</sub> Cycle-to-Cycle jitter to 300 ps</li> </ul>                                               |

|          |                                | <ul> <li>In QuadSPI AC specifications :</li> </ul>                                                                                  |

|          |                                | <ul> <li>Updated specs for T<sub>iv</sub> Data Output In-Valid Time</li> </ul>                                                      |

|          |                                | In figure 'QuadSPI output timing (SDR mode) diagram', marked Invalid                                                                |

|          |                                | area                                                                                                                                |

|          |                                | <ul> <li>In CMP with 8-bit DAC electrical specifications :</li> </ul>                                                               |

|          |                                | <ul> <li>Removed '(VAIO)' from decription of V<sub>HYST0</sub></li> </ul>                                                           |

|          |                                | In LPSPI electrical specifications :                                                                                                |

|          |                                | <ul> <li>Added note 'Undefined' in figures 'LPSPI slave mode timing (CPHA = 0)' and 'LPSPI slave mode timing (CPHA = 1)'</li> </ul> |

### Table 43. Revision History