#### NXP USA Inc. - FS32K144HFT0VLHT Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4F                                                         |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 80MHz                                                                    |

| Connectivity               | CANbus, FlexIO, I <sup>2</sup> C, LINbus, SPI, UART/USART                |

| Peripherals                | POR, PWM, WDT                                                            |

| Number of I/O              | 58                                                                       |

| Program Memory Size        | 512KB (512K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 4K x 8                                                                   |

| RAM Size                   | 64K × 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| Data Converters            | A/D 16x12b SAR; D/A1x8b                                                  |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-LQFP                                                                  |

| Supplier Device Package    | 64-LQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/fs32k144hft0vlht |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Communications interfaces

- Up to three Low Power Universal Asynchronous Receiver/Transmitter (LPUART/LIN) modules with DMA support and low power availability

- Up to three Low Power Serial Peripheral Interface (LPSPI) modules with DMA support and low power availability

- Up to two Low Power Inter-Integrated Circuit (LPI2C) modules with DMA support and low power availability

- Up to three FlexCAN modules (with optional CAN-FD support)

- FlexIO module for emulation of communication protocols and peripherals (UART, I2C, SPI, I2S, LIN, PWM, etc).

- Up to one 10/100Mbps Ethernet with IEEE1588 support and two Synchronous Audio Interface (SAI) modules.

- Safety and Security

- Cryptographic Services Engine (CSEc) implements a comprehensive set of cryptographic functions as described in the SHE (Secure Hardware Extension) Functional Specification. Note: CSEc (Security) or EEPROM writes/erase will trigger error flags in HSRUN mode (112 MHz) because this use case is not allowed to execute simultaneously. The device will need to switch to RUN mode (80 MHz) to execute CSEc (Security) or EEPROM writes/erase.

- 128-bit Unique Identification (ID) number

- Error-Correcting Code (ECC) on flash and SRAM memories

- System Memory Protection Unit (System MPU)

- Cyclic Redundancy Check (CRC) module

- Internal watchdog (WDOG)

- External Watchdog monitor (EWM) module

- Timing and control

- Up to eight independent 16-bit FlexTimers (FTM) modules, offering up to 64 standard channels (IC/OC/PWM)

- One 16-bit Low Power Timer (LPTMR) with flexible wake up control

- Two Programmable Delay Blocks (PDB) with flexible trigger system

- One 32-bit Low Power Interrupt Timer (LPIT) with 4 channels

- 32-bit Real Time Counter (RTC)

- Package

- 32-pin QFN, 48-pin LQFP, 64-pin LQFP, 100-pin LQFP, 100-pin MAPBGA, 144-pin LQFP, 176-pin LQFP package options

- 16 channel DMA with up to 63 request sources using DMAMUX

# **3** Ordering information

# 3.1 Selecting orderable part number

Not all part number combinations are available. See the attachment *S32K1xx\_Orderable\_Part\_Number\_List.xlsx* attached with the Datasheet for a list of standard orderable part numbers.

#### General

- 4. When input pad voltage levels are close to V<sub>DD</sub> or V<sub>SS</sub>, practically no current injection is possible.

- 5. While respecting the maximum current injection limit

- 6. This is the Electronic Control Unit (ECU) supply ramp rate and not directly the MCU ramp rate. Limit applies to both maximum absolute maximum ramp rate and typical operating conditions.

- 7. This is the MCU supply ramp rate and the ramp rate assumes that the S32K1xx HW design guidelines in AN5426 are followed. Limit applies to both maximum absolute maximum ramp rate and typical operating conditions.

- 8. T<sub>J</sub> (Junction temperature)=135 °C. Assumes T<sub>A</sub>=125 °C for RUN mode

- T<sub>J</sub> (Junction temperature)=125 °C. Assumes TA=105 °C for HSRUN mode

- Assumes maximum θJA for 2s2p board. See Thermal characteristics

- 9. 60 seconds lifetime; device in reset (no outputs enabled/toggling)

# 4.2 Voltage and current operating requirements

## NOTE

Device functionality is guaranteed up to the LVR assert level, however electrical performance of 12-bit ADC, CMP with 8-bit DAC, IO electrical characteristics, and communication modules electrical characteristics would be degraded when voltage drops below 2.7 V

| Symbol                                 | Description                                                                                                                                                                                      | Min.             | Max.                   | Unit | Notes |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------|------|-------|

| V <sub>DD</sub> <sup>2</sup>           | Supply voltage                                                                                                                                                                                   | 2.7 <sup>3</sup> | 5.5                    | V    | 4     |

| $V_{DD_OFF}$                           | Voltage allowed to be developed on V <sub>DD</sub><br>pin when it is not powered from any<br>external power supply source.                                                                       | 0                | 0.1                    | V    |       |

| V <sub>DDA</sub>                       | Analog supply voltage                                                                                                                                                                            | 2.7              | 5.5                    | V    | 4     |

| $V_{DD} - V_{DDA}$                     | V <sub>DD</sub> -to-V <sub>DDA</sub> differential voltage                                                                                                                                        | - 0.1            | 0.1                    | V    | 4     |

| V <sub>REFH</sub>                      | ADC reference voltage high                                                                                                                                                                       | 2.7              | V <sub>DDA</sub> + 0.1 | V    | 5     |

| V <sub>REFL</sub>                      | ADC reference voltage low                                                                                                                                                                        | -0.1             | 0.1                    | V    |       |

| V <sub>ODPU</sub>                      | Open drain pullup voltage level                                                                                                                                                                  | V <sub>DD</sub>  | V <sub>DD</sub>        | V    | 6     |

| I <sub>INJPAD_DC_OP</sub> <sup>7</sup> | Continuous DC input current (positive / negative) that can be injected into an I/O pin                                                                                                           | -3               | +3                     | mA   |       |

| I <sub>INJSUM_DC_OP</sub>              | Continuous total DC input current that can<br>be injected across all I/O pins such that<br>there's no degradation in accuracy of<br>analog modules: ADC and ACMP (See<br>section Analog Modules) | _                | 30                     | mA   |       |

#### Table 2. Voltage and current operating requirements 1

- Typical conditions assumes V<sub>DD</sub> = V<sub>DDA</sub> = V<sub>REFH</sub> = 5 V, temperature = 25 °C and typical silicon process unless otherwise stated.

- As V<sub>DD</sub> varies between the minimum value and the absolute maximum value the analog characteristics of the I/O and the ADC will both change. See section I/O parameters and ADC electrical specifications respectively for details.

- S32K148 will operate from 2.7 V when executing from internal FIRC. When the PLL is engaged S32K148 is guaranteed to operate from 2.97 V. All other S32K family devices operate from 2.7 V in all modes.

- V<sub>DD</sub> and V<sub>DDA</sub> must be shorted to a common source on PCB. The differential voltage between V<sub>DD</sub> and V<sub>DDA</sub> is for RF-AC only. Appropriate decoupling capacitors to be used to filter noise on the supplies. See application note AN5032 for reference supply design for SAR ADC.

### Table 7. Power consumption (Typicals unless stated otherwise) 1 (continued)

General

|                      |                          |     | VLPS (                            | μΑ) <sup>2</sup>    | V                                 | LPR (m                                      | A)                                          | STOP1<br>(mA) | STOP2<br>(mA) |                      | l@48<br>(mA)        |                      | 64 MHz<br>nA)       |                      | 80 MHz<br>nA)       |                      | N@112<br>(mA) <sup>3</sup> |                               |

|----------------------|--------------------------|-----|-----------------------------------|---------------------|-----------------------------------|---------------------------------------------|---------------------------------------------|---------------|---------------|----------------------|---------------------|----------------------|---------------------|----------------------|---------------------|----------------------|----------------------------|-------------------------------|

| Chip/Device          | Ambient Temperature (°C) |     | Peripherals disabled <sup>5</sup> | Peripherals enabled | Peripherals disabled <sup>6</sup> | Peripherals enabled use case 1 <sup>6</sup> | Peripherals enabled use case 2 <sup>7</sup> |               |               | Peripherals disabled | Peripherals enabled        | IDD/MHz (µA/MHz) <sup>4</sup> |

|                      |                          | Max | 1637                              | 1694                | 3.1                               | 3.21                                        | NA                                          | 12.7          | 13.7          | 25                   | 32.9                | 30.7                 | 38.8                | 36                   | 43.8                | N                    | A                          | 450                           |

| S32K144              | 25                       | Тур | 29.8                              | 42                  | 1.48                              | 1.50                                        | 2.91                                        | 7             | 7.7           | 19.7                 | 26.9                | 25.1                 | 33.3                | 30.2                 | 39.6                | 43.3                 | 55.6                       | 378                           |

|                      | 85                       | Тур | 150                               | 159                 | 1.72                              | 1.85                                        | 3.08                                        | 7.2           | 8.1           | 20.4                 | 27.1                | 26.1                 | 33.5                | 30.5                 | 40                  | 43.9                 | 56.1                       | 381                           |

|                      |                          | Max | 359                               | 384                 | 2.60                              | 2.65                                        | NA                                          | 9.2           | 9.9           | 23.2                 | 29.6                | 29.3                 | 36.2                | 34.8                 | 42.1                | 46.3                 | 59.7                       | 435                           |

|                      | 105                      | Тур | 256                               | 273                 | 1.80                              | 2.10                                        | 3.23                                        | 7.8           | 8.5           | 20.6                 | 27.4                | 26.6                 | 33.8                | 31.2                 | 40.5                | 44.8                 | 57.1                       | 390                           |

|                      |                          | Max | 850                               | 900                 | 2.65                              | 2.70                                        | NA                                          | 10.3          | 11.1          | 23.9                 | 30.6                | 30.3                 | 37.3                | 35.6                 | 43.5                | 47.9                 | 61.3                       | 445                           |

|                      | 125                      | Тур | NA                                | NA                  | NA                                | NA                                          | 3.65                                        | NA            | NA            | NA                   | NA                  | NA                   | NA                  | NA                   | NA                  | N                    | A                          | NA                            |

|                      |                          | Max | 1960                              | 1998                | 3.18                              | 3.25                                        | NA                                          | 12.9          | 13.8          | 26.9                 | 33.6                | 35                   | 40.3                | 38.7                 | 46.8                | N                    | A                          | 484                           |

| S32K146              | 25                       | Тур | 37                                | 47                  | 1.57                              | 1.61                                        | 3.3                                         | 8             | 9.2           | 23.4                 | 31.4                | 30.5                 | 40.2                | 36.2                 | 47.6                | 52                   | 68.3                       | 452                           |

|                      | 85                       | Тур | 207                               | 209                 | 1.79                              | 1.83                                        | 3.54                                        | 8.9           | 10.1          | 24.4                 | 32.4                | 31.5                 | 41.3                | 37.2                 | 48.7                | 53.3                 | 69.8                       | 465                           |

|                      |                          | Max | 974                               | 981                 | 3.32                              | 3.38                                        | NA                                          | 12.7          | 13.9          | 29.3                 | 37.9                | 36.7                 | 47                  | 42.4                 | 54.4                | 60.3                 | 78                         | 530                           |

|                      | 105                      | Тур | 419                               | 422                 | 1.99                              | 2.04                                        | 3.78                                        | 9.8           | 11            | 25.3                 | 33.4                | 32.5                 | 42.2                | 38.1                 | 49.6                | 54.4                 | 70.8                       | 477                           |

|                      |                          | Max | 2004                              | 2017                | 4.06                              | 4.13                                        | NA                                          | 17.1          | 18.3          | 34.1                 | 42.6                | 41.3                 | 51.4                | 46.9                 | 58.8                | 65.7                 | 82.8                       | 587                           |

|                      | 125                      | Тур | NA                                | NA                  | NA                                | NA                                          | 4.44                                        | NA            | NA            | NA                   | NA                  | NA                   | NA                  | NA                   | NA                  | N                    | A                          | NA                            |

|                      |                          | Max | 3358                              | 3380                | 5.28                              | 5.38                                        | NA                                          | 22.6          | 23.7          | 40.2                 | 48.8                | 47.3                 | 57.4                | 52.8                 | 64.8                | N                    | A                          | 660                           |

| S32K148 <sup>8</sup> | 25                       | Тур | 38                                | 54                  | 2.17                              | 2.20                                        | 3.45                                        | 8.5           | 9.6           | 27.6                 | 34.9                | 35.5                 | 45.3                | 42.1                 | 57.7                | 60.3                 | 83.3                       | 526                           |

|                      | 85                       | Тур | 336                               | 357                 | 2.30                              | 2.35                                        | 3.74                                        | 10.1          | 11.1          | 29.1                 | 37.0                | 36.8                 | 46.6                | 43.4                 | 59.9                | 62.9                 | 88.7                       | 543                           |

Table continues on the next page...

18

### Table 7. Power consumption (Typicals unless stated otherwise) 1 (continued)

|             |                          |     | VLPS (                            | μΑ) <sup>2</sup>    | V                                 | LPR (m                                      | A)                                          | STOP1<br>(mA) | STOP2<br>(mA) |                      | l@48<br>(mA)        |                      | 64 MHz<br>nA)       |                      | 80 MHz<br>nA)       |                      | N@112<br>(mA) <sup>3</sup> |                               |

|-------------|--------------------------|-----|-----------------------------------|---------------------|-----------------------------------|---------------------------------------------|---------------------------------------------|---------------|---------------|----------------------|---------------------|----------------------|---------------------|----------------------|---------------------|----------------------|----------------------------|-------------------------------|

| Chip/Device | Ambient Temperature (°C) |     | Peripherals disabled <sup>5</sup> | Peripherals enabled | Peripherals disabled <sup>6</sup> | Peripherals enabled use case 1 <sup>6</sup> | Peripherals enabled use case 2 <sup>7</sup> |               |               | Peripherals disabled | Peripherals enabled        | IDD/MHz (µA/MHz) <sup>4</sup> |

|             |                          | Max | 1660                              | 1736                | 3.48                              | 3.55                                        | NA                                          | 14.5          | 15.6          | 34.8                 | 43.6                | 41.9                 | 53.9                | 48.7                 | 65.1                | 70.4                 | 96.1                       | 609                           |

|             | 105                      | Тур | 560                               | 577                 | 2.49                              | 2.54                                        | 4.03                                        | 10.9          | 11.9          | 29.8                 | 37.8                | 37.6                 | 47.5                | 45.2                 | 61.5                | 63.8                 | 89.1                       | 565                           |

|             |                          | Max | 2945                              | 2970                | 4.40                              | 4.47                                        | NA                                          | 18.0          | 19.0          | 38.4                 | 46.8                | 44.9                 | 55.3                | 51.6                 | 66.8                | 73.6                 | 97.4                       | 645                           |

|             | 125                      | Тур | NA                                | NA                  | NA                                | NA                                          | 4.85                                        | NA            | NA            | NA                   | NA                  | NA                   | NA                  | NA                   | NA                  | N                    | İA                         | NA                            |

|             |                          | Max | 3990                              | 4166                | 6.00                              | 6.08                                        | NA                                          | 23.4          | 24.5          | 44.3                 | 52.5                | 50.9                 | 61.3                | 57.5                 | 71.6                | N                    | IA                         | 719                           |

- Typical current numbers are indicative for typical silicon process and may vary based on the silicon distribution and user configuration. Typical conditions assumes

V<sub>DD</sub> = V<sub>DDA</sub> = V<sub>REFH</sub> = 5 V, temperature = 25 °C and typical silicon process unless otherwise stated. All output pins are floating and On-chip pulldown is enabled for

all unused input pins.

- 2. Current numbers are for reduced configuration and may vary based on user configuration and silicon process variation.

- 3. HSRUN mode must not be used at 125°C. Max ambient temperature for HSRUN mode is 105°C.

- 4. Values mentioned for S32K14x devices are measured at RUN@80 MHz with peripherals disabled and values mentioned for S32K11x devices are measured at RUN@48 MHz with peripherals disabled.

- 5. With PMC\_REGSC[CLKBIASDIS] set to 1. See Reference Manual for details.

- 6. Data collected using RAM

- 7. Numbers on limited samples size and data collected with Flash

- 8. The S32K148 data points assume that ENET/QuadSPI/SAI etc. are inactive.

# 5.3 DC electrical specifications at 3.3 V Range

NOTE

For details on the pad types defined in Table 11 and Table 12, see Reference Manual section *IO Signal Table* and IO Signal Description Input Multiplexing sheet(s) attached with Reference Manual.

| Symbol                                              | Parameter                                                                           |                       | Value                   |                       | Unit | Notes |  |

|-----------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------|-------------------------|-----------------------|------|-------|--|

|                                                     |                                                                                     | Min.                  | Тур.                    | Max.                  |      |       |  |

| V <sub>DD</sub>                                     | I/O Supply Voltage                                                                  | 2.7                   | 3.3                     | 4                     | V    | 1     |  |

| V <sub>ih</sub>                                     | Input Buffer High Voltage                                                           | $0.7 \times V_{DD}$   | _                       | V <sub>DD</sub> + 0.3 | V    | 2     |  |

| V <sub>il</sub>                                     | Input Buffer Low Voltage                                                            | V <sub>SS</sub> – 0.3 |                         | $0.3 \times V_{DD}$   | V    | 3     |  |

| V <sub>hys</sub>                                    | Input Buffer Hysteresis                                                             | $0.06 \times V_{DD}$  | _                       | —                     | V    |       |  |

| loh <sub>GPIO</sub><br>loh <sub>GPIO-HD_DSE_0</sub> | I/O current source capability measured when pad $V_{oh} = (V_{DD} - 0.8 \text{ V})$ | 3.5                   | —                       | _                     | mA   |       |  |

| Iol <sub>GPIO</sub> -HD_DSE_0                       | I/O current sink capability measured when pad $V_{ol} = 0.8 \text{ V}$              | 3                     | _                       |                       | mA   |       |  |

| Ioh <sub>GPIO-HD_DSE_1</sub>                        | I/O current source capability measured when pad $V_{oh} = (V_{DD} - 0.8 \text{ V})$ | 14                    | —                       | _                     | mA   | 4     |  |

| Iol <sub>GPIO-HD_DSE_1</sub>                        | I/O current sink capability measured when pad $V_{\text{ol}}$ = 0.8 V               | 12                    | _                       | _                     | mA   | 4     |  |

| loh <sub>GPIO-FAST_DSE_0</sub>                      | I/O current sink capability measured when pad $V_{oh}{=}V_{DD}{-}0.8~V$             | 9.5                   | _                       | _                     | mA   | 5     |  |

| IOI <sub>GPIO-FAST_DSE_0</sub>                      | I/O current sink capability measured when pad $V_{\text{ol}}$ = 0.8 V               | 10                    | _                       | —                     | mA   | 5     |  |

| Ioh <sub>GPIO-FAST_DSE_1</sub>                      | I/O current sink capability measured when pad $V_{oh}{=}V_{DD}{-}0.8~V$             | 16                    | _                       | —                     | mA   | 5     |  |

| IOI <sub>GPIO-FAST_DSE_1</sub>                      | I/O current sink capability measured when pad $V_{\text{ol}}$ = 0.8 V               | 15.5                  | _                       | _                     | mA   | 5     |  |

| IOHT                                                | Output high current total for all ports                                             | _                     | _                       | 100                   | mA   |       |  |

| IIN                                                 | Input leakage current (per pin) for full tempera                                    | ture range at         | V <sub>DD</sub> = 3.3 V | /                     | ł    | 6     |  |

|                                                     | All pins other than high drive port pins                                            |                       | 0.005                   | 0.5                   | μA   |       |  |

|                                                     | High drive port pins <sup>7</sup>                                                   |                       | 0.010                   | 0.5                   | μA   | ]     |  |

| R <sub>PU</sub>                                     | Internal pullup resistors                                                           | 20                    |                         | 60                    | kΩ   | 8     |  |

| R <sub>PD</sub>                                     | Internal pulldown resistors                                                         | 20                    |                         | 60                    | kΩ   | 9     |  |

1. S32K148 will operate from 2.7 V when executing from internal FIRC. When the PLL is engaged S32K148 is guaranteed to operate from 2.97 V. All other S32K family devices operate from 2.7 V in all modes.

- 2. For reset pads, same V<sub>ih</sub> levels are applicable

- 3. For reset pads, same V<sub>il</sub> levels are applicable

- 4. The value given is measured at high drive strength mode. For value at low drive strength mode see the loh\_Standard value given above.

- 5. For refernce only. Run simulations with the IBIS model and custom board for accurate results.

#### I/O parameters

| Symbol                   | DSE | Rise tii | me (nS) <sup>1</sup> | Fall tim | ne (nS) <sup>1</sup> | Capacitance (pF) <sup>2</sup> |

|--------------------------|-----|----------|----------------------|----------|----------------------|-------------------------------|

|                          |     | Min.     | Max .                | Min.     | Max.                 |                               |

|                          |     | 17.3     | 54.8                 | 17.6     | 59.7                 | 200                           |

|                          | 1   | 1.1      | 4.6                  | 1.1      | 5.0                  | 25                            |

|                          |     | 2.0      | 5.7                  | 2.0      | 5.8                  | 50                            |

|                          |     | 5.4      | 16.0                 | 5.0      | 16.0                 | 200                           |

| tRF <sub>GPIO-FAST</sub> | 0   | 0.42     | 2.2                  | 0.37     | 2.2                  | 25                            |

|                          |     | 2.0      | 5.0                  | 1.9      | 5.2                  | 50                            |

|                          |     | 9.3      | 18.8                 | 8.5      | 19.3                 | 200                           |

|                          | 1   | 0.37     | 0.9                  | 0.35     | 0.9                  | 25                            |

|                          |     | 1.2      | 2.7                  | 1.2      | 2.9                  | 50                            |

|                          |     | 6.0      | 11.8                 | 6.0      | 12.3                 | 200                           |

#### Table 14. AC electrical specifications at 5 V Range (continued)

1. For reference only. Run simulations with the IBIS model and your custom board for accurate results.

2. Maximum capacitances supported on Standard IOs. However interface or protocol specific specifications might be different, for example for ENET, QSPI etc. . For protocol specific AC specifications, see respective sections.

# 5.7 Standard input pin capacitance

#### Table 15. Standard input pin capacitance

| Symbol            | Description                     | Min. | Max. | Unit |

|-------------------|---------------------------------|------|------|------|

| C <sub>IN_D</sub> | Input capacitance: digital pins | _    | 7    | pF   |

### NOTE

Please refer to External System Oscillator electrical specifications for EXTAL/XTAL pins.

# 5.8 Device clock specifications

### Table 16. Device clock specifications 1

| Symbol             | Description                      | Min. | Max. | Unit |

|--------------------|----------------------------------|------|------|------|

|                    | High Speed run mode <sup>2</sup> |      |      |      |

| f <sub>SYS</sub>   | System and core clock            | —    | 112  | MHz  |

| f <sub>BUS</sub>   | Bus clock                        | _    | 56   | MHz  |

| f <sub>FLASH</sub> | Flash clock                      | —    | 28   | MHz  |

|                    | Normal run mode (S32K11x series  | )    |      |      |

| f <sub>SYS</sub>   | System and core clock            | —    | 48   | MHz  |

| f <sub>BUS</sub>   | Bus clock                        | _    | 48   | MHz  |

Table continues on the next page...

|                       | Table 18.                                    | External S           | ystem Osc | illator frequ | lency spec | ifications |         |      |       | Clock    |

|-----------------------|----------------------------------------------|----------------------|-----------|---------------|------------|------------|---------|------|-------|----------|

| Symbol                | Description                                  | м                    | in.       | Ту            | /p.        | Ma         | ax.     | Unit | Notes | ck inte  |

|                       |                                              | S32K14x S32K11x S32K |           | S32K14x       | S32K11x    | S32K14x    | S32K11x | 1    |       | <b>_</b> |

| f <sub>osc_hi</sub>   | Oscillator crystal or resonator<br>frequency | 2                    | 4         |               | _          |            | 40      |      |       | face mo  |

| f <sub>ec_extal</sub> | Input clock frequency (external clock mode)  | _                    | -         |               | _          |            | 48      | MHz  | 1     | odules   |

| t <sub>dc_extal</sub> | Input clock duty cycle (external clock mode) | 4                    | 8         | 50            |            | 52         |         | %    | 1     |          |

| t <sub>cst</sub>      | Crystal Start-up Time                        |                      |           |               |            |            |         |      |       |          |

|                       | 8 MHz low-gain mode (HGO=0)                  | -                    | -         |               | 5          | -          | _       | ms   | 2     |          |

|                       | 8 MHz high-gain mode (HGO=1)                 | -                    | —         |               | 5          | -          | _       |      |       |          |

|                       | 40 MHz low-gain mode (HGO=0)                 | -                    | _         | 2             | 2          | —          |         | 1    |       |          |

|                       | 40 MHz high-gain mode (HGO=1)                | -                    | _         | 2             | 2          | —          |         |      |       |          |

### Table 18. External System Oscillator frequency specifications

Frequencies below 40 MHz can be used for degraded duty cycle upto 40-60% Proper PC board layout procedures must be followed to achieve specifications. 1.

2.

# 6.2.3 System Clock Generation (SCG) specifications

### 6.2.3.1 Fast internal RC Oscillator (FIRC) electrical specifications Table 19. Fast internal RC Oscillator electrical specifications

| Symbol                        | Parameter <sup>1</sup>                                               |      | Value |      | Unit               |

|-------------------------------|----------------------------------------------------------------------|------|-------|------|--------------------|

|                               |                                                                      | Min. | Тур.  | Max. |                    |

| F <sub>FIRC</sub>             | FIRC target frequency                                                | —    | 48    |      | MHz                |

| ΔF                            | Frequency deviation across process, voltage, and temperature < 105°C | —    | ±0.5  | ±1   | %F <sub>FIRC</sub> |

| ΔF125                         | Frequency deviation across process, voltage, and temperature < 125°C | —    | ±0.5  | ±1.1 | %F <sub>FIRC</sub> |

| T <sub>Startup</sub>          | Startup time                                                         |      | 3.4   | 5    | μs²                |

| T <sub>JIT</sub> , 3          | Cycle-to-Cycle jitter                                                | —    | 300   | 500  | ps                 |

| T <sub>JIT</sub> <sup>3</sup> | Long term jitter over 1000 cycles                                    | —    | 0.04  | 0.1  | %F <sub>FIRC</sub> |

1. With FIRC regulator enable

2. Startup time is defined as the time between clock enablement and clock availability for system use.

3. FIRC as system clock

## NOTE

Fast internal RC Oscillator is compliant with CAN and LIN standards.

### 6.2.3.2 Slow internal RC oscillator (SIRC) electrical specifications Table 20. Slow internal RC oscillator (SIRC) electrical specifications

| Symbol               | Parameter                                                                     |      |      | Unit |                    |

|----------------------|-------------------------------------------------------------------------------|------|------|------|--------------------|

|                      |                                                                               | Min. | Тур. | Max. | 1                  |

| F <sub>SIRC</sub>    | SIRC target frequency                                                         | _    | 8    | —    | MHz                |

| ΔF                   | Frequency deviation across process, voltage, and temperature $< 105^{\circ}C$ | —    | —    | ±3   | %F <sub>SIRC</sub> |

| ΔF125                | Frequency deviation across process, voltage, and temperature < 125°C          | _    | _    | ±3.3 | %F <sub>SIRC</sub> |

| T <sub>Startup</sub> | Startup time                                                                  | _    | 9    | 12.5 | μs <sup>1</sup>    |

1. Startup time is defined as the time between clock enablement and clock availability for system use.

# 6.2.4 Low Power Oscillator (LPO) electrical specifications Table 21. Low Power Oscillator (LPO) electrical specifications

| Symbol               | Parameter                               | Min. | Тур. | Max. | Unit |

|----------------------|-----------------------------------------|------|------|------|------|

| F <sub>LPO</sub>     | Internal low power oscillator frequency | 113  | 128  | 139  | kHz  |

| T <sub>startup</sub> | Startup Time                            | _    | _    | 20   | μs   |

# 6.2.5 SPLL electrical specifications

Table 22. SPLL electrical specifications

| Symbol                               | Parameter                                          | Min.   | Тур. | Max.                                                       | Unit |

|--------------------------------------|----------------------------------------------------|--------|------|------------------------------------------------------------|------|

| F <sub>SPLL_REF</sub> <sup>1</sup>   | PLL Reference Frequency Range                      | 8      | —    | 16                                                         | MHz  |

| F <sub>SPLL_Input</sub> <sup>2</sup> | PLL Input Frequency                                | 8      | —    | 40                                                         | MHz  |

| F <sub>VCO_CLK</sub>                 | VCO output frequency                               | 180    | —    | 320                                                        | MHz  |

| F <sub>SPLL_CLK</sub>                | PLL output frequency                               | 90     | —    | 160                                                        | MHz  |

| J <sub>CYC_SPLL</sub>                | PLL Period Jitter (RMS) <sup>3</sup>               | •      | ·    |                                                            |      |

|                                      | at F <sub>VCO_CLK</sub> 180 MHz                    | _      | 120  | —                                                          | ps   |

|                                      | at F <sub>VCO_CLK</sub> 320 MHz                    | _      | 75   | —                                                          | ps   |

| J <sub>ACC_SPLL</sub>                | PLL accumulated jitter over 1µs (RMS) <sup>3</sup> |        |      |                                                            |      |

|                                      | at F <sub>VCO_CLK</sub> 180 MHz                    | _      | 1350 | —                                                          | ps   |

|                                      | at F <sub>VCO_CLK</sub> 320 MHz                    | _      | 600  | —                                                          | ps   |

| D <sub>UNL</sub>                     | Lock exit frequency tolerance                      | ± 4.47 | —    | ± 5.97                                                     | %    |

| T <sub>SPLL_LOCK</sub>               | Lock detector detection time <sup>4</sup>          | —      | _    | 150 × 10 <sup>-6</sup> +<br>1075(1/F <sub>SPLL_REF</sub> ) | S    |

1. F<sub>SPLL\_REF</sub> is PLL reference frequency range after the PREDIV. For PREDIV and MULT settings refer SCG\_SPLLCFG register of Reference Manual.

F<sub>SPLL\_Input</sub> is PLL input frequency range before the PREDIV must be limited to the range 8 MHz to 40 MHz. This input source could be derived from a crystal oscillator or some other external square wave clock source using OSC bypass mode. For external clock source settings refer SCG\_SOSCCFG register of Reference Manual.

3. This specification was obtained using a NXP developed PCB. PLL jitter is dependent on the noise characteristics of each PCB and results will vary

4. Lock detector detection time is defined as the time between PLL enablement and clock availability for system use.

# 6.3 Memory and memory interfaces

# 6.3.1 Flash memory module (FTFC) electrical specifications

This section describes the electrical characteristics of the flash memory module.

| Symbol                  | Descriptio                                                   | on <sup>1</sup>        | S3   | 2K116 | S    | 32K118 |      |                  |

|-------------------------|--------------------------------------------------------------|------------------------|------|-------|------|--------|------|------------------|

|                         |                                                              |                        | Тур  | Max   | Тур  | Max    | Unit | Notes            |

| t <sub>ersscr</sub>     | Erase Flash Sector<br>execution time                         |                        | 12   | 130   | 12   | 130    | ms   | 2                |

| t <sub>pgmsec1k</sub>   | Program Section<br>execution time (1 KB<br>flash)            | _                      | 5    | —     | 5    | -      | ms   |                  |

| t <sub>rd1all</sub>     | Read 1s All Block<br>execution time                          |                        | _    | 1.7   | _    | 2.8    | ms   |                  |

| t <sub>rdonce</sub>     | Read Once execution time                                     |                        | _    | 30    | —    | 30     | μs   |                  |

| t <sub>pgmonce</sub>    | Program Once execution time                                  |                        | 90   | —     | 90   | _      | μs   |                  |

| t <sub>ersall</sub>     | Erase All Blocks<br>execution time                           |                        | 150  | 1500  | 230  | 2500   | ms   | 2                |

| t <sub>vfykey</sub>     | Verify Backdoor Access<br>Key execution time                 | _                      | —    | 35    | —    | 35     | μs   |                  |

| t <sub>ersallu</sub>    | Erase All Blocks<br>Unsecure execution time                  | _                      | 150  | 1500  | 230  | 2500   | ms   | 2                |

| t <sub>pgmpart</sub>    | Program Partition for<br>EEPROM execution time               | 32 KB EEPROM<br>backup | 71   | —     | 71   | -      | ms   | 3                |

|                         |                                                              | 64 KB EEPROM<br>backup | —    | —     | —    | -      |      |                  |

| t <sub>setram</sub>     | Set FlexRAM Function execution time                          | Control Code<br>0xFF   | 0.08 | —     | 0.08 | -      | ms   | 3                |

|                         |                                                              | 32 KB EEPROM<br>backup | 0.8  | 1.2   | 0.8  | 1.2    |      |                  |

|                         |                                                              | 48 KB EEPROM<br>backup | —    | —     | —    | -      |      |                  |

|                         |                                                              | 64 KB EEPROM<br>backup | —    | —     | —    | —      |      |                  |

| t <sub>eewr8b</sub>     | Byte write to FlexRAM execution time                         | 32 KB EEPROM<br>backup | 385  | 1700  | 385  | 1700   | μs   | 3 <sup>,</sup> 4 |

|                         |                                                              | 48 KB EEPROM<br>backup | —    | —     | —    | _      |      |                  |

|                         |                                                              | 64 KB EEPROM<br>backup | —    | _     | —    | —      |      |                  |

| t <sub>eewr16b</sub>    | 16-bit write to FlexRAM execution time                       | 32 KB EEPROM<br>backup | 385  | 1700  | 385  | 1700   | μs   | 3 <sup>,</sup> 4 |

|                         |                                                              | 48 KB EEPROM<br>backup | —    | —     | -    | -      |      |                  |

|                         |                                                              | 64 KB EEPROM<br>backup | -    | _     | -    | -      |      |                  |

| t <sub>eewr32bers</sub> | 32-bit write to erased<br>FlexRAM location<br>execution time | _                      | 360  | 2000  | 360  | 2000   | μs   |                  |

Table 24. Flash command timing specifications for S32K11x (continued)

Table continues on the next page...

| Symbol                    | Descripti                                                                                                                                        | Description <sup>1</sup>                                            |     |                                     | s   | 32K118                        |      |                  |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----|-------------------------------------|-----|-------------------------------|------|------------------|

|                           |                                                                                                                                                  |                                                                     | Тур | Max                                 | Тур | Max                           | Unit | Notes            |

| t <sub>eewr32b</sub>      | 32-bit write to FlexRAM execution time                                                                                                           | 32 KB EEPROM<br>backup                                              | 630 | 2000                                | 630 | 2000                          | μs   | 3 <sup>,</sup> 4 |

|                           |                                                                                                                                                  | 48 KB EEPROM<br>backup                                              | —   | —                                   | —   | —                             |      |                  |

|                           |                                                                                                                                                  | 64 KB EEPROM<br>backup                                              | —   | —                                   | —   | —                             |      |                  |

| t <sub>quickwr</sub> 32-ł | 32-bit Quick Write                                                                                                                               | 1st 32-bit write                                                    | 200 | 550                                 | 200 | 550                           | μs   | 4.5.6            |

|                           | execution time: Time<br>from CCIF clearing (start<br>the write) until CCIF<br>setting (32-bit write<br>complete, ready for next<br>32-bit write) | 2nd through Next<br>to Last (Nth-1)<br>32-bit write                 | 150 | 550                                 | 150 | 550                           | -    |                  |

|                           |                                                                                                                                                  | Last (Nth) 32-bit<br>write (time for<br>write only, not<br>cleanup) | 200 | 550                                 | 200 | 550                           |      |                  |

| t <sub>quickwrClnup</sub> | Quick Write Cleanup<br>execution time                                                                                                            | —                                                                   |     | (# of<br>Quick<br>Writes ) *<br>2.0 | —   | (# of Quick<br>Writes ) * 2.0 | ms   | 7                |

#### Table 24. Flash command timing specifications for S32K11x (continued)

- 1. All command times assume 25 MHz or greater flash clock frequency (for synchronization time between internal/external clocks).

- 2. Maximum times for erase parameters based on expectations at cycling end-of-life.

- For all EEPROM Emulation terms, the specified timing shown assumes previous record cleanup has occurred. This may be verified by executing FCCOB Command 0x77, and checking FCCOB number 5 contents show 0x00 - No EEPROM issues detected.

- 4. 1st time EERAM writes after a Reset or SETRAM may incur additional overhead for EEE cleanup, resulting in up to 2x the times shown.

- 5. Only after the Nth write completes will any data be valid. Emulated EEPROM record scheme cleanup overhead may occur after this point even after a brownout or reset. If power on reset occurs before the Nth write completes, the last valid record set will still be valid and the new records will be discarded.

- 6. Quick Write times may take up to 550 µs, as additional cleanup may occur when crossing sector boundaries.

- 7. Time for emulated EEPROM record scheme overhead cleanup. Automatically done after last (Nth) write completes, assuming still powered. Or via SETRAM cleanup execution command is requested at a later point.

## NOTE

Under certain circumstances FlexMEM maximum times may be exceeded. In this case the user or application may wait, or assert reset to the FTFC macro to stop the operation.

## 6.3.1.2 Reliability specifications

#### Table 25. NVM reliability specifications

| Symbol                 | Description                           | Min. | Тур. | Max. | Unit   | Notes |  |  |  |

|------------------------|---------------------------------------|------|------|------|--------|-------|--|--|--|

|                        | When using as Program and Data Flash  |      |      |      |        |       |  |  |  |

| t <sub>nvmretp1k</sub> | Data retention after up to 1 K cycles | 20   |      | _    | years  | 1     |  |  |  |

| n <sub>nvmcycp</sub>   | Cycling endurance                     | 1 K  | —    | _    | cycles | 2, 3  |  |  |  |

Table continues on the next page...

| NXP            |

|----------------|

| Semiconductors |

S32K1xx Data Sheet, Rev. 8, 06/2018

| FLASH PORT          | Sym              | Unit |        |             |                                 |                 |                                   | FLA                             | SH A   |     |        |                 |        |                      |                        | FLA          | SH B              |                 |

|---------------------|------------------|------|--------|-------------|---------------------------------|-----------------|-----------------------------------|---------------------------------|--------|-----|--------|-----------------|--------|----------------------|------------------------|--------------|-------------------|-----------------|

|                     |                  |      |        |             | RL                              | JN <sup>1</sup> |                                   |                                 |        |     | HSR    | UN <sup>1</sup> |        |                      | RUN/HSRUN <sup>2</sup> |              |                   |                 |

| QuadSPI Mode        |                  |      |        |             | SI                              | DR              |                                   |                                 |        |     | SDR    |                 |        | SI                   | DR                     | DE           | )R <sup>3</sup>   |                 |

|                     |                  |      |        |             | nternal Internal DQS<br>ampling |                 |                                   | Internal Internal I<br>Sampling |        |     | al DQS |                 |        | Internal<br>Sampling |                        | External DQS |                   |                 |

|                     | N1               |      |        | AD<br>oback | Internal N1<br>Loopback         |                 | PAD Internal<br>Loopback Loopback |                                 |        | N1  |        | External DQS    |        |                      |                        |              |                   |                 |

|                     |                  |      | Min    | Мах         | Min                             | Max             | Min                               | Max                             | Min    | Мах | Min    | Max             | Min    | Max                  | Min                    | Мах          | Min               | Max             |

|                     |                  |      |        |             |                                 | •               | Regis                             | ster Sett                       | ings   |     | •      | •               |        |                      |                        |              | •                 | •               |

| MCR[DDR_EN]         |                  | -    | (      | )           | (                               | C               | (                                 | C                               | (      | )   | 0      | )               | (      | )                    | (                      | )            | -                 | 1               |

| MCR[DQS_EN]         |                  | -    | (      | )           | -                               | 1               | -                                 | 1                               | (      | )   | 1      |                 | -      | 1                    | (                      | )            | -                 | 1               |

| MCR[SCLKCFG[0]]     |                  | -    | -      | -           | -                               | 1               | (                                 | C                               |        | -   | 1      |                 | (      | )                    |                        | -            |                   | -               |

| MCR[SCLKCFG[1]]     |                  | -    | -      | -           | -                               | 1               |                                   | 0                               |        | -   | 1      |                 | 0      |                      | -                      |              | -                 |                 |

| MCR[SCLKCFG[2]]     |                  | -    | -      | -           |                                 |                 |                                   | -                               | -      |     | -      |                 | -      |                      | 0                      |              |                   |                 |

| MCR[SCLKCFG[3]]     |                  | -    | -      | -           |                                 | -               |                                   | -                               | -      | -   | -      |                 |        | -                    | -                      | -            | (                 | C               |

| MCR[SCLKCFG[5]]     |                  | -    | (      | )           | (                               | C               | (                                 | C                               | (      | )   | 0      | )               | (      | )                    | (                      | )            | -                 | 1               |

| SMPR[FSPHS]         |                  | -    | (      | )           | -                               | 1               | (                                 | C                               | (      | )   | 1      |                 | (      | )                    | (                      | )            | (                 | )               |

| SMPR[FSDLY]         |                  | -    | (      | )           | (                               | )               | (                                 | C                               | (      | )   | 0      | )               | (      | )                    | (                      | )            | (                 | )               |

| SOCCR               |                  |      | -      | -           | (                               | C               | 2                                 | 3                               |        | -   | 0      | )               | 3      | 0                    |                        | -            |                   | -               |

| [SOCCFG[7:0]]       |                  |      |        |             |                                 |                 |                                   |                                 |        |     |        |                 |        |                      |                        |              |                   |                 |

| SOCCR[SOCCFG[15:8]] |                  | -    | -      |             |                                 | -               |                                   | -                               | -      |     | -      |                 |        | -                    | -                      |              | 3                 | 0               |

| FLSHCR[TDH]         |                  | -    | 0x     | 00          | 0x                              | 00              | 0x                                | :00                             | 0x     | 00  | 0x(    | 00              | 0x     | 00                   | 0x                     | 00           | 0x                | 01              |

|                     |                  |      |        |             |                                 |                 | Timing                            | g Param                         | eters  |     |        |                 |        |                      |                        |              |                   |                 |

| SCK Clock Frequency | f <sub>SCK</sub> | MHz  | -      | 38          | -                               | 64              | -                                 | 48                              | -      | 40  | -      | 80              | -      | 50                   | -                      | 20           | -                 | 20 <sup>4</sup> |

| SCK Clock Period    | t <sub>SCK</sub> | ns   | 1/fSCK | -           | 1/fSCK                          | -               | 1/fSCK                            | -                               | 1/fSCK | -   | 1/fSCK | -               | 1/fSCK | -                    | 50.0                   | -            | 50.0 <sup>4</sup> | -               |

Table continues on the next page...

Memory and memory interfaces

39

| Symbol            | Description                       | Conditions                                                                                                            | Min. | Typ. <sup>1</sup> | Max.  | Unit | Notes |

|-------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------|------|-------------------|-------|------|-------|

| f <sub>ADCK</sub> | ADC conversion clock<br>frequency | Normal usage                                                                                                          | 2    | 40                | 50    | MHz  | 3, 4  |

| f <sub>CONV</sub> | ADC conversion frequency          | No ADC hardware<br>averaging. <sup>5</sup> Continuous<br>conversions enabled,<br>subsequent conversion<br>time        | 46.4 | 928               | 1160  | Ksps | 6, 7  |

|                   |                                   | ADC hardware averaging<br>set to 32. <sup>5</sup> Continuous<br>conversions enabled,<br>subsequent conversion<br>time | 1.45 | 29                | 36.25 | Ksps | 6, 7  |

Table 27. 12-bit ADC operating conditions (continued)

- 1. Typical values assume  $V_{DDA} = 5 V$ , Temp = 25 °C,  $f_{ADCK} = 40 \text{ MHz}$ ,  $R_{AS}=20 \Omega$ , and  $C_{AS}=10 \text{ nF}$  unless otherwise stated. Typical values are for reference only, and are not tested in production.

- For packages without dedicated V<sub>REFH</sub> and V<sub>REFL</sub> pins, V<sub>REFH</sub> is internally tied to V<sub>DDA</sub>, and V<sub>REFL</sub> is internally tied to V<sub>SS</sub>. To get maximum performance, reference supply quality should be better than SAR ADC. See application note AN5032 for details.

- 3. Clock and compare cycle need to be set according to the guidelines mentioned in the Reference Manual .

- 4. ADC conversion will become less reliable above maximum frequency.

- 5. When using ADC hardware averaging, see the *Reference Manual* to determine the most appropriate setting for AVGS.

- 6. Numbers based on the minimum sampling time of 275 ns.

- 7. For guidelines and examples of conversion rate calculation, see the Reference Manual section 'Calibration function'

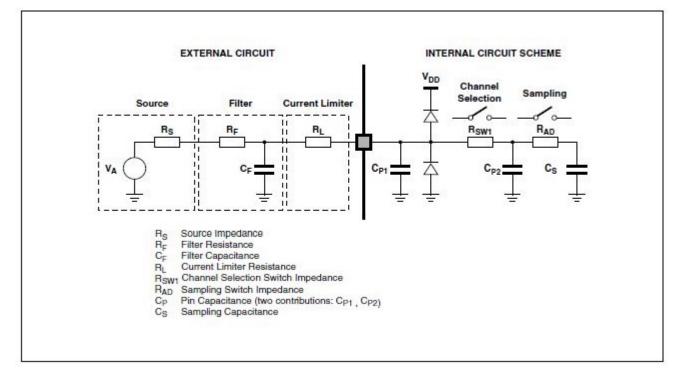

Figure 13. ADC input impedance equivalency diagram

# 6.4.1.2 12-bit ADC electrical characteristics

# NOTE

- ADC performance specifications are documented using a single ADC. For parallel/simultaneous operation of both ADCs, either for sampling the same channel by both ADCs or for sampling different channels by each ADC, some amount of decrease in performance can be expected. Care must be taken to stagger the two ADC conversions, in particular the sample phase, to minimize the impact of simultaneous conversions.

- On reduced pin packages where ADC reference pins are shared with supply pins, ADC analog performance characteristics may be impacted. The amount of variation will be directly impacted by the external PCB layout and hence care must be taken with PCB routing. See AN5426 for details

| Symbol               | Description                | Conditions <sup>1</sup> | Min. | Typ. <sup>2</sup> | Max.                                                 | Unit             | Notes      |

|----------------------|----------------------------|-------------------------|------|-------------------|------------------------------------------------------|------------------|------------|

| V <sub>DDA</sub>     | Supply voltage             |                         | 2.7  |                   | 3                                                    | V                |            |

| I <sub>DDA_ADC</sub> | Supply current per ADC     |                         | _    | 0.6               | _                                                    | mA               | 3          |

| SMPLTS               | Sample Time                |                         | 275  | _                 | Refer to<br>the<br><i>Reference</i><br><i>Manual</i> | ns               |            |

| TUE <sup>4</sup>     | Total unadjusted error     |                         | _    | ±4                | ±8                                                   | LSB <sup>5</sup> | 6, 7, 8, 9 |

| DNL                  | Differential non-linearity |                         | —    | ±1.0              | —                                                    | LSB <sup>5</sup> | 6, 7, 8, 9 |

| INL                  | Integral non-linearity     |                         | _    | ±2.0              | —                                                    | LSB <sup>5</sup> | 6, 7, 8, 9 |

Table 28. 12-bit ADC characteristics (2.7 V to 3 V) ( $V_{REFH} = V_{DDA}$ ,  $V_{REFL} = V_{SS}$ )

- 1. All accuracy numbers assume the ADC is calibrated with V<sub>REFH</sub>=V<sub>DDA</sub>=V<sub>DD</sub>, with the calibration frequency set to less than or equal to half of the maximum specified ADC clock frequency.

- 2. Typical values assume V<sub>DDA</sub> = 3 V, Temp = 25 °C,  $f_{ADCK}$  = 40 MHz, R<sub>AS</sub>=20  $\Omega$ , and C<sub>AS</sub>=10 nF.

- 3. The ADC supply current depends on the ADC conversion rate.

- 4. Represents total static error, which includes offset and full scale error.

- 5. 1 LSB =  $(V_{REFH} V_{REFL})/2^N$

- 6. The specifications are with averaging and in standalone mode only. Performance may degrade depending upon device use case scenario. When using ADC averaging, refer to the *Reference Manual* to determine the most appropriate settings for AVGS.

- For ADC signals adjacent to V<sub>DD</sub>/V<sub>SS</sub> or XTAL/EXTAL or high frequency switching pins, some degradation in the ADC performance may be observed.

- 8. All values guarantee the performance of the ADC for multiple ADC input channel pins. When using ADC to monitor the internal analog parameters, assume minor degradation.

- 9. All the parameters in the table are given assuming system clock as the clocking source for ADC.

| Symbol                                                                    | Description                                            | Min.  | Тур. | Max. | Unit             |

|---------------------------------------------------------------------------|--------------------------------------------------------|-------|------|------|------------------|

|                                                                           | Analog comparator hysteresis, Hyst2, Low-speed mode    |       |      |      |                  |

|                                                                           | -40 - 125 °C                                           | _     | 23   | 80   |                  |

| V <sub>HYST3</sub> Analog comparator hysteresis, Hyst3, High-spee<br>mode |                                                        |       |      |      | mV               |

|                                                                           | -40 - 125 °C                                           | _     | 46   | 200  |                  |

|                                                                           | Analog comparator hysteresis, Hyst3, Low-speed<br>mode |       |      |      |                  |

|                                                                           | -40 - 125 °C                                           | _     | 32   | 120  |                  |

| I <sub>DAC8b</sub>                                                        | 8-bit DAC current adder (enabled)                      |       |      |      |                  |

|                                                                           | 3.3V Reference Voltage                                 | _     | 6    | 9    | μA               |

|                                                                           | 5V Reference Voltage                                   | _     | 10   | 16   | μA               |

| INL <sup>5</sup>                                                          | 8-bit DAC integral non-linearity                       | -0.75 | —    | 0.75 | LSB <sup>6</sup> |

| DNL                                                                       | 8-bit DAC differential non-linearity                   | -0.5  | _    | 0.5  | LSB <sup>6</sup> |

| t <sub>DDAC</sub>                                                         | Initialization and switching settling time             | _     | —    | 30   | μs               |

Table 31. Comparator with 8-bit DAC electrical specifications (continued)

1. Difference at input > 200mV

2. Applied  $\pm$  (100 mV + V<sub>HYST0/1/2/3</sub>+ max. of V<sub>AIO</sub>) around switch point.

3. Applied ± (30 mV + 2 ×  $V_{HYST0/1/2/3}$ + max. of  $V_{AIO}$ ) around switch point.

4. Applied  $\pm$  (100 mV + V<sub>HYST0/1/2/3</sub>).

5. Calculation method used: Linear Regression Least Square Method

6. 1 LSB =  $V_{reference}/256$

## NOTE

For comparator IN signals adjacent to  $V_{DD}/V_{SS}$  or XTAL/ EXTAL or switching pins cross coupling may happen and hence hysteresis settings can be used to obtain the desired comparator performance. Additionally, an external capacitor (1nF) should be used to filter noise on input signal. Also, source drive should not be weak (Signal with < 50 K pull up/down is recommended).

**Communication modules**

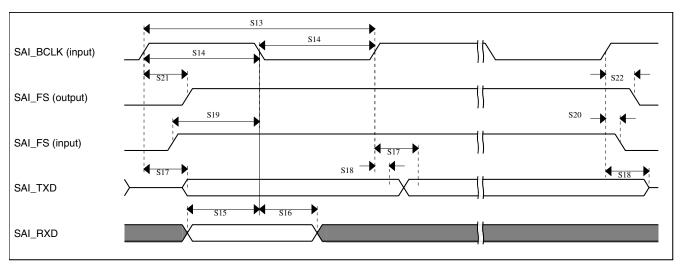

Figure 23. SAI Timing — Slave modes

# 6.5.6 Ethernet AC specifications

The following timing specs are defined at the chip I/O pin and must be translated appropriately to arrive at timing specs/constraints for the physical interface.

The following table describes the MII electrical characteristics.

- Measurements are with maximum output load of 25 pF, input transition of 1 ns and pad configured with fastest slew settings (DSE = 1'b1).

- I/O operating voltage ranges from 2.97 V to 3.6 V

- While doing the mode transition (RUN -> HSRUN or HSRUN -> RUN ), the interface should be OFF.

| Symbol | Description                           | Min. | Max. | Unit         |

|--------|---------------------------------------|------|------|--------------|

| _      | RXCLK frequency                       | —    | 25   | MHz          |

| MII1   | RXCLK pulse width high                | 35%  | 65%  | RXCLK period |

| MII2   | RXCLK pulse width low                 | 35%  | 65%  | RXCLK period |

| MII3   | RXD[3:0], RXDV, RXER to RXCLK setup   | 5    | —    | ns           |

| MII4   | RXCLK to RXD[3:0], RXDV, RXER hold    | 5    | —    | ns           |

| _      | TXCLK frequency                       | —    | 25   | MHz          |

| MII5   | TXCLK pulse width high                | 35%  | 65%  | TXCLK period |

| MII6   | TXCLK pulse width low                 | 35%  | 65%  | TXCLK period |

| MII7   | TXCLK to TXD[3:0], TXEN, TXER invalid | 2    | —    | ns           |

| MII8   | TXCLK to TXD[3:0], TXEN, TXER valid   | —    | 25   | ns           |

Table 35. MII signal switching specifications

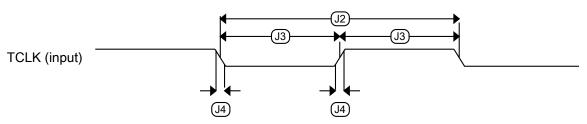

Figure 32. Test clock input timing

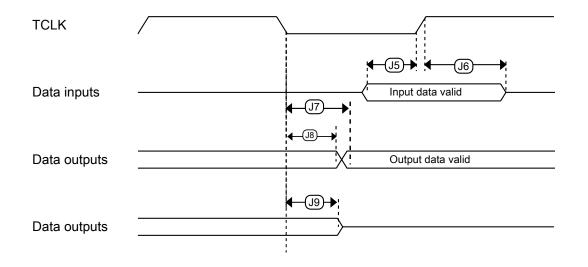

Figure 33. Boundary scan (JTAG) timing

# 7.3 General notes for specifications at maximum junction temperature

An estimation of the chip junction temperature, T<sub>J</sub>, can be obtained from this equation:

$$T_{J} = T_{A} + (R_{\theta JA} \times P_{D})$$

where:

- $T_A$  = ambient temperature for the package (°C)

- $R_{\theta JA}$  = junction to ambient thermal resistance (°C/W)

- $P_D$  = power dissipation in the package (W)

The junction to ambient thermal resistance is an industry standard value that provides a quick and easy estimation of thermal performance. Unfortunately, there are two values in common usage: the value determined on a single layer board and the value obtained on a board with two planes. For packages such as the PBGA, these values can be different by a factor of two. Which value is closer to the application depends on the power dissipated by other components on the board. The value obtained on a single layer board is appropriate for the tightly packed printed circuit board. The value obtained on the board with the internal planes is usually appropriate if the board has low power dissipation and the components are well separated.

When a heat sink is used, the thermal resistance is expressed in the following equation as the sum of a junction-to-case thermal resistance and a case-to-ambient thermal resistance:

# $R_{\theta JA} = R_{\theta JC} + R_{\theta CA}$

where:

- $R_{\theta JA}$  = junction to ambient thermal resistance (°C/W)

- $R_{\theta JC}$  = junction to case thermal resistance (°C/W)

- $R_{\theta CA}$  = case to ambient thermal resistance (°C/W)

$R_{\theta JC}$  is device related and cannot be influenced by the user. The user controls the thermal environment to change the case to ambient thermal resistance,  $R_{\theta CA}$ . For instance, the user can change the size of the heat sink, the air flow around the device, the interface material, the mounting arrangement on printed circuit board, or change the thermal dissipation on the printed circuit board surrounding the device.

| Table 43. Revision History | y (continued) |

|----------------------------|---------------|

|----------------------------|---------------|