#### NXP USA Inc. - FS32K144HRT0MLHT Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4F                                                         |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 80MHz                                                                    |

| Connectivity               | CANbus, FlexIO, I <sup>2</sup> C, LINbus, SPI, UART/USART                |

| Peripherals                | POR, PWM, WDT                                                            |

| Number of I/O              | 58                                                                       |

| Program Memory Size        | 512KB (512K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 4K x 8                                                                   |

| RAM Size                   | 64K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| Data Converters            | A/D 16x12b SAR; D/A1x8b                                                  |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-LQFP                                                                  |

| Supplier Device Package    | 64-LQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/fs32k144hrt0mlht |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Communications interfaces

- Up to three Low Power Universal Asynchronous Receiver/Transmitter (LPUART/LIN) modules with DMA support and low power availability

- Up to three Low Power Serial Peripheral Interface (LPSPI) modules with DMA support and low power availability

- Up to two Low Power Inter-Integrated Circuit (LPI2C) modules with DMA support and low power availability

- Up to three FlexCAN modules (with optional CAN-FD support)

- FlexIO module for emulation of communication protocols and peripherals (UART, I2C, SPI, I2S, LIN, PWM, etc).

- Up to one 10/100Mbps Ethernet with IEEE1588 support and two Synchronous Audio Interface (SAI) modules.

- Safety and Security

- Cryptographic Services Engine (CSEc) implements a comprehensive set of cryptographic functions as described in the SHE (Secure Hardware Extension) Functional Specification. Note: CSEc (Security) or EEPROM writes/erase will trigger error flags in HSRUN mode (112 MHz) because this use case is not allowed to execute simultaneously. The device will need to switch to RUN mode (80 MHz) to execute CSEc (Security) or EEPROM writes/erase.

- 128-bit Unique Identification (ID) number

- Error-Correcting Code (ECC) on flash and SRAM memories

- System Memory Protection Unit (System MPU)

- Cyclic Redundancy Check (CRC) module

- Internal watchdog (WDOG)

- External Watchdog monitor (EWM) module

- Timing and control

- Up to eight independent 16-bit FlexTimers (FTM) modules, offering up to 64 standard channels (IC/OC/PWM)

- One 16-bit Low Power Timer (LPTMR) with flexible wake up control

- Two Programmable Delay Blocks (PDB) with flexible trigger system

- One 32-bit Low Power Interrupt Timer (LPIT) with 4 channels

- 32-bit Real Time Counter (RTC)

- Package

- 32-pin QFN, 48-pin LQFP, 64-pin LQFP, 100-pin LQFP, 100-pin MAPBGA, 144-pin LQFP, 176-pin LQFP package options

- 16 channel DMA with up to 63 request sources using DMAMUX

#### Feature comparison

### Description Input Multiplexing sheet(s) attached with Reference Manual.

|               |                                                                                                    | S32                                                   | K11x                                      | S32K14x<br>K142 K144 K146 H |                                               |                                                               |                                                |  |

|---------------|----------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------|-----------------------------|-----------------------------------------------|---------------------------------------------------------------|------------------------------------------------|--|

|               | Parameter                                                                                          | K116                                                  | K118                                      | K142                        | K144                                          | K146                                                          | K148                                           |  |

|               | Core                                                                                               | Arr                                                   | n <sup>®</sup> Cortex™-M0+                |                             | Arr                                           | n <sup>®</sup> Cortex™-M4F                                    |                                                |  |

|               | Frequency                                                                                          | 48                                                    | MHz                                       | 80 MH                       | z (RUN mode) or 1                             | 12 MHz (HSRUN 1                                               | mode)1                                         |  |

|               | IEEE-754 FPU                                                                                       |                                                       | c                                         |                             |                                               | •                                                             |                                                |  |

|               | Cryptographic Services Engine (CSEc) <sup>1</sup>                                                  |                                                       | •                                         |                             |                                               | •                                                             |                                                |  |

|               | CRC module                                                                                         | 1                                                     | x                                         |                             | 1                                             | x                                                             |                                                |  |

|               | ISO 26262                                                                                          | capable u                                             | o to ASIL-B                               |                             | capable u                                     | o to ASIL-B                                                   |                                                |  |

|               | Peripheral speed                                                                                   | up to 4                                               | 8 MHz                                     |                             | up to 112 M                                   | Hz (HSRUN)                                                    |                                                |  |

|               | Crossbar                                                                                           |                                                       | •                                         |                             |                                               | •                                                             |                                                |  |

| E             | DMA                                                                                                |                                                       | •                                         |                             |                                               | •                                                             |                                                |  |

| System        | External Watchdog Monitor (EWM)                                                                    |                                                       | 0                                         |                             |                                               | •                                                             |                                                |  |

| sy            | Memory Protection Unit (MPU)                                                                       |                                                       | •                                         |                             |                                               | •                                                             |                                                |  |

|               | FIRC CMU                                                                                           |                                                       | •                                         |                             |                                               | 0                                                             |                                                |  |

|               | Watchdog                                                                                           | 1                                                     | x                                         |                             | 1                                             | x                                                             |                                                |  |

|               | Low power modes                                                                                    |                                                       | •                                         |                             |                                               | •                                                             |                                                |  |

|               | HSRUN mode1                                                                                        |                                                       | <b>o</b>                                  |                             |                                               | •                                                             |                                                |  |

|               | Number of I/Os                                                                                     | up to 43                                              | up to 58                                  | up t                        | io 89                                         | up to 128                                                     | up to 156                                      |  |

|               | Single supply voltage                                                                              | 2.7 -                                                 | 5.5 V                                     |                             | 2.7 -                                         | 5.5 V                                                         |                                                |  |

|               | Ambient Operation Temperature (Ta)                                                                 | -40°C to +105                                         | 5ºC / +125ºC                              |                             | -40°C to +10                                  | 5°C / +125°C                                                  |                                                |  |

|               | Flash                                                                                              | 128 KB                                                | 256 KB                                    | 256 KB                      | 512 KB                                        | 1 MB                                                          | 2 MB <sup>2</sup>                              |  |

|               | Error Correcting Code (ECC)                                                                        |                                                       | •                                         |                             |                                               | •                                                             |                                                |  |

|               | System RAM (including FlexRAM and MTB)                                                             | 17 KB                                                 | 25 KB                                     | 32 KB                       | 64 KB                                         | 128 KB                                                        | 256 KB                                         |  |

| Ž             | FlexRAM (also available as system RAM)                                                             |                                                       | KB                                        | -                           |                                               | KB                                                            |                                                |  |

| Memory        | Cache                                                                                              |                                                       | o                                         |                             | 4                                             | KB                                                            |                                                |  |

| Σ             | EEPROM emulated by FlexRAM <sup>1</sup>                                                            | 2 KB (up to 3                                         | 2 KB D-Flash)                             | 4 KE                        | 3 (up to 64 KB D-F                            | lash)                                                         | See footnote 3                                 |  |

|               | External memory interface                                                                          |                                                       | 0                                         |                             | 0                                             |                                                               | QuadSPI incl.<br>HyperBus™                     |  |

|               | Low Power Interrupt Timer (LPIT)                                                                   | 1                                                     | x                                         |                             | 1                                             | x                                                             |                                                |  |

| ÷             | FlexTimer (16-bit counter) 8 channels                                                              | 2x                                                    | (16)                                      | 4x                          | (32)                                          | 6x (48)                                                       | 8x (64)                                        |  |

| Timer         | Low Power Timer (LPTMR)                                                                            | 1                                                     | x                                         |                             | 1                                             | x                                                             |                                                |  |

| -             | Real Time Counter (RTC)                                                                            | 1                                                     | x                                         |                             | 1                                             | x                                                             |                                                |  |

|               | Programmable Delay Block (PDB)                                                                     | 1                                                     | х                                         |                             | 2                                             | 2x                                                            |                                                |  |

| bo            | Trigger mux (TRGMUX)                                                                               | 1x (43)                                               | 1x (45)                                   | 1x                          | (64)                                          | 1x (73)                                                       | 1x (81)                                        |  |

| Analog        | 12-bit SAR ADC (1 Msps each)                                                                       | 1x (13)                                               | 1x (16)                                   | 2x                          | (16)                                          | 2x (24)                                                       | 2x (32)                                        |  |

| A             | Comparator with 8-bit DAC                                                                          | 1                                                     | x                                         |                             | 1                                             | x                                                             |                                                |  |

|               | 10/100 Mbps IEEE-1588 Ethernet MAC                                                                 |                                                       | 0                                         |                             | 0                                             |                                                               | 1x                                             |  |

| Ę             | Serial Audio Interface (AC97, TDM, I2S)                                                            |                                                       | c                                         |                             | 0                                             |                                                               | 2x                                             |  |

| Communication | Low Power UART/LIN (LPUART)<br>(Supports LIN protocol versions 1.3, 2.0, 2.1, 2.2A, and SAE J2602) | 2                                                     | x                                         | 2x                          |                                               | Зх                                                            |                                                |  |

| Ē             | Low Power SPI (LPSPI)                                                                              | 1x                                                    | 2x                                        | 2x                          |                                               | Зx                                                            |                                                |  |

| E C           | Low Power I2C (LPI2C)                                                                              |                                                       | x                                         |                             | 1x                                            |                                                               | 2x                                             |  |

| 0             | FlexCAN<br>(CAN-FD ISO/CD 11898-1)                                                                 |                                                       | x<br>th FD)                               | 2x<br>(1x with FD)          | 3x<br>(1x with FD)                            | 3x3x1x with FD)(2x with FD)1x                                 |                                                |  |

|               | FlexIO (8 pins configurable as UART, SPI, I2C, I2S)                                                | 1                                                     | x                                         |                             | 1x                                            |                                                               |                                                |  |

| IDEs          | Debug & trace                                                                                      | SWD, MTB (1 KB), JTAG <sup>4</sup> SWD, JTAG (ITM, SW |                                           | JTAG (ITM, SWV,             | SWO)                                          | SWD, JTAG<br>(ITM, SWV,<br>SWO), ETM                          |                                                |  |

| -             | Ecosystem<br>(IDE, compiler, debugger)                                                             |                                                       | tudio (GCC) + SDK,<br>auterbach, iSystems | 1                           | NXP S32 Design S<br>AR, GHS, Arm®, L          | tudio (GCC) + SDł<br>auterbach, iSystem                       | ζ,<br>15                                       |  |

| Other         | Packages <sup>5</sup>                                                                              | 32-pin QFN<br>48-pin LQFP                             | 48-pin LQFP<br>64-pin LQFP                | 64-pin LQFP<br>100-pin LQFP | 64-pin LQFP<br>100-pin LQFP<br>100-pin MAPBGA | 64-pin LQFP<br>100-pin MAPBGA<br>100-pin LQFP<br>144-pin LQFP | 100-pin MAPBGA<br>144-pin LQFP<br>176-pin LQFP |  |

LEGEND:

• Not implemented

Available on the device 1 No write or erase access to Flash module, including Security (CSEc) and EEPROM commands, are allowed when device is running at HSRUN mode (112MHz) or VLPR mode.

2 Available when EEEPROM, CSEc and Data Flash are not used. Else only up to 1,984 KB is available for Program Flash.

3 4 KB (up to 512 KB D-Flash as a part of 2 MB Flash). Up to 64 KB of flash is used as EEPROM backup and the remaining 448 KB of the last 512 KB block can be used as Data flash or Program flash. See chapter FTFC for details.

4 Only for Boundary Scan Register

5 See Dimensions section for package drawings

### Figure 3. S32K1xx product series comparison

- 5.  $V_{\text{REFH}}$  should always be equal to or less than  $V_{\text{DDA}}$  + 0.1 V and  $V_{\text{DD}}$  + 0.1 V

- 6. Open drain outputs must be pulled to  $V_{DD}$ .

- 7. When input pad voltage levels are close to  $V_{DD}$  or  $V_{SS}$ , practically no current injection is possible.

## 4.3 Thermal operating characteristics

# Table 3. Thermal operating characteristics for 64 LQFP, 100 LQFP, and 100 MAP-BGApackages.

| Symbol                      | Parameter                       |      | Value |                  | Unit |

|-----------------------------|---------------------------------|------|-------|------------------|------|

|                             |                                 | Min. | Тур.  | Max.             |      |

| T <sub>A C-Grade Part</sub> | Ambient temperature under bias  | -40  | —     | 85 <sup>1</sup>  | °C   |

| T <sub>J C-Grade Part</sub> | Junction temperature under bias | -40  | —     | 105 <sup>1</sup> | °C   |

| T <sub>A V-Grade Part</sub> | Ambient temperature under bias  | -40  | _     | 105 <sup>1</sup> | °C   |

| T <sub>J V-Grade Part</sub> | Junction temperature under bias | -40  | —     | 125 <sup>1</sup> | °C   |

| T <sub>A M-Grade Part</sub> | Ambient temperature under bias  | -40  | —     | 125 <sup>2</sup> | °C   |

| T <sub>J M-Grade Part</sub> | Junction temperature under bias | -40  | —     | 135 <sup>2</sup> | °C   |

1. Values mentioned are measured at  $\leq$  112 MHz in HSRUN mode.

2. Values mentioned are measured at  $\leq$  80 MHz in RUN mode.

### Table 4. Supplies decoupling capacitors 1, 2

| Symbol                                                      | Description                               | Min. <sup>3</sup> | Тур. | Max. | Unit |

|-------------------------------------------------------------|-------------------------------------------|-------------------|------|------|------|

| C <sub>REF</sub> <sup>, 4</sup> , <sup>5</sup>              | ADC reference high decoupling capacitance | 70                | 100  |      | nF   |

| C <sub>DEC</sub> <sup>5</sup> , <sup>6</sup> , <sup>7</sup> | Recommended decoupling capacitance        | 70                | 100  |      | nF   |

V<sub>DD</sub> and V<sub>DDA</sub> must be shorted to a common source on PCB. The differential voltage between V<sub>DD</sub> and V<sub>DDA</sub> is for RF-AC only. Appropriate decoupling capacitors to be used to filter noise on the supplies. See application note AN5032 for reference supply design for SAR ADC. All V<sub>SS</sub> pins should be connected to common ground at the PCB level.

2. All decoupling capacitors must be low ESR ceramic capacitors (for example X7R type).

3. Minimum recommendation is after considering component aging and tolerance.

4. For improved performance, it is recommended to use 10 µF, 0.1 µF and 1 nF capacitors in parallel.

5. All decoupling capacitors should be placed as close as possible to the corresponding supply and ground pins.

6. Contact your local Field Applications Engineer for details on best analog routing practices.

7. The filtering used for decoupling the device supplies must comply with the following best practices rules:

• The protection/decoupling capacitors must be on the path of the trace connected to that component.

• No trace exceeding 1 mm from the protection to the trace or to the ground.

• The protection/decoupling capacitors must be as close as possible to the input pin of the device (maximum 2 mm).

• The ground of the protection is connected as short as possible to the ground plane under the integrated circuit.

| Symbol                | Description                           | Min. | Тур.  | Max. | Unit | Notes |

|-----------------------|---------------------------------------|------|-------|------|------|-------|

| V <sub>LVW</sub>      | Falling low-voltage warning threshold | 4.19 | 4.305 | 4.5  | V    |       |

| V <sub>LVW_HYST</sub> | LVW hysteresis                        | —    | 75    | —    | mV   | 1     |

| V <sub>BG</sub>       | Bandgap voltage reference             | 0.97 | 1.00  | 1.03 | V    |       |

Table 5. V<sub>DD</sub> supply LVR, LVD and POR operating requirements (continued)

1. Rising threshold is the sum of falling threshold and hysteresis voltage.

# 4.6 Power mode transition operating behaviors

All specifications in the following table assume this clock configuration:

- RUN Mode:

- Clock source: FIRC

- SYS\_CLK/CORE\_CLK = 48 MHz

- $BUS_CLK = 48 MHz$

- FLASH\_CLK = 24 MHz

- HSRUN Mode:

- Clock source: SPLL

- SYS\_CLK/CORE\_CLK = 112 MHz

- BUS\_CLK = 56 MHz

- FLASH\_CLK = 28 MHz

- VLPR Mode:

- Clock source: SIRC

- SYS\_CLK/CORE\_CLK = 4 MHz

- $BUS_CLK = 4 MHz$

- FLASH\_CLK = 1 MHz

- STOP1/STOP2 Mode:

- Clock source: FIRC

- SYS\_CLK/CORE\_CLK = 48 MHz

- $BUS\_CLK = 48 MHz$

- FLASH\_CLK = 24 MHz

- VLPS Mode: All clock sources disabled <sup>1</sup>

### Table 6. Power mode transition operating behaviors

| Symbol           | Description                                                                                                                                                       | Min. | Тур. | Max. | Unit |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| t <sub>POR</sub> | After a POR event, amount of time from the point $V_{DD}$ reaches 2.7 V to execution of the first instruction across the operating temperature range of the chip. | —    | 325  | _    | μs   |

Table continues on the next page...

- 1. For S32K11x FIRC/SOSC

- For S32K14x FIRC/SOSC/SPLL

S32K1xx Data Sheet, Rev. 8, 06/2018

### Table 7. Power consumption (Typicals unless stated otherwise) 1 (continued)

|             |                          |     | VLPS (                            | μΑ) <sup>2</sup>    | V                                 | LPR (m                                      | A)                                          | STOP1<br>(mA) | STOP2<br>(mA) |                      | l@48<br>(mA)        |                      | 64 MHz<br>nA)       |                      | 80 MHz<br>nA)       |                      | N@112<br>(mA) <sup>3</sup> |                               |

|-------------|--------------------------|-----|-----------------------------------|---------------------|-----------------------------------|---------------------------------------------|---------------------------------------------|---------------|---------------|----------------------|---------------------|----------------------|---------------------|----------------------|---------------------|----------------------|----------------------------|-------------------------------|

| Chip/Device | Ambient Temperature (°C) |     | Peripherals disabled <sup>5</sup> | Peripherals enabled | Peripherals disabled <sup>6</sup> | Peripherals enabled use case 1 <sup>6</sup> | Peripherals enabled use case 2 <sup>7</sup> |               |               | Peripherals disabled | Peripherals enabled        | IDD/MHz (µA/MHz) <sup>4</sup> |

|             |                          | Max | 1660                              | 1736                | 3.48                              | 3.55                                        | NA                                          | 14.5          | 15.6          | 34.8                 | 43.6                | 41.9                 | 53.9                | 48.7                 | 65.1                | 70.4                 | 96.1                       | 609                           |

|             | 105                      | Тур | 560                               | 577                 | 2.49                              | 2.54                                        | 4.03                                        | 10.9          | 11.9          | 29.8                 | 37.8                | 37.6                 | 47.5                | 45.2                 | 61.5                | 63.8                 | 89.1                       | 565                           |

|             |                          | Max | 2945                              | 2970                | 4.40                              | 4.47                                        | NA                                          | 18.0          | 19.0          | 38.4                 | 46.8                | 44.9                 | 55.3                | 51.6                 | 66.8                | 73.6                 | 97.4                       | 645                           |

|             | 125                      | Тур | NA                                | NA                  | NA                                | NA                                          | 4.85                                        | NA            | NA            | NA                   | NA                  | NA                   | NA                  | NA                   | NA                  | N                    | İA                         | NA                            |

|             |                          | Max | 3990                              | 4166                | 6.00                              | 6.08                                        | NA                                          | 23.4          | 24.5          | 44.3                 | 52.5                | 50.9                 | 61.3                | 57.5                 | 71.6                | N                    | IA                         | 719                           |

S32K1xx Data Sheet, Rev. 8, 06/2018

- Typical current numbers are indicative for typical silicon process and may vary based on the silicon distribution and user configuration. Typical conditions assumes

V<sub>DD</sub> = V<sub>DDA</sub> = V<sub>REFH</sub> = 5 V, temperature = 25 °C and typical silicon process unless otherwise stated. All output pins are floating and On-chip pulldown is enabled for

all unused input pins.

- 2. Current numbers are for reduced configuration and may vary based on user configuration and silicon process variation.

- 3. HSRUN mode must not be used at 125°C. Max ambient temperature for HSRUN mode is 105°C.

- 4. Values mentioned for S32K14x devices are measured at RUN@80 MHz with peripherals disabled and values mentioned for S32K11x devices are measured at RUN@48 MHz with peripherals disabled.

- 5. With PMC\_REGSC[CLKBIASDIS] set to 1. See Reference Manual for details.

- 6. Data collected using RAM

- 7. Numbers on limited samples size and data collected with Flash

- 8. The S32K148 data points assume that ENET/QuadSPI/SAI etc. are inactive.

# Table 17. External System Oscillator electrical specifications (continued)

| Symbol          | Description                                             | Min. | Тур. | Max. | Unit | Notes |

|-----------------|---------------------------------------------------------|------|------|------|------|-------|

|                 | High-gain mode (HGO=1)                                  | —    | 1    | _    | MΩ   |       |

| R <sub>S</sub>  | Series resistor                                         |      |      |      |      |       |

|                 | Low-gain mode (HGO=0)                                   | _    | 0    | _    | kΩ   |       |

|                 | High-gain mode (HGO=1)                                  | _    | 0    | _    | kΩ   |       |

| V <sub>pp</sub> | Peak-to-peak amplitude of oscillation (oscillator mode) |      |      |      |      | 3     |

|                 | Low-gain mode (HGO=0)                                   | _    | 1.0  | _    | V    |       |

|                 | High-gain mode (HGO=1)                                  |      | 3.3  | _    | V    |       |

1. Crystal oscillator circuit provides stable oscillations when  $g_{mXOSC} > 5 * gm_{crit}$ . The gm\_crit is defined as:

gm\_crit = 4 \* ESR \*  $(2\pi F)^2$  \*  $(C_0 + C_L)^2$

where:

2.

- $g_{mXOSC}$  is the transconductance of the internal oscillator circuit

- ESR is the equivalent series resistance of the external crystal

- F is the external crystal oscillation frequency

- C<sub>0</sub> is the shunt capacitance of the external crystal

- $C_L$  is the external crystal total load capacitance.  $C_L = C_s + [C_1 * C_2 / (C_1 + C_2)]$

- $C_s$  is stray or parasitic capacitance on the pin due to any PCB traces

- $C_1$ ,  $C_2$  external load capacitances on EXTAL and XTAL pins

See manufacture datasheet for external crystal component values

- When low-gain is selected, internal R<sub>F</sub> will be selected and external R<sub>F</sub> should not be attached.

- When high-gain is selected, external R<sub>F</sub> (1 M Ohm) needs to be connected for proper operation of the crystal. For external resistor, up to 5% tolerance is allowed.

- 3. The EXTAL and XTAL pins should only be connected to required oscillator components and must not be connected to any other devices.

# 6.2.2 External System Oscillator frequency specifications

### 6.2.4 Low Power Oscillator (LPO) electrical specifications Table 21. Low Power Oscillator (LPO) electrical specifications

| Symbol               | Parameter                               | Min. | Тур. | Max. | Unit |

|----------------------|-----------------------------------------|------|------|------|------|

| F <sub>LPO</sub>     | Internal low power oscillator frequency | 113  | 128  | 139  | kHz  |

| T <sub>startup</sub> | Startup Time                            | _    | _    | 20   | μs   |

# 6.2.5 SPLL electrical specifications

Table 22. SPLL electrical specifications

| Symbol                               | Parameter                                          | Min.   | Тур. | Max.                                                       | Unit |

|--------------------------------------|----------------------------------------------------|--------|------|------------------------------------------------------------|------|

| F <sub>SPLL_REF</sub> <sup>1</sup>   | PLL Reference Frequency Range                      | 8      | —    | 16                                                         | MHz  |

| F <sub>SPLL_Input</sub> <sup>2</sup> | PLL Input Frequency                                | 8      | —    | 40                                                         | MHz  |

| F <sub>VCO_CLK</sub>                 | VCO output frequency                               | 180    | —    | 320                                                        | MHz  |

| F <sub>SPLL_CLK</sub>                | PLL output frequency                               | 90     | —    | 160                                                        | MHz  |

| J <sub>CYC_SPLL</sub>                | PLL Period Jitter (RMS) <sup>3</sup>               | •      | ·    |                                                            |      |

|                                      | at F <sub>VCO_CLK</sub> 180 MHz                    | _      | 120  | —                                                          | ps   |

|                                      | at F <sub>VCO_CLK</sub> 320 MHz                    | _      | 75   | —                                                          | ps   |

| J <sub>ACC_SPLL</sub>                | PLL accumulated jitter over 1µs (RMS) <sup>3</sup> |        |      |                                                            |      |

|                                      | at F <sub>VCO_CLK</sub> 180 MHz                    | _      | 1350 | —                                                          | ps   |

|                                      | at F <sub>VCO_CLK</sub> 320 MHz                    | _      | 600  | —                                                          | ps   |

| D <sub>UNL</sub>                     | Lock exit frequency tolerance                      | ± 4.47 | —    | ± 5.97                                                     | %    |

| T <sub>SPLL_LOCK</sub>               | Lock detector detection time <sup>4</sup>          | —      | _    | 150 × 10 <sup>-6</sup> +<br>1075(1/F <sub>SPLL_REF</sub> ) | S    |

1. F<sub>SPLL\_REF</sub> is PLL reference frequency range after the PREDIV. For PREDIV and MULT settings refer SCG\_SPLLCFG register of Reference Manual.

F<sub>SPLL\_Input</sub> is PLL input frequency range before the PREDIV must be limited to the range 8 MHz to 40 MHz. This input source could be derived from a crystal oscillator or some other external square wave clock source using OSC bypass mode. For external clock source settings refer SCG\_SOSCCFG register of Reference Manual.

3. This specification was obtained using a NXP developed PCB. PLL jitter is dependent on the noise characteristics of each PCB and results will vary

4. Lock detector detection time is defined as the time between PLL enablement and clock availability for system use.

# 6.3 Memory and memory interfaces

## 6.3.1 Flash memory module (FTFC) electrical specifications

This section describes the electrical characteristics of the flash memory module.

### 6.3.1.1 Flash timing specifications — commands Table 23. Flash command timing specifications for S32K14x

| Symbol                | Descrip                                          | tion <sup>1</sup>         | S32 | K142 | S3  | 2K144 | S32 | K146  | S32  | 2K148    |      |       |

|-----------------------|--------------------------------------------------|---------------------------|-----|------|-----|-------|-----|-------|------|----------|------|-------|

|                       |                                                  |                           | Тур | Max  | Тур | Max   | Тур | Max   | Тур  | Max      | Unit | Notes |

| t <sub>rd1blk</sub>   | Read 1 Block                                     | 32 KB flash               | _   | _    | _   | _     | _   |       | _    | _        | ms   |       |

|                       | execution time                                   | 64 KB flash               |     | 0.5  | _   | 0.5   | _   | 0.5   | _    | _        |      |       |

|                       |                                                  | 128 KB flash              | _   | _    | _   | _     | _   | _     | _    | <u> </u> | -    |       |

|                       |                                                  | 256 KB flash              | _   | 2    | _   | —     | _   | _     | —    | -        | 1    |       |

|                       |                                                  | 512 KB flash              | _   | —    | -   | 1.8   | —   | 2     | —    | 2        |      |       |

| t <sub>rd1sec</sub>   | Read 1 Section                                   | 2 KB flash                | —   | 75   | —   | 75    | _   | 75    | —    | 75       | μs   |       |

|                       | execution time                                   | 4 KB flash                | —   | 100  | -   | 100   | —   | 100   | —    | 100      | 1    |       |

| t <sub>pgmchk</sub>   | Program Check<br>execution time                  | —                         | _   | 95   | -   | 95    | -   | 95    |      | 100      | μs   |       |

| t <sub>pgm8</sub>     | Program Phrase execution time                    | —                         | 90  | 225  | 90  | 225   | 90  | 225   | 90   | 225      | μs   |       |

| t <sub>ersblk</sub>   | Erase Flash                                      | 32 KB flash               | —   | —    | -   | —     | —   | —     | —    | -        | ms   | 2     |

|                       | Block execution time                             | 64 KB flash               | 30  | 550  | 30  | 550   | 30  | 550   | —    | -        | 1    |       |

|                       |                                                  | 128 KB flash              | —   | —    | —   | —     | —   | —     | —    | -        | 1    |       |

|                       |                                                  | 256 KB flash              | 250 | 2125 | —   | —     | —   | —     | —    | —        |      |       |

|                       |                                                  | 512 KB flash              | —   | —    | 250 | 4250  | 250 | 4250  | 250  | 4250     |      |       |

| t <sub>ersscr</sub>   | Erase Flash<br>Sector execution<br>time          |                           | 12  | 130  | 12  | 130   | 12  | 130   | 12   | 130      | ms   | 2     |

| t <sub>pgmsec1k</sub> | Program Section<br>execution time<br>(1KB flash) |                           | 5   | _    | 5   | -     | 5   | _     | 5    | —        | ms   |       |

| t <sub>rd1all</sub>   | Read 1s All<br>Block execution<br>time           |                           | _   | 2.8  | _   | 2.3   | -   | 5.2   | —    | 8.2      | ms   |       |

| t <sub>rdonce</sub>   | Read Once<br>execution time                      | _                         | -   | 30   | —   | 30    | -   | 30    | -    | 30       | μs   |       |

| t <sub>pgmonce</sub>  | Program Once<br>execution time                   | —                         | 90  | —    | 90  | —     | 90  | —     | 90   | -        | μs   |       |

| t <sub>ersall</sub>   | Erase All Blocks execution time                  | —                         | 250 | 2800 | 400 | 4900  | 700 | 10000 | 1400 | 17000    | ms   | 2     |

| t <sub>vfykey</sub>   | Verify Backdoor<br>Access Key<br>execution time  | _                         | _   | 35   | _   | 35    | -   | 35    | -    | 35       | μs   |       |

| t <sub>ersallu</sub>  | Erase All Blocks<br>Unsecure<br>execution time   |                           | 250 | 2800 | 400 | 4900  | 700 | 10000 | 1400 | 17000    | ms   | 2     |

| t <sub>pgmpart</sub>  | Program<br>Partition for<br>EEPROM               | 32 KB<br>EEPROM<br>backup | 70  | _    | 70  | _     | 70  | —     | —    | —        | ms   | 3     |

|                       | execution time                                   | 64 KB<br>EEPROM<br>backup | 71  | _    | 71  | -     | 71  | —     | 150  | —        |      |       |

Table continues on the next page...

#### Memory and memory interfaces

| Symbol                  | Descrip                                                             | tion <sup>1</sup>                                       | S32  | K142 | S3   | 2K144 | S32  | K146 | S32  | 2K148 |      |                                 |

|-------------------------|---------------------------------------------------------------------|---------------------------------------------------------|------|------|------|-------|------|------|------|-------|------|---------------------------------|

|                         |                                                                     |                                                         | Тур  | Max  | Тур  | Max   | Тур  | Max  | Тур  | Max   | Unit | Notes                           |

| t <sub>setram</sub>     | Set FlexRAM<br>Function                                             | Control<br>Code 0xFF                                    | 0.08 | —    | 0.08 | —     | 0.08 |      | 0.08 | _     | ms   | 3                               |

|                         | execution time                                                      | 32 KB<br>EEPROM<br>backup                               | 0.8  | 1.2  | 0.8  | 1.2   | 0.8  | 1.2  | _    | -     |      |                                 |

|                         |                                                                     | 48 KB<br>EEPROM<br>backup                               | 1    | 1.5  | 1    | 1.5   | 1    | 1.5  |      | _     |      |                                 |

|                         |                                                                     | 64 KB<br>EEPROM<br>backup                               | 1.3  | 1.9  | 1.3  | 1.9   | 1.3  | 1.9  | 1.3  | 1.9   |      |                                 |

| t <sub>eewr8b</sub>     | Byte write to<br>FlexRAM<br>execution time                          | 32 KB<br>EEPROM<br>backup                               | 385  | 1700 | 385  | 1700  | 385  | 1700 | _    | -     | μs   | 3 <sup>,</sup> 4                |

|                         |                                                                     | 48 KB<br>EEPROM<br>backup                               | 430  | 1850 | 430  | 1850  | 430  | 1850 | _    | -     |      |                                 |

|                         |                                                                     | 64 KB<br>EEPROM<br>backup                               | 475  | 2000 | 475  | 2000  | 475  | 2000 | 475  | 4000  |      |                                 |

| t <sub>eewr16b</sub>    | 16-bit write to<br>FlexRAM<br>execution time                        | 32 KB<br>EEPROM<br>backup                               | 385  | 1700 | 385  | 1700  | 385  | 1700 |      | _     | μs   | 3 <sup>,</sup> 4                |

|                         |                                                                     | 48 KB<br>EEPROM<br>backup                               | 430  | 1850 | 430  | 1850  | 430  | 1850 | _    | -     |      |                                 |

|                         |                                                                     | 64 KB<br>EEPROM<br>backup                               | 475  | 2000 | 475  | 2000  | 475  | 2000 | 475  | 4000  |      |                                 |

| t <sub>eewr32bers</sub> | 32-bit write to<br>erased FlexRAM<br>location<br>execution time     | _                                                       | 360  | 2000 | 360  | 2000  | 360  | 2000 | 360  | 2000  | μs   |                                 |

| t <sub>eewr32b</sub>    | 32-bit write to<br>FlexRAM<br>execution time                        | 32 KB<br>EEPROM<br>backup                               | 630  | 2000 | 630  | 2000  | 630  | 2000 | _    | -     | μs   | 3 <sup>,</sup> 4                |

|                         |                                                                     | 48 KB<br>EEPROM<br>backup                               | 720  | 2125 | 720  | 2125  | 720  | 2125 | _    | -     |      |                                 |

|                         |                                                                     | 64 KB<br>EEPROM<br>backup                               | 810  | 2250 | 810  | 2250  | 810  | 2250 | 810  | 4500  |      |                                 |

| t <sub>quickwr</sub>    | 32-bit Quick<br>Write execution                                     | 1st 32-bit<br>write                                     | 200  | 550  | 200  | 550   | 200  | 550  | 200  | 1100  | μs   | 4 <sup>,</sup> 5 <sup>,</sup> 6 |

|                         | time: Time from<br>CCIF clearing<br>(start the write)<br>until CCIF | 2nd through<br>Next to Last<br>(Nth-1) 32-<br>bit write | 150  | 550  | 150  | 550   | 150  | 550  | 150  | 550   |      |                                 |

Table 23. Flash command timing specifications for S32K14x (continued)

Table continues on the next page...

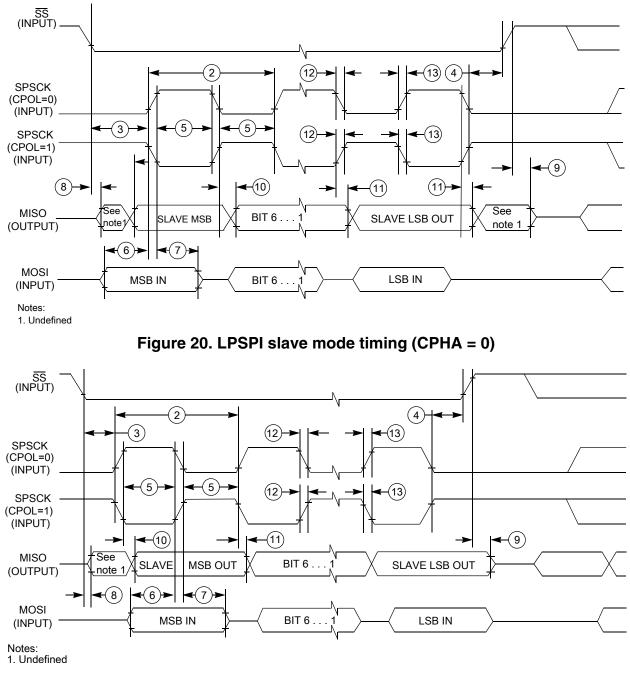

### Table 32. LPSPI electrical specifications1 (continued)

| Γ | Num | Symbol | Description | Conditions                    |      | Run Mode <sup>2</sup> |      |      |      | HSRUN | Mode <sup>2</sup> |      | VLPR Mode |      |       |      | Unit |

|---|-----|--------|-------------|-------------------------------|------|-----------------------|------|------|------|-------|-------------------|------|-----------|------|-------|------|------|

|   |     |        |             |                               | 5.0  | V IO                  | 3.3  | V IO | 5.0  | V IO  | 3.3               | V IO | 5.0       | V IO | 3.3 \ | / 10 |      |

|   |     |        |             |                               | Min. | Max.                  | Min. | Max. | Min. | Max.  | Min.              | Max. | Min.      | Max. | Min.  | Max. |      |

|   |     |        |             | Master<br>Loopback(slow)<br>6 | -    |                       | -    |      | -    |       | -                 |      | -         |      | -     |      |      |

- 1. Trace length should not exceed 11 inches for SCK pad when used in Master loopback mode.

- 2. While transitioning from HSRUN mode to RUN mode, LPSPI output clock should not be more than 14 MHz.

- 3. f<sub>periph</sub> = LPSPI peripheral clock

- 4.  $t_{periph} = 1/f_{periph}$

- 5. Master Loopback mode In this mode LPSPI\_SCK clock is delayed for sampling the input data which is enabled by setting LPSPI\_CFGR1[SAMPLE] bit as 1. Clock pads used are PTD15 and PTE0. Applicable only for LPSPI0.

- 6. Master Loopback (slow) In this mode LPSPI\_SCK clock is delayed for sampling the input data which is enabled by setting LPSPI\_CFGR1[SAMPLE] bit as 1. Clock pad used is PTB2. Applicable only for LPSPI0.

- 7. This is the maximum operating frequency (f<sub>op</sub>) for LPSPI0 with medium PAD type only. Otherwise, the maximum operating frequency (f<sub>op</sub>) is 12 Mhz.

- 8. Set the PCSSCK configuration bit as 0, for a minimum of 1 delay cycle of LPSPI baud rate clock, where PCSSCK ranges from 0 to 255.

- 9. Set the SCKPCS configuration bit as 0, for a minimum of 1 delay cycle of LPSPI baud rate clock, where SCKPCS ranges from 0 to 255.

- 10. While selecting odd dividers, ensure Duty Cycle is meeting this parameter.

- 11. Maximum operating frequency (fop ) is 12 MHz irrespective of PAD type and LPSPI instance.

- 12. Applicable for LPSPI0 only with medium PAD type, with maximum operating frequency (f<sub>op</sub>) as 14 MHz.

S32K1xx

Data

Sheet,

Rev.

,œ

06/2018

**Communication modules**

Figure 21. LPSPI slave mode timing (CPHA = 1)

# 6.5.3 LPI2C electrical specifications

See General AC specifications for LPI2C specifications.

For supported baud rate see section 'Chip-specific LPI2C information' of the *Reference Manual*.

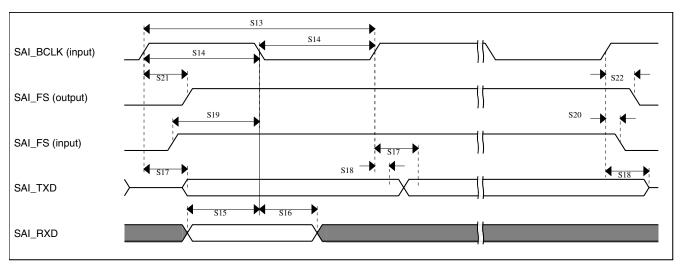

**Communication modules**

Figure 23. SAI Timing — Slave modes

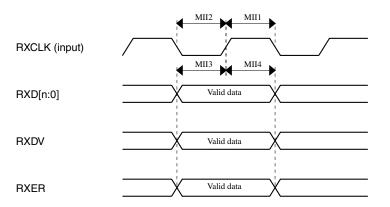

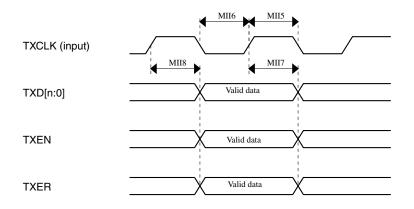

# 6.5.6 Ethernet AC specifications

The following timing specs are defined at the chip I/O pin and must be translated appropriately to arrive at timing specs/constraints for the physical interface.

The following table describes the MII electrical characteristics.

- Measurements are with maximum output load of 25 pF, input transition of 1 ns and pad configured with fastest slew settings (DSE = 1'b1).

- I/O operating voltage ranges from 2.97 V to 3.6 V

- While doing the mode transition (RUN -> HSRUN or HSRUN -> RUN ), the interface should be OFF.

| Symbol | Description                           | Min. | Max. | Unit         |

|--------|---------------------------------------|------|------|--------------|

| _      | RXCLK frequency                       | —    | 25   | MHz          |

| MII1   | RXCLK pulse width high                | 35%  | 65%  | RXCLK period |

| MII2   | RXCLK pulse width low                 | 35%  | 65%  | RXCLK period |

| MII3   | RXD[3:0], RXDV, RXER to RXCLK setup   | 5    | —    | ns           |

| MII4   | RXCLK to RXD[3:0], RXDV, RXER hold    | 5    | —    | ns           |

| _      | TXCLK frequency                       | —    | 25   | MHz          |

| MII5   | TXCLK pulse width high                | 35%  | 65%  | TXCLK period |

| MII6   | TXCLK pulse width low                 | 35%  | 65%  | TXCLK period |

| MII7   | TXCLK to TXD[3:0], TXEN, TXER invalid | 2    | —    | ns           |

| MII8   | TXCLK to TXD[3:0], TXEN, TXER valid   | —    | 25   | ns           |

Table 35. MII signal switching specifications

#### **Communication modules**

Figure 24. MII receive diagram

### Figure 25. MII transmit signal diagram

The following table describes the RMII electrical characteristics.

- Measurements are with maximum output load of 25 pF, input transition of 1 ns and pad configured with fastest slew settings (DSE = 1'b1).

- I/O operating voltage ranges from 2.97 V to 3.6 V

- While doing the mode transition (RUN -> HSRUN or HSRUN -> RUN ), the interface should be OFF.

| Symbol       | Description                              | Min. | Max. | Unit               |

|--------------|------------------------------------------|------|------|--------------------|

| —            | RMII input clock RMII_CLK Frequency      | —    | 50   | MHz                |

| RMII1, RMII5 | RMII_CLK pulse width high                | 35%  | 65%  | RMII_CLK<br>period |

| RMII2, RMII6 | RMII_CLK pulse width low                 | 35%  | 65%  | RMII_CLK<br>period |

| RMII3        | RXD[1:0], CRS_DV, RXER to RMII_CLK setup | 4    | _    | ns                 |

| RMII4        | RMII_CLK to RXD[1:0], CRS_DV, RXER hold  | 2    |      | ns                 |

Table continues on the next page...

#### S32K1xx Data Sheet, Rev. 8, 06/2018

| Symbol | Description                                        | Run Mode |          |          |          |          | HSRUN Mode |          |          |          | VLPR Mode |          |          |     |

|--------|----------------------------------------------------|----------|----------|----------|----------|----------|------------|----------|----------|----------|-----------|----------|----------|-----|

|        |                                                    | 5.0 V IO |          | 3.3 V IO |          | 5.0 V IO |            | 3.3 V IO |          | 5.0 V IO |           | 3.3 V IO |          |     |

|        |                                                    | Min.     | Max.     | Min.     | Max.     | Min.     | Max.       | Min.     | Max.     | Min.     | Max.      | Min.     | Max.     | 1   |

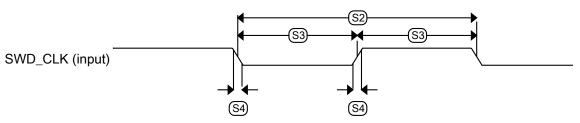

| S1     | SWD_CLK frequency of<br>operation                  | -        | 25       | -        | 25       | -        | 25         | -        | 25       | -        | 10        | -        | 10       | MHz |

| S2     | SWD_CLK cycle period                               | 1/S1     | -        | 1/S1     | -        | 1/S1     | -          | 1/S1     | -        | 1/S1     | -         | 1/S1     | -        | ns  |

| S3     | SWD_CLK clock pulse width                          | S2/2 - 5 | S2/2 + 5 | S2/2 - 5 | S2/2 + 5 | S2/2 - 5 | S2/2 + 5   | S2/2 - 5 | S2/2 + 5 | S2/2 - 5 | S2/2 + 5  | S2/2 - 5 | S2/2 + 5 | ns  |

| S4     | SWD_CLK rise and fall times                        | -        | 1        | -        | 1        | -        | 1          | -        | 1        | -        | 1         | -        | 1        | ns  |

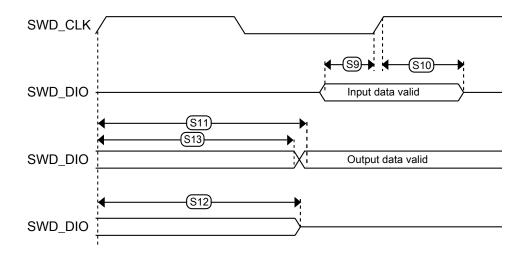

| S9     | SWD_DIO input data setup time to SWD_CLK rise      | 4        | -        | 4        | -        | 4        | -          | 4        | -        | 16       | -         | 16       | -        | ns  |

| S10    | SWD_DIO input data hold time<br>after SWD_CLK rise | 3        | -        | 3        | -        | 3        | -          | 3        | -        | 10       | -         | 10       | -        | ns  |

| S11    | SWD_CLK high to SWD_DIO data valid                 | -        | 28       | -        | 38       | -        | 28         | -        | 38       | -        | 70        | -        | 77       | ns  |

| S12    | SWD_CLK high to SWD_DIO<br>high-Z                  | -        | 28       | -        | 38       | -        | 28         | -        | 38       | -        | 70        | -        | 77       | ns  |

| S13    | SWD_CLK high to SWD_DIO data invalid               | 0        | -        | 0        | -        | 0        | -          | 0        | -        | 0        | -         | 0        | -        | ns  |

# Table 38. SWD electrical specifications

Figure 29. Serial wire clock input timing

Figure 30. Serial wire data timing

### 6.6.2 Trace electrical specifications

The following table describes the Trace electrical characteristics.

- Measurements are with maximum output load of 50 pF, input transition of 1 ns and pad configured with fastest slew settings (DSE = 1'b1).

- While doing the mode transition (RUN -> HSRUN or HSRUN -> RUN ), the interface should be OFF.

|   | Symbol | Description      | RUN Mode |    |    | HSRUI | N Mode | VLPR<br>Mode | Unit |

|---|--------|------------------|----------|----|----|-------|--------|--------------|------|

| — | Fsys   | System frequency | 80       | 48 | 40 | 112   | 80     | 4            | MHz  |

| Table 39. | Trace | specifications |

|-----------|-------|----------------|

|-----------|-------|----------------|

Table continues on the next page ...

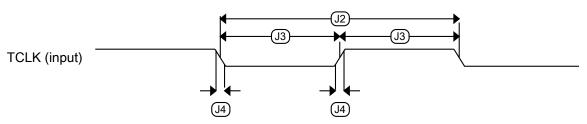

Figure 32. Test clock input timing

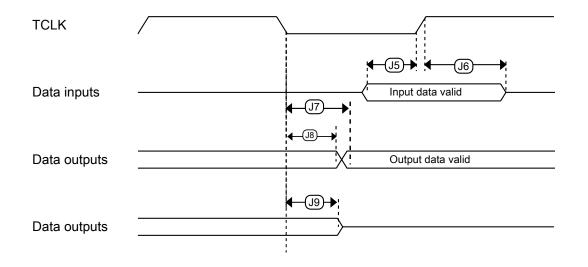

Figure 33. Boundary scan (JTAG) timing

|                                                    | -            |                                                        |         |         |         |         |         |         |         |   |

|----------------------------------------------------|--------------|--------------------------------------------------------|---------|---------|---------|---------|---------|---------|---------|---|

| Rating                                             | Conditions   | Symbol                                                 | Package |         |         | Values  |         |         |         |   |

|                                                    |              |                                                        |         | S32K116 | S32K118 | S32K142 | S32K144 | S32K146 | S32K148 |   |

|                                                    |              |                                                        | 144     | NA      | NA      | NA      | NA      | 37      | 31      | [ |

|                                                    |              |                                                        | 176     | NA      | NA      | NA      | NA      | NA      | 30      | ĺ |

| Thermal resistance, Junction to Ambient            | Four layer   | R <sub>θJMA</sub>                                      | 32      | 26      | NA      | NA      | NA      | NA      | NA      | ĺ |

| (@200 ft/min) <sup>1, 3</sup>                      | board (2s2p) |                                                        | 48      | 48      | 41      | NA      | NA      | NA      | NA      | ĺ |

|                                                    |              |                                                        | 64      | NA      | 37      | 36      | 36      | 35      | NA      | ĺ |

|                                                    |              |                                                        | 100     | NA      | NA      | 34      | 34      | 33      | NA      | ĺ |

|                                                    |              |                                                        | 144     | NA      | NA      | NA      | NA      | 36      | 30      | ĺ |

|                                                    |              |                                                        | 176     | NA      | NA      | NA      | NA      | NA      | 29      | ĺ |

| Thermal resistance, Junction to Board <sup>4</sup> | _            | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | 32      | 11      | NA      | NA      | NA      | NA      | NA      | ĺ |

|                                                    |              |                                                        | 48      | 33      | 24      | NA      | NA      | NA      | NA      | ĺ |

|                                                    |              |                                                        | 64      | NA      | 26      | 25      | 25      | 23      | NA      | ĺ |

|                                                    |              |                                                        | 25      | 24      | NA      | ĺ       |         |         |         |   |

|                                                    |              |                                                        | 144     | NA      | NA      | NA      | NA      | 30      | 24      | ĺ |

|                                                    |              |                                                        | 176     | NA      | NA      | NA      | NA      | NA      | 24      | ĺ |

| Thermal resistance, Junction to Case <sup>5</sup>  | —            | R <sub>θJC</sub>                                       | 32      | NA      | NA      | NA      | NA      | NA      | NA      | ĺ |

|                                                    |              |                                                        | 48      | 23      | 19      | NA      | NA      | NA      | NA      | ĺ |

|                                                    |              |                                                        | 64      | NA      | 14      | 13      | 12      | 11      | NA      | ĺ |

|                                                    |              |                                                        | 100     | NA      | NA      | 13      | 12      | 11      | NA      | ĺ |

|                                                    |              |                                                        | 144     | NA      | NA      | NA      | NA      | 12      | 9       | ĺ |

|                                                    |              |                                                        | 176     | NA      | NA      | NA      | NA      | NA      | 9       |   |

| Thermal resistance, Junction to Case               | _            | R <sub>0JCBottom</sub>                                 | 32      | 1       |         |         | NA      |         |         |   |

| (Bottom) <sup>6</sup>                              |              |                                                        | 48      |         |         | N       | A       |         |         |   |

|                                                    |              |                                                        | 64      |         |         |         |         |         |         | 1 |

### Table 41. Thermal characteristics for 32-pin QFN and 48/64/100/144/176-pin LQFP package (continued)

Table continues on the next page...

100 144 176

70

S32K1xx Data Sheet,

Rev. 8, 06/2018

| Rev. No. | Date        | Substantial Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |             | <ul> <li>Updated note 'All the limits defined'</li> <li>Updated parameter 'I<sub>INJPAD_DC_ABS</sub>', 'VIN_DC', I<sub>INJSUM_DC_ABS</sub>.</li> <li>In Table 2,</li> <li>Updated parameter I<sub>INJPAD_DC_ABS</sub>', 'VIN_DC', I<sub>INJSUM_DC_ABS</sub>.</li> <li>In Table 5, updated TBDs for V<sub>LVR_HYST</sub>, V<sub>LVD_HYST</sub>, and <sub>VLVW_HYST</sub></li> <li>In Power mode transition operating behaviors,</li> <li>Added VLPR → VLPS</li> <li>Added VLPR → VLPS</li> <li>Added VLPS → VLPR</li> <li>Updated TBDs for VLPS → Asynchronous DMA Wakeup, STOP1 → Asynchronous DMA Wakeup, and STOP2 → Asynchronous DMA Wakeup</li> <li>In Table 7, updated the specifications for S32K144.</li> <li>Updated the attachment S32K1xx_Power_Modes _Configuration.xlsx.</li> <li>In Table 15, removed C<sub>IN_A</sub>.</li> <li>In Table 17,</li> <li>Updated specificatins for g<sub>mXOSC</sub>.</li> <li>Removed I<sub>DDSC</sub>C</li> <li>In Table 19,</li> <li>Added parameter ΔF125.</li> <li>Removed I<sub>DDFIRC</sub></li> <li>In Table 21, removed I<sub>LPO</sub></li> <li>Updated section: Flash memory module (FTFC) electrical specifications</li> <li>In section: 12-bit ADC operating conditions,</li> <li>Updated TBDs for I<sub>DDA_ADC</sub> and TUE in Table 29</li> <li>In section: 12-bit ADC operating conditions, updated TBDs for I<sub>DDA_ADC</sub> and TUE in Table 27.</li> <li>In section: 12-bit ADC operating conditions, updated Table 27.</li> <li>In section: CMP with 8-bit DAC electrical specifications, added note 'For comparator IN signals adjacent'</li> </ul> |

| 5        | 06 Dec 2017 | <ul> <li>Removed S32K148 from 'Caution'</li> <li>Updated figure: S32K1xx product series comparison for <ul> <li>'EEPROM emulated by FlexRAM' of S32K148 (Added content to footnote)</li> <li>Added support for LIN protocol version 2.2 A</li> </ul> </li> <li>In Absolute maximum ratings : <ul> <li>Added note 'Unless otherwise'</li> <li>Added parameter 'Added note 'T<sub>ramp_MCU</sub>'</li> <li>Updated footnote for 'T<sub>ramp</sub>'</li> </ul> </li> <li>In Voltage and current operating requirements : <ul> <li>Added footnote 'V<sub>DD</sub> and V<sub>DDA</sub> must be shorted' against parameter 'V<sub>DD</sub>-V<sub>DDA</sub>'</li> <li>Updated footnote 'V<sub>DD</sub> and V<sub>DDA</sub> must be shorted'</li> </ul> </li> <li>In Power and ground pins <ul> <li>Added diagrams for 32-QFN and 48-LQFP and footnote below the diagrams.</li> <li>Updated footnote 'V<sub>DD</sub> and V<sub>DDA</sub> must be shorted'</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

### Table 43. Revision History (continued)

Table continues on the next page ...

#### How to Reach Us:

Home Page: nxp.com

Web Support: nxp.com/support Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

While NXP has implemented advanced security features, all products may be subject to unidentified vulnerabilities. Customers are responsible for the design and operation of their applications and products to reduce the effect of these vulnerabilities on customer's applications and products, and NXP accepts no liability for any vulnerability that is discovered. Customers should implement appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP. the NXP logo. NXP SECURE CONNECTIONS FOR A SMARTER WORLD. COOLFLUX. EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorIQ, QorIQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, and UMEMS are trademarks of NXP B.V. All other product or service names are the property of their respective owners. Arm, AMBA, Artisan, Cortex, Jazelle, Keil, SecurCore, Thumb, TrustZone, and µVision are registered trademarks of Arm Limited (or its subsidiaries) in the EU and/or elsewhere. Arm7, Arm9, Arm11, big.LITTLE, CoreLink, CoreSight, DesignStart, Mali, Mbed, NEON, POP, Sensinode, Socrates, ULINK and Versatile are trademarks of Arm Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© 2015–2018 NXP B.V.

Document Number S32K1XX Revision 8, 06/2018