Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Core Size32-Bit Single-CoreSpeed64MHzConnectivityCANbus, FlexIO, I²C, LINbus, SPI, UART/USARTPeripheralsPOR, PWM, WDTNumber of I/O89Program Memory Size512KB (512K x 8)Program Memory TypeFLASHEEPROM Size4K x 8RAM Size64K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 5.5VData ConvertersA/D 16x12b SAR; D/A1x8bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Muning TypeSurface Mount                                                   |                            |                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------|

| Core Size32-Bit Single-CoreSpeed64MHzConnectivityCANbus, FlexIO, I²C, LINbus, SPI, UART/USARTPeripheralsPOR, PWM, WDTNumber of I/O89Program Memory Size512KB (512K x 8)Program Memory TypeFLASHEEPROM Size4K x 8RAM Size64K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 5.5VData ConvertersA/D 16x12b SAR; D/A1x8bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LFBGAInternal00-MAPBGA (11x11) | Product Status             | Active                                                                   |

| Speed64MHzConnectivityCANbus, FlexIO, I²C, LINbus, SPI, UART/USARTPeripheralsPOR, PWM, WDTNumber of I/O89Program Memory Size512KB (512K x 8)Program Memory TypeFLASHEEPROM Size64K x 8RAM Size64K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 5.5VData ConvertersA/D 16x12b SAR; D/A1x8bOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LFBGASupplier Device Package100-MAPBGA (11x11)                                  | Core Processor             | ARM® Cortex®-M4F                                                         |

| ConnectivityCANbus, FlexIO, I²C, LINbus, SPI, UART/USARTPeripheralsPOR, PWM, WDTNumber of I/O89Program Memory Size512KB (512K x 8)Program Memory TypeFLASHEEPROM Size4K x 8RAM Size64K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 5.5VData ConvertersA/D 16x12b SAR; D/A1x8bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LFBGASupplier Device Package100-MAPBGA (11x11)                      | Core Size                  | 32-Bit Single-Core                                                       |

| PeripheralsPOR, PWM, WDTNumber of I/O89Program Memory Size512KB (512K x 8)Program Memory TypeFLASHEEPROM Size4K x 8RAM Size64K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 5.5VData ConvertersA/D 16x12b SAR; D/A1x8bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LFBGASupplier Device Package100-MAPBGA (11x11)                                                                              | Speed                      | 64MHz                                                                    |

| Number of I/O89Program Memory Size512KB (512K x 8)Program Memory TypeFLASHEEPROM Size4K x 8RAM Size64K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 5.5VData ConvertersA/D 16x12b SAR; D/A1x8bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LFBGASupplier Device Package100-MAPBGA (11x11)                                                                                                      | Connectivity               | CANbus, FlexIO, I <sup>2</sup> C, LINbus, SPI, UART/USART                |

| Program Memory Size512KB (512K x 8)Program Memory TypeFLASHEEPROM Size4K x 8RAM Size64K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 5.5VData ConvertersA/D 16x12b SAR; D/A1x8bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LFBGASupplier Device Package100-MAPBGA (11x11)                                                                                                                     | Peripherals                | POR, PWM, WDT                                                            |

| Program Memory TypeFLASHEEPROM Size4K x 8RAM Size64K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 5.5VData ConvertersA/D 16x12b SAR; D/A1x8bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LFBGASupplier Device Package100-MAPBGA (11x11)                                                                                                                                                        | Number of I/O              | 89                                                                       |

| EEPROM Size4K x 8RAM Size64K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 5.5VData ConvertersA/D 16x12b SAR; D/A1x8bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LFBGASupplier Device Package100-MAPBGA (11x11)                                                                                                                                                                                | Program Memory Size        | 512KB (512K x 8)                                                         |

| RAM Size64K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 5.5VData ConvertersA/D 16x12b SAR; D/A1x8bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LFBGASupplier Device Package100-MAPBGA (11x11)                                                                                                                                                                                                 | Program Memory Type        | FLASH                                                                    |

| Voltage - Supply (Vcc/Vdd)2.7V ~ 5.5VData ConvertersA/D 16x12b SAR; D/A1x8bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LFBGASupplier Device Package100-MAPBGA (11x11)                                                                                                                                                                                                                | EEPROM Size                | 4K x 8                                                                   |

| Data ConvertersA/D 16x12b SAR; D/A1x8bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LFBGASupplier Device Package100-MAPBGA (11x11)                                                                                                                                                                                                                                                     | RAM Size                   | 64K x 8                                                                  |

| Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LFBGASupplier Device Package100-MAPBGA (11x11)                                                                                                                                                                                                                                                                                           | Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| Operating Temperature     -40°C ~ 85°C (TA)       Mounting Type     Surface Mount       Package / Case     100-LFBGA       Supplier Device Package     100-MAPBGA (11x11)                                                                                                                                                                                                                                                                         | Data Converters            | A/D 16x12b SAR; D/A1x8b                                                  |

| Mounting Type     Surface Mount       Package / Case     100-LFBGA       Supplier Device Package     100-MAPBGA (11x11)                                                                                                                                                                                                                                                                                                                           | Oscillator Type            | Internal                                                                 |

| Package / Case     100-LFBGA       Supplier Device Package     100-MAPBGA (11x11)                                                                                                                                                                                                                                                                                                                                                                 | Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Supplier Device Package     100-MAPBGA (11x11)                                                                                                                                                                                                                                                                                                                                                                                                    | Mounting Type              | Surface Mount                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Package / Case             | 100-LFBGA                                                                |

| Purchase URL https://www.e-xfl.com/product-detail/nxp-semiconductors/fs32k144mat0cmhr                                                                                                                                                                                                                                                                                                                                                             | Supplier Device Package    | 100-MAPBGA (11x11)                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/fs32k144mat0cmhr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table 7. Power consumption (Typicals unless stated otherwise) 1 (continued)

General

|                      |                          |     | VLPS (                            | μΑ) <sup>2</sup>    | V                                 | LPR (m                                      | A)                                          | STOP1<br>(mA) | STOP2<br>(mA) |                      | l@48<br>(mA)        |                      | 64 MHz<br>nA)       |                      | 80 MHz<br>nA)       |                      | N@112<br>(mA) <sup>3</sup> |                               |

|----------------------|--------------------------|-----|-----------------------------------|---------------------|-----------------------------------|---------------------------------------------|---------------------------------------------|---------------|---------------|----------------------|---------------------|----------------------|---------------------|----------------------|---------------------|----------------------|----------------------------|-------------------------------|

| Chip/Device          | Ambient Temperature (°C) |     | Peripherals disabled <sup>5</sup> | Peripherals enabled | Peripherals disabled <sup>6</sup> | Peripherals enabled use case 1 <sup>6</sup> | Peripherals enabled use case 2 <sup>7</sup> |               |               | Peripherals disabled | Peripherals enabled        | IDD/MHz (µA/MHz) <sup>4</sup> |

|                      |                          | Max | 1637                              | 1694                | 3.1                               | 3.21                                        | NA                                          | 12.7          | 13.7          | 25                   | 32.9                | 30.7                 | 38.8                | 36                   | 43.8                | N                    | A                          | 450                           |

| S32K144              | 25                       | Тур | 29.8                              | 42                  | 1.48                              | 1.50                                        | 2.91                                        | 7             | 7.7           | 19.7                 | 26.9                | 25.1                 | 33.3                | 30.2                 | 39.6                | 43.3                 | 55.6                       | 378                           |

|                      | 85                       | Тур | 150                               | 159                 | 1.72                              | 1.85                                        | 3.08                                        | 7.2           | 8.1           | 20.4                 | 27.1                | 26.1                 | 33.5                | 30.5                 | 40                  | 43.9                 | 56.1                       | 381                           |

|                      |                          | Max | 359                               | 384                 | 2.60                              | 2.65                                        | NA                                          | 9.2           | 9.9           | 23.2                 | 29.6                | 29.3                 | 36.2                | 34.8                 | 42.1                | 46.3                 | 59.7                       | 435                           |

|                      | 105                      | Тур | 256                               | 273                 | 1.80                              | 2.10                                        | 3.23                                        | 7.8           | 8.5           | 20.6                 | 27.4                | 26.6                 | 33.8                | 31.2                 | 40.5                | 44.8                 | 57.1                       | 390                           |

|                      |                          | Max | 850                               | 900                 | 2.65                              | 2.70                                        | NA                                          | 10.3          | 11.1          | 23.9                 | 30.6                | 30.3                 | 37.3                | 35.6                 | 43.5                | 47.9                 | 61.3                       | 445                           |

|                      | 125                      | Тур | NA                                | NA                  | NA                                | NA                                          | 3.65                                        | NA            | NA            | NA                   | NA                  | NA                   | NA                  | NA                   | NA                  | N                    | A                          | NA                            |

|                      |                          | Max | 1960                              | 1998                | 3.18                              | 3.25                                        | NA                                          | 12.9          | 13.8          | 26.9                 | 33.6                | 35                   | 40.3                | 38.7                 | 46.8                | N                    | A                          | 484                           |

| S32K146              | 25                       | Тур | 37                                | 47                  | 1.57                              | 1.61                                        | 3.3                                         | 8             | 9.2           | 23.4                 | 31.4                | 30.5                 | 40.2                | 36.2                 | 47.6                | 52                   | 68.3                       | 452                           |

|                      | 85                       | Тур | 207                               | 209                 | 1.79                              | 1.83                                        | 3.54                                        | 8.9           | 10.1          | 24.4                 | 32.4                | 31.5                 | 41.3                | 37.2                 | 48.7                | 53.3                 | 69.8                       | 465                           |

|                      |                          | Max | 974                               | 981                 | 3.32                              | 3.38                                        | NA                                          | 12.7          | 13.9          | 29.3                 | 37.9                | 36.7                 | 47                  | 42.4                 | 54.4                | 60.3                 | 78                         | 530                           |

|                      | 105                      | Тур | 419                               | 422                 | 1.99                              | 2.04                                        | 3.78                                        | 9.8           | 11            | 25.3                 | 33.4                | 32.5                 | 42.2                | 38.1                 | 49.6                | 54.4                 | 70.8                       | 477                           |

|                      |                          | Max | 2004                              | 2017                | 4.06                              | 4.13                                        | NA                                          | 17.1          | 18.3          | 34.1                 | 42.6                | 41.3                 | 51.4                | 46.9                 | 58.8                | 65.7                 | 82.8                       | 587                           |

|                      | 125                      | Тур | NA                                | NA                  | NA                                | NA                                          | 4.44                                        | NA            | NA            | NA                   | NA                  | NA                   | NA                  | NA                   | NA                  | N                    | A                          | NA                            |

|                      |                          | Max | 3358                              | 3380                | 5.28                              | 5.38                                        | NA                                          | 22.6          | 23.7          | 40.2                 | 48.8                | 47.3                 | 57.4                | 52.8                 | 64.8                | N                    | A                          | 660                           |

| S32K148 <sup>8</sup> | 25                       | Тур | 38                                | 54                  | 2.17                              | 2.20                                        | 3.45                                        | 8.5           | 9.6           | 27.6                 | 34.9                | 35.5                 | 45.3                | 42.1                 | 57.7                | 60.3                 | 83.3                       | 526                           |

|                      | 85                       | Тур | 336                               | 357                 | 2.30                              | 2.35                                        | 3.74                                        | 10.1          | 11.1          | 29.1                 | 37.0                | 36.8                 | 46.6                | 43.4                 | 59.9                | 62.9                 | 88.7                       | 543                           |

Table continues on the next page...

18

The following table shows the power consumption targets for S32K148 in various mode of operations measure at 3.3 V.

| Chip/Device | Ambient             |     | RUN@80                           | MHz (mA)                               | HSRUN@112 MHz (mA) <sup>1</sup>  |                                        |  |

|-------------|---------------------|-----|----------------------------------|----------------------------------------|----------------------------------|----------------------------------------|--|

| Chip/Device | Temperature<br>(°C) |     | Peripherals<br>enabled +<br>QSPI | Peripherals<br>enabled +<br>ENET + SAI | Peripherals<br>enabled +<br>QSPI | Peripherals<br>enabled +<br>ENET + SAI |  |

| S32K148     | 25                  | Тур | 67.3                             | 79.1                                   | 89.8                             | 105.5                                  |  |

|             | 85                  | Тур | 67.4                             | 79.2                                   | 95.6                             | 105.9                                  |  |

|             |                     | Max | 82.5                             | 88.2                                   | 109.7                            | 117.4                                  |  |

|             | 105                 | Тур | 68.0                             | 79.8                                   | 96.6                             | 106.7                                  |  |

|             |                     | Max | 80.3                             | 89.1                                   | 109.0                            | 119.0                                  |  |

|             | 125                 | Max | 83.5                             | 94.7                                   | N                                | İA                                     |  |

Table 9.Power consumption at 3.3 V

1. HSRUN mode must not be used at 125°C. Max ambient temperature for HSRUN mode is 105°C.

### 4.8 ESD handling ratings

| Symbol           | Description                                           | Min.   | Max. | Unit | Notes |

|------------------|-------------------------------------------------------|--------|------|------|-------|

| V <sub>HBM</sub> | Electrostatic discharge voltage, human body model     | - 4000 | 4000 | V    | 1     |

| V <sub>CDM</sub> | Electrostatic discharge voltage, charged-device model |        |      |      | 2     |

|                  | All pins except the corner pins                       | - 500  | 500  | V    |       |

|                  | Corner pins only                                      | - 750  | 750  | V    |       |

| I <sub>LAT</sub> | Latch-up current at ambient temperature of 125 °C     | - 100  | 100  | mA   | 3     |

1. Determined according to JEDEC Standard JESD22-A114, *Electrostatic Discharge (ESD) Sensitivity Testing Human Body Model (HBM)*.

2. Determined according to JEDEC Standard JESD22-C101, Field-Induced Charged-Device Model Test Method for Electrostatic-Discharge-Withstand Thresholds of Microelectronic Components.

3. Determined according to JEDEC Standard JESD78, IC Latch-Up Test.

### 4.9 EMC radiated emissions operating behaviors

EMC measurements to IC-level IEC standards are available from NXP on request.

### 5.3 DC electrical specifications at 3.3 V Range

NOTE

For details on the pad types defined in Table 11 and Table 12, see Reference Manual section *IO Signal Table* and IO Signal Description Input Multiplexing sheet(s) attached with Reference Manual.

| Symbol                                              | Parameter                                                                           |                       | Value                   |                       | Unit | Notes |  |

|-----------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------|-------------------------|-----------------------|------|-------|--|

|                                                     |                                                                                     | Min. Typ              |                         | Max.                  |      |       |  |

| V <sub>DD</sub>                                     | I/O Supply Voltage                                                                  | 2.7                   | 3.3                     | 4                     | V    | 1     |  |

| V <sub>ih</sub>                                     | Input Buffer High Voltage                                                           | $0.7 \times V_{DD}$   | _                       | V <sub>DD</sub> + 0.3 | V    | 2     |  |

| V <sub>il</sub>                                     | Input Buffer Low Voltage                                                            | V <sub>SS</sub> – 0.3 |                         | $0.3 \times V_{DD}$   | V    | 3     |  |

| V <sub>hys</sub>                                    | Input Buffer Hysteresis                                                             | $0.06 \times V_{DD}$  | _                       | —                     | V    |       |  |

| loh <sub>GPIO</sub><br>loh <sub>GPIO-HD_DSE_0</sub> | I/O current source capability measured when pad $V_{oh} = (V_{DD} - 0.8 \text{ V})$ | 3.5                   | —                       | _                     | mA   |       |  |

| Iol <sub>GPIO</sub> -HD_DSE_0                       | I/O current sink capability measured when pad $V_{ol} = 0.8 \text{ V}$              | 3                     | _                       |                       | mA   |       |  |

| Ioh <sub>GPIO-HD_DSE_1</sub>                        | I/O current source capability measured when pad $V_{oh} = (V_{DD} - 0.8 \text{ V})$ | 14                    | —                       | _                     | mA   | 4     |  |

| Iol <sub>GPIO-HD_DSE_1</sub>                        | I/O current sink capability measured when pad $V_{\text{ol}}$ = 0.8 V               | 12                    | _                       | _                     | mA   | 4     |  |

| loh <sub>GPIO-FAST_DSE_0</sub>                      | I/O current sink capability measured when pad $V_{oh}{=}V_{DD}{-}0.8~V$             | 9.5                   | _                       | _                     | mA   | 5     |  |

| IOI <sub>GPIO-FAST_DSE_0</sub>                      | I/O current sink capability measured when pad $V_{\text{ol}}$ = 0.8 V               | 10                    | _                       | —                     | mA   | 5     |  |

| Ioh <sub>GPIO-FAST_DSE_1</sub>                      | I/O current sink capability measured when pad $V_{oh}{=}V_{DD}{-}0.8~V$             | 16                    | _                       | —                     | mA   | 5     |  |

| IOI <sub>GPIO-FAST_DSE_1</sub>                      | I/O current sink capability measured when pad $V_{\text{ol}}$ = 0.8 V               | 15.5                  | _                       | _                     | mA   | 5     |  |

| IOHT                                                | Output high current total for all ports                                             | _                     | _                       | 100                   | mA   |       |  |

| IIN                                                 | Input leakage current (per pin) for full tempera                                    | ture range at         | V <sub>DD</sub> = 3.3 V | /                     | ł    | 6     |  |

|                                                     | All pins other than high drive port pins                                            |                       | 0.005                   | 0.5                   | μA   |       |  |

|                                                     | High drive port pins <sup>7</sup>                                                   |                       | 0.010                   | 0.5                   | μA   | ]     |  |

| R <sub>PU</sub>                                     | Internal pullup resistors                                                           | 20                    |                         | 60                    | kΩ   | 8     |  |

| R <sub>PD</sub>                                     | Internal pulldown resistors                                                         | 20                    |                         | 60                    | kΩ   | 9     |  |

1. S32K148 will operate from 2.7 V when executing from internal FIRC. When the PLL is engaged S32K148 is guaranteed to operate from 2.97 V. All other S32K family devices operate from 2.7 V in all modes.

- 2. For reset pads, same V<sub>ih</sub> levels are applicable

- 3. For reset pads, same V<sub>il</sub> levels are applicable

- 4. The value given is measured at high drive strength mode. For value at low drive strength mode see the loh\_Standard value given above.

- 5. For refernce only. Run simulations with the IBIS model and custom board for accurate results.

#### I/O parameters

- 6. Several I/O have both high drive and normal drive capability selected by the associated Portx\_PCRn[DSE] control bit. All other GPIOs are normal drive only. For details see IO Signal Description Input Multiplexing sheet(s) attached with the *Reference Manual*.

- 7. When using ENET and SAI on S32K148, the overall device limits associated with high drive pin configurations must be respected i.e. On 144-pin LQFP the general purpose pins: PTA10, PTD0, and PTE4 must be set to low drive.

- 8. Measured at input  $V = V_{SS}$

- 9. Measured at input  $V = V_{DD}$

### 5.4 DC electrical specifications at 5.0 V Range

| Symbol                                              | Parameter                                                                      |                           | Value                   |                        | Unit | Notes |

|-----------------------------------------------------|--------------------------------------------------------------------------------|---------------------------|-------------------------|------------------------|------|-------|

|                                                     |                                                                                | Min.                      | Тур.                    | Max.                   |      |       |

| V <sub>DD</sub>                                     | I/O Supply Voltage                                                             | 4                         | _                       | 5.5                    | V    |       |

| V <sub>ih</sub>                                     | V <sub>ih</sub> Input Buffer High Voltage                                      |                           | _                       | V <sub>DD</sub> + 0.3  | V    | 1     |

| V <sub>il</sub>                                     | Input Buffer Low Voltage                                                       | V <sub>SS</sub> – 0.3     | _                       | 0.35 x V <sub>DD</sub> | V    | 2     |

| V <sub>hys</sub>                                    | Input Buffer Hysteresis                                                        | 0.06 x<br>V <sub>DD</sub> | _                       | —                      | V    |       |

| loh <sub>GPIO</sub><br>loh <sub>GPIO-HD_DSE_0</sub> | I/O current source capability measured when pad $V_{oh}$ = ( $V_{DD}$ - 0.8 V) | 5                         | _                       | —                      | mA   |       |

| Iol <sub>GPIO</sub><br>Iol <sub>GPIO-HD_DSE_0</sub> | I/O current sink capability measured when pad $V_{\rm ol}{=}$ 0.8 V            | 5                         | _                       | —                      | mA   |       |

| Ioh <sub>GPIO-HD_DSE_1</sub>                        |                                                                                |                           | _                       | —                      | mA   | 3     |

| IOI <sub>GPIO-HD_DSE_1</sub>                        | I/O current sink capability measured when pad $V_{ol} = 0.8 V$                 | 20                        | _                       | —                      | mA   | 3     |

| Ioh <sub>GPIO-FAST_DSE_0</sub>                      | I/O current sink capability measured when pad $V_{oh} = V_{DD} - 0.8 V$        | 14.0                      | —                       | —                      | mA   | 4     |

| IOI <sub>GPIO-FAST_DSE_0</sub>                      | I/O current sink capability measured when pad $V_{ol}$ = 0.8 V                 | 14.5                      | —                       | _                      | mA   | 4     |

| loh <sub>GPIO-FAST_DSE_1</sub>                      | I/O current sink capability measured when pad $V_{oh} = V_{DD} - 0.8 V$        | 21                        | —                       | —                      | mA   | 4     |

| IOI <sub>GPIO-FAST_DSE_1</sub>                      | I/O current sink capability measured when pad $V_{ol}$ = 0.8 V                 | 20.5                      | —                       | —                      | mA   | 4     |

| IOHT                                                | Output high current total for all ports                                        | —                         | _                       | 100                    | mA   |       |

| IIN                                                 | Input leakage current (per pin) for full te                                    | mperature r               | ange at V <sub>DD</sub> | <sub>0</sub> = 5.5 V   |      | 5     |

|                                                     | All pins other than high drive port pins                                       |                           | 0.005                   | 0.5                    | μA   |       |

|                                                     | High drive port pins                                                           |                           | 0.010                   | 0.5                    | μA   |       |

| R <sub>PU</sub>                                     | Internal pullup resistors                                                      | 20                        |                         | 50                     | kΩ   | 6     |

| R <sub>PD</sub>                                     | Internal pulldown resistors                                                    | 20                        |                         | 50                     | kΩ   | 7     |

Table 12. DC electrical specifications at 5.0 V Range

1. For reset pads, same V<sub>ih</sub> levels are applicable

2. For reset pads, same V<sub>il</sub> levels are applicable

- 3. The strong pad I/O pin is capable of switching a 50 pF load up to 40 MHz.

- 4. For refernce only. Run simulations with the IBIS model and custom board for accurate results.

- 5. Several I/O have both high drive and normal drive capability selected by the associated Portx\_PCRn[DSE] control bit. All other GPIOs are normal drive only. For details refer to *SK3K144\_IO\_Signal\_Description\_Input\_Multiplexing.xlsx* attached with the *Reference Manual*.

- 6. Measured at input  $V = V_{SS}$

- 7. Measured at input  $V = V_{DD}$

| Symbol                   | DSE | Rise tir | ne (nS) <sup>1</sup> | Fall tin | ne (nS) <sup>1</sup> | Capacitance (pF) <sup>2</sup> |

|--------------------------|-----|----------|----------------------|----------|----------------------|-------------------------------|

|                          |     | Min.     | Max.                 | Min.     | Max.                 |                               |

| tRF <sub>GPIO</sub>      | NA  | 3.2      | 14.5                 | 3.4      | 15.7                 | 25                            |

|                          |     | 5.7      | 23.7                 | 6.0      | 26.2                 | 50                            |

|                          |     | 20.0     | 80.0                 | 20.8     | 88.4                 | 200                           |

| tRF <sub>GPIO-HD</sub>   | 0   | 3.2      | 14.5                 | 3.4      | 15.7                 | 25                            |

|                          |     | 5.7      | 23.7                 | 6.0      | 26.2                 | 50                            |

|                          |     | 20.0     | 80.0                 | 20.8     | 88.4                 | 200                           |

|                          | 1   | 1.5      | 5.8                  | 1.7      | 6.1                  | 25                            |

|                          |     | 2.4      | 8.0                  | 2.6      | 8.3                  | 50                            |

|                          |     | 6.3      | 22.0                 | 6.0      | 23.8                 | 200                           |

| tRF <sub>GPIO-FAST</sub> | 0   | 0.6      | 2.8                  | 0.5      | 2.8                  | 25                            |

|                          |     | 3.0      | 7.1                  | 2.6      | 7.5                  | 50                            |

|                          |     | 12.0     | 27.0                 | 10.3     | 26.8                 | 200                           |

|                          | 1   | 0.4      | 1.3                  | 0.38     | 1.3                  | 25                            |

|                          |     | 1.5      | 3.8                  | 1.4      | 3.9                  | 50                            |

|                          |     | 7.4      | 14.9                 | 7.0      | 15.3                 | 200                           |

### 5.5 AC electrical specifications at 3.3 V range

Table 13. AC electrical specifications at 3.3 V Range

1. For reference only. Run simulations with the IBIS model and your custom board for accurate results.

2. Maximum capacitances supported on Standard IOs. However interface or protocol specific specifications might be different, for example for ENET, QSPI etc. . For protocol specific AC specifications, see respective sections.

### 5.6 AC electrical specifications at 5 V range

| Symbol                 | DSE | Rise tir | me (nS) <sup>1</sup> | Fall time (nS) <sup>1</sup> |      | Capacitance (pF) <sup>2</sup> |

|------------------------|-----|----------|----------------------|-----------------------------|------|-------------------------------|

|                        |     | Min.     | Max .                | Min.                        | Max. |                               |

| tRF <sub>GPIO</sub>    | NA  | 2.8      | 9.4                  | 2.9                         | 10.7 | 25                            |

|                        |     | 5.0      | 15.7                 | 5.1                         | 17.4 | 50                            |

|                        |     | 17.3     | 54.8                 | 17.6                        | 59.7 | 200                           |

| tRF <sub>GPIO-HD</sub> | 0   | 2.8      | 9.4                  | 2.9                         | 10.7 | 25                            |

|                        |     | 5.0      | 15.7                 | 5.1                         | 17.4 | 50                            |

#### Table 14. AC electrical specifications at 5 V Range

Table continues on the next page...

| Symbol             | Description                      | Min. | Max.            | Unit |

|--------------------|----------------------------------|------|-----------------|------|

| f <sub>FLASH</sub> | Flash clock                      |      | 24              | MHz  |

|                    | Normal run mode (S32K14x series) | 3    | 1               |      |

| f <sub>SYS</sub>   | System and core clock            | _    | 80              | MHz  |

| f <sub>BUS</sub>   | Bus clock                        | _    | 40 <sup>4</sup> | MHz  |

| f <sub>FLASH</sub> | Flash clock                      | _    | 26.67           | MHz  |

|                    | VLPR mode <sup>5</sup>           |      |                 |      |

| f <sub>SYS</sub>   | System and core clock            |      | 4               | MHz  |

| f <sub>BUS</sub>   | Bus clock                        |      | 4               | MHz  |

| f <sub>FLASH</sub> | Flash clock                      | _    | 1               | MHz  |

| f <sub>ERCLK</sub> | External reference clock         |      | 16              | MHz  |

1. Refer to the section Feature comparison for the availability of modes and other specifications.

- 2. Only available on some devices. See section Feature comparison.

- 3. With SPLL as system clock source.

- 4. 48 MHz when f<sub>SYS</sub> is 48 MHz

5. The frequency limitations in VLPR mode here override any frequency specification listed in the timing specification for any other module.

# 6 Peripheral operating requirements and behaviors

#### 6.1 System modules

There are no electrical specifications necessary for the device's system modules.

#### 6.2 Clock interface modules

#### 6.2.1 External System Oscillator electrical specifications

#### 6.2.4 Low Power Oscillator (LPO) electrical specifications Table 21. Low Power Oscillator (LPO) electrical specifications

| Symbol               | Parameter                               | Min. | Тур. | Max. | Unit |

|----------------------|-----------------------------------------|------|------|------|------|

| F <sub>LPO</sub>     | Internal low power oscillator frequency | 113  | 128  | 139  | kHz  |

| T <sub>startup</sub> | Startup Time                            | _    | _    | 20   | μs   |

# 6.2.5 SPLL electrical specifications

Table 22. SPLL electrical specifications

| Symbol                               | Parameter                                          | Min.   | Тур. | Max.                                                       | Unit |

|--------------------------------------|----------------------------------------------------|--------|------|------------------------------------------------------------|------|

| F <sub>SPLL_REF</sub> <sup>1</sup>   | PLL Reference Frequency Range                      | 8      | —    | 16                                                         | MHz  |

| F <sub>SPLL_Input</sub> <sup>2</sup> | PLL Input Frequency                                | 8      | —    | 40                                                         | MHz  |

| F <sub>VCO_CLK</sub>                 | VCO output frequency                               | 180    | —    | 320                                                        | MHz  |

| F <sub>SPLL_CLK</sub>                | PLL output frequency                               | 90     | —    | 160                                                        | MHz  |

| J <sub>CYC_SPLL</sub>                | PLL Period Jitter (RMS) <sup>3</sup>               | •      | ·    |                                                            |      |

|                                      | at F <sub>VCO_CLK</sub> 180 MHz                    | _      | 120  | —                                                          | ps   |

|                                      | at F <sub>VCO_CLK</sub> 320 MHz                    | _      | 75   | —                                                          | ps   |

| J <sub>ACC_SPLL</sub>                | PLL accumulated jitter over 1µs (RMS) <sup>3</sup> |        |      |                                                            |      |

|                                      | at F <sub>VCO_CLK</sub> 180 MHz                    | _      | 1350 | —                                                          | ps   |

|                                      | at F <sub>VCO_CLK</sub> 320 MHz                    | _      | 600  | —                                                          | ps   |

| D <sub>UNL</sub>                     | Lock exit frequency tolerance                      | ± 4.47 | —    | ± 5.97                                                     | %    |

| T <sub>SPLL_LOCK</sub>               | Lock detector detection time <sup>4</sup>          | —      | _    | 150 × 10 <sup>-6</sup> +<br>1075(1/F <sub>SPLL_REF</sub> ) | S    |

1. F<sub>SPLL\_REF</sub> is PLL reference frequency range after the PREDIV. For PREDIV and MULT settings refer SCG\_SPLLCFG register of Reference Manual.

F<sub>SPLL\_Input</sub> is PLL input frequency range before the PREDIV must be limited to the range 8 MHz to 40 MHz. This input source could be derived from a crystal oscillator or some other external square wave clock source using OSC bypass mode. For external clock source settings refer SCG\_SOSCCFG register of Reference Manual.

3. This specification was obtained using a NXP developed PCB. PLL jitter is dependent on the noise characteristics of each PCB and results will vary

4. Lock detector detection time is defined as the time between PLL enablement and clock availability for system use.

# 6.3 Memory and memory interfaces

### 6.3.1 Flash memory module (FTFC) electrical specifications

This section describes the electrical characteristics of the flash memory module.

| Symbol                     | Description <sup>1</sup>                                              |                                                                        | S32 | K142                                | S3  | 2K144                               | S32 | K146                                | S32 | K148                                |      |       |

|----------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------|-----|-------------------------------------|-----|-------------------------------------|-----|-------------------------------------|-----|-------------------------------------|------|-------|

|                            |                                                                       |                                                                        | Тур | Max                                 | Тур | Max                                 | Тур | Max                                 | Тур | Max                                 | Unit | Notes |

|                            | setting (32-bit<br>write complete,<br>ready for next<br>32-bit write) | Last (Nth)<br>32-bit write<br>(time for<br>write only,<br>not cleanup) | 200 | 550                                 | 200 | 550                                 | 200 | 550                                 | 200 | 550                                 |      |       |

| t <sub>quickwr</sub> Clnup | Quick Write<br>Cleanup<br>execution time                              |                                                                        | —   | (# of<br>Quick<br>Writes<br>) * 2.0 |     | (# of<br>Quick<br>Writes )<br>* 2.0 |     | (# of<br>Quick<br>Writes<br>) * 2.0 |     | (# of<br>Quick<br>Writes<br>) * 2.0 | ms   | 7     |

Table 23. Flash command timing specifications for S32K14x (continued)

- 1. All command times assumes 25 MHz or greater flash clock frequency (for synchronization time between internal/external clocks).

- 2. Maximum times for erase parameters based on expectations at cycling end-of-life.

- For all EEPROM Emulation terms, the specified timing shown assumes previous record cleanup has occurred. This may be verified by executing FCCOB Command 0x77, and checking FCCOB number 5 contents show 0x00 - No EEPROM issues detected.

- 4. 1st time EERAM writes after a Reset or SETRAM may incur additional overhead for EEE cleanup, resulting in up to 2× the times shown.

- 5. Only after the Nth write completes will any data be valid. Emulated EEPROM record scheme cleanup overhead may occur after this point even after a brownout or reset. If power on reset occurs before the Nth write completes, the last valid record set will still be valid and the new records will be discarded.

- 6. Quick Write times may take up to 550 µs, as additional cleanup may occur when crossing sector boundaries.

- 7. Time for emulated EEPROM record scheme overhead cleanup. Automatically done after last (Nth) write completes, assuming still powered. Or via SETRAM cleanup execution command is requested at a later point.

#### Table 24. Flash command timing specifications for S32K11x

| Symbol              | Descripti                        | on <sup>1</sup> | S32 | 2K116 | S   | 32K118 |      |       |

|---------------------|----------------------------------|-----------------|-----|-------|-----|--------|------|-------|

|                     |                                  |                 | Тур | Max   | Тур | Max    | Unit | Notes |

| t <sub>rd1blk</sub> | Read 1 Block execution           | 32 KB flash     | —   | 0.36  | —   | 0.36   | ms   |       |

|                     | time                             | 64 KB flash     | —   | —     | —   | _      |      |       |

|                     |                                  | 128 KB flash    | —   | 1.2   | —   | —      |      |       |

|                     |                                  | 256 KB flash    | —   | —     | —   | 2      |      |       |

|                     |                                  | 512 KB flash    | _   | —     | —   | _      |      |       |

| t <sub>rd1sec</sub> | Read 1 Section                   | 2 KB flash      |     | 75    | —   | 75     | μs   |       |

|                     | execution time                   | 4 KB flash      | —   | 100   | —   | 100    |      |       |

| t <sub>pgmchk</sub> | Program Check<br>execution time  | —               | —   | 100   | -   | 100    | μs   |       |

| t <sub>pgm8</sub>   | Program Phrase<br>execution time | -               | 90  | 225   | 90  | 225    | μs   |       |

| t <sub>ersblk</sub> | Erase Flash Block                | 32 KB flash     | 15  | 300   | 15  | 300    | ms   | 2     |

|                     | execution time                   | 64 KB flash     | —   | —     | —   | _      |      |       |

|                     |                                  | 128 KB flash    | 120 | 1100  | —   | —      |      |       |

|                     |                                  | 256 KB flash    | _   | —     | 250 | 2125   |      |       |

|                     |                                  | 512 KB flash    | _   | —     | —   | —      |      |       |

Table continues on the next page ...

| Symbol                    | Description                                                                                         | on <sup>1</sup>                                                     | S32 | K116                                | s   | 32K118                        |      |                    |

|---------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----|-------------------------------------|-----|-------------------------------|------|--------------------|

|                           |                                                                                                     |                                                                     | Тур | Max                                 | Тур | Max                           | Unit | Notes              |

| t <sub>eewr32b</sub>      | 32-bit write to FlexRAM execution time                                                              | 32 KB EEPROM<br>backup                                              | 630 | 2000                                | 630 | 2000                          | μs   | 3 <sup>,</sup> 4   |

|                           |                                                                                                     | 48 KB EEPROM<br>backup                                              | -   | —                                   | —   | —                             |      |                    |

|                           |                                                                                                     | 64 KB EEPROM<br>backup                                              | -   | —                                   | —   | —                             |      |                    |

| t <sub>quickwr</sub>      | 32-bit Quick Write                                                                                  | 1st 32-bit write                                                    | 200 | 550                                 | 200 | 550                           | μs   | 4 <sup>,</sup> 5,6 |

|                           | execution time: Time<br>from CCIF clearing (start<br>the write) until CCIF<br>setting (32-bit write | 2nd through Next<br>to Last (Nth-1)<br>32-bit write                 | 150 | 550                                 | 150 | 550                           |      |                    |

|                           | complete, ready for next<br>32-bit write)                                                           | Last (Nth) 32-bit<br>write (time for<br>write only, not<br>cleanup) | 200 | 550                                 | 200 | 550                           |      |                    |

| t <sub>quickwrClnup</sub> | Quick Write Cleanup<br>execution time                                                               | _                                                                   |     | (# of<br>Quick<br>Writes ) *<br>2.0 | —   | (# of Quick<br>Writes ) * 2.0 | ms   | 7                  |

#### Table 24. Flash command timing specifications for S32K11x (continued)

- 1. All command times assume 25 MHz or greater flash clock frequency (for synchronization time between internal/external clocks).

- 2. Maximum times for erase parameters based on expectations at cycling end-of-life.

- For all EEPROM Emulation terms, the specified timing shown assumes previous record cleanup has occurred. This may be verified by executing FCCOB Command 0x77, and checking FCCOB number 5 contents show 0x00 - No EEPROM issues detected.

- 4. 1st time EERAM writes after a Reset or SETRAM may incur additional overhead for EEE cleanup, resulting in up to 2x the times shown.

- 5. Only after the Nth write completes will any data be valid. Emulated EEPROM record scheme cleanup overhead may occur after this point even after a brownout or reset. If power on reset occurs before the Nth write completes, the last valid record set will still be valid and the new records will be discarded.

- 6. Quick Write times may take up to 550 µs, as additional cleanup may occur when crossing sector boundaries.

- 7. Time for emulated EEPROM record scheme overhead cleanup. Automatically done after last (Nth) write completes, assuming still powered. Or via SETRAM cleanup execution command is requested at a later point.

#### NOTE

Under certain circumstances FlexMEM maximum times may be exceeded. In this case the user or application may wait, or assert reset to the FTFC macro to stop the operation.

#### 6.3.1.2 Reliability specifications

#### Table 25. NVM reliability specifications

| Symbol                 | Description                           | Min.     | Тур.  | Max. | Unit   | Notes |

|------------------------|---------------------------------------|----------|-------|------|--------|-------|

|                        | When using as Program                 | and Data | Flash |      |        |       |

| t <sub>nvmretp1k</sub> | Data retention after up to 1 K cycles | 20       |       | _    | years  | 1     |

| n <sub>nvmcycp</sub>   | Cycling endurance                     | 1 K      | _     | _    | cycles | 2, 3  |

Table continues on the next page...

| Table 25. | NVM reliability | y s | pecifications | (continued) | ) |

|-----------|-----------------|-----|---------------|-------------|---|

|-----------|-----------------|-----|---------------|-------------|---|

| Symbol                  | Description                                                             | Min.      | Тур.         | Max. | Unit   | Notes   |

|-------------------------|-------------------------------------------------------------------------|-----------|--------------|------|--------|---------|

|                         | When using FlexMemory feature : Fle                                     | xRAM as E | Emulated EEP | ROM  |        |         |

| t <sub>nvmretee</sub>   | Data retention                                                          | 5         | —            | _    | years  | 4       |

| n <sub>nvmwree16</sub>  | Write endurance <ul> <li>EEPROM backup to FlexRAM ratio = 16</li> </ul> | 100 K     | _            | _    | writes | 5, 6, 7 |

| n <sub>nvmwree256</sub> | <ul> <li>EEPROM backup to FlexRAM ratio = 256</li> </ul>                | 1.6 M     | —            | —    | writes |         |

- 1. Data retention period per block begins upon initial user factory programming or after each subsequent erase.

- 2. Program and Erase for PFlash and DFlash are supported across product temperature specification in Normal Mode (not supported in HSRUN mode).

- 3. Cycling endurance is per DFlash or PFlash Sector.

- 4. Data retention period per block begins upon initial user factory programming or after each subsequent erase. Background maintenance operations during normal FlexRAM usage extend effective data retention life beyond 5 years.

- FlexMemory write endurance specified for 16-bit and/or 32-bit writes to FlexRAM and is supported across product temperature specification in Normal Mode (not supported in HSRUN mode). Greater write endurance may be achieved with larger ratios of EEPROM backup to FlexRAM.

- 6. For usage of any EEE driver other than the FlexMemory feature, the endurance spec will fall back to the specified endurance value of the D-Flash specification (1K).

- 7. FlexMemory calculator tool is available at NXP web site for help in estimation of the maximum write endurance achievable at specific EEPROM/FlexRAM ratios. The "In Spec" portions of the online calculator refer to the NVM reliability specifications section of data sheet. This calculator is only applies to the FlexMemory feature.

#### 6.3.2 QuadSPI AC specifications

The following table describes the QuadSPI electrical characteristics.

- Measurements are with maximum output load of 25 pF, input transition of 1 ns and pad configured with fastest slew settings (DSE = 1'b1).

- I/O operating voltage ranges from 2.97 V to 3.6 V

- While doing the mode transition (RUN -> HSRUN or HSRUN -> RUN ), the interface should be OFF.

- Add 50 ohm series termination on board in QuadSPI SCK for Flash A to avoid loop back reflection when using in Internal DQS (PAD Loopback) mode.

- QuadSPI trace length should be 3 inches.

- For non-Quad mode of operation if external device doesn't have pull-up feature, external pull-up needs to be added at board level for non-used pads.

- With external pull-up, performance of the interface may degrade based on load associated with external pull-up.

#### 6.4.1.2 12-bit ADC electrical characteristics

#### NOTE

- ADC performance specifications are documented using a single ADC. For parallel/simultaneous operation of both ADCs, either for sampling the same channel by both ADCs or for sampling different channels by each ADC, some amount of decrease in performance can be expected. Care must be taken to stagger the two ADC conversions, in particular the sample phase, to minimize the impact of simultaneous conversions.

- On reduced pin packages where ADC reference pins are shared with supply pins, ADC analog performance characteristics may be impacted. The amount of variation will be directly impacted by the external PCB layout and hence care must be taken with PCB routing. See AN5426 for details

| Symbol               | Description                | Conditions <sup>1</sup> | Min. | Typ. <sup>2</sup> | Max.                                                 | Unit             | Notes      |

|----------------------|----------------------------|-------------------------|------|-------------------|------------------------------------------------------|------------------|------------|

| V <sub>DDA</sub>     | Supply voltage             |                         | 2.7  | _                 | 3                                                    | V                |            |

| I <sub>DDA_ADC</sub> | Supply current per ADC     |                         | _    | 0.6               | _                                                    | mA               | 3          |

| SMPLTS               | Sample Time                |                         | 275  | _                 | Refer to<br>the<br><i>Reference</i><br><i>Manual</i> | ns               |            |

| TUE <sup>4</sup>     | Total unadjusted error     |                         | _    | ±4                | ±8                                                   | LSB <sup>5</sup> | 6, 7, 8, 9 |

| DNL                  | Differential non-linearity |                         | _    | ±1.0              | _                                                    | LSB <sup>5</sup> | 6, 7, 8, 9 |

| INL                  | Integral non-linearity     |                         | _    | ±2.0              | —                                                    | LSB <sup>5</sup> | 6, 7, 8, 9 |

Table 28. 12-bit ADC characteristics (2.7 V to 3 V) ( $V_{REFH} = V_{DDA}$ ,  $V_{REFL} = V_{SS}$ )

- 1. All accuracy numbers assume the ADC is calibrated with V<sub>REFH</sub>=V<sub>DDA</sub>=V<sub>DD</sub>, with the calibration frequency set to less than or equal to half of the maximum specified ADC clock frequency.

- 2. Typical values assume V<sub>DDA</sub> = 3 V, Temp = 25 °C,  $f_{ADCK}$  = 40 MHz, R<sub>AS</sub>=20  $\Omega$ , and C<sub>AS</sub>=10 nF.

- 3. The ADC supply current depends on the ADC conversion rate.

- 4. Represents total static error, which includes offset and full scale error.

- 5. 1 LSB =  $(V_{REFH} V_{REFL})/2^N$

- 6. The specifications are with averaging and in standalone mode only. Performance may degrade depending upon device use case scenario. When using ADC averaging, refer to the *Reference Manual* to determine the most appropriate settings for AVGS.

- For ADC signals adjacent to V<sub>DD</sub>/V<sub>SS</sub> or XTAL/EXTAL or high frequency switching pins, some degradation in the ADC performance may be observed.

- 8. All values guarantee the performance of the ADC for multiple ADC input channel pins. When using ADC to monitor the internal analog parameters, assume minor degradation.

- 9. All the parameters in the table are given assuming system clock as the clocking source for ADC.

#### Table 32. LPSPI electrical specifications1

| Num | Symbol                         | Description                  | Conditions                            |                                    | Run  | Mode <sup>2</sup>                  |      |                                    | HSRU | N Mode <sup>2</sup>                |                 |                                    | VLPR | Mode                               |      | Unit |

|-----|--------------------------------|------------------------------|---------------------------------------|------------------------------------|------|------------------------------------|------|------------------------------------|------|------------------------------------|-----------------|------------------------------------|------|------------------------------------|------|------|

|     |                                |                              |                                       | 5.0                                | V IO | 3.3                                | V IO | 5.0                                | V IO | 3.3                                | V IO            | 5.0                                | V IO | 3.3                                | V IO | 1    |

|     |                                |                              |                                       | Min.                               | Max. | Min.                               | Max. | Min.                               | Max. | Min.                               | Max.            | Min.                               | Max. | Min.                               | Max. | 1    |

|     | f <sub>periph</sub> , 3, 4     | Peripheral                   | Slave                                 | -                                  | 40   | -                                  | 40   | -                                  | 56   | -                                  | 56              | -                                  | 4    | -                                  | 4    | MH   |

|     |                                | Frequency                    | Master                                | -                                  | 40   | -                                  | 40   | -                                  | 56   | -                                  | 56              | -                                  | 4    | -                                  | 4    | ]    |

|     |                                |                              | Master<br>Loopback <sup>5</sup>       | -                                  | 40   | -                                  | 48   | -                                  | 48   | -                                  | 48              | -                                  | 4    | -                                  | 4    |      |

|     |                                |                              | Master<br>Loopback(slow) <sup>6</sup> | -                                  | 48   | -                                  | 48   | -                                  | 48   | -                                  | 48              | -                                  | 4    | -                                  | 4    |      |

| 1   | f <sub>op</sub>                | Frequency of                 | Slave                                 | -                                  | 10   | -                                  | 10   | -                                  | 14   | -                                  | 14 <sup>7</sup> | -                                  | 2    | -                                  | 2    | MH   |

|     |                                | operation                    | Master                                | -                                  | 10   | -                                  | 10   | -                                  | 14   | -                                  | 14 <sup>7</sup> | -                                  | 2    | -                                  | 2    | 1    |

|     |                                |                              | Master<br>Loopback <sup>5</sup>       | -                                  | 20   | -                                  | 12   | -                                  | 24   | -                                  | 12              | -                                  | 2    | -                                  | 2    |      |

|     |                                |                              | Master<br>Loopback(slow) <sup>6</sup> | -                                  | 12   | -                                  | 12   | -                                  | 12   | -                                  | 12              | -                                  | 2    | -                                  | 2    |      |

| 2   | t <sub>SPSCK</sub>             | SPSCK                        | Slave                                 | 100                                | -    | 100                                | -    | 72                                 | -    | 72                                 | -               | 500                                | -    | 500                                | -    | ns   |

|     |                                | period                       | Master                                | 100                                | -    | 100                                | -    | 72                                 | -    | 72                                 | -               | 500                                | -    | 500                                | -    |      |

|     |                                |                              | Master<br>Loopback <sup>5</sup>       | 50                                 | -    | 83                                 | -    | 42                                 | -    | 83                                 | -               | 500                                | -    | 500                                | -    |      |

|     |                                |                              | Master<br>Loopback(slow) <sup>6</sup> | 83                                 | -    | 83                                 | -    | 83                                 | -    | 83                                 | -               | 500                                | -    | 500                                | -    |      |

| 3   | t <sub>Lead</sub> <sup>8</sup> | Enable lead                  | Slave                                 | -                                  | -    | -                                  | -    | -                                  | -    | -                                  | -               | -                                  | -    | -                                  | -    | ns   |

|     |                                | time (PCS to<br>SPSCK delay) | Master                                |                                    | -    |                                    | -    |                                    | -    |                                    | -               |                                    | -    |                                    | -    | ]    |

|     |                                |                              | Master<br>Loopback <sup>5</sup>       | 1-25                               |      | - <sup>-</sup> -25                 |      | - <sup>-</sup> -25                 |      | <sup>-</sup> -25                   |                 | -50                                |      | - <sup>-</sup> -50                 |      |      |

|     |                                |                              | Master<br>Loopback(slow) <sup>6</sup> | (PCSSCK+1)*t <sub>periph</sub> -25 |                 | (PCSSCK+1)*t <sub>periph</sub> -50 |      | (PCSSCK+1)*t <sub>periph</sub> -50 |      |      |

Table continues on the next page...

Communication modules

5

#### **Communication modules**

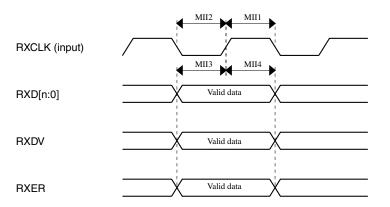

Figure 24. MII receive diagram

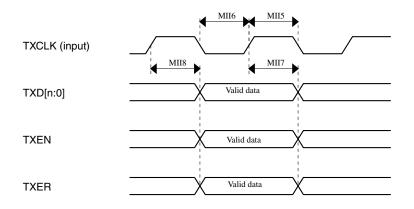

#### Figure 25. MII transmit signal diagram

The following table describes the RMII electrical characteristics.

- Measurements are with maximum output load of 25 pF, input transition of 1 ns and pad configured with fastest slew settings (DSE = 1'b1).

- I/O operating voltage ranges from 2.97 V to 3.6 V

- While doing the mode transition (RUN -> HSRUN or HSRUN -> RUN ), the interface should be OFF.

| Symbol       | Description                              | Min. | Max. | Unit               |

|--------------|------------------------------------------|------|------|--------------------|

| —            | RMII input clock RMII_CLK Frequency      | —    | 50   | MHz                |

| RMII1, RMII5 | RMII_CLK pulse width high                | 35%  | 65%  | RMII_CLK<br>period |

| RMII2, RMII6 | RMII_CLK pulse width low                 | 35%  | 65%  | RMII_CLK<br>period |

| RMII3        | RXD[1:0], CRS_DV, RXER to RMII_CLK setup | 4    | _    | ns                 |

| RMII4        | RMII_CLK to RXD[1:0], CRS_DV, RXER hold  | 2    |      | ns                 |

Table continues on the next page...

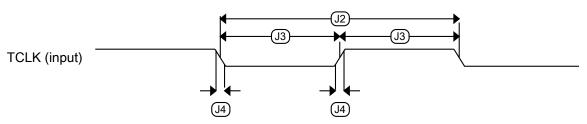

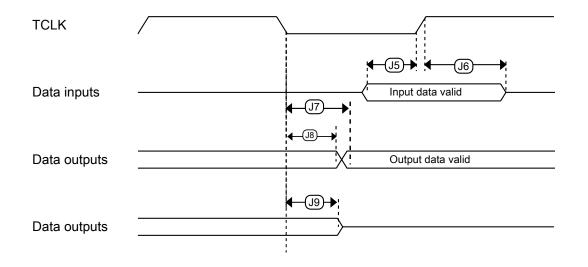

Figure 32. Test clock input timing

Figure 33. Boundary scan (JTAG) timing

# Table 41. Thermal characteristics for 32-pin QFN and 48/64/100/144/176-pin LQFP package (continued)

| Rating                                  | Conditions | Symbol | Package |         |         | Valu    | ues     |         |         | Unit |

|-----------------------------------------|------------|--------|---------|---------|---------|---------|---------|---------|---------|------|

|                                         |            |        |         | S32K116 | S32K118 | S32K142 | S32K144 | S32K146 | S32K148 |      |

| Thermal resistance, Junction to Package | Natural    | ΨJT    | 32      | 1       | NA      | NA      | NA      | NA      | NA      |      |

| Top <sup>7</sup>                        | Convection |        | 48      | 4       | 2       | NA      | NA      | NA      | NA      |      |

|                                         |            |        | 64      | NA      | 2       | 2       | 2       | 2       | NA      |      |

|                                         |            |        | 100     | NA      | NA      | 2       | 2       | 2       | NA      |      |

|                                         |            |        | 144     | NA      | NA      | NA      | NA      | 2       | 1       |      |

|                                         |            |        | 176     | NA      | NA      | NA      | NA      | NA      | 1       |      |

1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

2. Per JEDEC JESD51-2 with natural convection for horizontally oriented board. Board meets JESD51-9 specification for 1s or 2s2p board, respectively.

3. Per JEDEC JESD51-6 with forced convection for horizontally oriented board. Board meets JESD51-9 specification for 1s or 2s2p board, respectively.

4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

6. Thermal resistance between the die and the solder pad on the bottom of the package. Interface resistance is ignored.

7. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

#### Dimensions

To determine the junction temperature of the device in the application when heat sinks are not used, the Thermal Characterization Parameter ( $\Psi_{JT}$ ) can be used to determine the junction temperature with a measurement of the temperature at the top center of the package case using this equation:

$$T_J = T_T + (\Psi_{JT} \times P_D)$$

where:

- $T_T$  = thermocouple temperature on top of the package (°C)

- $\Psi_{JT}$  = thermal characterization parameter (°C/W)

- $P_D$  = power dissipation in the package (W)

The thermal characterization parameter is measured per JESD51-2 specification using a 40 gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over about 1 mm of wire extending from the junction. The thermocouple wire is placed flat against the package case to avoid measurement errors caused by cooling effects of the thermocouple wire.

# 8 Dimensions

# 8.1 Obtaining package dimensions

Package dimensions are provided in the package drawings.

To find a package drawing, go to http://www.nxp.com and perform a keyword search for the drawing's document number: