#### NXP USA Inc. - FS32K144MAT0VLHT Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4F                                                         |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 64MHz                                                                    |

| Connectivity               | CANbus, FlexIO, I <sup>2</sup> C, LINbus, SPI, UART/USART                |

| Peripherals                | POR, PWM, WDT                                                            |

| Number of I/O              | 58                                                                       |

| Program Memory Size        | 512KB (512K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 4K x 8                                                                   |

| RAM Size                   | 64K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| Data Converters            | A/D 16x12b SAR; D/A1x8b                                                  |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-LQFP                                                                  |

| Supplier Device Package    | 64-LQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/fs32k144mat0vlht |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

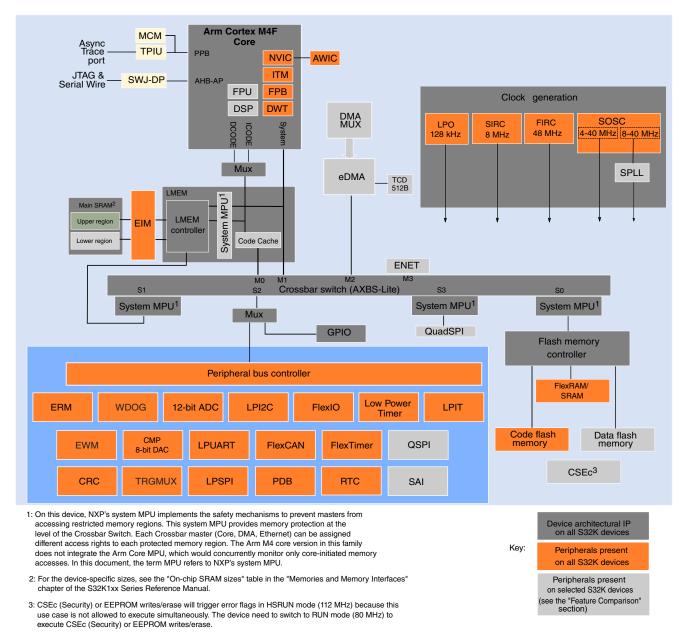

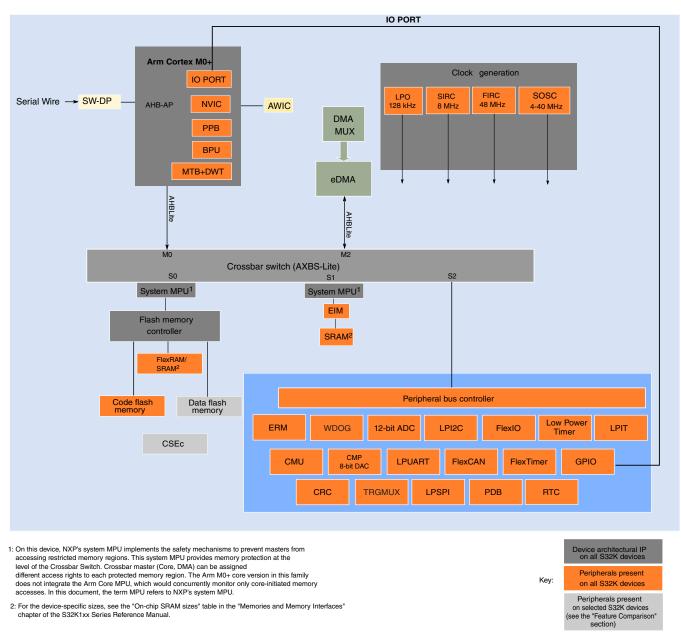

# 1 Block diagram

Following figures show superset high level architecture block diagrams of S32K14x series and S32K11x series respectively. Other devices within the family have a subset of the features. See Feature comparison for chip specific values.

Figure 1. High-level architecture diagram for the S32K14x family

#### Feature comparison

# 2 Feature comparison

The following figure summarizes the memory, peripherals and packaging options for the S32K1xx devices. All devices which share a common package are pin-to-pin compatible.

### NOTE

Availability of peripherals depends on the pin availability in a particular package. For more information see *IO Signal*

#### Feature comparison

## Description Input Multiplexing sheet(s) attached with Reference Manual.

|               |                                                                                                    | S32K11x                            |                                           |                                                                        | S32                                           | K14x                                                          |                                                |

|---------------|----------------------------------------------------------------------------------------------------|------------------------------------|-------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------|---------------------------------------------------------------|------------------------------------------------|

|               | Parameter                                                                                          | K116                               | K118                                      | K142                                                                   | K144                                          | K146                                                          | K148                                           |

|               | Core                                                                                               | Arr                                | n <sup>®</sup> Cortex™-M0+                |                                                                        | Arr                                           | n <sup>®</sup> Cortex™-M4F                                    |                                                |

|               | Frequency                                                                                          | 48                                 | MHz                                       | 80 MH                                                                  | z (RUN mode) or 1                             | 12 MHz (HSRUN 1                                               | mode)1                                         |

|               | IEEE-754 FPU                                                                                       |                                    | c                                         |                                                                        |                                               | •                                                             |                                                |

|               | Cryptographic Services Engine (CSEc) <sup>1</sup>                                                  |                                    | •                                         |                                                                        |                                               | •                                                             |                                                |

|               | CRC module                                                                                         | 1                                  | x                                         | 1x                                                                     |                                               |                                                               |                                                |

|               | ISO 26262                                                                                          | capable u                          | o to ASIL-B                               |                                                                        |                                               |                                                               |                                                |

|               | Peripheral speed                                                                                   | up to 4                            | 8 MHz                                     | capable up to ASIL-B<br>up to 112 MHz (HSRUN)                          |                                               |                                                               |                                                |

|               | Crossbar                                                                                           |                                    | •                                         |                                                                        |                                               | •                                                             |                                                |

| E             | DMA                                                                                                |                                    | •                                         |                                                                        |                                               | •                                                             |                                                |

| System        | External Watchdog Monitor (EWM)                                                                    |                                    | 0                                         |                                                                        |                                               | •                                                             |                                                |

| sy            | Memory Protection Unit (MPU)                                                                       |                                    | •                                         |                                                                        |                                               | •                                                             |                                                |

|               | FIRC CMU                                                                                           |                                    | •                                         |                                                                        |                                               | 0                                                             |                                                |

|               | Watchdog                                                                                           | 1                                  | x                                         |                                                                        | 1                                             | x                                                             |                                                |

|               | Low power modes                                                                                    |                                    | •                                         |                                                                        |                                               | •                                                             |                                                |

|               | HSRUN mode1                                                                                        |                                    | 0                                         |                                                                        |                                               | •                                                             |                                                |

|               | Number of I/Os                                                                                     | up to 43                           | up to 58                                  | up t                                                                   | io 89                                         | up to 128                                                     | up to 156                                      |

|               | Single supply voltage                                                                              | 2.7 -                              | 5.5 V                                     |                                                                        | 2.7 -                                         | 5.5 V                                                         |                                                |

|               | Ambient Operation Temperature (Ta)                                                                 | -40°C to +105                      | 5ºC / +125ºC                              |                                                                        | -40°C to +10                                  | 5°C / +125°C                                                  |                                                |

|               | Flash                                                                                              | 128 KB                             | 256 KB                                    | 256 KB                                                                 | 512 KB                                        | 1 MB                                                          | 2 MB <sup>2</sup>                              |

|               | Error Correcting Code (ECC)                                                                        |                                    | •                                         |                                                                        |                                               | •                                                             |                                                |

|               | System RAM (including FlexRAM and MTB)                                                             | 17 KB                              | 25 KB                                     | 32 KB                                                                  | 64 KB                                         | 128 KB                                                        | 256 KB                                         |

| Ž             | FlexRAM (also available as system RAM)                                                             |                                    | KB                                        | -                                                                      |                                               | KB                                                            |                                                |

| Memory        | Cache                                                                                              |                                    | o                                         |                                                                        | 4                                             | KB                                                            |                                                |

| Σ             | EEPROM emulated by FlexRAM <sup>1</sup>                                                            | 2 KB (up to 3                      | 2 KB D-Flash)                             | 4 KE                                                                   | See footnote 3                                |                                                               |                                                |

|               | External memory interface                                                                          |                                    | o                                         |                                                                        | QuadSPI incl.<br>HyperBus™                    |                                                               |                                                |

|               | Low Power Interrupt Timer (LPIT)                                                                   | 1                                  | x                                         | 1x                                                                     |                                               |                                                               |                                                |

| ÷             | FlexTimer (16-bit counter) 8 channels                                                              | 2x                                 | (16)                                      | 4x                                                                     | (32)                                          | 6x (48)                                                       | 8x (64)                                        |

| Timer         | Low Power Timer (LPTMR)                                                                            | 1                                  | x                                         |                                                                        | 1                                             | x                                                             |                                                |

| -             | Real Time Counter (RTC)                                                                            | 1                                  | x                                         |                                                                        | 1                                             | x                                                             |                                                |

|               | Programmable Delay Block (PDB)                                                                     | 1                                  | х                                         |                                                                        | 2                                             | 2x                                                            |                                                |

| bo            | Trigger mux (TRGMUX)                                                                               | 1x (43)                            | 1x (45)                                   | 1x                                                                     | (64)                                          | 1x (73)                                                       | 1x (81)                                        |

| Analog        | 12-bit SAR ADC (1 Msps each)                                                                       | 1x (13)                            | 1x (16)                                   | 2x                                                                     | (16)                                          | 2x (24)                                                       | 2x (32)                                        |

| A             | Comparator with 8-bit DAC                                                                          | 1                                  | x                                         |                                                                        | 1                                             | x                                                             |                                                |

|               | 10/100 Mbps IEEE-1588 Ethernet MAC                                                                 |                                    | 0                                         |                                                                        | 0                                             |                                                               | 1x                                             |

| Ę             | Serial Audio Interface (AC97, TDM, I2S)                                                            |                                    | c                                         |                                                                        | 0                                             |                                                               | 2x                                             |

| Communication | Low Power UART/LIN (LPUART)<br>(Supports LIN protocol versions 1.3, 2.0, 2.1, 2.2A, and SAE J2602) | 2                                  | x                                         | 2x                                                                     |                                               | Зх                                                            |                                                |

| Ē             | Low Power SPI (LPSPI)                                                                              | 1x                                 | 2x                                        | 2x                                                                     |                                               | Зx                                                            |                                                |

| E C           | Low Power I2C (LPI2C)                                                                              |                                    | x                                         |                                                                        | 1x                                            |                                                               | 2x                                             |

| 0             | FlexCAN<br>(CAN-FD ISO/CD 11898-1)                                                                 | 1x<br>(1x with FD)                 |                                           | 2x<br>(1x with FD)                                                     | 3x<br>(1x with FD)                            | 3x<br>(2x with FD)                                            | 3x<br>(3x with FD)                             |

|               | FlexIO (8 pins configurable as UART, SPI, I2C, I2S)                                                | 1x                                 |                                           |                                                                        | 1x                                            |                                                               |                                                |

| IDEs          | Debug & trace                                                                                      | SWD, MTB (1 KB), JTAG <sup>4</sup> |                                           | SWD,                                                                   | SWD, JTAG<br>(ITM, SWV,<br>SWO), ETM          |                                                               |                                                |

| -             | Ecosystem<br>(IDE, compiler, debugger)                                                             |                                    | tudio (GCC) + SDK,<br>auterbach, iSystems | NXP S32 Design Studio (GCC) + SI<br>IAR, GHS, Arm®, Lauterbach, iSyste |                                               |                                                               | ζ,<br>15                                       |

| Other         | Packages <sup>5</sup>                                                                              | 32-pin QFN<br>48-pin LQFP          | 48-pin LQFP<br>64-pin LQFP                | 64-pin LQFP<br>100-pin LQFP                                            | 64-pin LQFP<br>100-pin LQFP<br>100-pin MAPBGA | 64-pin LQFP<br>100-pin MAPBGA<br>100-pin LQFP<br>144-pin LQFP | 100-pin MAPBGA<br>144-pin LQFP<br>176-pin LQFP |

LEGEND:

• Not implemented

Available on the device 1 No write or erase access to Flash module, including Security (CSEc) and EEPROM commands, are allowed when device is running at HSRUN mode (112MHz) or VLPR mode.

2 Available when EEEPROM, CSEc and Data Flash are not used. Else only up to 1,984 KB is available for Program Flash.

3 4 KB (up to 512 KB D-Flash as a part of 2 MB Flash). Up to 64 KB of flash is used as EEPROM backup and the remaining 448 KB of the last 512 KB block can be used as Data flash or Program flash. See chapter FTFC for details.

4 Only for Boundary Scan Register

5 See Dimensions section for package drawings

### Figure 3. S32K1xx product series comparison

- 5.  $V_{REFH}$  should always be equal to or less than  $V_{DDA}$  + 0.1 V and  $V_{DD}$  + 0.1 V

- 6. Open drain outputs must be pulled to  $V_{DD}$ .

- 7. When input pad voltage levels are close to  $V_{DD}$  or  $V_{SS}$ , practically no current injection is possible.

# 4.3 Thermal operating characteristics

# Table 3. Thermal operating characteristics for 64 LQFP, 100 LQFP, and 100 MAP-BGApackages.

| Symbol                      | Parameter                       | Value |      |                  | Unit |

|-----------------------------|---------------------------------|-------|------|------------------|------|

|                             |                                 | Min.  | Тур. | Max.             |      |

| T <sub>A C-Grade Part</sub> | Ambient temperature under bias  | -40   | —    | 85 <sup>1</sup>  | °C   |

| T <sub>J C-Grade Part</sub> | Junction temperature under bias | -40   | —    | 105 <sup>1</sup> | °C   |

| T <sub>A V-Grade Part</sub> | Ambient temperature under bias  | -40   | _    | 105 <sup>1</sup> | °C   |

| T <sub>J V-Grade Part</sub> | Junction temperature under bias | -40   | —    | 125 <sup>1</sup> | °C   |

| T <sub>A M-Grade Part</sub> | Ambient temperature under bias  | -40   | —    | 125 <sup>2</sup> | °C   |

| T <sub>J M-Grade Part</sub> | Junction temperature under bias | -40   | —    | 135 <sup>2</sup> | °C   |

1. Values mentioned are measured at  $\leq$  112 MHz in HSRUN mode.

2. Values mentioned are measured at  $\leq$  80 MHz in RUN mode.

#### Table 4. Supplies decoupling capacitors 1, 2

| Symbol                                                      | Description                               | Min. <sup>3</sup> | Тур. | Max. | Unit |

|-------------------------------------------------------------|-------------------------------------------|-------------------|------|------|------|

| C <sub>REF</sub> <sup>, 4</sup> , <sup>5</sup>              | ADC reference high decoupling capacitance | 70                | 100  |      | nF   |

| C <sub>DEC</sub> <sup>5</sup> , <sup>6</sup> , <sup>7</sup> | Recommended decoupling capacitance        | 70                | 100  |      | nF   |

V<sub>DD</sub> and V<sub>DDA</sub> must be shorted to a common source on PCB. The differential voltage between V<sub>DD</sub> and V<sub>DDA</sub> is for RF-AC only. Appropriate decoupling capacitors to be used to filter noise on the supplies. See application note AN5032 for reference supply design for SAR ADC. All V<sub>SS</sub> pins should be connected to common ground at the PCB level.

2. All decoupling capacitors must be low ESR ceramic capacitors (for example X7R type).

3. Minimum recommendation is after considering component aging and tolerance.

4. For improved performance, it is recommended to use 10 µF, 0.1 µF and 1 nF capacitors in parallel.

5. All decoupling capacitors should be placed as close as possible to the corresponding supply and ground pins.

6. Contact your local Field Applications Engineer for details on best analog routing practices.

7. The filtering used for decoupling the device supplies must comply with the following best practices rules:

• The protection/decoupling capacitors must be on the path of the trace connected to that component.

• No trace exceeding 1 mm from the protection to the trace or to the ground.

• The protection/decoupling capacitors must be as close as possible to the input pin of the device (maximum 2 mm).

• The ground of the protection is connected as short as possible to the ground plane under the integrated circuit.

#### I/O parameters

- 6. Several I/O have both high drive and normal drive capability selected by the associated Portx\_PCRn[DSE] control bit. All other GPIOs are normal drive only. For details see IO Signal Description Input Multiplexing sheet(s) attached with the *Reference Manual*.

- 7. When using ENET and SAI on S32K148, the overall device limits associated with high drive pin configurations must be respected i.e. On 144-pin LQFP the general purpose pins: PTA10, PTD0, and PTE4 must be set to low drive.

- 8. Measured at input  $V = V_{SS}$

- 9. Measured at input  $V = V_{DD}$

# 5.4 DC electrical specifications at 5.0 V Range

| Symbol                                              | Parameter                                                                      |                           | Value                   |                        | Unit | Notes |

|-----------------------------------------------------|--------------------------------------------------------------------------------|---------------------------|-------------------------|------------------------|------|-------|

|                                                     |                                                                                | Min.                      | Тур.                    | Max.                   |      |       |

| V <sub>DD</sub>                                     | I/O Supply Voltage                                                             | 4                         | _                       | 5.5                    | V    |       |

| V <sub>ih</sub>                                     | Input Buffer High Voltage                                                      | 0.65 x<br>V <sub>DD</sub> | _                       | V <sub>DD</sub> + 0.3  | V    | 1     |

| V <sub>il</sub>                                     | Input Buffer Low Voltage                                                       | V <sub>SS</sub> – 0.3     | _                       | 0.35 x V <sub>DD</sub> | V    | 2     |

| V <sub>hys</sub>                                    | Input Buffer Hysteresis                                                        | 0.06 x<br>V <sub>DD</sub> | _                       | —                      | V    |       |

| loh <sub>GPIO</sub><br>loh <sub>GPIO-HD_DSE_0</sub> | I/O current source capability measured when pad $V_{oh}$ = ( $V_{DD}$ - 0.8 V) | 5                         | _                       | —                      | mA   |       |

| Iol <sub>GPIO</sub><br>Iol <sub>GPIO-HD_DSE_0</sub> | I/O current sink capability measured when pad $V_{\rm ol}{=}$ 0.8 V            | 5                         | _                       | —                      | mA   |       |

| Ioh <sub>GPIO-HD_DSE_1</sub>                        | I/O current source capability measured when pad $V_{oh} = V_{DD} - 0.8 V$      | 20                        | _                       | —                      | mA   | 3     |

| IOI <sub>GPIO-HD_DSE_1</sub>                        | I/O current sink capability measured when pad $V_{ol} = 0.8 V$                 | 20                        | _                       | —                      | mA   | 3     |

| Ioh <sub>GPIO-FAST_DSE_0</sub>                      | I/O current sink capability measured when pad $V_{oh} = V_{DD} - 0.8 V$        | 14.0                      | —                       | —                      | mA   | 4     |

| IOI <sub>GPIO-FAST_DSE_0</sub>                      | I/O current sink capability measured when pad $V_{ol}$ = 0.8 V                 | 14.5                      | —                       | _                      | mA   | 4     |

| loh <sub>GPIO-FAST_DSE_1</sub>                      | I/O current sink capability measured when pad $V_{oh} = V_{DD} - 0.8 V$        | 21                        | —                       | —                      | mA   | 4     |

| IOI <sub>GPIO-FAST_DSE_1</sub>                      | I/O current sink capability measured when pad $V_{ol}$ = 0.8 V                 | 20.5                      | —                       | —                      | mA   | 4     |

| IOHT                                                | Output high current total for all ports                                        | —                         |                         | 100                    | mA   |       |

| IIN                                                 | Input leakage current (per pin) for full te                                    | mperature r               | ange at V <sub>DD</sub> | <sub>0</sub> = 5.5 V   |      | 5     |

| All pins other than high drive port pins            |                                                                                |                           | 0.005                   | 0.5                    | μA   |       |

|                                                     | High drive port pins                                                           |                           | 0.010                   | 0.5                    | μA   |       |

| R <sub>PU</sub>                                     | Internal pullup resistors                                                      | 20                        |                         | 50                     | kΩ   | 6     |

| R <sub>PD</sub>                                     | Internal pulldown resistors                                                    | 20                        |                         | 50                     | kΩ   | 7     |

Table 12. DC electrical specifications at 5.0 V Range

1. For reset pads, same V<sub>ih</sub> levels are applicable

2. For reset pads, same V<sub>il</sub> levels are applicable

- 3. The strong pad I/O pin is capable of switching a 50 pF load up to 40 MHz.

- 4. For refernce only. Run simulations with the IBIS model and custom board for accurate results.

#### S32K1xx Data Sheet, Rev. 8, 06/2018

- 5. Several I/O have both high drive and normal drive capability selected by the associated Portx\_PCRn[DSE] control bit. All other GPIOs are normal drive only. For details refer to *SK3K144\_IO\_Signal\_Description\_Input\_Multiplexing.xlsx* attached with the *Reference Manual*.

- 6. Measured at input  $V = V_{SS}$

- 7. Measured at input  $V = V_{DD}$

| Symbol                   | DSE | Rise tir | ne (nS) <sup>1</sup> | Fall tin | ne (nS) <sup>1</sup> | Capacitance (pF) <sup>2</sup> |

|--------------------------|-----|----------|----------------------|----------|----------------------|-------------------------------|

|                          |     | Min.     | Max.                 | Min.     | Max.                 |                               |

| tRF <sub>GPIO</sub>      | NA  | 3.2      | 14.5                 | 3.4      | 15.7                 | 25                            |

|                          |     | 5.7      | 23.7                 | 6.0      | 26.2                 | 50                            |

|                          |     | 20.0     | 80.0                 | 20.8     | 88.4                 | 200                           |

| tRF <sub>GPIO-HD</sub>   | 0   | 3.2      | 14.5                 | 3.4      | 15.7                 | 25                            |

|                          |     | 5.7      | 23.7                 | 6.0      | 26.2                 | 50                            |

|                          |     | 20.0     | 80.0                 | 20.8     | 88.4                 | 200                           |

|                          | 1   | 1.5      | 5.8                  | 1.7      | 6.1                  | 25                            |

|                          |     | 2.4      | 8.0                  | 2.6      | 8.3                  | 50                            |

|                          |     | 6.3      | 22.0                 | 6.0      | 23.8                 | 200                           |

| tRF <sub>GPIO-FAST</sub> | 0   | 0.6      | 2.8                  | 0.5      | 2.8                  | 25                            |

|                          |     | 3.0      | 7.1                  | 2.6      | 7.5                  | 50                            |

|                          |     | 12.0     | 27.0                 | 10.3     | 26.8                 | 200                           |

|                          | 1   | 0.4      | 1.3                  | 0.38     | 1.3                  | 25                            |

|                          |     | 1.5      | 3.8                  | 1.4      | 3.9                  | 50                            |

|                          |     | 7.4      | 14.9                 | 7.0      | 15.3                 | 200                           |

# 5.5 AC electrical specifications at 3.3 V range

Table 13. AC electrical specifications at 3.3 V Range

1. For reference only. Run simulations with the IBIS model and your custom board for accurate results.

2. Maximum capacitances supported on Standard IOs. However interface or protocol specific specifications might be different, for example for ENET, QSPI etc. . For protocol specific AC specifications, see respective sections.

# 5.6 AC electrical specifications at 5 V range

| Symbol                 | DSE | Rise tir | me (nS) <sup>1</sup> | Fall tim | ie (nS) <sup>1</sup> | Capacitance (pF) <sup>2</sup> |

|------------------------|-----|----------|----------------------|----------|----------------------|-------------------------------|

|                        |     | Min.     | Max .                | Min.     | Max.                 |                               |

| tRF <sub>GPIO</sub>    | NA  | 2.8      | 9.4                  | 2.9      | 10.7                 | 25                            |

|                        |     | 5.0      | 15.7                 | 5.1      | 17.4                 | 50                            |

|                        |     | 17.3     | 54.8                 | 17.6     | 59.7                 | 200                           |

| tRF <sub>GPIO-HD</sub> | 0   | 2.8      | 9.4                  | 2.9      | 10.7                 | 25                            |

|                        |     | 5.0      | 15.7                 | 5.1      | 17.4                 | 50                            |

#### Table 14. AC electrical specifications at 5 V Range

Table continues on the next page...

S32K1xx Data Sheet, Rev. 8, 06/2018

# Table 17. External System Oscillator electrical specifications (continued)

| Symbol          | Description                                             | Min. | Тур. | Max. | Unit | Notes |

|-----------------|---------------------------------------------------------|------|------|------|------|-------|

|                 | High-gain mode (HGO=1)                                  | —    | 1    | _    | MΩ   |       |

| R <sub>S</sub>  | R <sub>S</sub> Series resistor                          |      |      |      |      |       |

|                 | Low-gain mode (HGO=0)                                   | _    | 0    | _    | kΩ   |       |

|                 | High-gain mode (HGO=1)                                  | _    | 0    | _    | kΩ   |       |

| V <sub>pp</sub> | Peak-to-peak amplitude of oscillation (oscillator mode) |      |      |      |      | 3     |

|                 | Low-gain mode (HGO=0)                                   | _    | 1.0  | _    | V    |       |

|                 | High-gain mode (HGO=1)                                  |      | 3.3  | _    | V    |       |

1. Crystal oscillator circuit provides stable oscillations when  $g_{mXOSC} > 5 * gm_{crit}$ . The gm\_crit is defined as:

gm\_crit = 4 \* ESR \*  $(2\pi F)^2$  \*  $(C_0 + C_L)^2$

where:

2.

- $g_{mXOSC}$  is the transconductance of the internal oscillator circuit

- ESR is the equivalent series resistance of the external crystal

- F is the external crystal oscillation frequency

- C<sub>0</sub> is the shunt capacitance of the external crystal

- $C_L$  is the external crystal total load capacitance.  $C_L = C_s + [C_1 * C_2 / (C_1 + C_2)]$

- $C_s$  is stray or parasitic capacitance on the pin due to any PCB traces

- $C_1$ ,  $C_2$  external load capacitances on EXTAL and XTAL pins

See manufacture datasheet for external crystal component values

- When low-gain is selected, internal R<sub>F</sub> will be selected and external R<sub>F</sub> should not be attached.

- When high-gain is selected, external R<sub>F</sub> (1 M Ohm) needs to be connected for proper operation of the crystal. For external resistor, up to 5% tolerance is allowed.

- 3. The EXTAL and XTAL pins should only be connected to required oscillator components and must not be connected to any other devices.

# 6.2.2 External System Oscillator frequency specifications

## 6.3.1.1 Flash timing specifications — commands Table 23. Flash command timing specifications for S32K14x

| Symbol                | Descrip                                          | tion <sup>1</sup>         | S32 | K142 | S3  | 2K144 | S32 | K146  | S32K148 |          |      |       |

|-----------------------|--------------------------------------------------|---------------------------|-----|------|-----|-------|-----|-------|---------|----------|------|-------|

|                       |                                                  |                           | Тур | Max  | Тур | Max   | Тур | Max   | Тур     | Max      | Unit | Notes |

| t <sub>rd1blk</sub>   | Read 1 Block                                     | 32 KB flash               | _   | _    | _   | _     | _   |       | _       | _        | ms   |       |

|                       | execution time                                   | 64 KB flash               |     | 0.5  | _   | 0.5   | _   | 0.5   | _       | _        |      |       |

|                       |                                                  | 128 KB flash              | _   | _    | _   | _     | _   | _     | _       | <u> </u> | -    |       |

|                       |                                                  | 256 KB flash              | _   | 2    | _   | —     | _   | _     | —       | -        | 1    |       |

|                       |                                                  | 512 KB flash              | _   | —    | -   | 1.8   | —   | 2     | —       | 2        |      |       |

| t <sub>rd1sec</sub>   | Read 1 Section                                   | 2 KB flash                | —   | 75   | —   | 75    | _   | 75    | —       | 75       | μs   |       |

|                       | execution time                                   | 4 KB flash                | —   | 100  | -   | 100   | —   | 100   | —       | 100      | 1    |       |

| t <sub>pgmchk</sub>   | Program Check execution time                     | —                         | _   | 95   | -   | 95    | -   | 95    |         | 100      | μs   |       |

| t <sub>pgm8</sub>     | Program Phrase execution time                    | —                         | 90  | 225  | 90  | 225   | 90  | 225   | 90      | 225      | μs   |       |

| t <sub>ersblk</sub>   | Erase Flash                                      | 32 KB flash               | —   | —    | -   | —     | —   | —     | —       | -        | ms   | 2     |

|                       | Block execution time                             | 64 KB flash               | 30  | 550  | 30  | 550   | 30  | 550   | —       | —        | 1    |       |

|                       |                                                  | 128 KB flash              | —   | —    | —   | —     | —   | —     | —       | -        | 1    |       |

|                       |                                                  | 256 KB flash              | 250 | 2125 | —   | —     | —   | —     | —       | —        |      |       |

|                       |                                                  | 512 KB flash              | —   | —    | 250 | 4250  | 250 | 4250  | 250     | 4250     |      |       |

| t <sub>ersscr</sub>   | Erase Flash<br>Sector execution<br>time          |                           | 12  | 130  | 12  | 130   | 12  | 130   | 12      | 130      | ms   | 2     |

| t <sub>pgmsec1k</sub> | Program Section<br>execution time<br>(1KB flash) |                           | 5   | _    | 5   | -     | 5   | _     | 5       | —        | ms   |       |

| t <sub>rd1all</sub>   | Read 1s All<br>Block execution<br>time           |                           | _   | 2.8  | _   | 2.3   | -   | 5.2   | —       | 8.2      | ms   |       |

| t <sub>rdonce</sub>   | Read Once<br>execution time                      | _                         | -   | 30   | —   | 30    | -   | 30    | -       | 30       | μs   |       |

| t <sub>pgmonce</sub>  | Program Once<br>execution time                   | —                         | 90  | —    | 90  | —     | 90  | —     | 90      | -        | μs   |       |

| t <sub>ersall</sub>   | Erase All Blocks execution time                  | —                         | 250 | 2800 | 400 | 4900  | 700 | 10000 | 1400    | 17000    | ms   | 2     |

| t <sub>vfykey</sub>   | Verify Backdoor<br>Access Key<br>execution time  | _                         | _   | 35   | _   | 35    | -   | 35    | -       | 35       | μs   |       |

| t <sub>ersallu</sub>  | Erase All Blocks<br>Unsecure<br>execution time   |                           | 250 | 2800 | 400 | 4900  | 700 | 10000 | 1400    | 17000    | ms   | 2     |

| t <sub>pgmpart</sub>  | Program<br>Partition for<br>EEPROM               | 32 KB<br>EEPROM<br>backup | 70  | _    | 70  | _     | 70  | —     | —       | —        | ms   | 3     |

| 1                     | execution time                                   | 64 KB<br>EEPROM<br>backup | 71  | _    | 71  | -     | 71  | —     | 150     | —        | -    |       |

Table continues on the next page...

#### Memory and memory interfaces

| Symbol                  | Description <sup>1</sup>                                            |                                                         | S32  | K142 | S3   | 2K144 | S32  | K146 | S32  | 2K148 |      |                                 |

|-------------------------|---------------------------------------------------------------------|---------------------------------------------------------|------|------|------|-------|------|------|------|-------|------|---------------------------------|

|                         |                                                                     |                                                         | Тур  | Max  | Тур  | Max   | Тур  | Max  | Тур  | Max   | Unit | Notes                           |

| t <sub>setram</sub>     | Set FlexRAM<br>Function                                             | Control<br>Code 0xFF                                    | 0.08 | —    | 0.08 | —     | 0.08 |      | 0.08 | _     | ms   | 3                               |

|                         | execution time                                                      | 32 KB<br>EEPROM<br>backup                               | 0.8  | 1.2  | 0.8  | 1.2   | 0.8  | 1.2  | _    | -     |      |                                 |

|                         |                                                                     | 48 KB<br>EEPROM<br>backup                               | 1    | 1.5  | 1    | 1.5   | 1    | 1.5  |      | _     |      |                                 |

|                         |                                                                     | 64 KB<br>EEPROM<br>backup                               | 1.3  | 1.9  | 1.3  | 1.9   | 1.3  | 1.9  | 1.3  | 1.9   |      |                                 |

| t <sub>eewr8b</sub>     | Byte write to<br>FlexRAM<br>execution time                          | 32 KB<br>EEPROM<br>backup                               | 385  | 1700 | 385  | 1700  | 385  | 1700 | _    | -     | μs   | 3 <sup>,</sup> 4                |

|                         |                                                                     | 48 KB<br>EEPROM<br>backup                               | 430  | 1850 | 430  | 1850  | 430  | 1850 | _    | -     |      |                                 |

|                         |                                                                     | 64 KB<br>EEPROM<br>backup                               | 475  | 2000 | 475  | 2000  | 475  | 2000 | 475  | 4000  |      |                                 |

| t <sub>eewr16b</sub>    | 16-bit write to<br>FlexRAM<br>execution time                        | 32 KB<br>EEPROM<br>backup                               | 385  | 1700 | 385  | 1700  | 385  | 1700 |      | _     | μs   | 3 <sup>,</sup> 4                |

|                         |                                                                     | 48 KB<br>EEPROM<br>backup                               | 430  | 1850 | 430  | 1850  | 430  | 1850 | _    | -     |      |                                 |

|                         |                                                                     | 64 KB<br>EEPROM<br>backup                               | 475  | 2000 | 475  | 2000  | 475  | 2000 | 475  | 4000  |      |                                 |

| t <sub>eewr32bers</sub> | 32-bit write to<br>erased FlexRAM<br>location<br>execution time     | _                                                       | 360  | 2000 | 360  | 2000  | 360  | 2000 | 360  | 2000  | μs   |                                 |

| t <sub>eewr32b</sub>    | 32-bit write to<br>FlexRAM<br>execution time                        | 32 KB<br>EEPROM<br>backup                               | 630  | 2000 | 630  | 2000  | 630  | 2000 | _    | -     | μs   | 3 <sup>,</sup> 4                |

|                         |                                                                     | 48 KB<br>EEPROM<br>backup                               | 720  | 2125 | 720  | 2125  | 720  | 2125 | _    | -     |      |                                 |

|                         |                                                                     | 64 KB<br>EEPROM<br>backup                               | 810  | 2250 | 810  | 2250  | 810  | 2250 | 810  | 4500  |      |                                 |

| t <sub>quickwr</sub>    | 32-bit Quick<br>Write execution                                     | 1st 32-bit<br>write                                     | 200  | 550  | 200  | 550   | 200  | 550  | 200  | 1100  | μs   | 4 <sup>,</sup> 5 <sup>,</sup> 6 |

|                         | time: Time from<br>CCIF clearing<br>(start the write)<br>until CCIF | 2nd through<br>Next to Last<br>(Nth-1) 32-<br>bit write | 150  | 550  | 150  | 550   | 150  | 550  | 150  | 550   |      |                                 |

Table 23. Flash command timing specifications for S32K14x (continued)

Table continues on the next page...

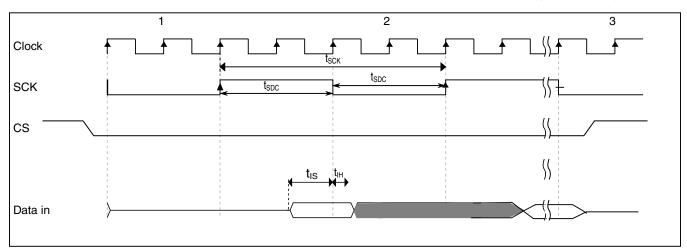

Figure 9. QuadSPI input timing (SDR mode) diagram

Figure 10. QuadSPI output timing (SDR mode) diagram

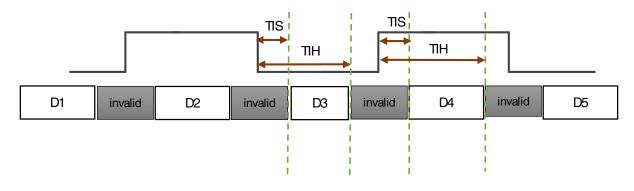

TIS-Setup Time TIH-Hold Time

Figure 11. QuadSPI input timing (HyperRAM mode) diagram

| Symbol               | Description                | Conditions <sup>1</sup> | Min. | Typ. <sup>2</sup> | Max.                                                 | Unit             | Notes      |

|----------------------|----------------------------|-------------------------|------|-------------------|------------------------------------------------------|------------------|------------|

| V <sub>DDA</sub>     | Supply voltage             |                         | 3    | —                 | 5.5                                                  | V                |            |

| I <sub>DDA_ADC</sub> | Supply current per ADC     |                         | —    | 1                 | —                                                    | mA               | 3          |

| SMPLTS               | Sample Time                |                         | 275  | _                 | Refer to<br>the<br><i>Reference</i><br><i>Manual</i> | ns               |            |

| TUE <sup>4</sup>     | Total unadjusted error     |                         | —    | ±4                | ±8                                                   | LSB <sup>5</sup> | 6, 7, 8, 9 |

| DNL                  | Differential non-linearity |                         | —    | ±0.7              | —                                                    | LSB <sup>5</sup> | 6, 7, 8, 9 |

| INL                  | Integral non-linearity     |                         | —    | ±1.0              | —                                                    | LSB <sup>5</sup> | 6, 7, 8, 9 |

Table 29. 12-bit ADC characteristics (3 V to 5.5 V)(V<sub>REFH</sub> = V<sub>DDA</sub>, V<sub>REFL</sub> = V<sub>SS</sub>)

- 1. All accuracy numbers assume the ADC is calibrated with V<sub>REFH</sub>=V<sub>DDA</sub>=V<sub>DD</sub>, with the calibration frequency set to less than or equal to half of the maximum specified ADC clock frequency.

- 2. Typical values assume  $V_{DDA} = 5.0 \text{ V}$ , Temp = 25 °C,  $f_{ADCK} = 40 \text{ MHz}$ ,  $R_{AS}=20 \Omega$ , and  $C_{AS}=10 \text{ nF}$  unless otherwise stated.

- 3. The ADC supply current depends on the ADC conversion rate.

- 4. Represents total static error, which includes offset and full scale error.

- 5. 1 LSB =  $(V_{REFH} V_{REFL})/2^N$

- 6. The specifications are with averaging and in standalone mode only. Performance may degrade depending upon device use case scenario. When using ADC averaging, refer to the *Reference Manual* to determine the most appropriate settings for AVGS.

- For ADC signals adjacent to V<sub>DD</sub>/V<sub>SS</sub> or XTAL/EXTAL or high frequency switching pins, some degradation in the ADC performance may be observed.

- 8. All values guarantee the performance of the ADC for multiple ADC input channel pins. When using ADC to monitor the internal analog parameters, assume minor degradation.

- 9. All the parameters in the table are given assuming system clock as the clocking source for ADC.

### NOTE

- Due to triple bonding in lower pin packages like 32-QFN, 48-LQFP, and 64-LQFP degradation might be seen in ADC parameters.

- When using high speed interfaces such as the QuadSPI, SAI0, SAI1 or ENET there may be some ADC degradation on the adjacent analog input paths. See following table for details.

| Pin name | TGATE purpose      |

|----------|--------------------|

| PTE8     | CMP0_IN3           |

| PTC3     | ADC0_SE11/CMP0_IN4 |

| PTC2     | ADC0_SE10/CMP0_IN5 |

| PTD7     | CMP0_IN6           |

| PTD6     | CMP0_IN7           |

| PTD28    | ADC1_SE22          |

| PTD27    | ADC1_SE21          |

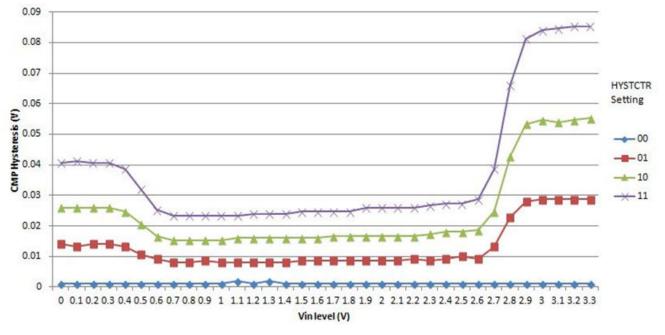

| Symbol             | Description                                          | Min.  | Тур. | Max. | Unit             |

|--------------------|------------------------------------------------------|-------|------|------|------------------|

|                    | Analog comparator hysteresis, Hyst2, Low-speed mode  |       |      |      |                  |

|                    | -40 - 125 °C                                         | _     | 23   | 80   |                  |

| V <sub>HYST3</sub> | Analog comparator hysteresis, Hyst3, High-speed mode |       |      |      | mV               |

|                    | -40 - 125 °C                                         | _     | 46   | 200  |                  |

|                    | Analog comparator hysteresis, Hyst3, Low-speed mode  |       |      |      |                  |

|                    | -40 - 125 °C                                         | _     | 32   | 120  |                  |

| I <sub>DAC8b</sub> | 8-bit DAC current adder (enabled)                    |       | 1    |      |                  |

|                    | 3.3V Reference Voltage                               | _     | 6    | 9    | μA               |

|                    | 5V Reference Voltage                                 | _     | 10   | 16   | μA               |

| INL <sup>5</sup>   | 8-bit DAC integral non-linearity                     | -0.75 | _    | 0.75 | LSB <sup>6</sup> |

| DNL                | 8-bit DAC differential non-linearity                 | -0.5  | _    | 0.5  | LSB <sup>6</sup> |

| t <sub>DDAC</sub>  | Initialization and switching settling time           | —     | _    | 30   | μs               |

Table 31. Comparator with 8-bit DAC electrical specifications (continued)

1. Difference at input > 200mV

2. Applied  $\pm$  (100 mV + V<sub>HYST0/1/2/3</sub>+ max. of V<sub>AIO</sub>) around switch point.

3. Applied ± (30 mV + 2 ×  $V_{HYST0/1/2/3}$ + max. of  $V_{AIO}$ ) around switch point.

4. Applied  $\pm$  (100 mV + V<sub>HYST0/1/2/3</sub>).

5. Calculation method used: Linear Regression Least Square Method

6. 1 LSB =  $V_{reference}/256$

# NOTE

For comparator IN signals adjacent to  $V_{DD}/V_{SS}$  or XTAL/ EXTAL or switching pins cross coupling may happen and hence hysteresis settings can be used to obtain the desired comparator performance. Additionally, an external capacitor (1nF) should be used to filter noise on input signal. Also, source drive should not be weak (Signal with < 50 K pull up/down is recommended).

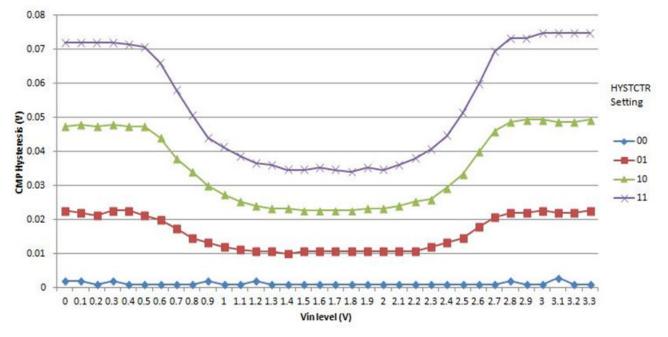

Figure 14. Typical hysteresis vs. Vin level (VDDA = 3.3 V, PMODE = 0)

Figure 15. Typical hysteresis vs. Vin level (VDDA = 3.3 V, PMODE = 1)

**Communication modules**

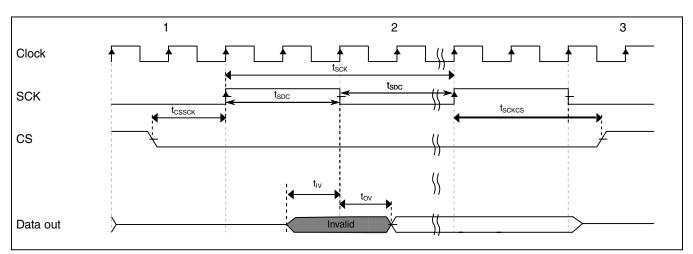

## Table 32. LPSPI electrical specifications1 (continued)

| Num | Symbol                | Description                           | Conditions                            |                                  | Run                                   | Mode <sup>2</sup>                |            |                                  | HSRU       | N Mode <sup>2</sup>                  |            |                                     | VLPR       | Mode                               |            | Unit |    |  |

|-----|-----------------------|---------------------------------------|---------------------------------------|----------------------------------|---------------------------------------|----------------------------------|------------|----------------------------------|------------|--------------------------------------|------------|-------------------------------------|------------|------------------------------------|------------|------|----|--|

|     |                       |                                       |                                       | 5.0 V IO                         |                                       | 3.3 V IO                         |            | 5.0 V IO                         |            | 3.3 V IO                             |            | 5.0 V IO                            |            | 3.3                                | V IO       |      |    |  |

|     |                       |                                       |                                       | Min.                             | Max.                                  | Min.                             | Max.       | Min.                             | Max.       | Min.                                 | Max.       | Min.                                | Max.       | Min.                               | Max.       | 1    |    |  |

| 4   | t <sub>Lag</sub> 9    | Enable lag                            | Slave                                 | -                                | -                                     | -                                | -          | -                                | -          | -                                    | -          | -                                   | -          | -                                  | -          | ns   |    |  |

|     |                       | time (After<br>SPSCK delay)           | Master                                |                                  |                                       | - 25                             | -          |                                  | -          |                                      | -          |                                     | -          |                                    | -          |      |    |  |

|     |                       | of corracially)                       | Master<br>Loopback <sup>5</sup>       | - 25                             |                                       |                                  |            | - 25                             |            | - 25                                 |            | - 50                                |            | 50                                 |            |      |    |  |

|     |                       |                                       | Master<br>Loopback(slow) <sup>6</sup> | (SCKPCS+1)*t <sub>periph</sub> - |                                       | (SCKPCS+1)*t <sub>periph</sub> - |            | (SCKPCS+1)*t <sub>periph</sub> - |            | (SCKPCS+1)*t <sub>periph</sub> - 25  |            | (SCKPCS+1)*t <sub>periph</sub> - 50 |            | (SCKPCS+1)*t <sub>periph</sub> -50 |            |      |    |  |

| 5   | twspsck <sup>10</sup> |                                       |                                       |                                  |                                       |                                  |            |                                  |            |                                      |            |                                     |            |                                    |            | ns   |    |  |

|     |                       | ) high or low<br>time (SPSCK          | Master                                | tsPSCK/2-3                       | tspsck/2+3                            | ကို                              | ۴+<br>۲-   | ကို                              | ς<br>+3    | က်                                   | с+3        | 2-5                                 | 5+5        | 2-2                                | 5+2        |      |    |  |

|     |                       | duty cycle)                           | Master<br>Loopback <sup>5</sup>       |                                  |                                       | tspsck/2-3                       | tspsck/2+3 | tspsck/2-3                       | tspsck/2+3 | tspsck/2-3                           | tspsck/2+3 | tspsck/2-5                          | tspsck/2+5 | tspsck/2-5                         | tsPSCK/2+5 |      |    |  |

|     |                       |                                       | Master<br>Loopback(slow) <sup>6</sup> | <b>H</b>                         | <u>ب</u>                              | +                                | μ,         | +                                | ÷.         | -                                    | ÷.         | -                                   | ů.         | -                                  | <u>ب</u>   |      |    |  |

| 6   | t <sub>SU</sub>       | Data setup<br>time(inputs)            |                                       | Slave                            | 3                                     | -                                | 5          | -                                | 3          | -                                    | 5          | -                                   | 18         | -                                  | 18         | -    | ns |  |

|     |                       |                                       | Master                                | 29                               | -                                     | 38                               | -          | 26                               | -          | 37 <sup>11</sup><br>32 <sup>12</sup> | -          | 72                                  | -          | 78                                 | -          | _    |    |  |

|     |                       |                                       | Master<br>Loopback <sup>5</sup>       | 7                                | -                                     | 8                                | -          | 5                                | -          | 7                                    | -          | 20                                  | -          | 20                                 | -          | -    |    |  |

|     |                       |                                       |                                       |                                  | Master<br>Loopback(slow) <sup>6</sup> | 8                                | -          | 10                               | -          | 7                                    | -          | 9                                   | -          | 20                                 | -          | 20   | -  |  |

| 7   | t <sub>HI</sub>       | Data hold                             | Slave                                 | 3                                | -                                     | 3                                | -          | 3                                | -          | 3                                    | -          | 14                                  | -          | 14                                 | -          | ns   |    |  |

|     |                       | time(inputs)                          | Master 0 - 0 -                        | 0                                | -                                     | 0                                | -          | 0                                | -          | 0                                    | -          |                                     |            |                                    |            |      |    |  |

|     |                       |                                       | Master<br>Loopback <sup>5</sup>       | 3                                | -                                     | 3                                | -          | 2                                | -          | 3                                    | -          | 11                                  | -          | 11                                 | -          |      |    |  |

|     |                       | Master<br>Loopback(slow) <sup>6</sup> | 3                                     | -                                | 3                                     | -                                | 3          | -                                | 3          | -                                    | 12         | -                                   | 12         | -                                  |            |      |    |  |

Table continues on the next page...

52

S32K1xx Data Sheet, Rev. 8, 06/2018

### Table 32. LPSPI electrical specifications1 (continued)

| Γ | Num | Symbol | Description | Conditions                    | Run Mode <sup>2</sup> |      |          | HSRUN Mode <sup>2</sup> |          |      |          | VLPR Mode |          |      |          | Unit |  |

|---|-----|--------|-------------|-------------------------------|-----------------------|------|----------|-------------------------|----------|------|----------|-----------|----------|------|----------|------|--|

|   |     |        |             |                               | 5.0 V IO              |      | 3.3 V IO |                         | 5.0 V IO |      | 3.3 V IO |           | 5.0 V IO |      | 3.3 V IO |      |  |

|   |     |        |             |                               | Min.                  | Max. | Min.     | Max.                    | Min.     | Max. | Min.     | Max.      | Min.     | Max. | Min.     | Max. |  |

|   |     |        |             | Master<br>Loopback(slow)<br>6 | -                     |      | -        |                         | -        |      | -        |           | -        |      | -        |      |  |

- 1. Trace length should not exceed 11 inches for SCK pad when used in Master loopback mode.

- 2. While transitioning from HSRUN mode to RUN mode, LPSPI output clock should not be more than 14 MHz.

- 3. f<sub>periph</sub> = LPSPI peripheral clock

- 4.  $t_{periph} = 1/f_{periph}$

- 5. Master Loopback mode In this mode LPSPI\_SCK clock is delayed for sampling the input data which is enabled by setting LPSPI\_CFGR1[SAMPLE] bit as 1. Clock pads used are PTD15 and PTE0. Applicable only for LPSPI0.

- 6. Master Loopback (slow) In this mode LPSPI\_SCK clock is delayed for sampling the input data which is enabled by setting LPSPI\_CFGR1[SAMPLE] bit as 1. Clock pad used is PTB2. Applicable only for LPSPI0.

- 7. This is the maximum operating frequency (f<sub>op</sub>) for LPSPI0 with medium PAD type only. Otherwise, the maximum operating frequency (f<sub>op</sub>) is 12 Mhz.

- 8. Set the PCSSCK configuration bit as 0, for a minimum of 1 delay cycle of LPSPI baud rate clock, where PCSSCK ranges from 0 to 255.

- 9. Set the SCKPCS configuration bit as 0, for a minimum of 1 delay cycle of LPSPI baud rate clock, where SCKPCS ranges from 0 to 255.

- 10. While selecting odd dividers, ensure Duty Cycle is meeting this parameter.

- 11. Maximum operating frequency (fop ) is 12 MHz irrespective of PAD type and LPSPI instance.

- 12. Applicable for LPSPI0 only with medium PAD type, with maximum operating frequency (f<sub>op</sub>) as 14 MHz.

S32K1xx

Data

Sheet,

Rev.

,œ

06/2018

**Communication modules**

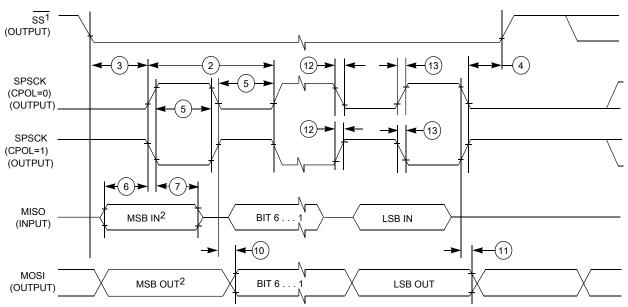

1. If configured as an output.

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

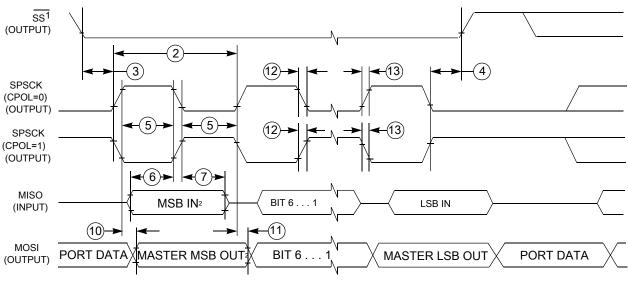

1.If configured as output

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

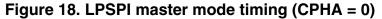

### Figure 19. LPSPI master mode timing (CPHA = 1)

#### **Communication modules**

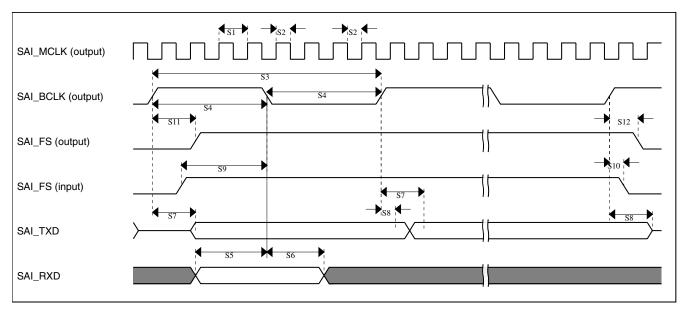

Figure 22. SAI Timing — Master modes

| Symbol           | Description                            | Min. | Max. | Unit        |

|------------------|----------------------------------------|------|------|-------------|

| _                | Operating voltage                      | 2.97 | 3.6  | V           |

| S13              | SAI_BCLK cycle time (input)            | 80   | _    | ns          |

| S14 <sup>1</sup> | SAI_BCLK pulse width high/low (input)  | 45%  | 55%  | BCLK period |

| S15              | SAI_RXD input setup before<br>SAI_BCLK | 8    | _    | ns          |

| S16              | SAI_RXD input hold after<br>SAI_BCLK   |      |      | ns          |

| S17              | SAI_BCLK to SAI_TXD output valid       |      | 28   | ns          |

| S18              | SAI_BCLK to SAI_TXD output invalid     | 0    | _    | ns          |

| S19              | SAI_FS input setup before<br>SAI_BCLK  | 8    | _    | ns          |

| S20              | SAI_FS input hold after SAI_BCLK       | 2    | _    | ns          |

| S21              | SAI_BCLK to SAI_FS output valid        | _    | 28   | ns          |

| S22              | SAI_BCLK to SAI_FS output invalid      | 0    | _    | ns          |

### Table 34. Slave mode timing specifications

1. The slave mode parameters (S15 - S22) assume 50% duty cycle on SAI\_BCLK input. Any change in SAI\_BCLK duty cycle input must be taken care during the board design or by the master timing.

# Table 42. Thermal characteristics for the 100 MAPBGA package

| Rating                                                                          | Conditions                 | Symbol           | ool Values |         |         |      |  |  |  |

|---------------------------------------------------------------------------------|----------------------------|------------------|------------|---------|---------|------|--|--|--|

|                                                                                 |                            |                  | S32K146    | S32K144 | S32K148 | 1    |  |  |  |

| Thermal resistance, Junction to Ambient (Natural Convection) <sup>1, 2</sup>    | Single layer board (1s)    | $R_{\thetaJA}$   | 57.2       | 61.0    | 52.5    | °C/W |  |  |  |

| Thermal resistance, Junction to Ambient (Natural Convection) <sup>1, 2, 3</sup> | Four layer board<br>(2s2p) | $R_{\thetaJA}$   | 32.1       | 35.6    | 27.5    | °C/W |  |  |  |

| Thermal resistance, Junction to Ambient (@200 ft/min) 1, 2, 3                   | Single layer board (1s)    | $R_{\theta JMA}$ | 44.1       | 46.6    | 39.0    | °C/W |  |  |  |

| Thermal resistance, Junction to Ambient (@200 ft/min) <sup>1, 3</sup>           | Two layer board<br>(2s2p)  | $R_{\theta JMA}$ | 27.2       | 30.9    | 22.8    | °C/W |  |  |  |

| Thermal resistance, Junction to Board <sup>4</sup>                              | —                          | R <sub>θJB</sub> | 15.3       | 18.9    | 11.2    | °C/W |  |  |  |

| Thermal resistance, Junction to Case <sup>5</sup>                               | —                          | R <sub>θJC</sub> | 10.2       | 14.2    | 7.5     | °C/W |  |  |  |

| Thermal resistance, Junction to Package Top outside center <sup>6</sup>         | —                          | Ψյт              | 0.2        | 0.4     | 0.2     | °C/W |  |  |  |

| Thermal resistance, Junction to Package Bottom outside center <sup>7</sup>      | —                          | Ψјв              | 12.2       | 15.9    | 18.3    | °C/W |  |  |  |

1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

2. Per SEMI G38-87 and JEDEC JESD51-2 with the single layer board horizontal.

3. Per JEDEC JESD51-6 with the board horizontal.

4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

6. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

7. Thermal characterization parameter indicating the temperature difference between package bottom center and the junction temperature per JEDEC JESD51-12. When Greek letters are not available, the thermal characterization parameter is written as Psi-JB.

S32K1xx Data

۱ Sheet,

Rev.

<u>,</u>

06/2018

Rev. No.

Date

|   |               | <ul> <li>Updated 3.3 V numbers and added footnote against f<sub>op</sub>, t<sub>SU</sub>, ans t<sub>V</sub> in HSRUN Mode</li> <li>Added footnote to 't<sub>WSPSCK</sub>'</li> <li>Updated Thermal characteristics for S32K11x</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |