## NXP USA Inc. - FS32K144MFT0VLHR Datasheet

#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4F                                                         |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 64MHz                                                                    |

| Connectivity               | CANbus, FlexIO, I <sup>2</sup> C, LINbus, SPI, UART/USART                |

| Peripherals                | POR, PWM, WDT                                                            |

| Number of I/O              | 58                                                                       |

| Program Memory Size        | 512KB (512K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 4K x 8                                                                   |

| RAM Size                   | 64K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| Data Converters            | A/D 16x12b SAR; D/A1x8b                                                  |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-LQFP                                                                  |

| Supplier Device Package    | 64-LQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/fs32k144mft0vlhr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Communications interfaces

- Up to three Low Power Universal Asynchronous Receiver/Transmitter (LPUART/LIN) modules with DMA support and low power availability

- Up to three Low Power Serial Peripheral Interface (LPSPI) modules with DMA support and low power availability

- Up to two Low Power Inter-Integrated Circuit (LPI2C) modules with DMA support and low power availability

- Up to three FlexCAN modules (with optional CAN-FD support)

- FlexIO module for emulation of communication protocols and peripherals (UART, I2C, SPI, I2S, LIN, PWM, etc).

- Up to one 10/100Mbps Ethernet with IEEE1588 support and two Synchronous Audio Interface (SAI) modules.

- Safety and Security

- Cryptographic Services Engine (CSEc) implements a comprehensive set of cryptographic functions as described in the SHE (Secure Hardware Extension) Functional Specification. Note: CSEc (Security) or EEPROM writes/erase will trigger error flags in HSRUN mode (112 MHz) because this use case is not allowed to execute simultaneously. The device will need to switch to RUN mode (80 MHz) to execute CSEc (Security) or EEPROM writes/erase.

- 128-bit Unique Identification (ID) number

- Error-Correcting Code (ECC) on flash and SRAM memories

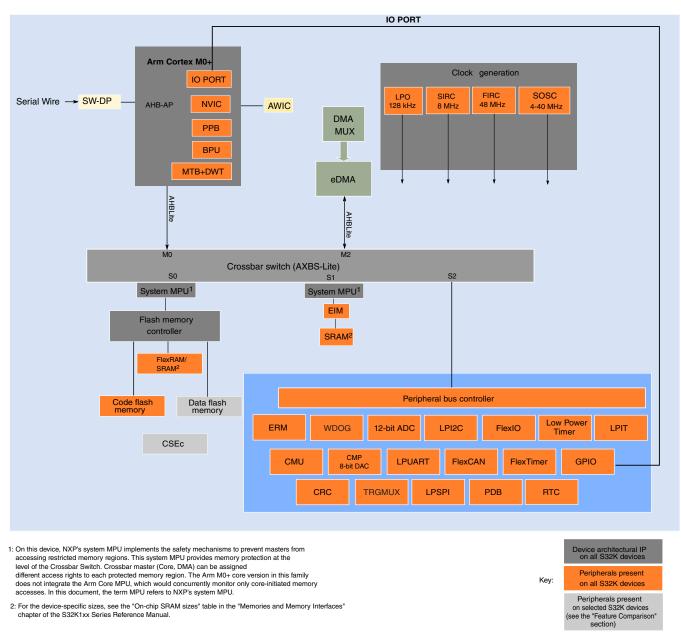

- System Memory Protection Unit (System MPU)

- Cyclic Redundancy Check (CRC) module

- Internal watchdog (WDOG)

- External Watchdog monitor (EWM) module

- Timing and control

- Up to eight independent 16-bit FlexTimers (FTM) modules, offering up to 64 standard channels (IC/OC/PWM)

- One 16-bit Low Power Timer (LPTMR) with flexible wake up control

- Two Programmable Delay Blocks (PDB) with flexible trigger system

- One 32-bit Low Power Interrupt Timer (LPIT) with 4 channels

- 32-bit Real Time Counter (RTC)

- Package

- 32-pin QFN, 48-pin LQFP, 64-pin LQFP, 100-pin LQFP, 100-pin MAPBGA, 144-pin LQFP, 176-pin LQFP package options

- 16 channel DMA with up to 63 request sources using DMAMUX

### Feature comparison

# 2 Feature comparison

The following figure summarizes the memory, peripherals and packaging options for the S32K1xx devices. All devices which share a common package are pin-to-pin compatible.

## NOTE

Availability of peripherals depends on the pin availability in a particular package. For more information see *IO Signal*

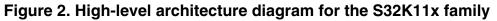

# 3.2 Ordering information

Product status

P: Prototype F: Qualified

Product type/brand S32: Automotive 32-bit MCU

Product line K: Arm Cortex MCUs

### Series/Family

1: 1st product series 2: 2nd product series

### Core platform/Performance

- 1: Arm Cortex M0+

- 4: Arm Cortex M4F

### Memory size

|         | 2    | 4    | 6    | 8    |

|---------|------|------|------|------|

| S32K11x |      |      | 128K | 256K |

| S32K14x | 256K | 512K | 1M   | 2M   |

### Ordering option

X: Speed

B: 48 MHz without DMA (S32K11x only) L: 48 MHz with DMA (S32K11x only) H: 80 MHz U<sup>1</sup>: 112 MHz (Not valid with M temperature/125C)

Y: Optional feature

- R: Base feature set

- F: CAN FD, FlexIO

- A1: CAN FD, FlexIO, Security

- E: Ethernet, Serial Audio Interface (S32K148 only) J1: Ethernet, Serial Audio Interface, CAN FD, FlexIO, Security (S32K148 only)

### Wafer, Fab and revision

Fx: ATMC<sup>2</sup> Tx: GF XX: Flex #<sup>2</sup>

x0: 1st revision

### Temperature

V: -40C to 105C M: -40C to 125C W: -40C to 150C<sup>2</sup>

### Package

| Pins | LQFP | QFN | BGA |

|------|------|-----|-----|

| 32   | -    | FM  | -   |

| 48   | LF   | -   | -   |

| 64   | LH   | -   | -   |

| 100  | LL   | -   | ΜΗ  |

| 144  | LQ   | -   | -   |

| 176  | LU   |     |     |

Tape and Reel T: Trays/Tubes R: Tape and Reel

1. CSEc (Security) or EEPROM writes/erase will trigger error flags in HSRUN mode (112 MHz) because this use case is not allowed to execute simultaneously. The device will need to switch to RUN mode (80 MHz) to execute CSEc (Security) or EEPROM writes/erase.

2. Not supported yet

3. Part numbers no longer offered as standard include:

Ordering Option X (M:64MHz); Ordering Option Y (N: limited RAM. 16KB for K142, 48KB for K144, 96KB for K146, 192KB for K148 S: Security); Temperature (C: -40C to 85C)

### NOTE

Not all part number combinations are available. See S32K1xx\_Orderable\_Part\_Number\_List.xlsx attached with the Datasheet for list of standard orderable parts.

## Figure 4. Ordering information

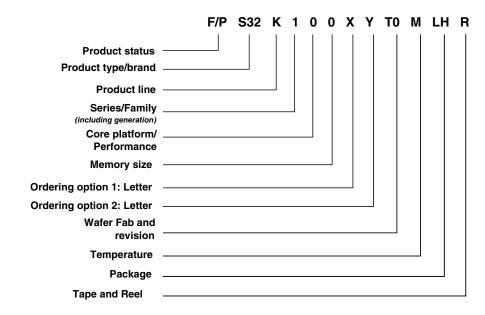

## General

- 4. When input pad voltage levels are close to V<sub>DD</sub> or V<sub>SS</sub>, practically no current injection is possible.

- 5. While respecting the maximum current injection limit

- 6. This is the Electronic Control Unit (ECU) supply ramp rate and not directly the MCU ramp rate. Limit applies to both maximum absolute maximum ramp rate and typical operating conditions.

- 7. This is the MCU supply ramp rate and the ramp rate assumes that the S32K1xx HW design guidelines in AN5426 are followed. Limit applies to both maximum absolute maximum ramp rate and typical operating conditions.

- 8. T<sub>J</sub> (Junction temperature)=135 °C. Assumes T<sub>A</sub>=125 °C for RUN mode

- T<sub>J</sub> (Junction temperature)=125 °C. Assumes TA=105 °C for HSRUN mode

- Assumes maximum θJA for 2s2p board. See Thermal characteristics

- 9. 60 seconds lifetime; device in reset (no outputs enabled/toggling)

# 4.2 Voltage and current operating requirements

## NOTE

Device functionality is guaranteed up to the LVR assert level, however electrical performance of 12-bit ADC, CMP with 8-bit DAC, IO electrical characteristics, and communication modules electrical characteristics would be degraded when voltage drops below 2.7 V

| Symbol                                 | Description                                                                                                                                                                                      | Min.             | Max.                   | Unit | Notes |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------|------|-------|

| V <sub>DD</sub> <sup>2</sup>           | Supply voltage                                                                                                                                                                                   | 2.7 <sup>3</sup> | 5.5                    | V    | 4     |

| $V_{DD_OFF}$                           | Voltage allowed to be developed on V <sub>DD</sub><br>pin when it is not powered from any<br>external power supply source.                                                                       | 0                | 0.1                    | V    |       |

| V <sub>DDA</sub>                       | Analog supply voltage                                                                                                                                                                            | 2.7              | 5.5                    | V    | 4     |

| $V_{DD} - V_{DDA}$                     | V <sub>DD</sub> -to-V <sub>DDA</sub> differential voltage                                                                                                                                        | - 0.1            | 0.1                    | V    | 4     |

| V <sub>REFH</sub>                      | ADC reference voltage high                                                                                                                                                                       | 2.7              | V <sub>DDA</sub> + 0.1 | V    | 5     |

| V <sub>REFL</sub>                      | ADC reference voltage low                                                                                                                                                                        | -0.1             | 0.1                    | V    |       |

| V <sub>ODPU</sub>                      | Open drain pullup voltage level                                                                                                                                                                  | V <sub>DD</sub>  | V <sub>DD</sub>        | V    | 6     |

| I <sub>INJPAD_DC_OP</sub> <sup>7</sup> | Continuous DC input current (positive / negative) that can be injected into an I/O pin                                                                                                           | -3               | +3                     | mA   |       |

| I <sub>INJSUM_DC_OP</sub>              | Continuous total DC input current that can<br>be injected across all I/O pins such that<br>there's no degradation in accuracy of<br>analog modules: ADC and ACMP (See<br>section Analog Modules) | _                | 30                     | mA   |       |

## Table 2. Voltage and current operating requirements 1

- Typical conditions assumes V<sub>DD</sub> = V<sub>DDA</sub> = V<sub>REFH</sub> = 5 V, temperature = 25 °C and typical silicon process unless otherwise stated.

- As V<sub>DD</sub> varies between the minimum value and the absolute maximum value the analog characteristics of the I/O and the ADC will both change. See section I/O parameters and ADC electrical specifications respectively for details.

- S32K148 will operate from 2.7 V when executing from internal FIRC. When the PLL is engaged S32K148 is guaranteed to operate from 2.97 V. All other S32K family devices operate from 2.7 V in all modes.

- V<sub>DD</sub> and V<sub>DDA</sub> must be shorted to a common source on PCB. The differential voltage between V<sub>DD</sub> and V<sub>DDA</sub> is for RF-AC only. Appropriate decoupling capacitors to be used to filter noise on the supplies. See application note AN5032 for reference supply design for SAR ADC.

- 5.  $V_{REFH}$  should always be equal to or less than  $V_{DDA}$  + 0.1 V and  $V_{DD}$  + 0.1 V

- 6. Open drain outputs must be pulled to  $V_{DD}$ .

- 7. When input pad voltage levels are close to  $V_{DD}$  or  $V_{SS}$ , practically no current injection is possible.

# 4.3 Thermal operating characteristics

# Table 3. Thermal operating characteristics for 64 LQFP, 100 LQFP, and 100 MAP-BGApackages.

| Symbol                      | Parameter                       | Value |      |                  | Unit |

|-----------------------------|---------------------------------|-------|------|------------------|------|

|                             |                                 | Min.  | Тур. | Max.             |      |

| T <sub>A C-Grade Part</sub> | Ambient temperature under bias  | -40   | —    | 85 <sup>1</sup>  | °C   |

| T <sub>J C-Grade Part</sub> | Junction temperature under bias | -40   | —    | 105 <sup>1</sup> | °C   |

| T <sub>A V-Grade Part</sub> | Ambient temperature under bias  | -40   | _    | 105 <sup>1</sup> | °C   |

| T <sub>J V-Grade Part</sub> | Junction temperature under bias | -40   | —    | 125 <sup>1</sup> | °C   |

| T <sub>A M-Grade Part</sub> | Ambient temperature under bias  | -40   | —    | 125 <sup>2</sup> | °C   |

| T <sub>J M-Grade Part</sub> | Junction temperature under bias | -40   | —    | 135 <sup>2</sup> | °C   |

1. Values mentioned are measured at  $\leq$  112 MHz in HSRUN mode.

2. Values mentioned are measured at  $\leq$  80 MHz in RUN mode.

\*Note: VSSA and VSS are shorted at package level

# 4.5 LVR, LVD and POR operating requirements

## Table 5. V<sub>DD</sub> supply LVR, LVD and POR operating requirements

| Symbol                | Description                                        | Min. | Тур.  | Max. | Unit | Notes |

|-----------------------|----------------------------------------------------|------|-------|------|------|-------|

| V <sub>POR</sub>      | Rising and falling $V_{DD}$ POR detect voltage     | 1.1  | 1.6   | 2.0  | V    |       |

| V <sub>LVR</sub>      | LVR falling threshold (RUN, HSRUN, and STOP modes) | 2.50 | 2.58  | 2.7  | V    |       |

| V <sub>LVR_HYST</sub> | LVR hysteresis                                     |      | 45    |      | mV   | 1     |

| $V_{LVR_{LP}}$        | LVR falling threshold (VLPS/VLPR modes)            | 1.97 | 2.22  | 2.44 | V    |       |

| V <sub>LVD</sub>      | Falling low-voltage detect threshold               | 2.8  | 2.875 | 3    | V    |       |

| V <sub>LVD_HYST</sub> | LVD hysteresis                                     | —    | 50    | _    | mV   | 1     |

Table continues on the next page ...

# 5.3 DC electrical specifications at 3.3 V Range

NOTE

For details on the pad types defined in Table 11 and Table 12, see Reference Manual section *IO Signal Table* and IO Signal Description Input Multiplexing sheet(s) attached with Reference Manual.

| Symbol                                              | Parameter                                                                           |                       | Value                   |                       | Unit | Notes |

|-----------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------|-------------------------|-----------------------|------|-------|

|                                                     |                                                                                     | Min.                  | Тур.                    | Max.                  |      |       |

| V <sub>DD</sub>                                     | I/O Supply Voltage                                                                  | 2.7                   | 3.3                     | 4                     | V    | 1     |

| V <sub>ih</sub>                                     | Input Buffer High Voltage                                                           | $0.7 \times V_{DD}$   | _                       | V <sub>DD</sub> + 0.3 | V    | 2     |

| V <sub>il</sub>                                     | Input Buffer Low Voltage                                                            | V <sub>SS</sub> – 0.3 |                         | $0.3 \times V_{DD}$   | V    | 3     |

| V <sub>hys</sub>                                    | Input Buffer Hysteresis                                                             | $0.06 \times V_{DD}$  | _                       | —                     | V    |       |

| loh <sub>GPIO</sub><br>loh <sub>GPIO-HD_DSE_0</sub> | I/O current source capability measured when pad $V_{oh} = (V_{DD} - 0.8 \text{ V})$ | 3.5                   | —                       | _                     | mA   |       |

| Iol <sub>GPIO</sub> -HD_DSE_0                       | I/O current sink capability measured when pad $V_{ol} = 0.8 \text{ V}$              | 3                     | _                       |                       | mA   |       |

| Ioh <sub>GPIO-HD_DSE_1</sub>                        | I/O current source capability measured when pad $V_{oh} = (V_{DD} - 0.8 \text{ V})$ | 14                    | —                       | _                     | mA   | 4     |

| Iol <sub>GPIO-HD_DSE_1</sub>                        | I/O current sink capability measured when pad $V_{\text{ol}}$ = 0.8 V               | 12                    | _                       | _                     | mA   | 4     |

| loh <sub>GPIO-FAST_DSE_0</sub>                      | I/O current sink capability measured when pad $V_{oh}{=}V_{DD}{-}0.8~V$             | 9.5                   | _                       | _                     | mA   | 5     |

| IOI <sub>GPIO-FAST_DSE_0</sub>                      | I/O current sink capability measured when pad $V_{\text{ol}}$ = 0.8 V               | 10                    | _                       | —                     | mA   | 5     |

| Ioh <sub>GPIO-FAST_DSE_1</sub>                      | I/O current sink capability measured when pad $V_{oh}{=}V_{DD}{-}0.8~V$             | 16                    | _                       | —                     | mA   | 5     |

| IOI <sub>GPIO-FAST_DSE_1</sub>                      | I/O current sink capability measured when pad $V_{\text{ol}}$ = 0.8 V               | 15.5                  | _                       | _                     | mA   | 5     |

| IOHT                                                | Output high current total for all ports                                             | _                     | _                       | 100                   | mA   |       |

| IIN                                                 | Input leakage current (per pin) for full tempera                                    | ture range at         | V <sub>DD</sub> = 3.3 V | /                     | 1    | 6     |

|                                                     | All pins other than high drive port pins                                            |                       | 0.005                   | 0.5                   | μA   |       |

|                                                     | High drive port pins <sup>7</sup>                                                   |                       | 0.010                   | 0.5                   | μA   | ]     |

| R <sub>PU</sub>                                     | Internal pullup resistors                                                           | 20                    |                         | 60                    | kΩ   | 8     |

| R <sub>PD</sub>                                     | Internal pulldown resistors                                                         | 20                    |                         | 60                    | kΩ   | 9     |

1. S32K148 will operate from 2.7 V when executing from internal FIRC. When the PLL is engaged S32K148 is guaranteed to operate from 2.97 V. All other S32K family devices operate from 2.7 V in all modes.

- 2. For reset pads, same V<sub>ih</sub> levels are applicable

- 3. For reset pads, same V<sub>il</sub> levels are applicable

- 4. The value given is measured at high drive strength mode. For value at low drive strength mode see the loh\_Standard value given above.

- 5. For refernce only. Run simulations with the IBIS model and custom board for accurate results.

| Symbol             | Description                      | Min. | Max.            | Unit |

|--------------------|----------------------------------|------|-----------------|------|

| f <sub>FLASH</sub> | Flash clock                      |      | 24              | MHz  |

|                    | Normal run mode (S32K14x series) | 3    | 1               |      |

| f <sub>SYS</sub>   | System and core clock            | _    | 80              | MHz  |

| f <sub>BUS</sub>   | Bus clock                        | _    | 40 <sup>4</sup> | MHz  |

| f <sub>FLASH</sub> | Flash clock                      | _    | 26.67           | MHz  |

|                    | VLPR mode <sup>5</sup>           |      |                 |      |

| f <sub>SYS</sub>   | System and core clock            |      | 4               | MHz  |

| f <sub>BUS</sub>   | Bus clock                        |      | 4               | MHz  |

| f <sub>FLASH</sub> | Flash clock                      | _    | 1               | MHz  |

| f <sub>ERCLK</sub> | External reference clock         |      | 16              | MHz  |

1. Refer to the section Feature comparison for the availability of modes and other specifications.

- 2. Only available on some devices. See section Feature comparison.

- 3. With SPLL as system clock source.

- 4. 48 MHz when f<sub>SYS</sub> is 48 MHz

5. The frequency limitations in VLPR mode here override any frequency specification listed in the timing specification for any other module.

# 6 Peripheral operating requirements and behaviors

## 6.1 System modules

There are no electrical specifications necessary for the device's system modules.

## 6.2 Clock interface modules

## 6.2.1 External System Oscillator electrical specifications

# Table 17. External System Oscillator electrical specifications (continued)

| Symbol          | Description                                             | Min. | Тур. | Max. | Unit | Notes |

|-----------------|---------------------------------------------------------|------|------|------|------|-------|

|                 | High-gain mode (HGO=1)                                  | —    | 1    | _    | MΩ   |       |

| R <sub>S</sub>  | Series resistor                                         |      |      |      |      |       |

|                 | Low-gain mode (HGO=0)                                   | _    | 0    | _    | kΩ   |       |

|                 | High-gain mode (HGO=1)                                  | _    | 0    | _    | kΩ   |       |

| V <sub>pp</sub> | Peak-to-peak amplitude of oscillation (oscillator mode) |      |      |      | 3    |       |

|                 | Low-gain mode (HGO=0)                                   | _    | 1.0  | _    | V    |       |

|                 | High-gain mode (HGO=1)                                  |      | 3.3  | _    | V    |       |

1. Crystal oscillator circuit provides stable oscillations when  $g_{mXOSC} > 5 * gm_{crit}$ . The gm\_crit is defined as:

gm\_crit = 4 \* ESR \*  $(2\pi F)^2$  \*  $(C_0 + C_L)^2$

where:

2.

- $g_{mXOSC}$  is the transconductance of the internal oscillator circuit

- ESR is the equivalent series resistance of the external crystal

- F is the external crystal oscillation frequency

- C<sub>0</sub> is the shunt capacitance of the external crystal

- $C_L$  is the external crystal total load capacitance.  $C_L = C_s + [C_1 * C_2 / (C_1 + C_2)]$

- $C_s$  is stray or parasitic capacitance on the pin due to any PCB traces

- $C_1$ ,  $C_2$  external load capacitances on EXTAL and XTAL pins

See manufacture datasheet for external crystal component values

- When low-gain is selected, internal R<sub>F</sub> will be selected and external R<sub>F</sub> should not be attached.

- When high-gain is selected, external R<sub>F</sub> (1 M Ohm) needs to be connected for proper operation of the crystal. For external resistor, up to 5% tolerance is allowed.

- 3. The EXTAL and XTAL pins should only be connected to required oscillator components and must not be connected to any other devices.

# 6.2.2 External System Oscillator frequency specifications

| NXP            |

|----------------|

| Semiconductors |

S32K1xx Data Sheet, Rev. 8, 06/2018

| FLASH PORT          | Sym              | Unit |        |               |        |                 |        | FLA            | SH A   |               |            |                 |        |              |                        | FLA           | SH B              |                 |

|---------------------|------------------|------|--------|---------------|--------|-----------------|--------|----------------|--------|---------------|------------|-----------------|--------|--------------|------------------------|---------------|-------------------|-----------------|

|                     |                  |      |        |               | RL     | JN <sup>1</sup> |        |                |        |               | HSR        | UN <sup>1</sup> |        |              | RUN/HSRUN <sup>2</sup> |               |                   |                 |

| QuadSPI Mode        |                  |      |        |               | SI     | DR              |        |                |        |               | SE         | R               |        |              | SDR D                  |               | DE                | )R <sup>3</sup> |

|                     |                  |      |        | rnal<br>pling |        | Interna         | al DQS |                |        | rnal<br>pling |            | Interna         | al DQS |              |                        | rnal<br>pling | Extern            | al DQS          |

|                     |                  |      | N      | 11            |        | AD<br>oback     |        | ernal<br>oback | N      | 11            | PA<br>Loop |                 |        | rnal<br>back | N                      | 11            | Extern            | al DQS          |

|                     |                  |      | Min    | Мах           | Min    | Мах             | Min    | Max            | Min    | Мах           | Min        | Max             | Min    | Мах          | Min                    | Мах           | Min               | Max             |

|                     |                  |      |        |               |        |                 | Regis  | ster Sett      | ings   |               | •          |                 |        |              |                        |               |                   | •               |

| MCR[DDR_EN]         |                  | -    | (      | )             | (      | )               | (      | )              | (      | )             | 0          |                 | (      | )            | (                      | )             | -                 | 1               |

| MCR[DQS_EN]         |                  | -    | (      | 0 1           |        | 1               | 1      |                | (      | )             | 1          |                 | 1      |              | 0                      |               | 1                 |                 |

| MCR[SCLKCFG[0]]     |                  | -    | -      | - 1           |        | 1               | 0 -    |                | 1      | 1 0           |            | -               |        | -            |                        |               |                   |                 |

| MCR[SCLKCFG[1]]     |                  | -    | -      | - 1           |        | 1               | 0 -    |                | 1 0    |               | -          |                 | -      |              |                        |               |                   |                 |

| MCR[SCLKCFG[2]]     |                  | -    | -      |               |        |                 |        |                |        |               | -          |                 | -      |              | 0                      |               |                   |                 |

| MCR[SCLKCFG[3]]     |                  | -    | -      | -             |        |                 |        | -              |        |               |            | -               |        | -            |                        | 0             |                   |                 |

| MCR[SCLKCFG[5]]     |                  | -    | (      | )             | 0      |                 | 0 0    |                | 0      |               | 0          |                 | 0      |              | 0                      |               | 1                 |                 |

| SMPR[FSPHS]         |                  | -    | (      | )             | 1      |                 | 1 0    |                | (      | )             | 1          |                 | 0      |              | 0                      |               | 0                 |                 |

| SMPR[FSDLY]         |                  | -    | (      | )             | (      | 0 0             |        | (              | )      | 0             |            | 0               |        | 0            |                        | 0             |                   |                 |

| SOCCR               |                  |      | -      | -             | 0      |                 | 0 23   |                | -      |               | 0          |                 | 30     |              | -                      |               | -                 |                 |

| [SOCCFG[7:0]]       |                  |      |        |               |        |                 |        |                |        |               |            |                 |        |              |                        |               |                   |                 |

| SOCCR[SOCCFG[15:8]] |                  | -    | -      |               | -      |                 |        | -              | -      |               | -          |                 | -      |              | -                      |               | 3                 | 0               |

| FLSHCR[TDH]         |                  | -    | 0x     | 00            | 0x     | 00              | 0x     | 00             | 0x     | 00            | 0x(        | 00              | 0x     | 00           | 0x                     | 00            | 0x                | 01              |

|                     |                  |      |        |               |        |                 | Timing | g Param        | eters  |               |            |                 |        |              |                        |               |                   |                 |

| SCK Clock Frequency | f <sub>SCK</sub> | MHz  | -      | 38            | -      | 64              | -      | 48             | -      | 40            | -          | 80              | -      | 50           | -                      | 20            | -                 | 20 <sup>4</sup> |

| SCK Clock Period    | t <sub>SCK</sub> | ns   | 1/fSCK | -             | 1/fSCK | -               | 1/fSCK | -              | 1/fSCK | -             | 1/fSCK     | -               | 1/fSCK | -            | 50.0                   | -             | 50.0 <sup>4</sup> | -               |

Table continues on the next page...

Memory and memory interfaces

39

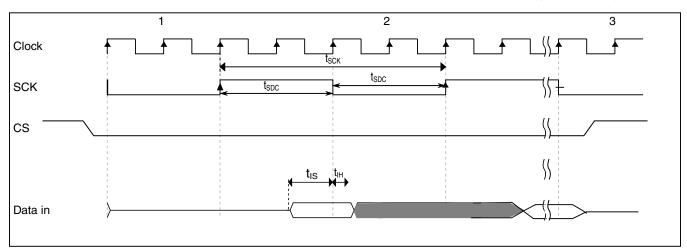

Figure 9. QuadSPI input timing (SDR mode) diagram

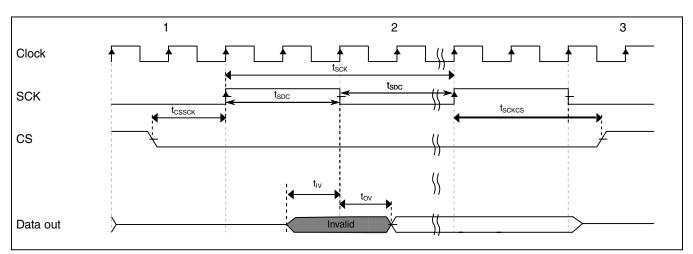

Figure 10. QuadSPI output timing (SDR mode) diagram

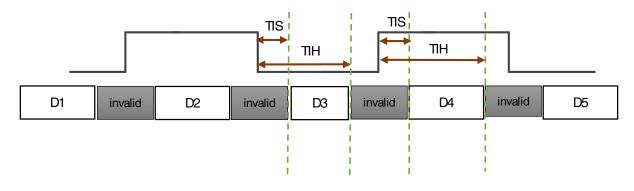

TIS-Setup Time TIH-Hold Time

Figure 11. QuadSPI input timing (HyperRAM mode) diagram

**ADC electrical specifications**

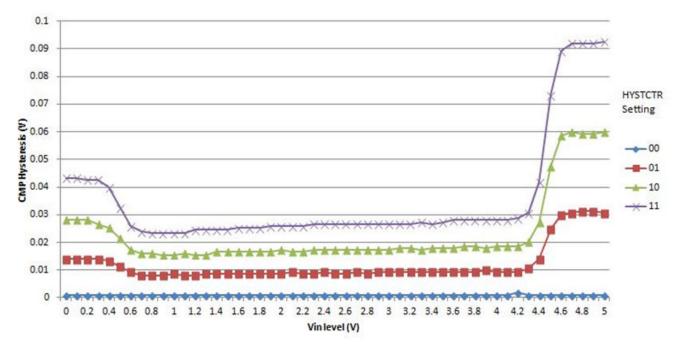

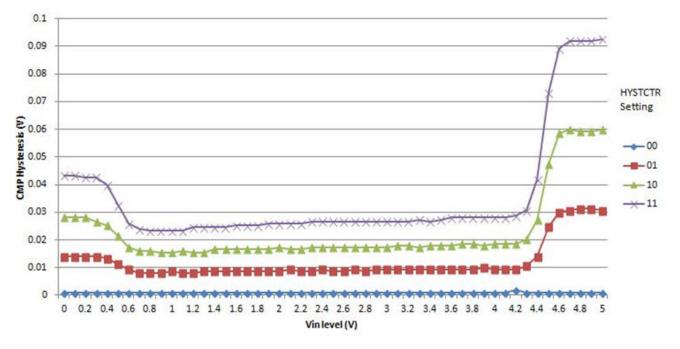

Figure 16. Typical hysteresis vs. Vin level (VDDA = 5 V, PMODE = 0)

Figure 17. Typical hysteresis vs. Vin level (VDDA = 5 V, PMODE = 1)

**Communication modules**

## Table 32. LPSPI electrical specifications1 (continued)

| Num | Num Symbol         | Description                  | Conditions                            |                                  | Run      | Mode <sup>2</sup>                |            |                                  | HSRU       | N Mode <sup>2</sup>                 |                                      |                                     | VLPR       | Mode                               |            | Un         |      |    |   |    |   |    |

|-----|--------------------|------------------------------|---------------------------------------|----------------------------------|----------|----------------------------------|------------|----------------------------------|------------|-------------------------------------|--------------------------------------|-------------------------------------|------------|------------------------------------|------------|------------|------|----|---|----|---|----|

|     |                    |                              |                                       |                                  |          | 5.0                              | V IO       | 3.3                              | V IO       | 5.0                                 | V IO                                 | 3.3                                 | V IO       | 5.0                                | V IO       | 3.3        | V IO |    |   |    |   |    |

|     |                    |                              |                                       | Min.                             | Max.     | Min.                             | Max.       | Min.                             | Max.       | Min.                                | Max.                                 | Min.                                | Max.       | Min.                               | Max.       | 1          |      |    |   |    |   |    |

| 4   | t <sub>Lag</sub> 9 | Enable lag                   | Slave                                 | -                                | -        | -                                | -          | -                                | -          | -                                   | -                                    | -                                   | -          | -                                  | -          | ns         |      |    |   |    |   |    |

|     |                    | time (After<br>SPSCK delay)  | Master                                |                                  | -        |                                  | -          |                                  | -          |                                     | -                                    |                                     | -          |                                    | -          |            |      |    |   |    |   |    |

|     |                    | of corracially)              | Master<br>Loopback <sup>5</sup>       | - 25                             |          | - 25                             |            | - 25                             |            | - 25                                |                                      | - 50                                |            | - 50                               |            |            |      |    |   |    |   |    |

|     |                    |                              | Master<br>Loopback(slow) <sup>6</sup> | (SCKPCS+1)*t <sub>periph</sub> - |          | (SCKPCS+1)*t <sub>periph</sub> - |            | (SCKPCS+1)*t <sub>periph</sub> - |            | (SCKPCS+1)*t <sub>periph</sub> - 25 |                                      | (SCKPCS+1)*t <sub>periph</sub> - 50 |            | (SCKPCS+1)*t <sub>periph</sub> -50 |            |            |      |    |   |    |   |    |

| 5   | )<br>              | Clock(SPSCK                  | Slave                                 |                                  |          |                                  |            |                                  |            |                                     |                                      |                                     |            |                                    |            | ns         |      |    |   |    |   |    |

|     |                    | ) high or low<br>time (SPSCK | Master                                | r<br>S                           | ε<br>+ 3 | ကို                              | ۴+<br>۲-   | ကို                              | £+3        | က်<br>ကို                           | £+3                                  | 2-2                                 | 5+5        | 2-2                                | 5+2        |            |      |    |   |    |   |    |

|     |                    | duty cycle)                  | Master<br>Loopback <sup>5</sup>       |                                  | spsck/   | tspsck/2+3                       | tspsck/2-3 | tspsck/2+3                       | tspsck/2-3 | tspsck/2+3                          | tspsck/2-3                           | tspsck/2+3                          | tspsck/2-5 | tspsck/2+5                         | tspsck/2-5 | tsPSCK/2+5 |      |    |   |    |   |    |

|     |                    |                              | Master<br>Loopback(slow) <sup>6</sup> | <b>H</b>                         | <u>ب</u> | +                                | μ,         | +                                | ÷.         | -                                   | ÷.                                   | +                                   | ů.         | -                                  | <u>ب</u>   |            |      |    |   |    |   |    |

| 6   | t <sub>SU</sub>    | Data setup<br>time(inputs)   | 1                                     |                                  |          |                                  |            |                                  | Slave      | 3                                   | -                                    | 5                                   | -          | 3                                  | -          | 5          | -    | 18 | - | 18 | - | ns |

|     |                    |                              |                                       | Master                           | 29       | -                                | 38         | -                                | 26         | -                                   | 37 <sup>11</sup><br>32 <sup>12</sup> | -                                   | 72         | -                                  | 78         | -          | _    |    |   |    |   |    |

|     |                    |                              | Master<br>Loopback <sup>5</sup>       | 7                                | -        | 8                                | -          | 5                                | -          | 7                                   | -                                    | 20                                  | -          | 20                                 | -          | -          |      |    |   |    |   |    |

|     |                    |                              | Master<br>Loopback(slow) <sup>6</sup> | 8                                | -        | 10                               | -          | 7                                | -          | 9                                   | -                                    | 20                                  | -          | 20                                 | -          |            |      |    |   |    |   |    |

| 7   | 1 10 1             | t <sub>HI</sub>              | Data hold<br>time(inputs)             | Slave                            | 3        | -                                | 3          | -                                | 3          | -                                   | 3                                    | -                                   | 14         | -                                  | 14         | -          | ns   |    |   |    |   |    |

|     |                    | time(inputs)                 |                                       | Master                           | 0        | -                                | 0          | -                                | 0          | -                                   | 0                                    | -                                   | 0          | -                                  | 0          | -          |      |    |   |    |   |    |

|     |                    |                              | Master<br>Loopback <sup>5</sup>       | 3                                | -        | 3                                | -          | 2                                | -          | 3                                   | -                                    | 11                                  | -          | 11                                 | -          |            |      |    |   |    |   |    |

|     |                    |                              | Master<br>Loopback(slow) <sup>6</sup> | 3                                | -        | 3                                | -          | 3                                | -          | 3                                   | -                                    | 12                                  | -          | 12                                 | -          |            |      |    |   |    |   |    |

Table continues on the next page...

52

**Communication modules**

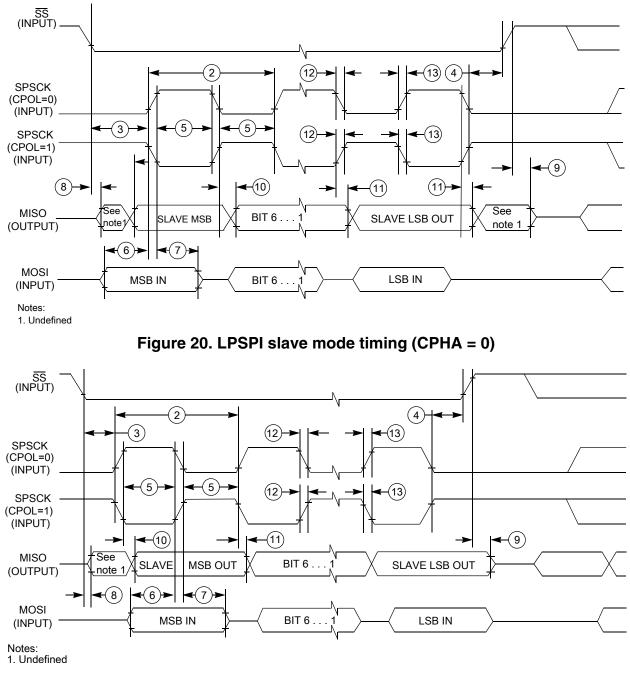

Figure 21. LPSPI slave mode timing (CPHA = 1)

# 6.5.3 LPI2C electrical specifications

See General AC specifications for LPI2C specifications.

For supported baud rate see section 'Chip-specific LPI2C information' of the *Reference Manual*.

## **Communication modules**

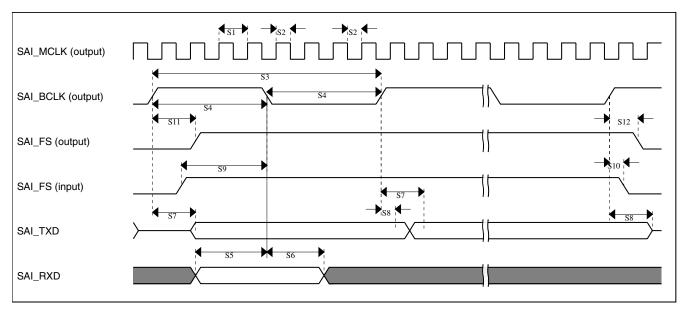

Figure 22. SAI Timing — Master modes

| Symbol           | Description                            | Min. | Max. | Unit        |

|------------------|----------------------------------------|------|------|-------------|

| _                | Operating voltage                      | 2.97 | 3.6  | V           |

| S13              | SAI_BCLK cycle time (input)            | 80   | _    | ns          |

| S14 <sup>1</sup> | SAI_BCLK pulse width high/low (input)  | 45%  | 55%  | BCLK period |

| S15              | SAI_RXD input setup before<br>SAI_BCLK | 8    | —    | ns          |

| S16              | SAI_RXD input hold after<br>SAI_BCLK   | 2    | —    | ns          |

| S17              | SAI_BCLK to SAI_TXD output valid       |      | 28   | ns          |

| S18              | SAI_BCLK to SAI_TXD output invalid     | 0    | _    | ns          |

| S19              | SAI_FS input setup before<br>SAI_BCLK  | 8    | —    | ns          |

| S20              | SAI_FS input hold after SAI_BCLK       | 2    | —    | ns          |

| S21              | SAI_BCLK to SAI_FS output valid        | _    | 28   | ns          |

| S22              | SAI_BCLK to SAI_FS output invalid      | 0    | _    | ns          |

## Table 34. Slave mode timing specifications

1. The slave mode parameters (S15 - S22) assume 50% duty cycle on SAI\_BCLK input. Any change in SAI\_BCLK duty cycle input must be taken care during the board design or by the master timing.

**Debug modules**

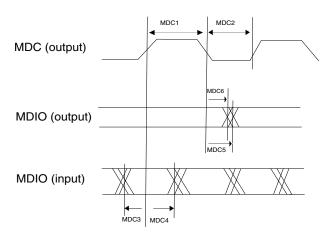

| Symbol | Description                                                                 | Min. | Max. | Unit       |

|--------|-----------------------------------------------------------------------------|------|------|------------|

| MDC1   | MDC pulse width high                                                        | 40%  | 60%  | MDC period |

| MDC2   | MDC pulse width low                                                         | 40%  | 60%  | MDC period |

| MDC3   | MDIO (input) to MDC rising edge setup                                       | 25   |      | ns         |

| MDC4   | MDIO (input) to MDC rising edge hold                                        | 0    |      | ns         |

| MDC5   | MDC falling edge to MDIO output valid (maximum propagation delay)           | —    | 25   | ns         |

| MDC6   | MDC6 MDC falling edge to MDIO output invalid<br>(minimum propagation delay) |      |      | ns         |

## 6.5.7 Clockout frequency

Maximum supported clock out frequency for this device is 20 MHz

# 6.6 Debug modules

## 6.6.1 SWD electrical specofications

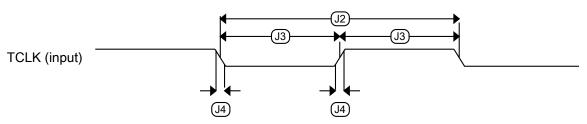

Figure 32. Test clock input timing

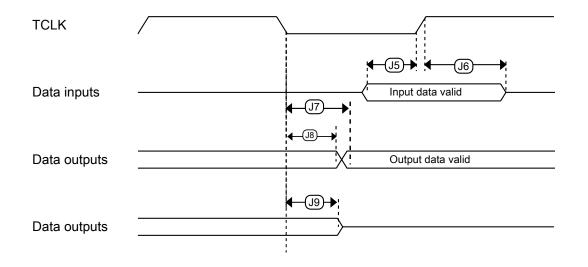

Figure 33. Boundary scan (JTAG) timing

## Table 41. Thermal characteristics for 32-pin QFN and 48/64/100/144/176-pin LQFP package

| Rating                                  | Conditions   | Symbol            | Package  | Values  |             |         |         |          |    | Un  |

|-----------------------------------------|--------------|-------------------|----------|---------|-------------|---------|---------|----------|----|-----|

|                                         |              |                   | S32K116  | S32K118 | S32K142     | S32K144 | S32K146 | S32K148  | 1  |     |

| Thermal resistance, Junction to Ambient | Single layer | R <sub>θJA</sub>  | 32       | 93      | NA          | NA      | NA      | NA       | NA | °C/ |

| (Natural Convection) <sup>1, 2</sup>    | board (1s)   |                   | 48       | 79      | 71          | NA      | NA      | NA       | NA |     |

|                                         |              |                   | 64       | NA      | 62          | 61      | 61      | 59       | NA | İ   |

|                                         |              |                   | 100      | NA      | NA          | 53      | 52      | 51       | NA | ĺ   |

|                                         |              |                   | 144      | NA      | NA          | NA      | NA      | 51       | 44 | 1   |

|                                         |              |                   | 176      | NA      | NA          | NA      | NA      | NA       | 42 |     |

| Thermal resistance, Junction to Ambient | Two layer    | R <sub>θJA</sub>  | 32       | 50      | NA          | NA      | NA      | NA       | NA | 1   |

| (Natural Convection) <sup>1</sup>       | board (1s1p) |                   | 48       | 58      | 50          | NA      | NA      | NA       | NA | _   |

|                                         |              |                   | 64       | NA      | 46          | 45      | 45      | 45 44 NA | NA |     |

|                                         |              |                   | 100      | NA      | NA          | 42      | 42      | 40       | NA | 1   |

|                                         |              |                   | 144      | NA      | NA          | NA      | NA      | 44       | 37 | 1   |

|                                         |              |                   | 176      | NA      | NA          | NA      | NA      | NA       | 36 | 1   |

| Thermal resistance, Junction to Ambient | Four layer   | R <sub>θJA</sub>  | 32       | 32      | NA          | NA      | NA      | NA       | NA |     |

| (Natural Convection) <sup>1, 2</sup>    | board (2s2p) |                   | 48       | 55      | 47          | NA      | NA      | NA       | NA | 1   |

|                                         |              |                   | 64 NA 44 | 44      | 43          | 43      | 41      | NA       |    |     |

|                                         |              |                   | 100      | NA      | NA NA 40 40 | 39      | NA      |          |    |     |

|                                         |              |                   | 144      | NA      | NA          | NA      | NA      | 42       | 36 |     |

|                                         |              |                   | 176      | NA      | NA          | NA      | NA      | NA       | 35 |     |

| Thermal resistance, Junction to Ambient | Single layer | R <sub>0JMA</sub> | 32       | 77      | NA          | NA      | NA      | NA       | NA |     |

| (@200 ft/min) <sup>1, 3</sup>           | board (1s)   |                   | 48       | 66      | 58          | NA      | NA      | NA       | NA |     |

|                                         |              |                   | 64       | NA      | 50          | 49      | 49      | 48       | NA |     |

|                                         |              |                   | 100      | NA      | NA          | 43      | 42      | 41       | NA | 1   |

|                                         |              |                   | 144      | NA      | NA          | NA      | NA      | 42       | 36 | ]   |

|                                         |              |                   | 176      | NA      | NA          | NA      | NA      | NA       | 34 | ]   |

| Thermal resistance, Junction to Ambient | Two layer    | R <sub>0JMA</sub> | 32       | 43      | NA          | NA      | NA      | NA       | NA | 1   |

| (@200 ft/min) <sup>1</sup>              | board (1s1p) |                   | 48       | 51      | 43          | NA      | NA      | NA       | NA | 1   |

|                                         |              |                   | 64       | NA      | 39          | 38      | 38      | 37       | NA | ]   |

|                                         |              |                   | 100      | NA      | NA          | 35      | 35      | 34       | NA | 1   |

Table continues on the next page...

69

| Table 43. Revision Histor | y (continued) |

|---------------------------|---------------|

|---------------------------|---------------|

| Rev. No. | Date         | Substantial Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |              | <ul> <li>Fixed the typo in R<sub>SW1</sub></li> <li>In LPSPI electrical specifications : <ul> <li>Updated t<sub>Lead</sub> and t<sub>Lag</sub></li> <li>Added footnote in Figure: LPSPI slave mode timing (CPHA = 0) and Figure: LPSPI slave mode timing (CPHA = 1)</li> </ul> </li> <li>In Thermal characteristics : <ul> <li>Updated the name of table: Thermal characteristics for 32-pin QFN and 48/64/100/144/176-pin LQFP package</li> <li>Deleted specs for R<sub>BJC</sub> for 32 QFN package</li> <li>Added 'R<sub>BJCBottom</sub>'</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 8        | 18 June 2018 | <ul> <li>In attachement 'S32K1xx Power_Modes _Configuration':</li> <li>Updated VLPR peripherals disabled and Peripherals Enabled use case #1, using 4 Mhz for System clock, 2 Mhz for bus clock, and 1Mhz for flash.</li> <li>Removed S32K116 from Notes</li> <li>In figure: S32K1xx product series comparison : <ul> <li>Added note 'Availability of peripherals depends on the pin availability'</li> <li>Updated 'Ambient Operation Temperature' row</li> <li>Updated 'System RAM (including FlexRAM and MTB)' row for S32K144, S32K146, and S32K148</li> </ul> </li> <li>In Ordering information : <ul> <li>Updated figure for 'Y: Optional feature'</li> <li>Updated footnote 3</li> </ul> </li> <li>In Power and ground pins : <ul> <li>In figure 'Power diagram', updtaed V<sub>Flash</sub> frequency to 3.3 V</li> </ul> </li> <li>In Power mode transition operating behaviors : <ul> <li>Updated IDDs for S32K116</li> <li>Added IDDs for S32K116</li> <li>Added footnote for 'VLPS Mode: All clock sources disabled'</li> </ul> </li> <li>In Power consumption : <ul> <li>Added footnote 'Data collected using RAM' to VLPR 'Peripherals enabled use case 1'</li> <li>Updated VLPR 'Peripherals enabled use case 1'</li> <li>Updated VLPS Peripherals enabled at 25 °C/Typicals for S32K142 and S32K144 to 40 µA and 42 µA respectively</li> <li>Added table 'VLPS additional use-case power consumption at typical conditions'</li> <li>In DC electrical specifications at 3.3 V Range : <ul> <li>Updated naming conventions</li> <li>Added specs for GPIO-FAST pad</li> </ul> </li> <li>In AC electrical specifications at 5.0 V Range : <ul> <li>Updated naming conventions</li> <li>Added specs for GPIO-FAST pad</li> </ul> </li> <li>In AC electrical specifications at 5.V range : <ul> <li>Updated naming conventions</li> <li>Added specs for GPIO-FAST pad</li> </ul> </li> <li>In AC electrical specifications at 5.V range : <ul> <li>Updated naming conventions</li> <li>Added specs for GPIO-FAST pad</li> </ul> </li> <li>In AC electrical specifications at 5.V range : <ul> <li>Updated naming convent</li></ul></li></ul></li></ul> |

| Rev. No. | Date | Substantial Changes                                                                                                                 |

|----------|------|-------------------------------------------------------------------------------------------------------------------------------------|

|          |      | <ul> <li>Updated specs for T<sub>JIT</sub> Cycle-to-Cycle jitter to 300 ps</li> </ul>                                               |

|          |      | <ul> <li>In QuadSPI AC specifications :</li> </ul>                                                                                  |

|          |      | <ul> <li>Updated specs for T<sub>iv</sub> Data Output In-Valid Time</li> </ul>                                                      |

|          |      | In figure 'QuadSPI output timing (SDR mode) diagram', marked Invalid                                                                |

|          |      | area                                                                                                                                |

|          |      | <ul> <li>In CMP with 8-bit DAC electrical specifications :</li> </ul>                                                               |

|          |      | <ul> <li>Removed '(VAIO)' from decription of V<sub>HYST0</sub></li> </ul>                                                           |

|          |      | In LPSPI electrical specifications :                                                                                                |

|          |      | <ul> <li>Added note 'Undefined' in figures 'LPSPI slave mode timing (CPHA = 0)' and 'LPSPI slave mode timing (CPHA = 1)'</li> </ul> |

## Table 43. Revision History