# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4F                                                         |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 64MHz                                                                    |

| Connectivity               | CANbus, FlexIO, I <sup>2</sup> C, LINbus, SPI, UART/USART                |

| Peripherals                | POR, PWM, WDT                                                            |

| Number of I/O              | 89                                                                       |

| Program Memory Size        | 512KB (512K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 4K x 8                                                                   |

| RAM Size                   | 64K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| Data Converters            | A/D 16x12b SAR; D/A1x8b                                                  |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 100-LQFP                                                                 |

| Supplier Device Package    | 100-LQFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/fs32k144mrt0cllt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- 5.  $V_{REFH}$  should always be equal to or less than  $V_{DDA}$  + 0.1 V and  $V_{DD}$  + 0.1 V

- 6. Open drain outputs must be pulled to  $V_{DD}$ .

- 7. When input pad voltage levels are close to  $V_{DD}$  or  $V_{SS}$ , practically no current injection is possible.

# 4.3 Thermal operating characteristics

# Table 3. Thermal operating characteristics for 64 LQFP, 100 LQFP, and 100 MAP-BGApackages.

| Symbol                      | Parameter                       |      | Value |                  | Unit |

|-----------------------------|---------------------------------|------|-------|------------------|------|

|                             |                                 | Min. | Тур.  | Max.             |      |

| T <sub>A C-Grade Part</sub> | Ambient temperature under bias  | -40  | —     | 85 <sup>1</sup>  | °C   |

| T <sub>J C-Grade Part</sub> | Junction temperature under bias | -40  | —     | 105 <sup>1</sup> | °C   |

| T <sub>A V-Grade Part</sub> | Ambient temperature under bias  | -40  | _     | 105 <sup>1</sup> | °C   |

| T <sub>J V-Grade Part</sub> | Junction temperature under bias | -40  | —     | 125 <sup>1</sup> | °C   |

| T <sub>A M-Grade Part</sub> | Ambient temperature under bias  | -40  | —     | 125 <sup>2</sup> | °C   |

| T <sub>J M-Grade Part</sub> | Junction temperature under bias | -40  | —     | 135 <sup>2</sup> | °C   |

1. Values mentioned are measured at  $\leq$  112 MHz in HSRUN mode.

2. Values mentioned are measured at  $\leq$  80 MHz in RUN mode.

## Table 4. Supplies decoupling capacitors 1, 2

| Symbol                                                      | Description                               | Min. <sup>3</sup> | Тур. | Max. | Unit |

|-------------------------------------------------------------|-------------------------------------------|-------------------|------|------|------|

| C <sub>REF</sub> <sup>, 4</sup> , <sup>5</sup>              | ADC reference high decoupling capacitance | 70                | 100  |      | nF   |

| C <sub>DEC</sub> <sup>5</sup> , <sup>6</sup> , <sup>7</sup> | Recommended decoupling capacitance        | 70                | 100  |      | nF   |

V<sub>DD</sub> and V<sub>DDA</sub> must be shorted to a common source on PCB. The differential voltage between V<sub>DD</sub> and V<sub>DDA</sub> is for RF-AC only. Appropriate decoupling capacitors to be used to filter noise on the supplies. See application note AN5032 for reference supply design for SAR ADC. All V<sub>SS</sub> pins should be connected to common ground at the PCB level.

2. All decoupling capacitors must be low ESR ceramic capacitors (for example X7R type).

3. Minimum recommendation is after considering component aging and tolerance.

4. For improved performance, it is recommended to use 10 µF, 0.1 µF and 1 nF capacitors in parallel.

5. All decoupling capacitors should be placed as close as possible to the corresponding supply and ground pins.

6. Contact your local Field Applications Engineer for details on best analog routing practices.

7. The filtering used for decoupling the device supplies must comply with the following best practices rules:

• The protection/decoupling capacitors must be on the path of the trace connected to that component.

• No trace exceeding 1 mm from the protection to the trace or to the ground.

• The protection/decoupling capacitors must be as close as possible to the input pin of the device (maximum 2 mm).

• The ground of the protection is connected as short as possible to the ground plane under the integrated circuit.

## Table 7. Power consumption (Typicals unless stated otherwise) 1 (continued)

General

|                      |                          |     | VLPS (                            | μΑ) <sup>2</sup>    | V                                 | LPR (m                                      | A)                                          | STOP1<br>(mA) | STOP2<br>(mA) |                      | l@48<br>(mA)        |                      | 64 MHz<br>nA)       |                      | 80 MHz<br>nA)       |                      | N@112<br>(mA) <sup>3</sup> |                               |

|----------------------|--------------------------|-----|-----------------------------------|---------------------|-----------------------------------|---------------------------------------------|---------------------------------------------|---------------|---------------|----------------------|---------------------|----------------------|---------------------|----------------------|---------------------|----------------------|----------------------------|-------------------------------|

| Chip/Device          | Ambient Temperature (°C) |     | Peripherals disabled <sup>5</sup> | Peripherals enabled | Peripherals disabled <sup>6</sup> | Peripherals enabled use case 1 <sup>6</sup> | Peripherals enabled use case 2 <sup>7</sup> |               |               | Peripherals disabled | Peripherals enabled        | IDD/MHz (µA/MHz) <sup>4</sup> |

|                      |                          | Max | 1637                              | 1694                | 3.1                               | 3.21                                        | NA                                          | 12.7          | 13.7          | 25                   | 32.9                | 30.7                 | 38.8                | 36                   | 43.8                | N                    | A                          | 450                           |

| S32K144              | 25                       | Тур | 29.8                              | 42                  | 1.48                              | 1.50                                        | 2.91                                        | 7             | 7.7           | 19.7                 | 26.9                | 25.1                 | 33.3                | 30.2                 | 39.6                | 43.3                 | 55.6                       | 378                           |

|                      | 85                       | Тур | 150                               | 159                 | 1.72                              | 1.85                                        | 3.08                                        | 7.2           | 8.1           | 20.4                 | 27.1                | 26.1                 | 33.5                | 30.5                 | 40                  | 43.9                 | 56.1                       | 381                           |

|                      |                          | Max | 359                               | 384                 | 2.60                              | 2.65                                        | NA                                          | 9.2           | 9.9           | 23.2                 | 29.6                | 29.3                 | 36.2                | 34.8                 | 42.1                | 46.3                 | 59.7                       | 435                           |

|                      | 105                      | Тур | 256                               | 273                 | 1.80                              | 2.10                                        | 3.23                                        | 7.8           | 8.5           | 20.6                 | 27.4                | 26.6                 | 33.8                | 31.2                 | 40.5                | 44.8                 | 57.1                       | 390                           |

|                      |                          | Max | 850                               | 900                 | 2.65                              | 2.70                                        | NA                                          | 10.3          | 11.1          | 23.9                 | 30.6                | 30.3                 | 37.3                | 35.6                 | 43.5                | 47.9                 | 61.3                       | 445                           |

|                      | 125                      | Тур | NA                                | NA                  | NA                                | NA                                          | 3.65                                        | NA            | NA            | NA                   | NA                  | NA                   | NA                  | NA                   | NA                  | N                    | A                          | NA                            |

|                      |                          | Max | 1960                              | 1998                | 3.18                              | 3.25                                        | NA                                          | 12.9          | 13.8          | 26.9                 | 33.6                | 35                   | 40.3                | 38.7                 | 46.8                | N                    | A                          | 484                           |

| S32K146              | 25                       | Тур | 37                                | 47                  | 1.57                              | 1.61                                        | 3.3                                         | 8             | 9.2           | 23.4                 | 31.4                | 30.5                 | 40.2                | 36.2                 | 47.6                | 52                   | 68.3                       | 452                           |

|                      | 85                       | Тур | 207                               | 209                 | 1.79                              | 1.83                                        | 3.54                                        | 8.9           | 10.1          | 24.4                 | 32.4                | 31.5                 | 41.3                | 37.2                 | 48.7                | 53.3                 | 69.8                       | 465                           |

|                      |                          | Max | 974                               | 981                 | 3.32                              | 3.38                                        | NA                                          | 12.7          | 13.9          | 29.3                 | 37.9                | 36.7                 | 47                  | 42.4                 | 54.4                | 60.3                 | 78                         | 530                           |

|                      | 105                      | Тур | 419                               | 422                 | 1.99                              | 2.04                                        | 3.78                                        | 9.8           | 11            | 25.3                 | 33.4                | 32.5                 | 42.2                | 38.1                 | 49.6                | 54.4                 | 70.8                       | 477                           |

|                      |                          | Max | 2004                              | 2017                | 4.06                              | 4.13                                        | NA                                          | 17.1          | 18.3          | 34.1                 | 42.6                | 41.3                 | 51.4                | 46.9                 | 58.8                | 65.7                 | 82.8                       | 587                           |

|                      | 125                      | Тур | NA                                | NA                  | NA                                | NA                                          | 4.44                                        | NA            | NA            | NA                   | NA                  | NA                   | NA                  | NA                   | NA                  | N                    | A                          | NA                            |

|                      |                          | Max | 3358                              | 3380                | 5.28                              | 5.38                                        | NA                                          | 22.6          | 23.7          | 40.2                 | 48.8                | 47.3                 | 57.4                | 52.8                 | 64.8                | N                    | A                          | 660                           |

| S32K148 <sup>8</sup> | 25                       | Тур | 38                                | 54                  | 2.17                              | 2.20                                        | 3.45                                        | 8.5           | 9.6           | 27.6                 | 34.9                | 35.5                 | 45.3                | 42.1                 | 57.7                | 60.3                 | 83.3                       | 526                           |

|                      | 85                       | Тур | 336                               | 357                 | 2.30                              | 2.35                                        | 3.74                                        | 10.1          | 11.1          | 29.1                 | 37.0                | 36.8                 | 46.6                | 43.4                 | 59.9                | 62.9                 | 88.7                       | 543                           |

Table continues on the next page...

18

# 5.3 DC electrical specifications at 3.3 V Range

NOTE

For details on the pad types defined in Table 11 and Table 12, see Reference Manual section *IO Signal Table* and IO Signal Description Input Multiplexing sheet(s) attached with Reference Manual.

| Symbol                                              | Parameter                                                                           |                       | Value |                       | Unit | Notes |  |

|-----------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------|-------|-----------------------|------|-------|--|

|                                                     |                                                                                     | Min.                  | Тур.  | Max.                  |      |       |  |

| V <sub>DD</sub>                                     | I/O Supply Voltage                                                                  | 2.7                   | 3.3   | 4                     | V    | 1     |  |

| V <sub>ih</sub>                                     | Input Buffer High Voltage                                                           | $0.7 \times V_{DD}$   | _     | V <sub>DD</sub> + 0.3 | V    | 2     |  |

| V <sub>il</sub>                                     | Input Buffer Low Voltage                                                            | V <sub>SS</sub> – 0.3 |       | $0.3 \times V_{DD}$   | V    | 3     |  |

| V <sub>hys</sub>                                    | Input Buffer Hysteresis                                                             | $0.06 \times V_{DD}$  | _     | —                     | V    |       |  |

| loh <sub>GPIO</sub><br>loh <sub>GPIO-HD_DSE_0</sub> | I/O current source capability measured when pad $V_{oh} = (V_{DD} - 0.8 \text{ V})$ | 3.5                   | —     | _                     | mA   |       |  |

| Iol <sub>GPIO</sub> -HD_DSE_0                       | I/O current sink capability measured when pad $V_{ol} = 0.8 \text{ V}$              | 3                     | _     |                       | mA   |       |  |

| Ioh <sub>GPIO-HD_DSE_1</sub>                        | I/O current source capability measured when pad $V_{oh} = (V_{DD} - 0.8 \text{ V})$ | 14                    | —     | _                     | mA   | 4     |  |

| Iol <sub>GPIO-HD_DSE_1</sub>                        | I/O current sink capability measured when pad $V_{\text{ol}}$ = 0.8 V               | 12                    | _     | _                     | mA   | 4     |  |

| loh <sub>GPIO-FAST_DSE_0</sub>                      | I/O current sink capability measured when pad $V_{oh}{=}V_{DD}{-}0.8~V$             | 9.5                   | _     | _                     | mA   | 5     |  |

| IOI <sub>GPIO-FAST_DSE_0</sub>                      | I/O current sink capability measured when pad $V_{\text{ol}}$ = 0.8 V               | 10                    | _     | —                     | mA   | 5     |  |

| Ioh <sub>GPIO-FAST_DSE_1</sub>                      | I/O current sink capability measured when pad $V_{oh}{=}V_{DD}{-}0.8~V$             | 16                    | _     | —                     | mA   | 5     |  |

| IOI <sub>GPIO-FAST_DSE_1</sub>                      | I/O current sink capability measured when pad $V_{\text{ol}}$ = 0.8 V               | 15.5                  | _     | _                     | mA   | 5     |  |

| IOHT                                                | Output high current total for all ports                                             | _                     | _     | 100                   | mA   |       |  |

| IIN                                                 |                                                                                     |                       | ł     | 6                     |      |       |  |

|                                                     | All pins other than high drive port pins                                            |                       | 0.005 | 0.5                   | μA   |       |  |

|                                                     | High drive port pins <sup>7</sup>                                                   |                       | 0.010 | 0.5                   | μA   | ]     |  |

| R <sub>PU</sub>                                     | Internal pullup resistors                                                           | 20                    |       | 60                    | kΩ   | 8     |  |

| R <sub>PD</sub>                                     | Internal pulldown resistors                                                         | 20                    |       | 60                    | kΩ   | 9     |  |

1. S32K148 will operate from 2.7 V when executing from internal FIRC. When the PLL is engaged S32K148 is guaranteed to operate from 2.97 V. All other S32K family devices operate from 2.7 V in all modes.

- 2. For reset pads, same V<sub>ih</sub> levels are applicable

- 3. For reset pads, same V<sub>il</sub> levels are applicable

- 4. The value given is measured at high drive strength mode. For value at low drive strength mode see the loh\_Standard value given above.

- 5. For refernce only. Run simulations with the IBIS model and custom board for accurate results.

#### I/O parameters

- 6. Several I/O have both high drive and normal drive capability selected by the associated Portx\_PCRn[DSE] control bit. All other GPIOs are normal drive only. For details see IO Signal Description Input Multiplexing sheet(s) attached with the *Reference Manual*.

- 7. When using ENET and SAI on S32K148, the overall device limits associated with high drive pin configurations must be respected i.e. On 144-pin LQFP the general purpose pins: PTA10, PTD0, and PTE4 must be set to low drive.

- 8. Measured at input  $V = V_{SS}$

- 9. Measured at input  $V = V_{DD}$

# 5.4 DC electrical specifications at 5.0 V Range

| Symbol                                              | Parameter                                                                      |                           | Value                   |                        | Unit                                                         | Notes |

|-----------------------------------------------------|--------------------------------------------------------------------------------|---------------------------|-------------------------|------------------------|--------------------------------------------------------------|-------|

|                                                     |                                                                                | Min.                      | Тур.                    | Max.                   |                                                              |       |

| V <sub>DD</sub>                                     | I/O Supply Voltage                                                             | 4                         | _                       | 5.5                    | V                                                            |       |

| V <sub>ih</sub>                                     | Input Buffer High Voltage                                                      | 0.65 x<br>V <sub>DD</sub> | _                       | V <sub>DD</sub> + 0.3  | V                                                            | 1     |

| V <sub>il</sub>                                     | Input Buffer Low Voltage                                                       | V <sub>SS</sub> – 0.3     | _                       | 0.35 x V <sub>DD</sub> | V                                                            | 2     |

| V <sub>hys</sub>                                    | Input Buffer Hysteresis                                                        | 0.06 x<br>V <sub>DD</sub> | _                       | —                      | V                                                            |       |

| loh <sub>GPIO</sub><br>loh <sub>GPIO-HD_DSE_0</sub> | I/O current source capability measured when pad $V_{oh}$ = ( $V_{DD}$ - 0.8 V) | 5                         | _                       | —                      | mA                                                           |       |

| Iol <sub>GPIO</sub><br>Iol <sub>GPIO-HD_DSE_0</sub> | I/O current sink capability measured when pad $V_{\rm ol}{=}$ 0.8 V            | 5                         | _                       | —                      | mA                                                           |       |

| Ioh <sub>GPIO-HD_DSE_1</sub>                        | I/O current source capability measured when pad $V_{oh} = V_{DD} - 0.8 V$      | 20                        | _                       | —                      | mA                                                           | 3     |

| IOI <sub>GPIO-HD_DSE_1</sub>                        | I/O current sink capability measured when pad $V_{ol} = 0.8 V$                 | 20                        | _                       | —                      | mA                                                           | 3     |

| Ioh <sub>GPIO-FAST_DSE_0</sub>                      | I/O current sink capability measured when pad $V_{oh} = V_{DD} - 0.8 V$        | 14.0                      | —                       | —                      | mA                                                           | 4     |

| IOI <sub>GPIO-FAST_DSE_0</sub>                      | I/O current sink capability measured when pad $V_{ol}$ = 0.8 V                 | 14.5                      | —                       | _                      | mA                                                           | 4     |

| loh <sub>GPIO-FAST_DSE_1</sub>                      | I/O current sink capability measured when pad $V_{oh} = V_{DD} - 0.8 V$        | 21                        | —                       | —                      | mA                                                           | 4     |

| IOI <sub>GPIO-FAST_DSE_1</sub>                      | I/O current sink capability measured when pad $V_{ol}$ = 0.8 V                 | 20.5                      | —                       | —                      | mA                                                           | 4     |

| IOHT                                                | Output high current total for all ports                                        | —                         |                         | 100                    | mA                                                           |       |

| IIN                                                 | Input leakage current (per pin) for full te                                    | mperature r               | ange at V <sub>DD</sub> | <sub>0</sub> = 5.5 V   | mA 2<br>mA 2<br>mA 2<br>mA 2<br>mA 2<br>mA 2<br>mA 2<br>mA 2 | 5     |

|                                                     | All pins other than high drive port pins                                       |                           | 0.005                   | 0.5                    | μA                                                           |       |

|                                                     | High drive port pins                                                           |                           | 0.010                   | 0.5                    | μA                                                           |       |

| R <sub>PU</sub>                                     | Internal pullup resistors                                                      | 20                        |                         | 50                     | kΩ                                                           | 6     |

| R <sub>PD</sub>                                     | Internal pulldown resistors                                                    | 20                        |                         | 50                     | kΩ                                                           | 7     |

Table 12. DC electrical specifications at 5.0 V Range

1. For reset pads, same V<sub>ih</sub> levels are applicable

2. For reset pads, same V<sub>il</sub> levels are applicable

- 3. The strong pad I/O pin is capable of switching a 50 pF load up to 40 MHz.

- 4. For refernce only. Run simulations with the IBIS model and custom board for accurate results.

- 5. Several I/O have both high drive and normal drive capability selected by the associated Portx\_PCRn[DSE] control bit. All other GPIOs are normal drive only. For details refer to *SK3K144\_IO\_Signal\_Description\_Input\_Multiplexing.xlsx* attached with the *Reference Manual*.

- 6. Measured at input  $V = V_{SS}$

- 7. Measured at input  $V = V_{DD}$

| Symbol                   | DSE | Rise tir | ne (nS) <sup>1</sup> | Fall tin | ne (nS) <sup>1</sup> | Capacitance (pF) <sup>2</sup> |

|--------------------------|-----|----------|----------------------|----------|----------------------|-------------------------------|

|                          |     | Min.     | Max.                 | Min.     | Max.                 |                               |

| tRF <sub>GPIO</sub>      | NA  | 3.2      | 14.5                 | 3.4      | 15.7                 | 25                            |

|                          |     | 5.7      | 23.7                 | 6.0      | 26.2                 | 50                            |

|                          |     | 20.0     | 80.0                 | 20.8     | 88.4                 | 200                           |

| tRF <sub>GPIO-HD</sub>   | 0   | 3.2      | 14.5                 | 3.4      | 15.7                 | 25                            |

|                          |     | 5.7      | 23.7                 | 6.0      | 26.2                 | 50                            |

| -                        |     | 20.0     | 80.0                 | 20.8     | 88.4                 | 200                           |

|                          | 1   | 1.5      | 5.8                  | 1.7      | 6.1                  | 25                            |

|                          |     | 2.4      | 8.0                  | 2.6      | 8.3                  | 50                            |

|                          |     | 6.3      | 22.0                 | 6.0      | 23.8                 | 200                           |

| tRF <sub>GPIO-FAST</sub> | 0   | 0.6      | 2.8                  | 0.5      | 2.8                  | 25                            |

|                          |     | 3.0      | 7.1                  | 2.6      | 7.5                  | 50                            |

|                          |     | 12.0     | 27.0                 | 10.3     | 26.8                 | 200                           |

|                          | 1   | 0.4      | 1.3                  | 0.38     | 1.3                  | 25                            |

|                          |     | 1.5      | 3.8                  | 1.4      | 3.9                  | 50                            |

|                          |     | 7.4      | 14.9                 | 7.0      | 15.3                 | 200                           |

# 5.5 AC electrical specifications at 3.3 V range

Table 13. AC electrical specifications at 3.3 V Range

1. For reference only. Run simulations with the IBIS model and your custom board for accurate results.

2. Maximum capacitances supported on Standard IOs. However interface or protocol specific specifications might be different, for example for ENET, QSPI etc. . For protocol specific AC specifications, see respective sections.

# 5.6 AC electrical specifications at 5 V range

| Symbol                 | DSE | Rise tir | me (nS) <sup>1</sup> | Fall tim | ie (nS) <sup>1</sup> | Capacitance (pF) <sup>2</sup> |

|------------------------|-----|----------|----------------------|----------|----------------------|-------------------------------|

|                        |     | Min.     | Max .                | Min.     | Max.                 |                               |

| tRF <sub>GPIO</sub>    | NA  | 2.8      | 9.4                  | 2.9      | 10.7                 | 25                            |

|                        |     | 5.0      | 15.7                 | 5.1      | 17.4                 | 50                            |

|                        |     | 17.3     | 54.8                 | 17.6     | 59.7                 | 200                           |

| tRF <sub>GPIO-HD</sub> | 0   | 2.8      | 9.4                  | 2.9      | 10.7                 | 25                            |

|                        |     | 5.0      | 15.7                 | 5.1      | 17.4                 | 50                            |

### Table 14. AC electrical specifications at 5 V Range

Table continues on the next page...

| Symbol                     | Description <sup>1</sup>                                              |                                                                        | Description <sup>1</sup> S32K142 |                                     | S3  | S32K144 S32                         |     | 632K146 S                           |     | S32K148                             |      |       |

|----------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------|-------------------------------------|-----|-------------------------------------|-----|-------------------------------------|-----|-------------------------------------|------|-------|

|                            |                                                                       |                                                                        | Тур                              | Max                                 | Тур | Max                                 | Тур | Max                                 | Тур | Max                                 | Unit | Notes |

|                            | setting (32-bit<br>write complete,<br>ready for next<br>32-bit write) | Last (Nth)<br>32-bit write<br>(time for<br>write only,<br>not cleanup) | 200                              | 550                                 | 200 | 550                                 | 200 | 550                                 | 200 | 550                                 |      |       |

| t <sub>quickwr</sub> Clnup | Quick Write<br>Cleanup<br>execution time                              |                                                                        | —                                | (# of<br>Quick<br>Writes<br>) * 2.0 |     | (# of<br>Quick<br>Writes )<br>* 2.0 |     | (# of<br>Quick<br>Writes<br>) * 2.0 |     | (# of<br>Quick<br>Writes<br>) * 2.0 | ms   | 7     |

Table 23. Flash command timing specifications for S32K14x (continued)

- 1. All command times assumes 25 MHz or greater flash clock frequency (for synchronization time between internal/external clocks).

- 2. Maximum times for erase parameters based on expectations at cycling end-of-life.

- For all EEPROM Emulation terms, the specified timing shown assumes previous record cleanup has occurred. This may be verified by executing FCCOB Command 0x77, and checking FCCOB number 5 contents show 0x00 - No EEPROM issues detected.

- 4. 1st time EERAM writes after a Reset or SETRAM may incur additional overhead for EEE cleanup, resulting in up to 2× the times shown.

- 5. Only after the Nth write completes will any data be valid. Emulated EEPROM record scheme cleanup overhead may occur after this point even after a brownout or reset. If power on reset occurs before the Nth write completes, the last valid record set will still be valid and the new records will be discarded.

- 6. Quick Write times may take up to 550 µs, as additional cleanup may occur when crossing sector boundaries.

- 7. Time for emulated EEPROM record scheme overhead cleanup. Automatically done after last (Nth) write completes, assuming still powered. Or via SETRAM cleanup execution command is requested at a later point.

## Table 24. Flash command timing specifications for S32K11x

| Symbol              | Descripti                        | on <sup>1</sup> | S32 | 2K116 | S   | 32K118 |      |       |

|---------------------|----------------------------------|-----------------|-----|-------|-----|--------|------|-------|

|                     |                                  |                 | Тур | Max   | Тур | Max    | Unit | Notes |

| t <sub>rd1blk</sub> | Read 1 Block execution           | 32 KB flash     | —   | 0.36  | —   | 0.36   | ms   |       |

|                     | time                             | 64 KB flash     | —   | —     | —   | _      |      |       |

|                     |                                  | 128 KB flash    | —   | 1.2   | —   | —      |      |       |

|                     |                                  | 256 KB flash    | —   | —     | —   | 2      |      |       |

|                     |                                  | 512 KB flash    | _   | —     | —   | _      | μs   |       |

| t <sub>rd1sec</sub> | Read 1 Section                   | 2 KB flash      |     | 75    | —   | 75     |      |       |

| (                   | execution time                   | 4 KB flash      | —   | 100   | —   | 100    |      |       |

| t <sub>pgmchk</sub> | Program Check<br>execution time  | —               | —   | 100   | -   | 100    | μs   |       |

| t <sub>pgm8</sub>   | Program Phrase<br>execution time | -               | 90  | 225   | 90  | 225    | μs   |       |

| t <sub>ersblk</sub> | Erase Flash Block                | 32 KB flash     | 15  | 300   | 15  | 300    | μs   | 2     |

|                     | execution time                   | 64 KB flash     | —   | —     | —   | _      |      |       |

|                     |                                  | 128 KB flash    | 120 | 1100  | —   | —      |      |       |

|                     |                                  | 256 KB flash    | _   | —     | 250 | 2125   |      |       |

|                     |                                  | 512 KB flash    | _   | —     | —   | —      |      |       |

Table continues on the next page ...

| Table 25. | NVM reliability | y s | pecifications | (continued) | ) |

|-----------|-----------------|-----|---------------|-------------|---|

|-----------|-----------------|-----|---------------|-------------|---|

| Symbol                  | Description                                                             | Min.      | Тур.         | Max. | Unit   | Notes   |

|-------------------------|-------------------------------------------------------------------------|-----------|--------------|------|--------|---------|

|                         | When using FlexMemory feature : Fle                                     | xRAM as E | Emulated EEP | ROM  |        |         |

| t <sub>nvmretee</sub>   | Data retention                                                          | 5         | —            | _    | years  | 4       |

| n <sub>nvmwree16</sub>  | Write endurance <ul> <li>EEPROM backup to FlexRAM ratio = 16</li> </ul> | 100 K     | _            | _    | writes | 5, 6, 7 |

| n <sub>nvmwree256</sub> | <ul> <li>EEPROM backup to FlexRAM ratio = 256</li> </ul>                | 1.6 M     | —            | —    | writes |         |

- 1. Data retention period per block begins upon initial user factory programming or after each subsequent erase.

- 2. Program and Erase for PFlash and DFlash are supported across product temperature specification in Normal Mode (not supported in HSRUN mode).

- 3. Cycling endurance is per DFlash or PFlash Sector.

- 4. Data retention period per block begins upon initial user factory programming or after each subsequent erase. Background maintenance operations during normal FlexRAM usage extend effective data retention life beyond 5 years.

- FlexMemory write endurance specified for 16-bit and/or 32-bit writes to FlexRAM and is supported across product temperature specification in Normal Mode (not supported in HSRUN mode). Greater write endurance may be achieved with larger ratios of EEPROM backup to FlexRAM.

- 6. For usage of any EEE driver other than the FlexMemory feature, the endurance spec will fall back to the specified endurance value of the D-Flash specification (1K).

- 7. FlexMemory calculator tool is available at NXP web site for help in estimation of the maximum write endurance achievable at specific EEPROM/FlexRAM ratios. The "In Spec" portions of the online calculator refer to the NVM reliability specifications section of data sheet. This calculator is only applies to the FlexMemory feature.

## 6.3.2 QuadSPI AC specifications

The following table describes the QuadSPI electrical characteristics.

- Measurements are with maximum output load of 25 pF, input transition of 1 ns and pad configured with fastest slew settings (DSE = 1'b1).

- I/O operating voltage ranges from 2.97 V to 3.6 V

- While doing the mode transition (RUN -> HSRUN or HSRUN -> RUN ), the interface should be OFF.

- Add 50 ohm series termination on board in QuadSPI SCK for Flash A to avoid loop back reflection when using in Internal DQS (PAD Loopback) mode.

- QuadSPI trace length should be 3 inches.

- For non-Quad mode of operation if external device doesn't have pull-up feature, external pull-up needs to be added at board level for non-used pads.

- With external pull-up, performance of the interface may degrade based on load associated with external pull-up.

| NXP            |

|----------------|

| Semiconductors |

S32K1xx Data Sheet, Rev. 8, 06/2018

| FLASH PORT          | FLASH PORT Sym Unit |     |        |               | FLASH A |                 |        |                |        |               |            |                 |        | FLASH B      |                        |               |                   |                 |

|---------------------|---------------------|-----|--------|---------------|---------|-----------------|--------|----------------|--------|---------------|------------|-----------------|--------|--------------|------------------------|---------------|-------------------|-----------------|

|                     |                     |     |        |               | RL      | JN <sup>1</sup> |        |                |        |               | HSR        | UN <sup>1</sup> |        |              | RUN/HSRUN <sup>2</sup> |               |                   |                 |

| QuadSPI Mode        |                     |     |        |               | SI      | DR              |        |                |        |               | SE         | DR              |        |              | SDR                    |               | DDR <sup>3</sup>  |                 |

|                     |                     |     |        | rnal<br>pling |         | Intern          | al DQS |                |        | rnal<br>pling |            | Interna         | al DQS |              |                        | rnal<br>pling | Extern            | al DQS          |

|                     |                     |     | N      | 11            |         | AD<br>oback     |        | ernal<br>oback | N      | 11            | PA<br>Loop |                 |        | rnal<br>back | N                      | 11            | Extern            | al DQS          |

|                     |                     |     | Min    | Мах           | Min     | Max             | Min    | Max            | Min    | Мах           | Min        | Max             | Min    | Max          | Min                    | Мах           | Min               | Max             |

|                     |                     |     |        |               |         | •               | Regis  | ster Sett      | ings   |               | •          | •               |        |              |                        |               |                   | •               |

| MCR[DDR_EN]         |                     | -   | (      | )             | (       | C               | (      | C              | (      | )             | 0          | )               | (      | )            | (                      | )             | -                 | 1               |

| MCR[DQS_EN]         |                     | -   | (      | )             | 1       |                 | 1      |                | 0 1    |               | 1          |                 | 0      |              | 1                      |               |                   |                 |

| MCR[SCLKCFG[0]]     |                     | -   | -      | -             | -       | 1               | 0      |                | - 1    |               |            | 0               |        | -            |                        | -             |                   |                 |

| MCR[SCLKCFG[1]]     |                     | -   | -      | -             | -       | 1               | 0      |                | - 1    |               | 0          |                 | -      |              | -                      |               |                   |                 |

| MCR[SCLKCFG[2]]     |                     | -   | -      | -             |         | -               | -      |                | -      |               | -          |                 | -      |              | -                      |               | 0                 |                 |

| MCR[SCLKCFG[3]]     |                     | -   | -      | -             |         | -               | -      |                | -      |               | -          |                 | -      |              | -                      |               | 0                 |                 |

| MCR[SCLKCFG[5]]     |                     | -   | (      | )             | (       | C               | 0      |                | 0      |               | 0          |                 | 0      |              | 0                      |               | 1                 |                 |

| SMPR[FSPHS]         |                     | -   | (      | )             | -       | 1               | 0      |                | 0 1    |               | 0          |                 | 0      |              | 0                      |               |                   |                 |

| SMPR[FSDLY]         |                     | -   | (      | )             | (       | )               | (      | C              | (      | 0 0           |            | 0               |        | 0            |                        | 0             |                   |                 |

| SOCCR               |                     |     | -      | -             | 0       |                 | 23     |                | -      |               | 0          |                 | 30     |              | -                      |               | -                 |                 |

| [SOCCFG[7:0]]       |                     |     |        |               |         |                 |        |                |        |               |            |                 |        |              |                        |               |                   |                 |

| SOCCR[SOCCFG[15:8]] |                     | -   | -      |               |         | -               |        | -              | -      |               | -          |                 |        | -            | -                      |               | 3                 | 0               |

| FLSHCR[TDH]         |                     | -   | 0x     | 0x00 0x00     |         | 0x              | :00    | 0x             | 00     | 0x(           | 00         | 0x              | 00     | 0x           | 00                     | 0x            | 01                |                 |

|                     |                     |     |        |               |         |                 | Timing | g Param        | eters  |               |            |                 |        |              |                        |               |                   |                 |

| SCK Clock Frequency | f <sub>SCK</sub>    | MHz | -      | 38            | -       | 64              | -      | 48             | -      | 40            | -          | 80              | -      | 50           | -                      | 20            | -                 | 20 <sup>4</sup> |

| SCK Clock Period    | t <sub>SCK</sub>    | ns  | 1/fSCK | -             | 1/fSCK  | -               | 1/fSCK | -              | 1/fSCK | -             | 1/fSCK     | -               | 1/fSCK | -            | 50.0                   | -             | 50.0 <sup>4</sup> | -               |

Table continues on the next page...

Memory and memory interfaces

39

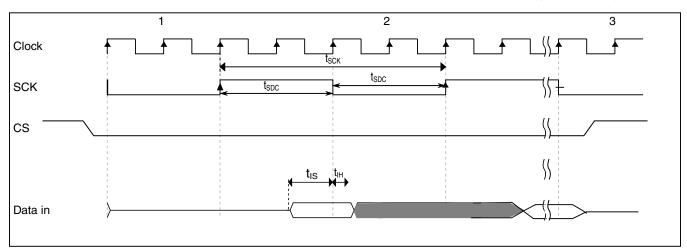

Figure 9. QuadSPI input timing (SDR mode) diagram

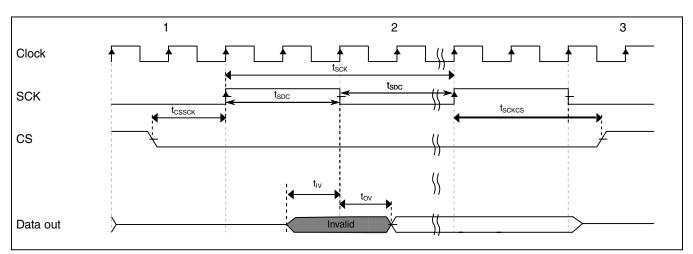

Figure 10. QuadSPI output timing (SDR mode) diagram

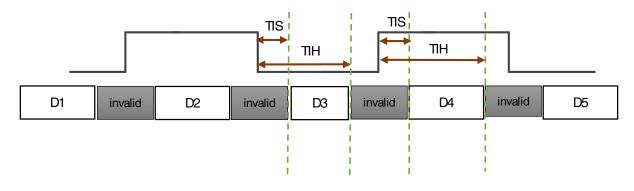

TIS-Setup Time TIH-Hold Time

Figure 11. QuadSPI input timing (HyperRAM mode) diagram

## 6.4.1.2 12-bit ADC electrical characteristics

## NOTE

- ADC performance specifications are documented using a single ADC. For parallel/simultaneous operation of both ADCs, either for sampling the same channel by both ADCs or for sampling different channels by each ADC, some amount of decrease in performance can be expected. Care must be taken to stagger the two ADC conversions, in particular the sample phase, to minimize the impact of simultaneous conversions.

- On reduced pin packages where ADC reference pins are shared with supply pins, ADC analog performance characteristics may be impacted. The amount of variation will be directly impacted by the external PCB layout and hence care must be taken with PCB routing. See AN5426 for details

| Symbol               | Description                | Conditions <sup>1</sup> | Min. | Typ. <sup>2</sup> | Max.                                                 | Unit             | Notes      |

|----------------------|----------------------------|-------------------------|------|-------------------|------------------------------------------------------|------------------|------------|

| V <sub>DDA</sub>     | Supply voltage             |                         | 2.7  | _                 | 3                                                    | V                |            |

| I <sub>DDA_ADC</sub> | Supply current per ADC     |                         | _    | 0.6               | _                                                    | mA               | 3          |

| SMPLTS               | Sample Time                |                         | 275  | _                 | Refer to<br>the<br><i>Reference</i><br><i>Manual</i> | ns               |            |

| TUE <sup>4</sup>     | Total unadjusted error     |                         | _    | ±4                | ±8                                                   | LSB <sup>5</sup> | 6, 7, 8, 9 |

| DNL                  | Differential non-linearity |                         | _    | ±1.0              | _                                                    | LSB <sup>5</sup> | 6, 7, 8, 9 |

| INL                  | Integral non-linearity     |                         | _    | ±2.0              | —                                                    | LSB <sup>5</sup> | 6, 7, 8, 9 |

Table 28. 12-bit ADC characteristics (2.7 V to 3 V) ( $V_{REFH} = V_{DDA}$ ,  $V_{REFL} = V_{SS}$ )

- 1. All accuracy numbers assume the ADC is calibrated with V<sub>REFH</sub>=V<sub>DDA</sub>=V<sub>DD</sub>, with the calibration frequency set to less than or equal to half of the maximum specified ADC clock frequency.

- 2. Typical values assume V<sub>DDA</sub> = 3 V, Temp = 25 °C,  $f_{ADCK}$  = 40 MHz, R<sub>AS</sub>=20  $\Omega$ , and C<sub>AS</sub>=10 nF.

- 3. The ADC supply current depends on the ADC conversion rate.

- 4. Represents total static error, which includes offset and full scale error.

- 5. 1 LSB =  $(V_{REFH} V_{REFL})/2^N$

- 6. The specifications are with averaging and in standalone mode only. Performance may degrade depending upon device use case scenario. When using ADC averaging, refer to the *Reference Manual* to determine the most appropriate settings for AVGS.

- For ADC signals adjacent to V<sub>DD</sub>/V<sub>SS</sub> or XTAL/EXTAL or high frequency switching pins, some degradation in the ADC performance may be observed.

- 8. All values guarantee the performance of the ADC for multiple ADC input channel pins. When using ADC to monitor the internal analog parameters, assume minor degradation.

- 9. All the parameters in the table are given assuming system clock as the clocking source for ADC.

## 6.4.2 CMP with 8-bit DAC electrical specifications Table 31. Comparator with 8-bit DAC electrical specifications

| Symbol             | Description                                          | Min. | Тур.                 | Max.             | Unit |  |  |  |  |

|--------------------|------------------------------------------------------|------|----------------------|------------------|------|--|--|--|--|

| I <sub>DDHS</sub>  | Supply current, High-speed mode <sup>1</sup>         |      |                      |                  | μA   |  |  |  |  |

|                    | -40 - 125 ℃                                          | _    | 230                  | 300              |      |  |  |  |  |

| I <sub>DDLS</sub>  | Supply current, Low-speed mode <sup>1</sup>          |      |                      |                  | μA   |  |  |  |  |

|                    | -40 - 105 °C                                         | _    | 6                    | 11               |      |  |  |  |  |

|                    | -40 - 125 ℃                                          | -    | 6                    | 13               |      |  |  |  |  |

| V <sub>AIN</sub>   | Analog input voltage                                 | 0    | 0 - V <sub>DDA</sub> | V <sub>DDA</sub> | V    |  |  |  |  |

| V <sub>AIO</sub>   | Analog input offset voltage, High-speed mode         |      |                      |                  | mV   |  |  |  |  |

|                    | -40 - 125 °C                                         | -25  | ±1                   | 25               |      |  |  |  |  |

| V <sub>AIO</sub>   | Analog input offset voltage, Low-speed mode          |      |                      |                  | mV   |  |  |  |  |

|                    | -40 - 125 °C                                         | -40  | ±4                   | 40               |      |  |  |  |  |

| t <sub>DHSB</sub>  | Propagation delay, High-speed mode <sup>2</sup>      |      |                      |                  | ns   |  |  |  |  |

|                    | -40 - 105 °C                                         | _    | 35                   | 200              |      |  |  |  |  |

|                    | -40 - 125 °C                                         | _    | 35                   | 300              |      |  |  |  |  |

| t <sub>DLSB</sub>  | Propagation delay, Low-speed mode <sup>2</sup>       |      |                      |                  | μs   |  |  |  |  |

|                    | -40 - 105 °C                                         | _    | 0.5                  | 2                |      |  |  |  |  |

|                    | -40 - 125 ℃                                          | _    | 0.5                  | 3                |      |  |  |  |  |

| t <sub>DHSS</sub>  | Propagation delay, High-speed mode <sup>3</sup>      |      |                      |                  | ns   |  |  |  |  |

|                    | -40 - 105 °C                                         | _    | 70                   | 400              |      |  |  |  |  |

|                    | -40 - 125 ℃                                          | _    | 70                   | 500              |      |  |  |  |  |

| t <sub>DLSS</sub>  | Propagation delay, Low-speed mode <sup>3</sup>       |      |                      |                  | μs   |  |  |  |  |

|                    | -40 - 105 °C                                         | _    | 1                    | 5                |      |  |  |  |  |

|                    | -40 - 125 °C                                         | _    | 1                    | 5                | 1    |  |  |  |  |

| t <sub>IDHS</sub>  | Initialization delay, High-speed mode <sup>4</sup>   |      |                      |                  | μs   |  |  |  |  |

|                    | -40 - 125 °C                                         |      | 1.5                  | 3                |      |  |  |  |  |

| t <sub>IDLS</sub>  | Initialization delay, Low-speed mode <sup>4</sup>    |      |                      |                  | μs   |  |  |  |  |

|                    | -40 - 125 °C                                         | _    | 10                   | 30               |      |  |  |  |  |

| V <sub>HYST0</sub> | Analog comparator hysteresis, Hyst0                  |      |                      |                  | mV   |  |  |  |  |

|                    | -40 - 125 °C                                         | _    | 0                    | _                |      |  |  |  |  |

| V <sub>HYST1</sub> | Analog comparator hysteresis, Hyst1, High-speed mode |      | -                    |                  | mV   |  |  |  |  |

|                    | -40 - 125 °C                                         | _    | 19                   | 66               |      |  |  |  |  |

|                    | Analog comparator hysteresis, Hyst1, Low-speed mode  |      |                      |                  |      |  |  |  |  |

|                    | -40 - 125 °C                                         | _    | 15                   | 40               |      |  |  |  |  |

| V <sub>HYST2</sub> | Analog comparator hysteresis, Hyst2, High-speed mode |      |                      |                  | mV   |  |  |  |  |

|                    | -40 - 125 °C                                         | _    | 34                   | 133              |      |  |  |  |  |

Table continues on the next page...

**Communication modules**

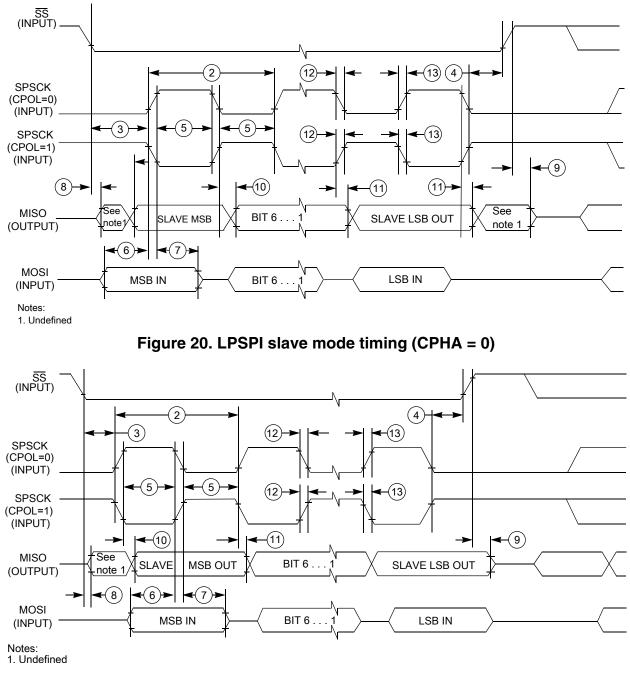

## Table 32. LPSPI electrical specifications1 (continued)

| Num | Num Symbol Dese                                                                                |                              | Conditions                            |                                       | Run                              | Mode <sup>2</sup> |                                  |            | HSRU                                      | N Mode <sup>2</sup>                  |                                     |            | VLPR                                | Mode       |                                    | Un   |    |   |   |   |

|-----|------------------------------------------------------------------------------------------------|------------------------------|---------------------------------------|---------------------------------------|----------------------------------|-------------------|----------------------------------|------------|-------------------------------------------|--------------------------------------|-------------------------------------|------------|-------------------------------------|------------|------------------------------------|------|----|---|---|---|

|     |                                                                                                |                              |                                       |                                       | 5.0                              | V IO              | 3.3                              | V IO       | 5.0                                       | V IO                                 | 3.3                                 | V IO       | 5.0                                 | V IO       | 3.3                                | V IO |    |   |   |   |

|     |                                                                                                |                              |                                       | Min.                                  | Max.                             | Min.              | Max.                             | Min.       | Max.                                      | Min.                                 | Max.                                | Min.       | Max.                                | Min.       | Max.                               |      |    |   |   |   |

| 4   | t <sub>Lag</sub> 9                                                                             | Enable lag                   | Slave                                 | -                                     | -                                | -                 | -                                | -          | -                                         | -                                    | -                                   | -          | -                                   | -          | -                                  | ns   |    |   |   |   |

|     |                                                                                                | time (After<br>SPSCK delay)  | Master                                |                                       | -                                |                   | -                                |            | -                                         |                                      | -                                   |            | -                                   |            | -                                  |      |    |   |   |   |

|     |                                                                                                | of corradiay)                | Master<br>Loopback <sup>5</sup>       | - 25                                  |                                  | - 25              |                                  | - 25       |                                           | - 25                                 |                                     | - 50       |                                     | - 50       |                                    |      |    |   |   |   |

|     |                                                                                                |                              |                                       | Master<br>Loopback(slow) <sup>6</sup> | (SCKPCS+1)*t <sub>periph</sub> - |                   | (SCKPCS+1)*t <sub>periph</sub> - |            | (SCKPCS+1)*t <sub>periph</sub> -          |                                      | (SCKPCS+1)*t <sub>periph</sub> - 25 |            | (SCKPCS+1)*t <sub>periph</sub> - 50 |            | (SCKPCS+1)*t <sub>periph</sub> -50 |      |    |   |   |   |

| 5   | 5 t <sub>WSPSCK</sub> <sup>10</sup> Clock(SPSCK<br>) high or low<br>time (SPSCK<br>duty cycle) |                              | Slave                                 |                                       |                                  |                   |                                  |            |                                           |                                      |                                     |            |                                     |            |                                    | ns   |    |   |   |   |

|     |                                                                                                | ) high or low<br>time (SPSCK | Master                                | က်<br>ဂ                               | ε<br>+ 3                         | ကို               | ۴+<br>۲-                         | 2+3        | 5 0 0 10 10 10 10 10 10 10 10 10 10 10 10 | 2-2                                  | 5+5                                 | 2-2        | 5+2                                 |            |                                    |      |    |   |   |   |

|     |                                                                                                |                              | Master<br>Loopback <sup>5</sup>       | tsPSCK/2-3<br>tsPSCK/2+3              | tspsck/2+3                       | tspsck/2-3        | tspsck/2+3                       | tspsck/2-3 | tspsck/2+3                                | tspsck/2-3                           | tspsck/2+3                          | tspsck/2-5 | tspsck/2+5                          | tspsck/2-5 | tsPSCK/2+5                         |      |    |   |   |   |

|     |                                                                                                |                              | Master<br>Loopback(slow) <sup>6</sup> | 4                                     | <u>ب</u>                         | +                 | μ,                               | +          | ÷.                                        | -                                    | ÷.                                  | +          | ů.                                  | -          | <u>ب</u>                           |      |    |   |   |   |

| 6   | t <sub>SU</sub>                                                                                | Data setup                   | Slave                                 | 3                                     | -                                | 5                 | -                                | 3          | -                                         | 5                                    | -                                   | 18         | -                                   | 18         | -                                  | ns   |    |   |   |   |

|     |                                                                                                | time(inputs)                 | Master                                | 29                                    | -                                | 38                | -                                | 26         | -                                         | 37 <sup>11</sup><br>32 <sup>12</sup> | -                                   | 72         | -                                   | 78         | -                                  |      |    |   |   |   |

|     |                                                                                                |                              | Master<br>Loopback <sup>5</sup>       | 7                                     | -                                | 8                 | -                                | 5          | -                                         | 7                                    | -                                   | 20         | -                                   | 20         | -                                  |      |    |   |   |   |

|     |                                                                                                |                              | Master<br>Loopback(slow) <sup>6</sup> | 8                                     | -                                | 10                | -                                | 7          | -                                         | 9                                    | -                                   | 20         | -                                   | 20         | -                                  |      |    |   |   |   |

| 7   |                                                                                                | t <sub>HI</sub>              | time (inpute)                         | Slave                                 | 3                                | -                 | 3                                | -          | 3                                         | -                                    | 3                                   | -          | 14                                  | -          | 14                                 | -    | ns |   |   |   |

|     |                                                                                                | time(inputs)                 |                                       | time(inputs)                          | time(inputs)                     | time(inputs)      | time(inputs)                     | Master     | 0                                         | -                                    | 0                                   | -          | 0                                   | -          | 0                                  | -    | 0  | - | 0 | - |

|     |                                                                                                |                              | Master<br>Loopback <sup>5</sup>       | 3                                     | -                                | 3                 | -                                | 2          | -                                         | 3                                    | -                                   | 11         | -                                   | 11         | -                                  |      |    |   |   |   |

|     |                                                                                                |                              | Master<br>Loopback(slow) <sup>6</sup> | 3                                     | -                                | 3                 | -                                | 3          | -                                         | 3                                    | -                                   | 12         | -                                   | 12         | -                                  |      |    |   |   |   |

Table continues on the next page...

52

**Communication modules**

Figure 21. LPSPI slave mode timing (CPHA = 1)

# 6.5.3 LPI2C electrical specifications

See General AC specifications for LPI2C specifications.

For supported baud rate see section 'Chip-specific LPI2C information' of the *Reference Manual*.

# 6.5.4 FlexCAN electical specifications

For supported baud rate, see section 'Protocol timing' of the Reference Manual.

## 6.5.5 SAI electrical specifications

The following table describes the SAI electrical characteristics.

- Measurements are with maximum output load of 50 pF, input transition of 1 ns and pad configured with fastest slew settings (DSE = 1'b1).

- I/O operating voltage ranges from 2.97 V to 3.6 V

- While doing the mode transition (RUN -> HSRUN or HSRUN -> RUN ), the interface should be OFF.

| Symbol | Description                            | Min. | Max. | Unit        |  |  |

|--------|----------------------------------------|------|------|-------------|--|--|

| _      | Operating voltage                      | 2.97 | 3.6  | V           |  |  |

| S1     | SAI_MCLK cycle time                    | 40   | _    | ns          |  |  |

| S2     | SAI_MCLK pulse width high/low          | 45%  | 55%  | MCLK period |  |  |

| S3     | SAI_BCLK cycle time                    | 80   | _    | ns          |  |  |

| S4     | SAI_BCLK pulse width high/low          | 45%  | 55%  | BCLK period |  |  |

| S5     | SAI_RXD input setup before<br>SAI_BCLK | 28   | _    | ns          |  |  |

| S6     | SAI_RXD input hold after<br>SAI_BCLK   | 0    | —    | ns          |  |  |

| S7     | SAI_BCLK to SAI_TXD output valid       | —    | 8    | ns          |  |  |

| S8     | SAI_BCLK to SAI_TXD output<br>invalid  | -2   | —    | ns          |  |  |

| S9     | SAI_FS input setup before<br>SAI_BCLK  | 28   | —    | ns          |  |  |

| S10    | SAI_FS input hold after<br>SAI_BCLK    | 0    | —    | ns          |  |  |

| S11    | SAI_BCLK to SAI_FS output valid        | _    | 8    | ns          |  |  |

| \$12   | SAI_BCLK to SAI_FS output invalid      | -2   | —    | ns          |  |  |

### Dimensions

To determine the junction temperature of the device in the application when heat sinks are not used, the Thermal Characterization Parameter ( $\Psi_{JT}$ ) can be used to determine the junction temperature with a measurement of the temperature at the top center of the package case using this equation:

$$T_J = T_T + (\Psi_{JT} \times P_D)$$

where:

- $T_T$  = thermocouple temperature on top of the package (°C)

- $\Psi_{JT}$  = thermal characterization parameter (°C/W)

- $P_D$  = power dissipation in the package (W)

The thermal characterization parameter is measured per JESD51-2 specification using a 40 gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over about 1 mm of wire extending from the junction. The thermocouple wire is placed flat against the package case to avoid measurement errors caused by cooling effects of the thermocouple wire.

# 8 Dimensions

# 8.1 Obtaining package dimensions

Package dimensions are provided in the package drawings.

To find a package drawing, go to http://www.nxp.com and perform a keyword search for the drawing's document number:

| Package option | Document Number       |

|----------------|-----------------------|

| 32-pin QFN     | SOT617-3 <sup>1</sup> |

| 48-pin LQFP    | 98ASH00962A           |

| 64-pin LQFP    | 98ASS23234W           |

| 100-pin LQFP   | 98ASS23308W           |

| 100-pin MAPBGA | 98ASA00802D           |

| 144-pin LQFP   | 98ASS23177W           |

| 176-pin LQFP   | 98ASS23479W           |

1. 5x5 mm package

Table continues on the next page...

Rev. No.

Date

|   |               | <ul> <li>Updated 3.3 V numbers and added footnote against f<sub>op</sub>, t<sub>SU</sub>, ans t<sub>V</sub> in HSRUN Mode</li> <li>Added footnote to 't<sub>WSPSCK</sub>'</li> <li>Updated Thermal characteristics for S32K11x</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |