Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/fs32k146uat0vlht |

|----------------------------|--------------------------------------------------------------------------|

| Supplier Device Package    | 64-LQFP (10x10)                                                          |

| Package / Case             | 64-LQFP                                                                  |

| Mounting Type              | Surface Mount                                                            |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Oscillator Type            | Internal                                                                 |

| Data Converters            | A/D 24x12b SAR; D/A1x8b                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| RAM Size                   | 128K x 8                                                                 |

| EEPROM Size                | 4K x 8                                                                   |

| Program Memory Type        | FLASH                                                                    |

| Program Memory Size        | 1MB (1M x 8)                                                             |

| Number of I/O              | 58                                                                       |

| Peripherals                | POR, PWM, WDT                                                            |

| Connectivity               | CANbus, FlexIO, I <sup>2</sup> C, LINbus, SPI, UART/USART                |

| Speed                      | 112MHz                                                                   |

| Core Size                  | 32-Bit Single-Core                                                       |

| Core Processor             | ARM® Cortex®-M4F                                                         |

| Product Status             | Active                                                                   |

| Details                    |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### · Communications interfaces

- Up to three Low Power Universal Asynchronous Receiver/Transmitter (LPUART/LIN) modules with DMA support and low power availability

- Up to three Low Power Serial Peripheral Interface (LPSPI) modules with DMA support and low power availability

- Up to two Low Power Inter-Integrated Circuit (LPI2C) modules with DMA support and low power availability

- Up to three FlexCAN modules (with optional CAN-FD support)

- FlexIO module for emulation of communication protocols and peripherals (UART, I2C, SPI, I2S, LIN, PWM, etc).

- Up to one 10/100Mbps Ethernet with IEEE1588 support and two Synchronous Audio Interface (SAI) modules.

#### · Safety and Security

- Cryptographic Services Engine (CSEc) implements a comprehensive set of cryptographic functions as described in the SHE (Secure Hardware Extension) Functional Specification. Note: CSEc (Security) or EEPROM writes/erase will trigger error flags in HSRUN mode (112 MHz) because this use case is not allowed to execute simultaneously. The device will need to switch to RUN mode (80 MHz) to execute CSEc (Security) or EEPROM writes/erase.

- 128-bit Unique Identification (ID) number

- Error-Correcting Code (ECC) on flash and SRAM memories

- System Memory Protection Unit (System MPU)

- Cyclic Redundancy Check (CRC) module

- Internal watchdog (WDOG)

- External Watchdog monitor (EWM) module

### · Timing and control

- Up to eight independent 16-bit FlexTimers (FTM) modules, offering up to 64 standard channels (IC/OC/PWM)

- One 16-bit Low Power Timer (LPTMR) with flexible wake up control

- Two Programmable Delay Blocks (PDB) with flexible trigger system

- One 32-bit Low Power Interrupt Timer (LPIT) with 4 channels

- 32-bit Real Time Counter (RTC)

#### Package

- 32-pin QFN, 48-pin LQFP, 64-pin LQFP, 100-pin LQFP, 100-pin MAPBGA, 144-pin LQFP, 176-pin LQFP package options

- 16 channel DMA with up to 63 request sources using DMAMUX

# 3.2 Ordering information

#### **Product status**

P: Prototype F: Qualified

#### Product type/brand

S32: Automotive 32-bit MCU

#### Product line

K: Arm Cortex MCUs

### Series/Family

1: 1st product series

2: 2nd product series

#### Core platform/Performance

1: Arm Cortex M0+

4: Arm Cortex M4F

### Memory size

|         | 2    | 4    | 6    | 8    |  |  |

|---------|------|------|------|------|--|--|

| S32K11x |      |      | 128K | 256K |  |  |

| S32K14x | 256K | 512K | 1M   | 2M   |  |  |

#### **Ordering option**

X: Speed

B: 48 MHz without DMA (S32K11x only) L: 48 MHz with DMA (S32K11x only)

H: 80 MHz

U1: 112 MHz (Not valid with M temperature/125C)

Y: Optional feature

R: Base feature set F: CAN FD, FlexIO

A1: CAN FD, FlexIO, Security

E: Ethernet, Serial Audio Interface (S32K148 only)

J1: Ethernet, Serial Audio Interface, CAN FD, FlexIO, Security (S32K148 only)

### Wafer, Fab and revision

Fx: ATMC<sup>2</sup> Tx: GF XX: Flex #<sup>2</sup>

x0: 1st revision

#### Temperature

V: -40C to 105C M: -40C to 125C W: -40C to 150C<sup>2</sup>

#### **Package**

| Pins | LQFP | QFN | BGA |

|------|------|-----|-----|

| 32   | -    | FM  | -   |

| 48   | LF   | •   | -   |

| 64   | H    | -   | -   |

| 100  | LL   | ,   | МН  |

| 144  | ß    |     | •   |

| 176  | LU   | -   | -   |

### Tape and Reel

T: Trays/Tubes

R: Tape and Reel

- CSEc (Security) or EEPROM writes/erase will trigger error flags in HSRUN mode (112 MHz) because this use case is not allowed to

execute simultaneously. The device will need to switch to RUN mode (80 MHz) to execute CSEc (Security) or EEPROM writes/erase.

- 2. Not supported yet

- Part numbers no longer offered as standard include:

Ordering Option X (M:64MHz); Ordering Option Y (N: limited RAM. 16KB for K142, 48KB for K144, 96KB for K146, 192KB for K148

Security); Temperature (C: -40C to 85C)

### NOTE

Not all part number combinations are available. See S32K1xx\_Orderable\_Part\_Number\_List.xlsx attached with the Datasheet for list of standard orderable parts.

### Figure 4. Ordering information

S32K1xx Data Sheet, Rev. 8, 06/2018

Table 5. V<sub>DD</sub> supply LVR, LVD and POR operating requirements (continued)

| Symbol                | Description                           | Min. | Тур.  | Max. | Unit | Notes |

|-----------------------|---------------------------------------|------|-------|------|------|-------|

| $V_{LVW}$             | Falling low-voltage warning threshold | 4.19 | 4.305 | 4.5  | V    |       |

| V <sub>LVW_HYST</sub> | LVW hysteresis                        | _    | 75    | _    | mV   | 1     |

| V <sub>BG</sub>       | Bandgap voltage reference             | 0.97 | 1.00  | 1.03 | V    |       |

1. Rising threshold is the sum of falling threshold and hysteresis voltage.

# 4.6 Power mode transition operating behaviors

All specifications in the following table assume this clock configuration:

- RUN Mode:

- Clock source: FIRC

- SYS CLK/CORE CLK = 48 MHz

- BUS CLK = 48 MHz

- FLASH\_CLK = 24 MHz

- HSRUN Mode:

- Clock source: SPLL

- SYS CLK/CORE CLK = 112 MHz

- BUS CLK = 56 MHz

- FLASH\_CLK = 28 MHz

- VLPR Mode:

- Clock source: SIRC

- SYS\_CLK/CORE\_CLK = 4 MHz

- BUS CLK = 4 MHz

- FLASH CLK = 1 MHz

- STOP1/STOP2 Mode:

- Clock source: FIRC

- SYS CLK/CORE CLK = 48 MHz

- BUS\_CLK = 48 MHz

- FLASH CLK = 24 MHz

- VLPS Mode: All clock sources disabled <sup>1</sup>

Table 6. Power mode transition operating behaviors

| Symbol | Description                                                                                                                                                       | Min. | Тур. | Max. | Unit |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

|        | After a POR event, amount of time from the point $V_{DD}$ reaches 2.7 V to execution of the first instruction across the operating temperature range of the chip. | _    | 325  | _    | μs   |

Table continues on the next page...

- 1. For S32K11x FIRC/SOSC

- For S32K14x FIRC/SOSC/SPLL

S32K1xx Data Sheet, Rev. 8, 06/2018

#### I/O parameters

- Several I/O have both high drive and normal drive capability selected by the associated Portx\_PCRn[DSE] control bit. All other GPIOs are normal drive only. For details see IO Signal Description Input Multiplexing sheet(s) attached with the Reference Manual.

- 7. When using ENET and SAI on S32K148, the overall device limits associated with high drive pin configurations must be respected i.e. On 144-pin LQFP the general purpose pins: PTA10, PTD0, and PTE4 must be set to low drive.

- 8. Measured at input  $V = V_{SS}$

- 9. Measured at input V = V<sub>DD</sub>

# 5.4 DC electrical specifications at 5.0 V Range

Table 12. DC electrical specifications at 5.0 V Range

| Symbol                         | Parameter                                                                 |                           | Value                   |                        | Unit | Notes |

|--------------------------------|---------------------------------------------------------------------------|---------------------------|-------------------------|------------------------|------|-------|

|                                |                                                                           | Min.                      | Тур.                    | Max.                   |      |       |

| $V_{DD}$                       | I/O Supply Voltage                                                        | 4                         | _                       | 5.5                    | V    |       |

| V <sub>ih</sub>                | Input Buffer High Voltage                                                 | 0.65 x<br>V <sub>DD</sub> | _                       | V <sub>DD</sub> + 0.3  | V    | 1     |

| V <sub>il</sub>                | Input Buffer Low Voltage                                                  | V <sub>SS</sub> – 0.3     | _                       | 0.35 x V <sub>DD</sub> | V    | 2     |

| $V_{hys}$                      | Input Buffer Hysteresis                                                   | 0.06 x<br>V <sub>DD</sub> | _                       | _                      | V    |       |

| Ioh <sub>GPIO</sub>            | I/O current source capability measured                                    | 5                         | _                       | _                      | mA   |       |

| $loh_{GPIO-HD\_DSE\_0}$        | when pad V <sub>oh</sub> = (V <sub>DD</sub> - 0.8 V)                      |                           |                         |                        |      |       |

| Iol <sub>GPIO</sub>            | I/O current sink capability measured                                      | 5                         | _                       | _                      | mA   |       |

| Iol <sub>GPIO-HD_DSE_0</sub>   | when pad V <sub>ol</sub> = 0.8 V                                          |                           |                         |                        |      |       |

| Ioh <sub>GPIO-HD_DSE_1</sub>   | I/O current source capability measured when pad $V_{oh} = V_{DD}$ - 0.8 V | 20                        | _                       | _                      | mA   | 3     |

| Iol <sub>GPIO-HD_DSE_1</sub>   | I/O current sink capability measured when pad $V_{ol} = 0.8 \text{ V}$    | 20                        | _                       | _                      | mA   | 3     |

| Ioh <sub>GPIO-FAST_DSE_0</sub> | I/O current sink capability measured when pad $V_{oh} = V_{DD}$ - 0.8 V   | 14.0                      | _                       | _                      | mA   | 4     |

| Iol <sub>GPIO-FAST_DSE_0</sub> | I/O current sink capability measured when pad $V_{ol}$ = 0.8 V            | 14.5                      | _                       | _                      | mA   | 4     |

| Ioh <sub>GPIO-FAST_DSE_1</sub> | I/O current sink capability measured when pad $V_{oh} = V_{DD}$ - 0.8 V   | 21                        | _                       | _                      | mA   | 4     |

| Iol <sub>GPIO-FAST_DSE_1</sub> | I/O current sink capability measured when pad $V_{ol}$ = 0.8 V            | 20.5                      | _                       | _                      | mA   | 4     |

| IOHT                           | Output high current total for all ports                                   | _                         | _                       | 100                    | mA   |       |

| IIN                            | Input leakage current (per pin) for full te                               | mperature r               | ange at V <sub>DE</sub> | = 5.5 V                |      | 5     |

|                                | All pins other than high drive port pins                                  |                           | 0.005                   | 0.5                    | μΑ   |       |

|                                | High drive port pins                                                      |                           | 0.010                   | 0.5                    | μΑ   |       |

| R <sub>PU</sub>                | Internal pullup resistors                                                 | 20                        |                         | 50                     | kΩ   | 6     |

| R <sub>PD</sub>                | Internal pulldown resistors                                               | 20                        |                         | 50                     | kΩ   | 7     |

- 1. For reset pads, same V<sub>ih</sub> levels are applicable

- 2. For reset pads, same V<sub>il</sub> levels are applicable

- 3. The strong pad I/O pin is capable of switching a 50 pF load up to 40 MHz.

- 4. For refernce only. Run simulations with the IBIS model and custom board for accurate results.

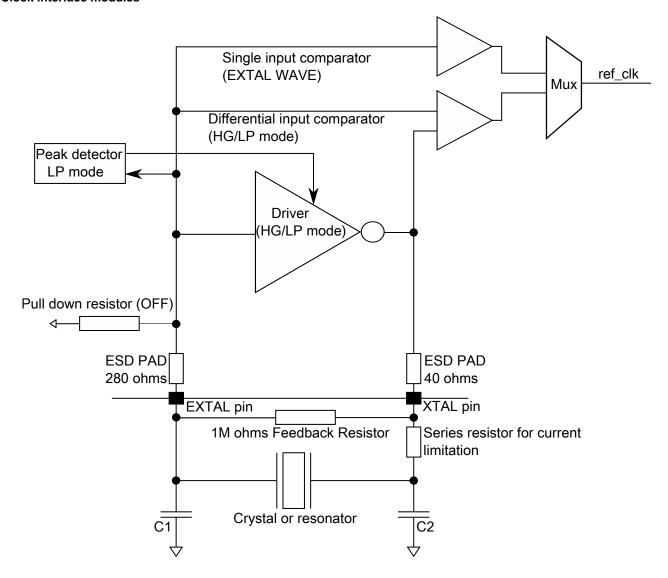

Figure 8. Oscillator connections scheme

Table 17. External System Oscillator electrical specifications

| Symbol              | Description                                           | Min.                  | Тур. | Max.            | Unit | Notes |

|---------------------|-------------------------------------------------------|-----------------------|------|-----------------|------|-------|

| g <sub>m</sub> xosc | Crystal oscillator transconductance                   |                       | -    |                 |      |       |

|                     | SCG_SOSCCFG[RANGE]=2'b10 for 4-8 MHz                  | 2.2                   | _    | 13.7            | mA/V |       |

|                     | SCG_SOSCCFG[RANGE]=2'b11 for 8-40 MHz                 | 16                    | _    | 47              | mA/V |       |

| V <sub>IL</sub>     | Input low voltage — EXTAL pin in external clock mode  | V <sub>SS</sub>       | _    | 1.15            | V    |       |

| V <sub>IH</sub>     | Input high voltage — EXTAL pin in external clock mode | 0.7 * V <sub>DD</sub> | _    | V <sub>DD</sub> | V    |       |

| C <sub>1</sub>      | EXTAL load capacitance                                | _                     | _    | _               |      | 1     |

| C <sub>2</sub>      | XTAL load capacitance                                 | _                     | _    | _               |      | 1     |

| R <sub>F</sub>      | Feedback resistor                                     |                       | •    | •               |      | 2     |

|                     | Low-gain mode (HGO=0)                                 | _                     | _    | _               | ΜΩ   |       |

Table continues on the next page...

### Memory and memory interfaces

Table 24. Flash command timing specifications for S32K11x (continued)

| Symbol                  | Description                                            | on <sup>1</sup>        | S3   | 2K116 | S    | 32K118 |      |       |

|-------------------------|--------------------------------------------------------|------------------------|------|-------|------|--------|------|-------|

|                         |                                                        |                        | Тур  | Max   | Тур  | Max    | Unit | Notes |

| t <sub>ersscr</sub>     | Erase Flash Sector execution time                      | _                      | 12   | 130   | 12   | 130    | ms   | 2     |

| t <sub>pgmsec1k</sub>   | Program Section<br>execution time (1 KB<br>flash)      | _                      | 5    | _     | 5    | _      | ms   |       |

| t <sub>rd1all</sub>     | Read 1s All Block execution time                       | _                      | _    | 1.7   | _    | 2.8    | ms   |       |

| t <sub>rdonce</sub>     | Read Once execution time                               | _                      | _    | 30    | _    | 30     | μs   |       |

| t <sub>pgmonce</sub>    | Program Once execution time                            | _                      | 90   | _     | 90   | _      | μs   |       |

| t <sub>ersall</sub>     | Erase All Blocks execution time                        | _                      | 150  | 1500  | 230  | 2500   | ms   | 2     |

| t <sub>vfykey</sub>     | Verify Backdoor Access<br>Key execution time           | _                      | _    | 35    | _    | 35     | μs   |       |

| t <sub>ersallu</sub>    | Erase All Blocks<br>Unsecure execution time            | _                      | 150  | 1500  | 230  | 2500   | ms   | 2     |

| t <sub>pgmpart</sub>    | Program Partition for EEPROM execution time            | 32 KB EEPROM<br>backup | 71   | _     | 71   | _      | ms   | 3     |

|                         |                                                        | 64 KB EEPROM<br>backup | _    | _     | _    | _      |      |       |

| t <sub>setram</sub>     | Set FlexRAM Function execution time                    | Control Code<br>0xFF   | 0.08 | _     | 0.08 | _      | ms   | 3     |

|                         |                                                        | 32 KB EEPROM<br>backup | 0.8  | 1.2   | 0.8  | 1.2    |      |       |

|                         |                                                        | 48 KB EEPROM<br>backup | _    | _     | _    | _      |      |       |

|                         |                                                        | 64 KB EEPROM<br>backup | _    | _     | _    | _      |      |       |

| t <sub>eewr8b</sub>     | Byte write to FlexRAM execution time                   | 32 KB EEPROM<br>backup | 385  | 1700  | 385  | 1700   | μs   | 3,4   |

|                         |                                                        | 48 KB EEPROM<br>backup | _    | _     | _    | _      |      |       |

|                         |                                                        | 64 KB EEPROM<br>backup |      | _     | _    | _      |      |       |

| t <sub>eewr16b</sub>    | 16-bit write to FlexRAM execution time                 | 32 KB EEPROM<br>backup | 385  | 1700  | 385  | 1700   | μs   | 3,4   |

|                         |                                                        | 48 KB EEPROM<br>backup | _    | _     | _    | _      |      |       |

|                         |                                                        | 64 KB EEPROM<br>backup | _    | _     | _    |        |      |       |

| t <sub>eewr32bers</sub> | 32-bit write to erased FlexRAM location execution time | _                      | 360  | 2000  | 360  | 2000   | μs   |       |

Table continues on the next page...

Table 24. Flash command timing specifications for S32K11x (continued)

| Symbol                    | Descripti                                                                                           | on <sup>1</sup>                                                     | S32 | K116                                | S   | 32K118                        |      |       |

|---------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----|-------------------------------------|-----|-------------------------------|------|-------|

|                           |                                                                                                     |                                                                     | Тур | Max                                 | Тур | Max                           | Unit | Notes |

| t <sub>eewr32b</sub>      | 32-bit write to FlexRAM execution time                                                              | 32 KB EEPROM<br>backup                                              | 630 | 2000                                | 630 | 2000                          | μs   | 3,4   |

|                           |                                                                                                     | 48 KB EEPROM<br>backup                                              | _   | _                                   | _   | _                             |      |       |

|                           |                                                                                                     | 64 KB EEPROM<br>backup                                              | _   | _                                   | _   | _                             |      |       |

| t <sub>quickwr</sub>      | 32-bit Quick Write                                                                                  | 1st 32-bit write                                                    | 200 | 550                                 | 200 | 550                           | μs   | 4.5.6 |

|                           | execution time: Time<br>from CCIF clearing (start<br>the write) until CCIF<br>setting (32-bit write | 2nd through Next<br>to Last (Nth-1)<br>32-bit write                 | 150 | 550                                 | 150 | 550                           |      |       |

|                           | complete, ready for next 32-bit write)                                                              | Last (Nth) 32-bit<br>write (time for<br>write only, not<br>cleanup) | 200 | 550                                 | 200 | 550                           |      |       |

| t <sub>quickwrClnup</sub> | Quick Write Cleanup execution time                                                                  | _                                                                   | _   | (# of<br>Quick<br>Writes ) *<br>2.0 | _   | (# of Quick<br>Writes ) * 2.0 | ms   | 7     |

- 1. All command times assume 25 MHz or greater flash clock frequency (for synchronization time between internal/external clocks).

- 2. Maximum times for erase parameters based on expectations at cycling end-of-life.

- For all EEPROM Emulation terms, the specified timing shown assumes previous record cleanup has occurred. This may

be verified by executing FCCOB Command 0x77, and checking FCCOB number 5 contents show 0x00 No EEPROM

issues detected.

- 4. 1st time EERAM writes after a Reset or SETRAM may incur additional overhead for EEE cleanup, resulting in up to 2x the times shown.

- 5. Only after the Nth write completes will any data be valid. Emulated EEPROM record scheme cleanup overhead may occur after this point even after a brownout or reset. If power on reset occurs before the Nth write completes, the last valid record set will still be valid and the new records will be discarded.

- 6. Quick Write times may take up to 550 µs, as additional cleanup may occur when crossing sector boundaries.

- 7. Time for emulated EEPROM record scheme overhead cleanup. Automatically done after last (Nth) write completes, assuming still powered. Or via SETRAM cleanup execution command is requested at a later point.

#### NOTE

Under certain circumstances FlexMEM maximum times may be exceeded. In this case the user or application may wait, or assert reset to the FTFC macro to stop the operation.

## 6.3.1.2 Reliability specifications

Table 25. NVM reliability specifications

| Symbol                 | Description                           | Min.     | Тур.  | Max. | Unit   | Notes |

|------------------------|---------------------------------------|----------|-------|------|--------|-------|

|                        | When using as Program                 | and Data | Flash | -    |        |       |

| t <sub>nvmretp1k</sub> | Data retention after up to 1 K cycles | 20       | _     | _    | years  | 1     |

| n <sub>nvmcycp</sub>   | Cycling endurance                     | 1 K      | _     | _    | cycles | 2, 3  |

Table continues on the next page...

S32K1xx Data Sheet, Rev. 8, 06/2018

### Memory and memory interfaces

Table 25. NVM reliability specifications (continued)

| Symbol                                                    | Description                                           | Min.  | Тур. | Max. | Unit   | Notes   |  |  |  |  |  |

|-----------------------------------------------------------|-------------------------------------------------------|-------|------|------|--------|---------|--|--|--|--|--|

| When using FlexMemory feature: FlexRAM as Emulated EEPROM |                                                       |       |      |      |        |         |  |  |  |  |  |

| t <sub>nvmretee</sub>                                     | Data retention                                        | 5     | _    | _    | years  | 4       |  |  |  |  |  |

| n <sub>nvmwree16</sub>                                    | Write endurance • EEPROM backup to FlexRAM ratio = 16 | 100 K | _    | _    | writes | 5, 6, 7 |  |  |  |  |  |

| n <sub>nvmwree256</sub>                                   | EEPROM backup to FlexRAM ratio = 256                  | 1.6 M | _    | _    | writes |         |  |  |  |  |  |

- 1. Data retention period per block begins upon initial user factory programming or after each subsequent erase.

- 2. Program and Erase for PFlash and DFlash are supported across product temperature specification in Normal Mode (not supported in HSRUN mode).

- 3. Cycling endurance is per DFlash or PFlash Sector.

- 4. Data retention period per block begins upon initial user factory programming or after each subsequent erase. Background maintenance operations during normal FlexRAM usage extend effective data retention life beyond 5 years.

- 5. FlexMemory write endurance specified for 16-bit and/or 32-bit writes to FlexRAM and is supported across product temperature specification in Normal Mode (not supported in HSRUN mode). Greater write endurance may be achieved with larger ratios of EEPROM backup to FlexRAM.

- 6. For usage of any EEE driver other than the FlexMemory feature, the endurance spec will fall back to the specified endurance value of the D-Flash specification (1K).

- 7. FlexMemory calculator tool is available at NXP web site for help in estimation of the maximum write endurance achievable at specific EEPROM/FlexRAM ratios. The "In Spec" portions of the online calculator refer to the NVM reliability specifications section of data sheet. This calculator is only applies to the FlexMemory feature.

# 6.3.2 QuadSPI AC specifications

The following table describes the QuadSPI electrical characteristics.

- Measurements are with maximum output load of 25 pF, input transition of 1 ns and pad configured with fastest slew settings (DSE = 1'b1).

- I/O operating voltage ranges from 2.97 V to 3.6 V

- While doing the mode transition (RUN -> HSRUN or HSRUN -> RUN ), the interface should be OFF.

- Add 50 ohm series termination on board in QuadSPI SCK for Flash A to avoid loop back reflection when using in Internal DQS (PAD Loopback) mode.

- QuadSPI trace length should be 3 inches.

- For non-Quad mode of operation if external device doesn't have pull-up feature, external pull-up needs to be added at board level for non-used pads.

- With external pull-up, performance of the interface may degrade based on load associated with external pull-up.

Table 26. QuadSPI electrical specifications (continued)

| FLASH PORT                   | Sym                | Unit |              |                 |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              | FLA          | ASH A                          |              |                |                       |              |              |                | FL/          | ASH B              |              |

|------------------------------|--------------------|------|--------------|-----------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|--------------------------------|--------------|----------------|-----------------------|--------------|--------------|----------------|--------------|--------------------|--------------|

|                              |                    |      |              |                 | RU           | JN <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |              |                                |              | HSR            | UN <sup>1</sup>       |              |              |                | RUN/I        | HSRUN <sup>2</sup> | 2            |

| QuadSPI Mode                 |                    |      |              |                 | S            | DR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              |              |                                |              | SDR            |                       |              |              | SDR            |              | DDR <sup>3</sup>   |              |

|                              |                    |      |              | ernal<br>ipling |              | Internal DQS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |              | Internal Internal DQS Sampling |              |                | al DQS                |              |              | ernal<br>pling | External DQS |                    |              |

|                              |                    |      | N            |                 |              | PAD International Internationa |              |              | N1                             |              |                | PAD Internal Loopback |              |              | N1             |              | External DQS       |              |

|                              | 1                  |      | Min          | Max             | Min          | Max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Min          | Max          | Min                            | Max          | Min            | Max                   | Min          | Max          | Min            | Max          | Min                | Max          |

| SCK Duty Cycle               | tspc               | ns   | tSCK/2 - 1.5 | tSCK/2 + 1.5    | tSCK/2 - 1.5 | tSCK/2 + 1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | tSCK/2 - 1.5 | tSCK/2 + 1.5 | tSCK/2 - 1.5                   | tSCK/2 + 1.5 | tSCK/2 - 0.750 | tSCK/2 - 0.750        | tSCK/2 - 1.5 | tSCK/2 + 1.5 | tSCK/2 - 2.5   | tSCK/2 + 2.5 | tSCK/2 - 2.5       | tSCK/2 + 2.5 |

| Data Input Setup Time        | t <sub>IS</sub>    | ns   | 15           | -               | 2.5          | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10           | -            | 14                             | -            | 1.6            | -                     | 9            | -            | 25             | -            | 2                  | -            |

| Data Input Hold Time         | t <sub>IH</sub>    | ns   | 0            | -               | 1            | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1            | -            | 0                              | -            | 1              | -                     | 1            | -            | 0              | -            | 20                 | -            |

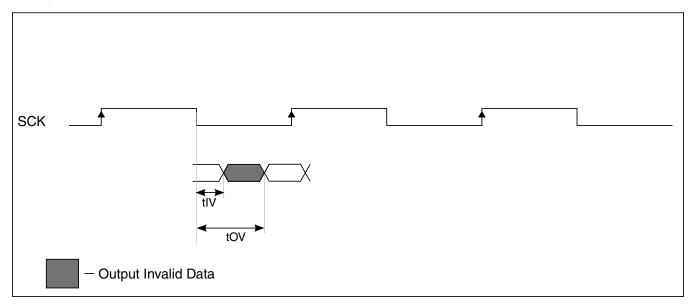

| Data Output Valid Time       | t <sub>OV</sub>    | ns   | -            | 4.5             | -            | 4.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -            | 4.5          | -                              | 4            | -              | 4                     | -            | 4            | -              | 10           | -                  | 10           |

| Data Output In-Valid<br>Time | t <sub>IV</sub>    | ns   | -            | 5               | -            | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -            | 5            | -                              | 5            | -              | 3 <sup>5</sup>        | -            | 5            | -              | 5            | 5                  | -            |

| CS to SCK Time <sup>6</sup>  | t <sub>CSSCK</sub> | ns   | 5            | -               | 5            | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5            | -            | 5                              | -            | 5              | -                     | 5            | -            | 10             | -            | 10                 | -            |

| SCK to CS Time <sup>7</sup>  | t <sub>SCKCS</sub> | ns   | 5            | -               | 5            | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5            | -            | 5                              | -            | 5              | -                     | 5            | -            | 5              | -            | 5                  | -            |

| Output Load                  |                    | pf   | 2            | 25              | 2            | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2            | 25           | 2                              | 25           | 2              | 5                     | 2            | 25           | 2              | 25           | 2                  | 25           |

- 1. See Reference Manual for details on mode settings

- 2. See Reference Manual for details on mode settings

- 3. Valid for HyperRAM only

- 4. RWDS(External DQS CLK) frequency

- 5. For operating frequency ≤ 64 Mhz, Output invalid time is 5 ns.

- 6. Program register value QuadSPI\_FLSHCR[TCSS] = 4`h2

- 7. Program register value QuadSPI\_FLSHCR[TCSH] = 4`h1

### **Analog modules**

Figure 12. QuadSPI output timing (HyperRAM mode) diagram

# 6.4 Analog modules

# 6.4.1 ADC electrical specifications

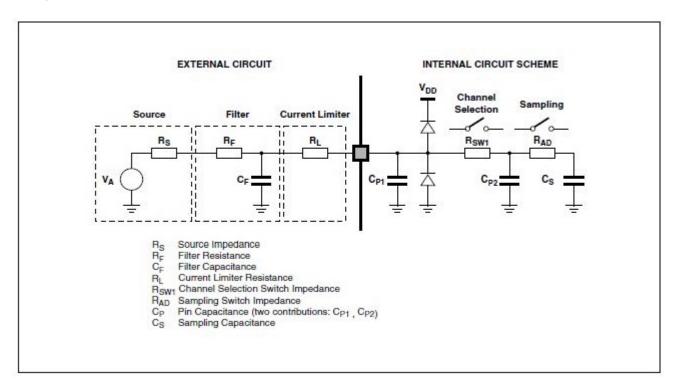

# 6.4.1.1 12-bit ADC operating conditions Table 27. 12-bit ADC operating conditions

| Symbol            | Description                           | Conditions                | Min.                                                                  | Typ. <sup>1</sup>  | Max.                                                                  | Unit | Notes |

|-------------------|---------------------------------------|---------------------------|-----------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------|------|-------|

| V <sub>REFH</sub> | ADC reference voltage high            |                           | See Voltage<br>and current<br>operating<br>requirements<br>for values | $V_{\mathrm{DDA}}$ | See Voltage<br>and current<br>operating<br>requirements<br>for values | V    | 2     |

| V <sub>REFL</sub> | ADC reference voltage low             |                           | See Voltage<br>and current<br>operating<br>requirements<br>for values | 0                  | See Voltage<br>and current<br>operating<br>requirements<br>for values | mV   | 2     |

| V <sub>ADIN</sub> | Input voltage                         |                           | V <sub>REFL</sub>                                                     | _                  | $V_{REFH}$                                                            | V    |       |

| R <sub>S</sub>    | Source impedendance                   | f <sub>ADCK</sub> < 4 MHz | _                                                                     | _                  | 5                                                                     | kΩ   |       |

| R <sub>SW1</sub>  | Channel Selection Switch<br>Impedance |                           | _                                                                     | 0.75               | 1.2                                                                   | kΩ   |       |

| R <sub>AD</sub>   | Sampling Switch Impedance             |                           | _                                                                     | 2                  | 5                                                                     | kΩ   |       |

| C <sub>P1</sub>   | Pin Capacitance                       |                           | _                                                                     | 10                 | _                                                                     | pF   |       |

| C <sub>P2</sub>   | Analog Bus Capacitance                |                           | _                                                                     | _                  | 4                                                                     | pF   |       |

| C <sub>S</sub>    | Sampling capacitance                  |                           | _                                                                     | 4                  | 5                                                                     | pF   |       |

Table continues on the next page...

43

| Table 27. | 12-bit ADC o | perating | conditions ( | (continued) | ) |

|-----------|--------------|----------|--------------|-------------|---|

|-----------|--------------|----------|--------------|-------------|---|

| Symbol            | Description                    | Conditions                                                                                                     | Min. | Typ. <sup>1</sup> | Max.  | Unit | Notes |

|-------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------|------|-------------------|-------|------|-------|

| f <sub>ADCK</sub> | ADC conversion clock frequency | Normal usage                                                                                                   | 2    | 40                | 50    | MHz  | 3, 4  |

| f <sub>CONV</sub> | ADC conversion frequency       | No ADC hardware<br>averaging. <sup>5</sup> Continuous<br>conversions enabled,<br>subsequent conversion<br>time | 46.4 | 928               | 1160  | Ksps | 6, 7  |

|                   |                                | ADC hardware averaging set to 32. <sup>5</sup> Continuous conversions enabled, subsequent conversion time      | 1.45 | 29                | 36.25 | Ksps | 6, 7  |

- 1. Typical values assume  $V_{DDA} = 5 \text{ V}$ , Temp = 25 °C,  $f_{ADCK} = 40 \text{ MHz}$ ,  $R_{AS} = 20 \Omega$ , and  $C_{AS} = 10 \text{ nF}$  unless otherwise stated. Typical values are for reference only, and are not tested in production.

- For packages without dedicated V<sub>REFH</sub> and V<sub>REFL</sub> pins, V<sub>REFH</sub> is internally tied to V<sub>DDA</sub>, and V<sub>REFL</sub> is internally tied to V<sub>SS</sub>.

To get maximum performance, reference supply quality should be better than SAR ADC. See application note AN5032 for details.

- 3. Clock and compare cycle need to be set according to the guidelines mentioned in the Reference Manual .

- 4. ADC conversion will become less reliable above maximum frequency.

- 5. When using ADC hardware averaging, see the Reference Manual to determine the most appropriate setting for AVGS.

- 6. Numbers based on the minimum sampling time of 275 ns.

- 7. For guidelines and examples of conversion rate calculation, see the Reference Manual section 'Calibration function'

Figure 13. ADC input impedance equivalency diagram

S32K1xx Data Sheet, Rev. 8, 06/2018

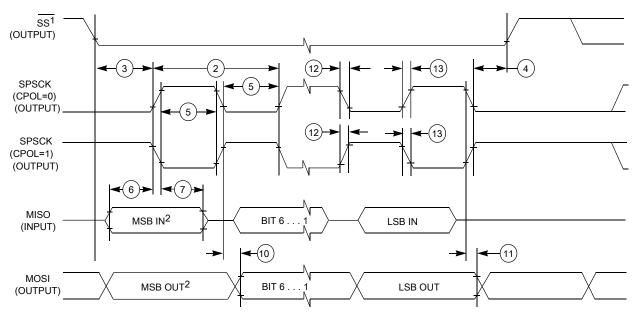

### Table 32. LPSPI electrical specifications1 (continued)

| Num | Symbol | Description | Conditions               | Run Mode <sup>2</sup> |      |      |      | HSRUN | l Mode <sup>2</sup> |      | VLPR Mode |      |      |       | Unit |  |

|-----|--------|-------------|--------------------------|-----------------------|------|------|------|-------|---------------------|------|-----------|------|------|-------|------|--|

|     |        |             |                          | 5.0                   | V IO | 3.3  | V IO | 5.0   | V IO                | 3.3  | V IO      | 5.0  | V IO | 3.3 \ | / IO |  |

|     |        |             |                          | Min.                  | Max. | Min. | Max. | Min.  | Max.                | Min. | Max.      | Min. | Max. | Min.  | Max. |  |

|     |        |             | Master<br>Loopback(slow) | -                     |      | -    |      | -     |                     | -    |           | -    |      | -     |      |  |

- Trace length should not exceed 11 inches for SCK pad when used in Master loopback mode.

- 2. While transitioning from HSRUN mode to RUN mode, LPSPI output clock should not be more than 14 MHz.

- 3. f<sub>periph</sub> = LPSPI peripheral clock

- 4.  $t_{periph} = 1/f_{periph}$

- 5. Master Loopback mode In this mode LPSPI\_SCK clock is delayed for sampling the input data which is enabled by setting LPSPI\_CFGR1[SAMPLE] bit as 1. Clock pads used are PTD15 and PTE0. Applicable only for LPSPI0.

- 6. Master Loopback (slow) In this mode LPSPI\_SCK clock is delayed for sampling the input data which is enabled by setting LPSPI\_CFGR1[SAMPLE] bit as 1. Clock pad used is PTB2. Applicable only for LPSPI0.

- 7. This is the maximum operating frequency (f<sub>op</sub>) for LPSPI0 with medium PAD type only. Otherwise, the maximum operating frequency (f<sub>op</sub>) is 12 Mhz.

- 8. Set the PCSSCK configuration bit as 0, for a minimum of 1 delay cycle of LPSPI baud rate clock, where PCSSCK ranges from 0 to 255.

- 9. Set the SCKPCS configuration bit as 0, for a minimum of 1 delay cycle of LPSPI baud rate clock, where SCKPCS ranges from 0 to 255.

- 10. While selecting odd dividers, ensure Duty Cycle is meeting this parameter.

- 11. Maximum operating frequency (f<sub>op</sub>) is 12 MHz irrespective of PAD type and LPSPI instance.

- 12. Applicable for LPSPI0 only with medium PAD type, with maximum operating frequency (f<sub>op</sub>) as 14 MHz.

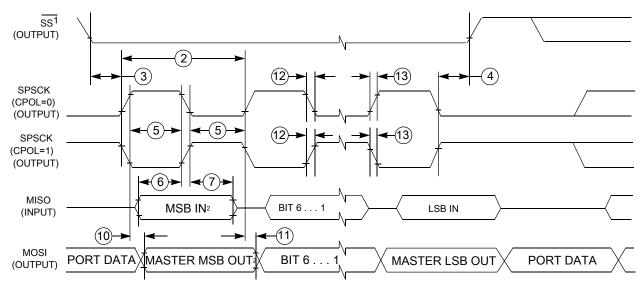

- 1. If configured as an output.

- 2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

Figure 18. LPSPI master mode timing (CPHA = 0)

- 1.If configured as output

- 2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

Figure 19. LPSPI master mode timing (CPHA = 1)

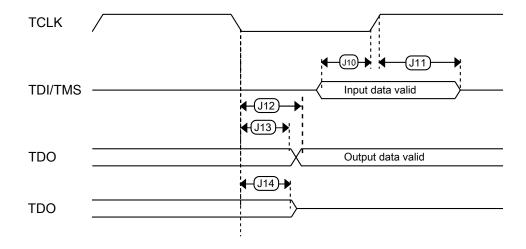

Table 38. SWD electrical specifications

| Symbol | Description                                     |          | Run      | Mode     |          |          | HSRU     | N Mode   |          | VLPR Mode |          |          |          | Unit |

|--------|-------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|-----------|----------|----------|----------|------|

|        |                                                 | 5.0      | V IO     | 3.3 \    | V IO     | 5.0      | V IO     | 3.3      | V IO     | 5.0       | V IO     | 3.3      | V IO     |      |

|        |                                                 | Min.     | Max.     | Min.     | Max.     | Min.     | Max.     | Min.     | Max.     | Min.      | Max.     | Min.     | Max.     |      |

| S1     | SWD_CLK frequency of operation                  | -        | 25       | -        | 25       | -        | 25       | -        | 25       | -         | 10       | -        | 10       | MHz  |

| S2     | SWD_CLK cycle period                            | 1/S1     | -        | 1/S1     | -        | 1/S1     | -        | 1/S1     | -        | 1/S1      | -        | 1/S1     | -        | ns   |

| S3     | SWD_CLK clock pulse width                       | S2/2 - 5 | S2/2 + 5 | S2/2 - 5  | S2/2 + 5 | S2/2 - 5 | S2/2 + 5 | ns   |

| S4     | SWD_CLK rise and fall times                     | -        | 1        | -        | 1        | -        | 1        | -        | 1        | -         | 1        | -        | 1        | ns   |

| S9     | SWD_DIO input data setup time to SWD_CLK rise   | 4        | -        | 4        | -        | 4        | -        | 4        | -        | 16        | -        | 16       | -        | ns   |

| S10    | SWD_DIO input data hold time after SWD_CLK rise | 3        | -        | 3        | -        | 3        | -        | 3        | -        | 10        | -        | 10       | -        | ns   |

| S11    | SWD_CLK high to SWD_DIO data valid              | -        | 28       | -        | 38       | -        | 28       | -        | 38       | -         | 70       | -        | 77       | ns   |

| S12    | SWD_CLK high to SWD_DIO high-Z                  | -        | 28       | -        | 38       | -        | 28       | -        | 38       | -         | 70       | -        | 77       | ns   |

| S13    | SWD_CLK high to SWD_DIO data invalid            | 0        | -        | 0        | -        | 0        | -        | 0        | -        | 0         | -        | 0        | -        | ns   |

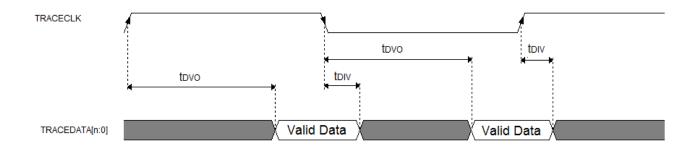

Table 39. Trace specifications (continued)

|                    | Symbol             | Symbol Description  |       | RUN Mode | •  | HSRUN Mode |       | VLPR<br>Mode | Unit |

|--------------------|--------------------|---------------------|-------|----------|----|------------|-------|--------------|------|

|                    | f <sub>TRACE</sub> | Max Trace frequency | 80    | 48       | 40 | 74.667     | 80    | 4            | MHz  |

| ads                | t <sub>DVO</sub>   | Data Output Valid   | 4     | 4        | 4  | 4          | 4     | 20           | ns   |

| Trace on fast pads | t <sub>DIV</sub>   | Data Output Invalid | -2    | -2       | -2 | -2         | -2    | -10          | ns   |

|                    | f <sub>TRACE</sub> | Max Trace frequency | 22.86 | 24       | 20 | 22.4       | 22.86 | 4            | MHz  |

| ads                | t <sub>DVO</sub>   | Data Output Valid   | 8     | 8        | 8  | 8          | 8     | 20           | ns   |

| Trace on slow pads | t <sub>DIV</sub>   | Data Output Invalid | -4    | -4       | -4 | -4         | -4    | -10          | ns   |

Figure 31. TRACE CLKOUT specifications

# 6.6.3 JTAG electrical specifications

Figure 34. Test Access Port timing

# 7 Thermal attributes

# 7.1 Description

The tables in the following sections describe the thermal characteristics of the device.

### **NOTE**

Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting side (board) temperature, ambient temperature, air flow, power dissipation or other components on the board, and board thermal resistance.

# 7.2 Thermal characteristics

Table 41. Thermal characteristics for 32-pin QFN and 48/64/100/144/176-pin LQFP package (continued)

| Rating                                  | Rating Conditions Symbol Package |     | Valı | Values  |         |         |         |         |         |  |

|-----------------------------------------|----------------------------------|-----|------|---------|---------|---------|---------|---------|---------|--|

|                                         |                                  |     |      | S32K116 | S32K118 | S32K142 | S32K144 | S32K146 | S32K148 |  |

| Thermal resistance, Junction to Package | Natural                          | ΨЈТ | 32   | 1       | NA      | NA      | NA      | NA      | NA      |  |

| Top <sup>7</sup>                        | Convection                       |     | 48   | 4       | 2       | NA      | NA      | NA      | NA      |  |

|                                         |                                  |     | 64   | NA      | 2       | 2       | 2       | 2       | NA      |  |

|                                         |                                  |     | 100  | NA      | NA      | 2       | 2       | 2       | NA      |  |

|                                         |                                  |     | 144  | NA      | NA      | NA      | NA      | 2       | 1       |  |

|                                         |                                  |     | 176  | NA      | NA      | NA      | NA      | NA      | 1       |  |

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per JEDEC JESD51-2 with natural convection for horizontally oriented board. Board meets JESD51-9 specification for 1s or 2s2p board, respectively.

- 3. Per JEDEC JESD51-6 with forced convection for horizontally oriented board. Board meets JESD51-9 specification for 1s or 2s2p board, respectively.