Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | ARM® Cortex®-M4F                                                         |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 112MHz                                                                   |

| Connectivity               | CANbus, Ethernet, FlexIO, I <sup>2</sup> C, LINbus, SPI, UART/USART      |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                          |

| Number of I/O              | 156                                                                      |

| Program Memory Size        | 2MB (2M x 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 4K x 8                                                                   |

| RAM Size                   | 256K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| Data Converters            | A/D 32x12b SAR; D/A 1x8b                                                 |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 176-LQFP                                                                 |

| Supplier Device Package    | 176-LQFP (24x24)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/fs32k148ujt0vlut |

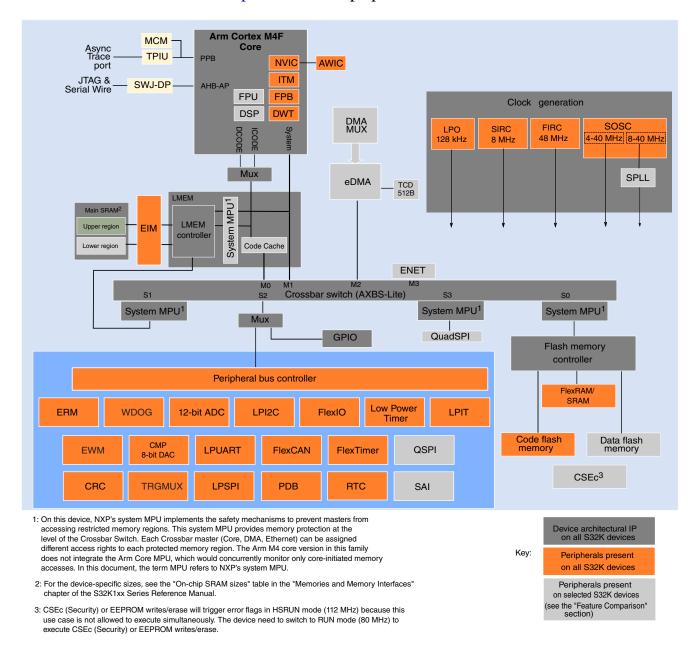

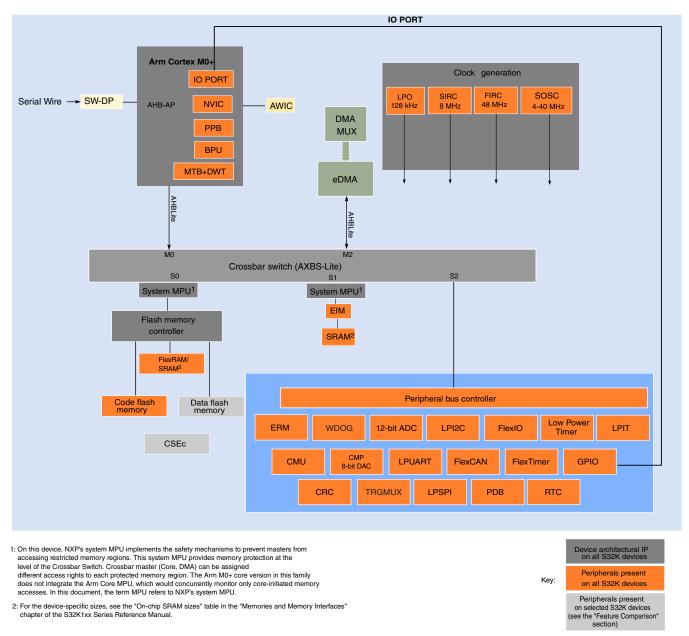

### 1 Block diagram

Following figures show superset high level architecture block diagrams of S32K14x series and S32K11x series respectively. Other devices within the family have a subset of the features. See Feature comparison for chip specific values.

Figure 1. High-level architecture diagram for the S32K14x family

Figure 2. High-level architecture diagram for the S32K11x family

# 2 Feature comparison

The following figure summarizes the memory, peripherals and packaging options for the S32K1xx devices. All devices which share a common package are pin-to-pin compatible.

### **NOTE**

Availability of peripherals depends on the pin availability in a particular package. For more information see *IO Signal*

### 4 General

### 4.1 Absolute maximum ratings

#### **NOTE**

- Functional operating conditions appear in the DC electrical characteristics. Absolute maximum ratings are stress ratings only, and functional operation at the maximum values is not guaranteed. See footnotes in the following table for specific conditions.

- Stress beyond the listed maximum values may affect device reliability or cause permanent damage to the device.

- All the limits defined in the datasheet specification must be honored together and any violation to any one or more will not guarantee desired operation.

- Unless otherwise specified, all maximum and minimum values in the datasheet are across process, voltage, and temperature.

| Symbol                                                                                                   | Parameter                                                                              | Conditions <sup>1</sup> | Min       | Max              | Unit |

|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------|-----------|------------------|------|

| V <sub>DD</sub> <sup>2</sup>                                                                             | 2.7 V - 5. 5V input supply voltage                                                     | _                       | -0.3      | 5.8 <sup>3</sup> | V    |

| $V_{REFH}$                                                                                               | 3.3 V / 5.0 V ADC high reference voltage                                               | _                       | -0.3      | 5.8 <sup>3</sup> | V    |

| I <sub>INJPAD_DC_ABS</sub> <sup>4</sup>                                                                  | Continuous DC input current (positive / negative) that can be injected into an I/O pin | _                       | -3        | +3               | mA   |

| $V_{IN\_DC}$                                                                                             | Continuous DC Voltage on any I/O pin with respect to V <sub>SS</sub>                   | _                       | -0.8      | 5.8 <sup>5</sup> | V    |

| I <sub>INJSUM_DC_ABS</sub>                                                                               | Sum of absolute value of injected currents on all the pins (Continuous DC limit)       | _                       | _         | 30               | mA   |

| T <sub>ramp</sub> <sup>6</sup>                                                                           | ECU supply ramp rate                                                                   | _                       | 0.5 V/min | 500 V/ms         | T —  |

| T <sub>ramp_MCU</sub> <sup>7</sup>                                                                       | MCU supply ramp rate                                                                   | _                       | 0.5 V/min | 100 V/ms         | 1 —  |

| T <sub>A</sub> <sup>8</sup>                                                                              | Ambient temperature                                                                    | _                       | -40       | 125              | °C   |

| T <sub>STG</sub>                                                                                         | Storage temperature                                                                    | _                       | -55       | 165              | °C   |

| V <sub>IN_TRANSIENT</sub> Transient overshoot voltage allowed on I/O pin beyond V <sub>IN_DC limit</sub> |                                                                                        | _                       | _         | 6.8 <sup>9</sup> | V    |

Table 1. Absolute maximum ratings

S32K1xx Data Sheet, Rev. 8, 06/2018

<sup>1.</sup> All voltages are referred to  $V_{\mbox{\footnotesize SS}}$  unless otherwise specified.

<sup>2.</sup> As V<sub>DD</sub> varies between the minimum value and the absolute maximum value the analog characteristics of the I/O and the ADC will both change. See section I/O parameters and ADC electrical specifications respectively for details.

<sup>3. 60</sup> s lifetime - No restrictions i.e. The part can switch.

<sup>10</sup> hours lifetime - Device in reset i.e. The part cannot switch.

### Table 4. Supplies decoupling capacitors 1, 2

| Symbol                                                      | Description                               | Min. <sup>3</sup> | Тур. | Max. | Unit |

|-------------------------------------------------------------|-------------------------------------------|-------------------|------|------|------|

| C <sub>REF</sub> , 4, 5                                     | ADC reference high decoupling capacitance | 70                | 100  | _    | nF   |

| C <sub>DEC</sub> <sup>5</sup> , <sup>6</sup> , <sup>7</sup> | Recommended decoupling capacitance        | 70                | 100  | _    | nF   |

- V<sub>DD</sub> and V<sub>DDA</sub> must be shorted to a common source on PCB. The differential voltage between V<sub>DD</sub> and V<sub>DDA</sub> is for RF-AC only. Appropriate decoupling capacitors to be used to filter noise on the supplies. See application note AN5032 for reference supply design for SAR ADC. All V<sub>SS</sub> pins should be connected to common ground at the PCB level.

- 2. All decoupling capacitors must be low ESR ceramic capacitors (for example X7R type).

- 3. Minimum recommendation is after considering component aging and tolerance.

- 4. For improved performance, it is recommended to use 10  $\mu$ F, 0.1  $\mu$ F and 1 nF capacitors in parallel.

- 5. All decoupling capacitors should be placed as close as possible to the corresponding supply and ground pins.

- 6. Contact your local Field Applications Engineer for details on best analog routing practices.

- 7. The filtering used for decoupling the device supplies must comply with the following best practices rules:

- The protection/decoupling capacitors must be on the path of the trace connected to that component.

- No trace exceeding 1 mm from the protection to the trace or to the ground.

- The protection/decoupling capacitors must be as close as possible to the input pin of the device (maximum 2 mm).

- The ground of the protection is connected as short as possible to the ground plane under the integrated circuit.

Table 5. V<sub>DD</sub> supply LVR, LVD and POR operating requirements (continued)

| Symbol                | Description                           | Min. | Тур.  | Max. | Unit | Notes |

|-----------------------|---------------------------------------|------|-------|------|------|-------|

| V <sub>LVW</sub>      | Falling low-voltage warning threshold | 4.19 | 4.305 | 4.5  | V    |       |

| V <sub>LVW_HYST</sub> | LVW hysteresis                        | _    | 75    | _    | mV   | 1     |

| V <sub>BG</sub>       | Bandgap voltage reference             | 0.97 | 1.00  | 1.03 | V    |       |

1. Rising threshold is the sum of falling threshold and hysteresis voltage.

### 4.6 Power mode transition operating behaviors

All specifications in the following table assume this clock configuration:

- RUN Mode:

- Clock source: FIRC

- SYS CLK/CORE CLK = 48 MHz

- BUS CLK = 48 MHz

- FLASH\_CLK = 24 MHz

- HSRUN Mode:

- Clock source: SPLL

- SYS CLK/CORE CLK = 112 MHz

- BUS CLK = 56 MHz

- FLASH\_CLK = 28 MHz

- VLPR Mode:

- Clock source: SIRC

- SYS\_CLK/CORE\_CLK = 4 MHz

- BUS CLK = 4 MHz

- FLASH CLK = 1 MHz

- STOP1/STOP2 Mode:

- Clock source: FIRC

- SYS CLK/CORE CLK = 48 MHz

- BUS\_CLK = 48 MHz

- FLASH CLK = 24 MHz

- VLPS Mode: All clock sources disabled <sup>1</sup>

Table 6. Power mode transition operating behaviors

| Symbol | Description                                                                                                                                                       | Min. | Тур. | Max. | Unit |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

|        | After a POR event, amount of time from the point $V_{DD}$ reaches 2.7 V to execution of the first instruction across the operating temperature range of the chip. | _    | 325  | _    | μs   |

Table continues on the next page...

1. • For S32K11x – FIRC/SOSC

For S32K14x – FIRC/SOSC/SPLL

S32K1xx Data Sheet, Rev. 8, 06/2018

Table 6. Power mode transition operating behaviors (continued)

| Symbol | Description                     | Min. | Тур.  | Max.  | Unit |

|--------|---------------------------------|------|-------|-------|------|

|        | VLPS → RUN                      | 8    | _     | 17    | μs   |

|        | STOP1 → RUN                     | 0.07 | 0.075 | 0.08  | μs   |

|        | STOP2 → RUN                     | 0.07 | 0.075 | 0.08  | μs   |

|        | VLPR → RUN                      | 19   | _     | 26    | μs   |

|        | VLPR → VLPS                     | 5.1  | 5.7   | 6.5   | μs   |

|        | VLPS → VLPR                     | 18.8 | 23    | 27.75 | μs   |

|        | RUN → Compute operation         | 0.72 | 0.75  | 0.77  | μs   |

|        | HSRUN → Compute operation       | 0.3  | 0.31  | 0.35  | μs   |

|        | RUN → STOP1                     | 0.35 | 0.38  | 0.4   | μs   |

|        | RUN → STOP2                     | 0.2  | 0.23  | 0.25  | μs   |

|        | RUN → VLPS                      | 0.3  | 0.35  | 0.4   | μs   |

|        | RUN → VLPR                      | 3.5  | 3.8   | 5     | μs   |

|        | VLPS → Asynchronous DMA Wakeup  | 105  | 110   | 125   | μs   |

|        | STOP1 → Asynchronous DMA Wakeup | 1    | 1.1   | 1.3   | μs   |

|        | STOP2 → Asynchronous DMA Wakeup | 1    | 1.1   | 1.3   | μs   |

|        | Pin reset → Code execution      | _    | 214   | _     | μs   |

#### NOTE

HSRUN should only be used when frequencies in excess of 80 MHz are required. When using 80 MHz and below, RUN mode is the recommended operating mode.

### 4.7 Power consumption

The following table shows the power consumption targets for the device in various mode of operations. Attached *S32K1xx\_Power\_Modes \_Configuration.xlsx* details the modes used in gathering the power consumption data stated in the following table Table 7. For full functionality refer to table: Module operation in available power modes of the *Reference Manual*.

Table 14. AC electrical specifications at 5 V Range (continued)

| Symbol                   | DSE | Rise tii | me (nS) <sup>1</sup> | Fall time (nS) 1 |      | Capacitance (pF) <sup>2</sup> |

|--------------------------|-----|----------|----------------------|------------------|------|-------------------------------|

|                          |     | Min.     | Max .                | Min.             | Max. |                               |

|                          |     | 17.3     | 54.8                 | 17.6             | 59.7 | 200                           |

|                          | 1   | 1.1      | 4.6                  | 1.1              | 5.0  | 25                            |

|                          |     | 2.0      | 5.7                  | 2.0              | 5.8  | 50                            |

|                          |     | 5.4      | 16.0                 | 5.0              | 16.0 | 200                           |

| tRF <sub>GPIO-FAST</sub> | 0   | 0.42     | 2.2                  | 0.37             | 2.2  | 25                            |

|                          |     | 2.0      | 5.0                  | 1.9              | 5.2  | 50                            |

|                          |     | 9.3      | 18.8                 | 8.5              | 19.3 | 200                           |

|                          | 1   | 0.37     | 0.9                  | 0.35             | 0.9  | 25                            |

|                          |     | 1.2      | 2.7                  | 1.2              | 2.9  | 50                            |

|                          |     | 6.0      | 11.8                 | 6.0              | 12.3 | 200                           |

<sup>1.</sup> For reference only. Run simulations with the IBIS model and your custom board for accurate results.

### 5.7 Standard input pin capacitance

Table 15. Standard input pin capacitance

| Symbol            | Description                     | Min. | Max. | Unit |

|-------------------|---------------------------------|------|------|------|

| C <sub>IN_D</sub> | Input capacitance: digital pins | _    | 7    | pF   |

#### NOTE

Please refer to External System Oscillator electrical specifications for EXTAL/XTAL pins.

### 5.8 Device clock specifications

Table 16. Device clock specifications 1

| Symbol             | Description                      | Min. | Max. | Unit |  |  |  |  |

|--------------------|----------------------------------|------|------|------|--|--|--|--|

|                    | High Speed run mode <sup>2</sup> |      |      |      |  |  |  |  |

| f <sub>SYS</sub>   | System and core clock            | _    | 112  | MHz  |  |  |  |  |

| f <sub>BUS</sub>   | Bus clock                        | _    | 56   | MHz  |  |  |  |  |

| f <sub>FLASH</sub> | Flash clock                      | _    | 28   | MHz  |  |  |  |  |

|                    | Normal run mode (S32K11x series  | )    |      |      |  |  |  |  |

| f <sub>SYS</sub>   | System and core clock            | _    | 48   | MHz  |  |  |  |  |

| f <sub>BUS</sub>   | Bus clock                        | _    | 48   | MHz  |  |  |  |  |

Table continues on the next page...

<sup>2.</sup> Maximum capacitances supported on Standard IOs. However interface or protocol specific specifications might be different, for example for ENET, QSPI etc. . For protocol specific AC specifications, see respective sections.

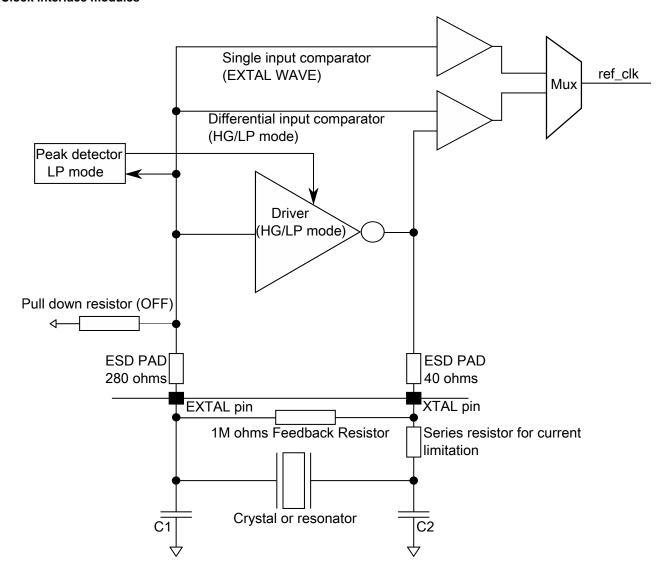

Figure 8. Oscillator connections scheme

Table 17. External System Oscillator electrical specifications

| Symbol              | Description                                           | Min.                  | Тур. | Max.            | Unit | Notes |

|---------------------|-------------------------------------------------------|-----------------------|------|-----------------|------|-------|

| g <sub>m</sub> xosc | Crystal oscillator transconductance                   |                       | -    |                 |      |       |

|                     | SCG_SOSCCFG[RANGE]=2'b10 for 4-8 MHz                  | 2.2                   | _    | 13.7            | mA/V |       |

|                     | SCG_SOSCCFG[RANGE]=2'b11 for 8-40 MHz                 | 16                    | _    | 47              | mA/V |       |

| V <sub>IL</sub>     | Input low voltage — EXTAL pin in external clock mode  | V <sub>SS</sub>       | _    | 1.15            | V    |       |

| V <sub>IH</sub>     | Input high voltage — EXTAL pin in external clock mode | 0.7 * V <sub>DD</sub> | _    | V <sub>DD</sub> | V    |       |

| C <sub>1</sub>      | EXTAL load capacitance                                | _                     | _    | _               |      | 1     |

| C <sub>2</sub>      | XTAL load capacitance                                 | _                     | _    | _               |      | 1     |

| R <sub>F</sub>      | Feedback resistor                                     |                       | •    | •               |      | 2     |

|                     | Low-gain mode (HGO=0)                                 | _                     | _    | _               | ΜΩ   |       |

Table continues on the next page...

# 6.2.4 Low Power Oscillator (LPO) electrical specifications Table 21. Low Power Oscillator (LPO) electrical specifications

| Symbol               | Parameter                               | Min. | Тур. | Max. | Unit |

|----------------------|-----------------------------------------|------|------|------|------|

| F <sub>LPO</sub>     | Internal low power oscillator frequency | 113  | 128  | 139  | kHz  |

| T <sub>startup</sub> | Startup Time                            | _    | _    | 20   | μs   |

### 6.2.5 SPLL electrical specifications

Table 22. SPLL electrical specifications

| Symbol                               | Parameter                                          | Min.   | Тур. | Max.                                                       | Unit |

|--------------------------------------|----------------------------------------------------|--------|------|------------------------------------------------------------|------|

| F <sub>SPLL_REF</sub> <sup>1</sup>   | PLL Reference Frequency Range                      | 8      | _    | 16                                                         | MHz  |

| F <sub>SPLL_Input</sub> <sup>2</sup> | PLL Input Frequency                                | 8      | _    | 40                                                         | MHz  |

| F <sub>VCO_CLK</sub>                 | VCO output frequency                               | 180    | _    | 320                                                        | MHz  |

| F <sub>SPLL_CLK</sub>                | PLL output frequency                               | 90     | _    | 160                                                        | MHz  |

| J <sub>CYC_SPLL</sub>                | PLL Period Jitter (RMS) <sup>3</sup>               |        |      |                                                            |      |

|                                      | at F <sub>VCO_CLK</sub> 180 MHz                    | _      | 120  | _                                                          | ps   |

|                                      | at F <sub>VCO_CLK</sub> 320 MHz                    | _      | 75   | _                                                          | ps   |

| J <sub>ACC_SPLL</sub>                | PLL accumulated jitter over 1µs (RMS) <sup>3</sup> |        |      |                                                            |      |

|                                      | at F <sub>VCO_CLK</sub> 180 MHz                    | _      | 1350 | _                                                          | ps   |

|                                      | at F <sub>VCO_CLK</sub> 320 MHz                    | _      | 600  | _                                                          | ps   |

| D <sub>UNL</sub>                     | Lock exit frequency tolerance                      | ± 4.47 | _    | ± 5.97                                                     | %    |

| T <sub>SPLL_LOCK</sub>               | Lock detector detection time <sup>4</sup>          | _      | _    | 150 × 10 <sup>-6</sup> +<br>1075(1/F <sub>SPLL_REF</sub> ) | S    |

<sup>1.</sup> F<sub>SPLL\_REF</sub> is PLL reference frequency range after the PREDIV. For PREDIV and MULT settings refer SCG\_SPLLCFG register of Reference Manual.

## 6.3 Memory and memory interfaces

### 6.3.1 Flash memory module (FTFC) electrical specifications

This section describes the electrical characteristics of the flash memory module.

<sup>2.</sup> F<sub>SPLL\_Input</sub> is PLL input frequency range before the PREDIV must be limited to the range 8 MHz to 40 MHz. This input source could be derived from a crystal oscillator or some other external square wave clock source using OSC bypass mode. For external clock source settings refer SCG\_SOSCCFG register of Reference Manual.

<sup>3.</sup> This specification was obtained using a NXP developed PCB. PLL jitter is dependent on the noise characteristics of each PCB and results will vary

<sup>4.</sup> Lock detector detection time is defined as the time between PLL enablement and clock availability for system use.

Table 24. Flash command timing specifications for S32K11x (continued)

| Symbol               | Description                                                          | Description <sup>1</sup>                                            |     |                                     | S   | 32K118                        |      |       |

|----------------------|----------------------------------------------------------------------|---------------------------------------------------------------------|-----|-------------------------------------|-----|-------------------------------|------|-------|

|                      |                                                                      |                                                                     | Тур | Max                                 | Тур | Max                           | Unit | Notes |

| t <sub>eewr32b</sub> | 32-bit write to FlexRAM execution time                               | 32 KB EEPROM<br>backup                                              | 630 | 2000                                | 630 | 2000                          | μs   | 3,4   |

|                      |                                                                      | 48 KB EEPROM<br>backup                                              | _   | _                                   | _   | _                             |      |       |

|                      |                                                                      | 64 KB EEPROM<br>backup                                              | _   | _                                   | _   | _                             |      |       |

| t <sub>quickwr</sub> | 32-bit Quick Write                                                   | 1st 32-bit write                                                    | 200 | 550                                 | 200 | 550                           | μs   | 4,5,6 |

|                      | execution time: Time from CCIF clearing (start the write) until CCIF | 2nd through Next<br>to Last (Nth-1)<br>32-bit write                 | 150 | 550                                 | 150 | 550                           |      |       |

|                      | setting (32-bit write complete, ready for next 32-bit write)         | Last (Nth) 32-bit<br>write (time for<br>write only, not<br>cleanup) | 200 | 550                                 | 200 | 550                           |      |       |

| tquickwrClnup        | Quick Write Cleanup execution time                                   | _                                                                   | _   | (# of<br>Quick<br>Writes ) *<br>2.0 | _   | (# of Quick<br>Writes ) * 2.0 | ms   | 7     |

- 1. All command times assume 25 MHz or greater flash clock frequency (for synchronization time between internal/external clocks).

- 2. Maximum times for erase parameters based on expectations at cycling end-of-life.

- For all EEPROM Emulation terms, the specified timing shown assumes previous record cleanup has occurred. This may

be verified by executing FCCOB Command 0x77, and checking FCCOB number 5 contents show 0x00 No EEPROM

issues detected.

- 4. 1st time EERAM writes after a Reset or SETRAM may incur additional overhead for EEE cleanup, resulting in up to 2x the times shown.

- Only after the Nth write completes will any data be valid. Emulated EEPROM record scheme cleanup overhead may occur after this point even after a brownout or reset. If power on reset occurs before the Nth write completes, the last valid record set will still be valid and the new records will be discarded.

- 6. Quick Write times may take up to 550 µs, as additional cleanup may occur when crossing sector boundaries.

- 7. Time for emulated EEPROM record scheme overhead cleanup. Automatically done after last (Nth) write completes, assuming still powered. Or via SETRAM cleanup execution command is requested at a later point.

#### NOTE

Under certain circumstances FlexMEM maximum times may be exceeded. In this case the user or application may wait, or assert reset to the FTFC macro to stop the operation.

### 6.3.1.2 Reliability specifications

Table 25. NVM reliability specifications

| Symbol                 | Description                           | Min.     | Тур.  | Max. | Unit   | Notes |

|------------------------|---------------------------------------|----------|-------|------|--------|-------|

|                        | When using as Program                 | and Data | Flash | -    |        |       |

| t <sub>nvmretp1k</sub> | Data retention after up to 1 K cycles | 20       | _     | _    | years  | 1     |

| n <sub>nvmcycp</sub>   | Cycling endurance                     | 1 K      | _     | _    | cycles | 2, 3  |

Table continues on the next page...

S32K1xx Data Sheet, Rev. 8, 06/2018

#### Memory and memory interfaces

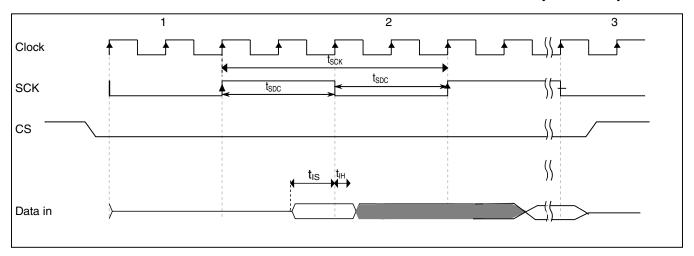

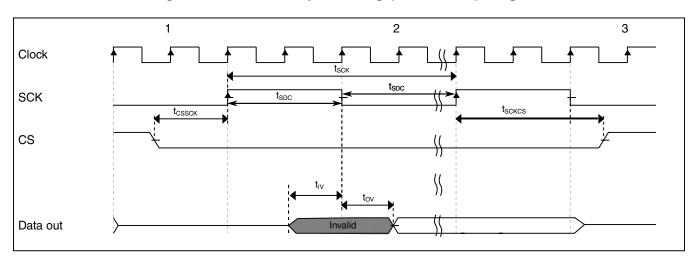

Figure 9. QuadSPI input timing (SDR mode) diagram

Figure 10. QuadSPI output timing (SDR mode) diagram

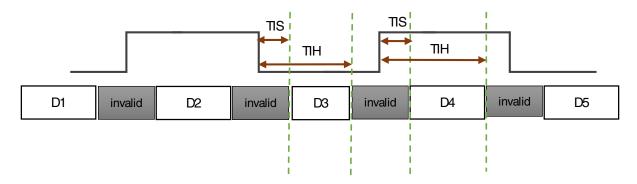

TIS-Setup Time

TIH – Hold Time

Figure 11. QuadSPI input timing (HyperRAM mode) diagram

| Table 27. | 12-bit ADC | operating | conditions | (continued) |

|-----------|------------|-----------|------------|-------------|

|-----------|------------|-----------|------------|-------------|

| Symbol            | Description                    | Conditions                                                                                                     | Min. | Typ. <sup>1</sup> | Max.  | Unit | Notes |

|-------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------|------|-------------------|-------|------|-------|

| f <sub>ADCK</sub> | ADC conversion clock frequency | Normal usage                                                                                                   | 2    | 40                | 50    | MHz  | 3, 4  |

| f <sub>CONV</sub> | ADC conversion frequency       | No ADC hardware<br>averaging. <sup>5</sup> Continuous<br>conversions enabled,<br>subsequent conversion<br>time | 46.4 | 928               | 1160  | Ksps | 6, 7  |

|                   |                                | ADC hardware averaging set to 32. <sup>5</sup> Continuous conversions enabled, subsequent conversion time      | 1.45 | 29                | 36.25 | Ksps | 6, 7  |

- 1. Typical values assume  $V_{DDA} = 5 \text{ V}$ , Temp = 25 °C,  $f_{ADCK} = 40 \text{ MHz}$ ,  $R_{AS} = 20 \Omega$ , and  $C_{AS} = 10 \text{ nF}$  unless otherwise stated. Typical values are for reference only, and are not tested in production.

- For packages without dedicated V<sub>REFH</sub> and V<sub>REFL</sub> pins, V<sub>REFH</sub> is internally tied to V<sub>DDA</sub>, and V<sub>REFL</sub> is internally tied to V<sub>SS</sub>.

To get maximum performance, reference supply quality should be better than SAR ADC. See application note AN5032 for details.

- 3. Clock and compare cycle need to be set according to the guidelines mentioned in the Reference Manual .

- 4. ADC conversion will become less reliable above maximum frequency.

- 5. When using ADC hardware averaging, see the Reference Manual to determine the most appropriate setting for AVGS.

- 6. Numbers based on the minimum sampling time of 275 ns.

- 7. For guidelines and examples of conversion rate calculation, see the Reference Manual section 'Calibration function'

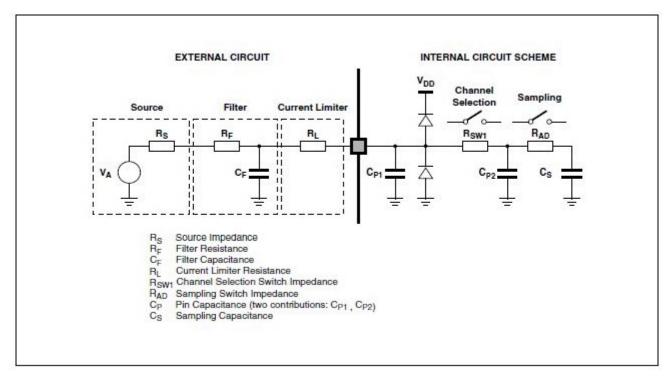

Figure 13. ADC input impedance equivalency diagram

#### 6.4.1.2 12-bit ADC electrical characteristics

#### NOTE

- ADC performance specifications are documented using a single ADC. For parallel/simultaneous operation of both ADCs, either for sampling the same channel by both ADCs or for sampling different channels by each ADC, some amount of decrease in performance can be expected. Care must be taken to stagger the two ADC conversions, in particular the sample phase, to minimize the impact of simultaneous conversions.

- On reduced pin packages where ADC reference pins are shared with supply pins, ADC analog performance characteristics may be impacted. The amount of variation will be directly impacted by the external PCB layout and hence care must be taken with PCB routing. See AN5426 for details

Table 28. 12-bit ADC characteristics (2.7 V to 3 V) ( $V_{REFH} = V_{DDA}$ ,  $V_{REFL} = V_{SS}$ )

| Symbol               | Description                | Conditions <sup>1</sup> | Min. | Typ. <sup>2</sup> | Max.                                   | Unit             | Notes      |

|----------------------|----------------------------|-------------------------|------|-------------------|----------------------------------------|------------------|------------|

| $V_{DDA}$            | Supply voltage             |                         | 2.7  | _                 | 3                                      | V                |            |

| I <sub>DDA_ADC</sub> | Supply current per ADC     |                         | _    | 0.6               | _                                      | mA               | 3          |

| SMPLTS               | Sample Time                |                         | 275  | -                 | Refer to<br>the<br>Reference<br>Manual | ns               |            |

| TUE <sup>4</sup>     | Total unadjusted error     |                         | _    | ±4                | ±8                                     | LSB <sup>5</sup> | 6, 7, 8, 9 |

| DNL                  | Differential non-linearity |                         | _    | ±1.0              | _                                      | LSB <sup>5</sup> | 6, 7, 8, 9 |

| INL                  | Integral non-linearity     |                         | _    | ±2.0              | _                                      | LSB <sup>5</sup> | 6, 7, 8, 9 |

- 1. All accuracy numbers assume the ADC is calibrated with V<sub>REFH</sub>=V<sub>DDA</sub>=V<sub>DD</sub>, with the calibration frequency set to less than or equal to half of the maximum specified ADC clock frequency.

- 2. Typical values assume  $V_{DDA}$  = 3 V, Temp = 25 °C,  $f_{ADCK}$  = 40 MHz,  $R_{AS}$ =20  $\Omega$ , and  $C_{AS}$ =10 nF.

- 3. The ADC supply current depends on the ADC conversion rate.

- 4. Represents total static error, which includes offset and full scale error.

- 5.  $1 LSB = (V_{REFH} V_{REFL})/2^N$

- 6. The specifications are with averaging and in standalone mode only. Performance may degrade depending upon device use case scenario. When using ADC averaging, refer to the *Reference Manual* to determine the most appropriate settings for AVGS.

- 7. For ADC signals adjacent to V<sub>DD</sub>/V<sub>SS</sub> or XTAL/EXTAL or high frequency switching pins, some degradation in the ADC performance may be observed.

- 8. All values guarantee the performance of the ADC for multiple ADC input channel pins. When using ADC to monitor the internal analog parameters, assume minor degradation.

- 9. All the parameters in the table are given assuming system clock as the clocking source for ADC.

## 6.4.2 CMP with 8-bit DAC electrical specifications

Table 31. Comparator with 8-bit DAC electrical specifications

| Symbol             | Description                                          | Min. | Тур.                 | Max.      | Unit |

|--------------------|------------------------------------------------------|------|----------------------|-----------|------|

| I <sub>DDHS</sub>  | Supply current, High-speed mode <sup>1</sup>         |      |                      |           | μA   |

|                    | -40 - 125 ℃                                          | _    | 230                  | 300       |      |

| I <sub>DDLS</sub>  | Supply current, Low-speed mode <sup>1</sup>          |      |                      |           | μΑ   |

|                    | -40 - 105 ℃                                          | _    | 6                    | 11        |      |

|                    | -40 - 125 °C                                         |      | 6                    | 13        |      |

| V <sub>AIN</sub>   | Analog input voltage                                 | 0    | 0 - V <sub>DDA</sub> | $V_{DDA}$ | V    |

| V <sub>AIO</sub>   | Analog input offset voltage, High-speed mode         |      | -                    |           | mV   |

|                    | -40 - 125 °C                                         | -25  | ±1                   | 25        |      |

| V <sub>AIO</sub>   | Analog input offset voltage, Low-speed mode          |      |                      |           | mV   |

|                    | -40 - 125 °C                                         | -40  | ±4                   | 40        |      |

| t <sub>DHSB</sub>  | Propagation delay, High-speed mode <sup>2</sup>      |      |                      |           | ns   |

|                    | -40 - 105 °C                                         | _    | 35                   | 200       |      |

|                    | -40 - 125 °C                                         |      | 35                   | 300       |      |

| t <sub>DLSB</sub>  | Propagation delay, Low-speed mode <sup>2</sup>       |      | 1                    |           | μs   |

|                    | -40 - 105 °C                                         | _    | 0.5                  | 2         |      |

|                    | -40 - 125 ℃                                          | _    | 0.5                  | 3         |      |

| t <sub>DHSS</sub>  | Propagation delay, High-speed mode <sup>3</sup>      |      |                      |           | ns   |

|                    | -40 - 105 °C                                         | _    | 70                   | 400       |      |

|                    | -40 - 125 ℃                                          | _    | 70                   | 500       |      |

| t <sub>DLSS</sub>  | Propagation delay, Low-speed mode <sup>3</sup>       |      |                      |           | μs   |

|                    | -40 - 105 °C                                         | _    | 1                    | 5         |      |

|                    | -40 - 125 ℃                                          | _    | 1                    | 5         |      |

| t <sub>IDHS</sub>  | Initialization delay, High-speed mode <sup>4</sup>   |      |                      |           | μs   |

|                    | -40 - 125 ℃                                          | _    | 1.5                  | 3         |      |

| t <sub>IDLS</sub>  | Initialization delay, Low-speed mode <sup>4</sup>    |      |                      |           | μs   |

|                    | -40 - 125 °C                                         | _    | 10                   | 30        |      |

| V <sub>HYST0</sub> | Analog comparator hysteresis, Hyst0                  |      | 1                    |           | mV   |

|                    | -40 - 125 ℃                                          | _    | 0                    | _         |      |

| V <sub>HYST1</sub> | Analog comparator hysteresis, Hyst1, High-speed mode |      | -                    |           | mV   |

|                    | -40 - 125 ℃                                          | _    | 19                   | 66        |      |

|                    | Analog comparator hysteresis, Hyst1, Low-speed mode  |      | -                    |           |      |

|                    | -40 - 125 °C                                         | _    | 15                   | 40        |      |

| V <sub>HYST2</sub> | Analog comparator hysteresis, Hyst2, High-speed mode |      |                      |           | mV   |

|                    | -40 - 125 ℃                                          | _    | 34                   | 133       |      |

Table continues on the next page...

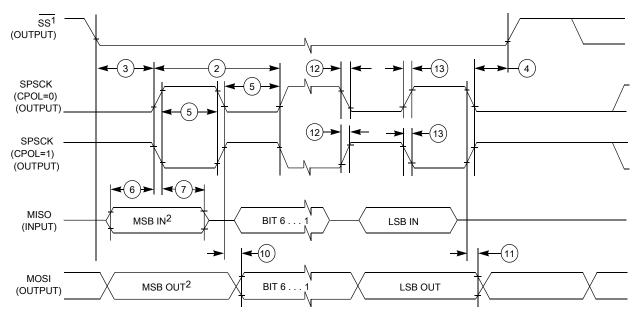

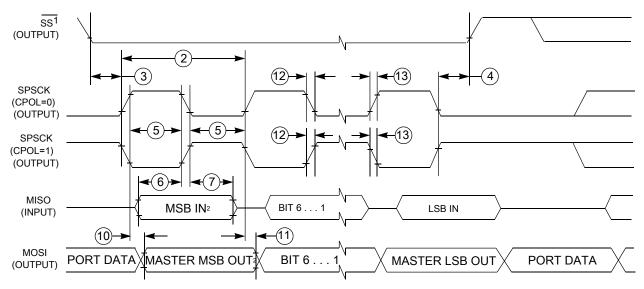

- 1. If configured as an output.

- 2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

Figure 18. LPSPI master mode timing (CPHA = 0)

- 1.If configured as output

- 2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

Figure 19. LPSPI master mode timing (CPHA = 1)

Table 38. SWD electrical specifications

| Symbol | Description                                     |          | Run      | Mode     |          |          | HSRU     | N Mode   |          |          | VLPR     | Mode     |          | Unit |

|--------|-------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|------|

|        |                                                 | 5.0      | V IO     | 3.3 \    | / IO     | 5.0      | V IO     | 3.3      | V IO     | 5.0      | V IO     | 3.3      | V IO     |      |

|        |                                                 | Min.     | Max.     | ľ    |

| S1     | SWD_CLK frequency of operation                  | -        | 25       | -        | 25       | -        | 25       | -        | 25       | -        | 10       | -        | 10       | MHz  |

| S2     | SWD_CLK cycle period                            | 1/S1     | -        | ns   |

| S3     | SWD_CLK clock pulse width                       | S2/2 - 5 | S2/2 + 5 | ns   |

| S4     | SWD_CLK rise and fall times                     | -        | 1        | -        | 1        | -        | 1        | -        | 1        | -        | 1        | -        | 1        | ns   |

| S9     | SWD_DIO input data setup time to SWD_CLK rise   | 4        | -        | 4        | -        | 4        | -        | 4        | -        | 16       | -        | 16       | -        | ns   |

| S10    | SWD_DIO input data hold time after SWD_CLK rise | 3        | -        | 3        | -        | 3        | -        | 3        | -        | 10       | -        | 10       | -        | ns   |

| S11    | SWD_CLK high to SWD_DIO data valid              | -        | 28       | -        | 38       | -        | 28       | -        | 38       | -        | 70       | -        | 77       | ns   |

| S12    | SWD_CLK high to SWD_DIO high-Z                  | -        | 28       | -        | 38       | -        | 28       | -        | 38       | -        | 70       | -        | 77       | ns   |

| S13    | SWD_CLK high to SWD_DIO data invalid            | 0        | -        | 0        | -        | 0        | -        | 0        | -        | 0        | -        | 0        | -        | ns   |

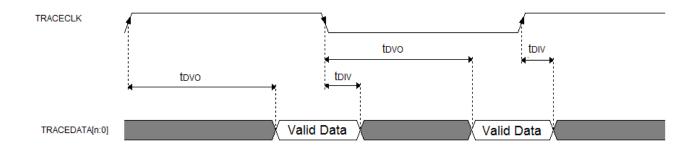

Table 39. Trace specifications (continued)

|                    | Symbol             | Symbol Description  |       | UN Mode | •  | HSRUI  | N Mode | VLPR<br>Mode | Unit |

|--------------------|--------------------|---------------------|-------|---------|----|--------|--------|--------------|------|

|                    | f <sub>TRACE</sub> | Max Trace frequency | 80    | 48      | 40 | 74.667 | 80     | 4            | MHz  |

| ads                | t <sub>DVO</sub>   | Data Output Valid   | 4     | 4       | 4  | 4      | 4      | 20           | ns   |

| Trace on fast pads | t <sub>DIV</sub>   | Data Output Invalid | -2    | -2      | -2 | -2     | -2     | -10          | ns   |

|                    | f <sub>TRACE</sub> | Max Trace frequency | 22.86 | 24      | 20 | 22.4   | 22.86  | 4            | MHz  |

| spg                | t <sub>DVO</sub>   | Data Output Valid   | 8     | 8       | 8  | 8      | 8      | 20           | ns   |

| Trace on slow pads | t <sub>DIV</sub>   | Data Output Invalid | -4    | -4      | -4 | -4     | -4     | -10          | ns   |

Figure 31. TRACE CLKOUT specifications

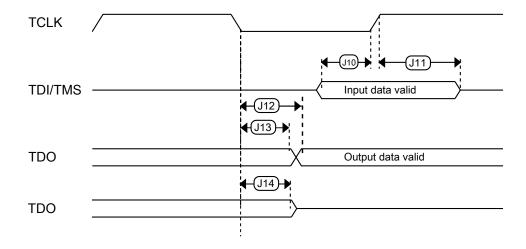

# 6.6.3 JTAG electrical specifications

Figure 34. Test Access Port timing

### 7 Thermal attributes

# 7.1 Description

The tables in the following sections describe the thermal characteristics of the device.

#### **NOTE**

Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting side (board) temperature, ambient temperature, air flow, power dissipation or other components on the board, and board thermal resistance.

### 7.2 Thermal characteristics

### Table 42. Thermal characteristics for the 100 MAPBGA package

| Rating                                                                          | Conditions              | Symbol           |         | Values  |         |      |  |  |

|---------------------------------------------------------------------------------|-------------------------|------------------|---------|---------|---------|------|--|--|

|                                                                                 |                         |                  | S32K146 | S32K144 | S32K148 | 1    |  |  |

| Thermal resistance, Junction to Ambient (Natural Convection) <sup>1, 2</sup>    | Single layer board (1s) | $R_{	hetaJA}$    | 57.2    | 61.0    | 52.5    | °C/W |  |  |

| Thermal resistance, Junction to Ambient (Natural Convection) <sup>1, 2, 3</sup> | Four layer board (2s2p) | $R_{	hetaJA}$    | 32.1    | 35.6    | 27.5    | °C/W |  |  |

| Thermal resistance, Junction to Ambient (@200 ft/min) 1,2,3                     | Single layer board (1s) | $R_{\theta JMA}$ | 44.1    | 46.6    | 39.0    | °C/W |  |  |

| Thermal resistance, Junction to Ambient (@200 ft/min) <sup>1, 3</sup>           | Two layer board (2s2p)  | $R_{	heta JMA}$  | 27.2    | 30.9    | 22.8    | °C/W |  |  |

| Thermal resistance, Junction to Board <sup>4</sup>                              | _                       | $R_{\theta JB}$  | 15.3    | 18.9    | 11.2    | °C/W |  |  |

| Thermal resistance, Junction to Case <sup>5</sup>                               | _                       | $R_{	heta JC}$   | 10.2    | 14.2    | 7.5     | °C/W |  |  |

| Thermal resistance, Junction to Package Top outside center <sup>6</sup>         | _                       | Ψлт              | 0.2     | 0.4     | 0.2     | °C/W |  |  |

| Thermal resistance, Junction to Package Bottom outside center <sup>7</sup>      | _                       | ΨЈВ              | 12.2    | 15.9    | 18.3    | °C/W |  |  |

- Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- Per SEMI G38-87 and JEDEC JESD51-2 with the single layer board horizontal.

- Per JEDEC JESD51-6 with the board horizontal.

- Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

- 7. Thermal characterization parameter indicating the temperature difference between package bottom center and the junction temperature per JEDEC JESD51-12. When Greek letters are not available, the thermal characterization parameter is written as Psi-JB.

75

## 9 Pinouts

## 9.1 Package pinouts and signal descriptions

For package pinouts and signal descriptions, refer to the Reference Manual.

# 10 Revision History

The following table provides a revision history for this document.

**Table 43. Revision History**

| Rev. No. | Date          | Substantial Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | 12 Aug 2016   | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2        | 03 March 2017 | Updated descpition of QSPI and Clock interfaces in Key Features section Updated figure: High-level architecture diagram for the S32K1xx family Updated figure: S32K1xx product series comparison Added note in section Selecting orderable part number Updated figure: Ordering information In table: Absolute maximum ratings: Added footnote to I <sub>INJPAD_DC</sub> Updated min and max value of I <sub>INJPAD_DC</sub> Updated description, max and min values for I <sub>INJSUM</sub> Updated V <sub>IN_TRANSIENT</sub> In table: Voltage and current operating requirements: Renamed V <sub>SUP_OFF</sub> Updated max value of V <sub>DD_OFF</sub> Removed V <sub>INA</sub> and V <sub>IN</sub> Added V <sub>REFH</sub> and V <sub>REFL</sub> Updated footnote "Typical conditions assumes V <sub>DD</sub> = V <sub>DDA</sub> = V <sub>REFH</sub> = 5 V Removed I <sub>NJSUM_AF</sub> Updated footnotes in table Table 4 Updated section Power mode transition operating behaviors In table: Power consumption Added footnote "With PMC_REGSC[CLKBIASDIS] " Updated conditions for VLPR Removed Idd/MHz for S32K144 Updated numbers for S32K142 and S32K148 Removed lase case footnotes In section Modes configuration: Replaced table "Modes configuration" with spreadsheet attachment: 'S32K1xx_Power_Modes_Master_configuration_sheet' In table: DC electrical specifications at 3.3 V Range: Added footnote to High drive port pins In table: DC electrical specifications at 5.0 V Range: |

Table continues on the next page...