Welcome to E-XFL.COM

#### Understanding <u>Embedded - CPLDs (Complex</u> <u>Programmable Logic Devices)</u>

Embedded - CPLDs, or Complex Programmable Logic Devices, are highly versatile digital logic devices used in electronic systems. These programmable components are designed to perform complex logical operations and can be customized for specific applications. Unlike fixedfunction ICs, CPLDs offer the flexibility to reprogram their configuration, making them an ideal choice for various embedded systems. They consist of a set of logic gates and programmable interconnects, allowing designers to implement complex logic circuits without needing custom hardware.

#### **Applications of Embedded - CPLDs**

#### Details

| Product Status                  | Obsolete                                                                    |

|---------------------------------|-----------------------------------------------------------------------------|

| Programmable Type               | In-System Reprogrammable™ (ISR™) CMOS                                       |

| Delay Time tpd(1) Max           | 10 ns                                                                       |

| Voltage Supply - Internal       | 4.75V ~ 5.25V                                                               |

| Number of Logic Elements/Blocks | -                                                                           |

| Number of Macrocells            | 32                                                                          |

| Number of Gates                 | -                                                                           |

| Number of I/O                   | 37                                                                          |

| Operating Temperature           | 0°C ~ 70°C (TA)                                                             |

| Mounting Type                   | Surface Mount                                                               |

| Package / Case                  | 44-LQFP                                                                     |

| Supplier Device Package         | 44-TQFP (10x10)                                                             |

| Purchase URL                    | https://www.e-xfl.com/product-detail/infineon-technologies/cy37032p44-125ac |

|                                 |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Selection Guide**

## 5.0V Selection Guide

#### General Information

| Device  | Macrocells | Dedicated Inputs | I/O Pins    | Speed (t <sub>PD</sub> ) | Speed (f <sub>MAX</sub> ) |

|---------|------------|------------------|-------------|--------------------------|---------------------------|

| CY37032 | 32         | 5                | 32          | 6                        | 200                       |

| CY37064 | 64         | 5                | 32/64       | 6                        | 200                       |

| CY37128 | 128        | 5                | 64/128      | 6.5                      | 167                       |

| CY37192 | 192        | 5                | 120         | 7.5                      | 154                       |

| CY37256 | 256        | 5                | 128/160/192 | 7.5                      | 154                       |

| CY37384 | 384        | 5                | 160/192     | 10                       | 118                       |

| CY37512 | 512        | 5                | 160/192/264 | 10                       | 118                       |

### Speed Bins

| Device  | 200 | 167 | 154 | 143 | 125 | 100 | 83 | 66 |

|---------|-----|-----|-----|-----|-----|-----|----|----|

| CY37032 | Х   |     | Х   |     | Х   |     |    |    |

| CY37064 | Х   |     | Х   |     | Х   |     |    |    |

| CY37128 |     | Х   |     |     | Х   | Х   |    |    |

| CY37192 |     |     | Х   |     | Х   |     | Х  |    |

| CY37256 |     |     | Х   |     | Х   |     | Х  |    |

| CY37384 |     |     |     |     | Х   |     | Х  |    |

| CY37512 |     |     |     |     | Х   | X   | Х  |    |

### Device-Package Offering and I/O Count

| Device  | 44-<br>Lead<br>TQFP | 44-<br>Lead<br>PLCC | 44-<br>Lead<br>CLCC | 84-<br>Lead<br>PLCC | 84-<br>Lead<br>CLCC | 100-<br>Lead<br>TQFP | 160-<br>Lead<br>TQFP | 160-<br>Lead<br>CQFP | 208-<br>Lead<br>PQFP | 208-<br>Lead<br>CQFP | 292-<br>Lead<br>PBGA | 388-<br>Lead<br>PBGA |

|---------|---------------------|---------------------|---------------------|---------------------|---------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| CY37032 | 37                  | 37                  |                     |                     |                     |                      |                      |                      |                      |                      |                      |                      |

| CY37064 | 37                  | 37                  | 37                  | 69                  |                     | 69                   |                      |                      |                      |                      |                      |                      |

| CY37128 |                     |                     |                     | 69                  | 69                  | 69                   | 133                  |                      |                      |                      |                      |                      |

| CY37192 |                     |                     |                     |                     |                     |                      | 125                  |                      |                      |                      |                      |                      |

| CY37256 |                     |                     |                     |                     |                     |                      | 133                  | 133                  | 165                  |                      | 197                  |                      |

| CY37384 |                     |                     |                     |                     |                     |                      |                      |                      | 165                  |                      | 197                  |                      |

| CY37512 |                     |                     |                     |                     |                     |                      |                      |                      | 165                  | 165                  | 197                  | 269                  |

#### 3.3V Selection Guide

General Information

| Device   | Macrocells | Dedicated Inputs | I/O Pins    | Speed (t <sub>PD</sub> ) | Speed (f <sub>MAX</sub> ) |

|----------|------------|------------------|-------------|--------------------------|---------------------------|

| CY37032V | 32         | 5                | 32          | 8.5                      | 143                       |

| CY37064V | 64         | 5                | 32/64       | 8.5                      | 143                       |

| CY37128V | 128        | 5                | 64/80/128   | 10                       | 125                       |

| CY37192V | 192        | 5                | 120         | 12                       | 100                       |

| CY37256V | 256        | 5                | 128/160/192 | 12                       | 100                       |

| CY37384V | 384        | 5                | 160/192     | 15                       | 83                        |

| CY37512V | 512        | 5                | 160/192/264 | 15                       | 83                        |

Speed Bins

| Device   | 200 | 167 | 154 | 143 | 125 | 100 | 83 | 66 |

|----------|-----|-----|-----|-----|-----|-----|----|----|

| CY37032V |     |     |     | Х   |     | Х   |    |    |

| CY37064V |     |     |     | Х   |     | Х   |    |    |

| CY37128V |     |     |     |     | Х   |     | Х  |    |

| CY37192V |     |     |     |     |     | Х   |    | Х  |

| CY37256V |     |     |     |     |     | Х   |    | Х  |

| CY37384V |     |     |     |     |     |     | Х  | Х  |

| CY37512V |     |     |     |     |     |     | Х  | Х  |

Device-Package Offering and I/O Count

**YPRESS**

| Device   | 44-<br>Lead<br>TQFP | 44-<br>Lead<br>CLCC | 48-<br>Lead<br>FBGA | 84-<br>Lead<br>CLCC | 100-<br>Lead<br>TQFP | 100-<br>Lead<br>FBGA | 160-<br>Lead<br>TQFP | 160-<br>Lead<br>CQFP | 208-<br>Lead<br>PQFP | 208-<br>Lead<br>CQFP | 292-<br>Lead<br>PBGA | 256-<br>Lead<br>FBGA | 388-<br>Lead<br>PBGA | 400-<br>Lead<br>FBGA |

|----------|---------------------|---------------------|---------------------|---------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| CY37032V | 37                  |                     | 37                  |                     |                      |                      |                      |                      |                      |                      |                      |                      |                      |                      |

| CY37064V | 37                  | 37                  | 37                  |                     | 69                   | 69                   |                      |                      |                      |                      |                      |                      |                      |                      |

| CY37128V |                     |                     |                     | 69                  | 69                   | 85                   | 133                  |                      |                      |                      |                      |                      |                      |                      |

| CY37192V |                     |                     |                     |                     |                      |                      | 125                  |                      |                      |                      |                      |                      |                      |                      |

| CY37256V |                     |                     |                     |                     |                      |                      | 133                  | 133                  | 165                  |                      | 197                  | 197                  |                      |                      |

| CY37384V |                     |                     |                     |                     |                      |                      |                      |                      | 165                  |                      | 197                  |                      |                      |                      |

| CY37512V |                     |                     |                     |                     |                      |                      |                      |                      | 165                  | 165                  | 197                  |                      | 269                  | 269                  |

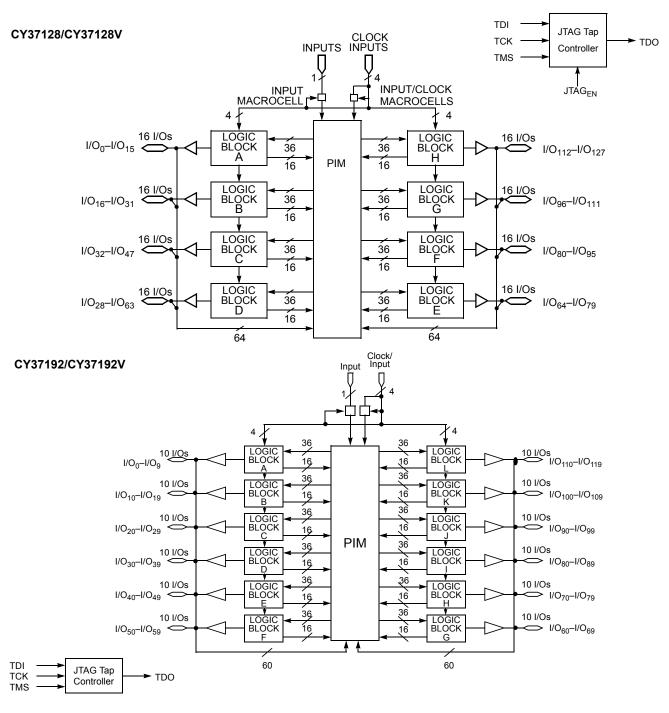

### Architecture Overview of Ultra37000 Family

#### Programmable Interconnect Matrix

The PIM consists of a completely global routing matrix for signals from I/O pins and feedbacks from the logic blocks. The PIM provides extremely robust interconnection to avoid fitting and density limitations.

The inputs to the PIM consist of all I/O and dedicated input pins and all macrocell feedbacks from within the logic blocks. The number of PIM inputs increases with pin count and the number of logic blocks. The outputs from the PIM are signals routed to the appropriate logic blocks. Each logic block receives 36 inputs from the PIM and their complements, allowing for 32-bit operations to be implemented in a single pass through the device. The wide number of inputs to the logic block also improves the routing capacity of the Ultra37000 family.

An important feature of the PIM is its simple timing. The propagation delay through the PIM is accounted for in the timing specifications for each device. There is no additional delay for traveling through the PIM. In fact, all inputs travel through the PIM. As a result, there are no route-dependent timing parameters on the Ultra37000 devices. The worst-case PIM delays are incorporated in all appropriate Ultra37000 specifications.

Routing signals through the PIM is completely invisible to the user. All routing is accomplished by software—no hand routing is necessary. *Warp*<sup>®</sup> and third-party development packages automatically route designs for the Ultra37000 family in a matter of minutes. Finally, the rich routing resources of the Ultra37000 family accommodate last minute logic changes while maintaining fixed pin assignments.

#### Logic Block

The logic block is the basic building block of the Ultra37000 architecture. It consists of a product term array, an intelligent product-term allocator, 16 macrocells, and a number of I/O cells. The number of I/O cells varies depending on the device used. Refer to *Figure 1* for the block diagram.

#### Product Term Array

Each logic block features a 72 x 87 programmable product term array. This array accepts 36 inputs from the PIM, which originate from macrocell feedbacks and device pins. Active LOW and active HIGH versions of each of these inputs are generated to create the full 72-input field. The 87 product terms in the array can be created from any of the 72 inputs.

Of the 87 product terms, 80 are for general-purpose use for the 16 macrocells in the logic block. Four of the remaining seven product terms in the logic block are output enable (OE) product terms. Each of the OE product terms controls up to eight of the 16 macrocells and is selectable on an individual macrocell basis. In other words, each I/O cell can select between one of two OE product terms to control the output buffer. The first two of these four OE product terms are available to the upper half of the I/O macrocells in a logic block. The other two OE product terms are available to the lower half of the I/O macrocells in a logic block.

The next two product terms in each logic block are dedicated asynchronous set and asynchronous reset product terms. The final product term is the product term clock. The set, reset, OE and product term clock have polarity control to realize OR functions in a single pass through the array.

The buried macrocell also supports input register capability. The buried macrocell can be configured to act as an input register (D-type or latch) whose input comes from the I/O pin associated with the neighboring macrocell. The output of all buried macrocells is sent directly to the PIM regardless of its configuration.

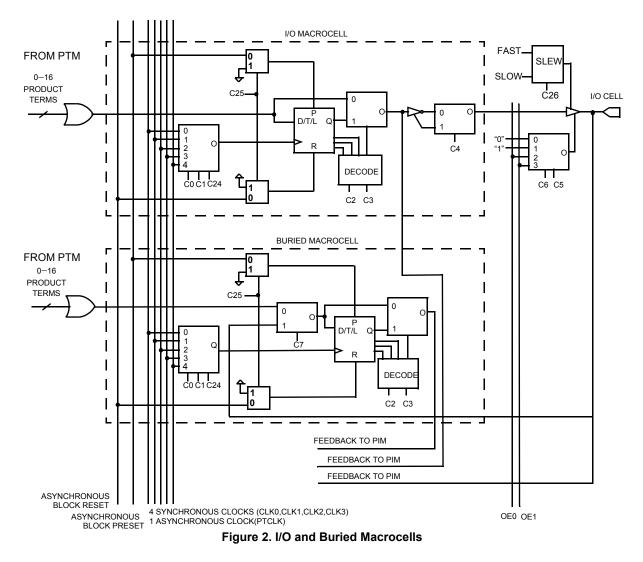

#### I/O Macrocell

*Figure 2* illustrates the architecture of the I/O macrocell. The I/O macrocell supports the same functions as the buried macrocell with the addition of I/O capability. At the output of the macrocell, a polarity control mux is available to select active LOW or active HIGH signals. This has the added advantage of allowing significant logic reduction to occur in many applications.

The Ultra37000 macrocell features a feedback path to the PIM separate from the I/O pin input path. This means that if the macrocell is buried (fed back internally only), the associated I/O pin can still be used as an input.

#### Bus Hold Capabilities on all I/Os

Bus-hold, which is an improved version of the popular internal pull-up resistor, is a weak latch connected to the pin that does not degrade the device's performance. As a latch, bus-hold maintains the last state of a pin when the pin is placed in a high-impedance state, thus reducing system noise in bus-interface applications. Bus-hold additionally allows unused device pins to remain unconnected on the board, which is particularly useful during prototyping as designers can route new signals to the device without cutting trace connections to  $V_{CC}$  or GND. For more information, see the application note Understanding Bus-Hold—A Feature of Cypress CPLDs.

#### Programmable Slew Rate Control

Each output has a programmable configuration bit, which sets the output slew rate to fast or slow. For designs concerned with meeting FCC emissions standards the slow edge provides for lower system noise. For designs requiring very high performance the fast edge rate provides maximum system performance.

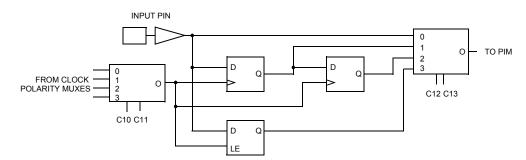

Figure 3. Input Macrocell

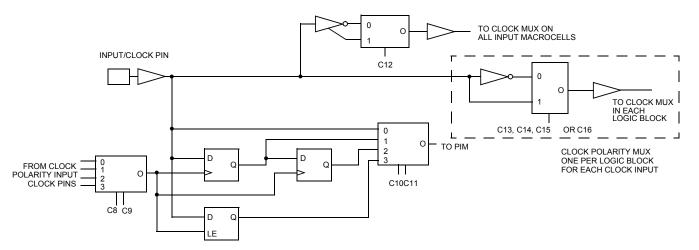

#### Figure 4. Input/Clock Macrocell

#### Clocking

Each I/O and buried macrocell has access to four synchronous clocks (CLK0, CLK1, CLK2 and CLK3) as well as an asynchronous product term clock PTCLK. Each input macrocell has access to all four synchronous clocks.

#### Dedicated Inputs/Clocks

Five pins on each member of the Ultra37000 family are designated as input-only. There are two types of dedicated inputs on Ultra37000 devices: input pins and input/clock pins. *Figure 3* illustrates the architecture for input pins. Four input options are available for the user: combinatorial, registered, double-registered, or latched. If a registered or latched option is selected, any one of the input clocks can be selected for control.

*Figure 4* illustrates the architecture for the input/clock pins. Like the input pins, input/clock pins can be combinatorial, registered, double-registered, or latched. In addition, these pins feed the clocking structures throughout the device. The clock path at the input has user-configurable polarity.

#### Product Term Clocking

In addition to the four synchronous clocks, the Ultra37000 family also has a product term clock for asynchronous clocking. Each logic block has an independent product term clock which is available to all 16 macrocells. Each product term clock also supports user configurable polarity selection.

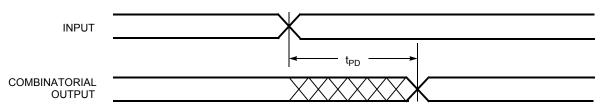

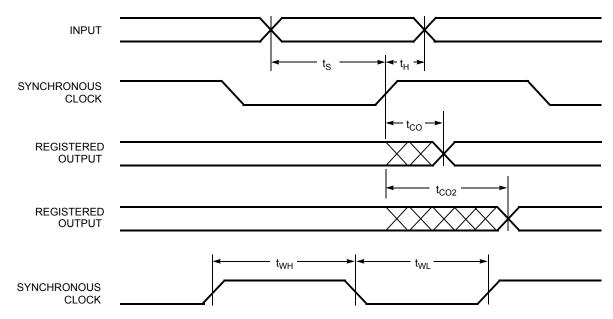

#### **Timing Model**

One of the most important features of the Ultra37000 family is the simplicity of its timing. All delays are worst case and system performance is unaffected by the features used. *Figure 5* illustrates the true timing model for the 167-MHz devices in high speed mode. For combinatorial paths, any input to any output incurs a 6.5-ns worst-case delay regardless of the amount of logic used. For synchronous systems, the input set-up time to the output macrocells for any input is 3.5 ns and the clock to output time is also 4.0 ns. These measurements are for any output and synchronous clock, regardless of the logic used.

The Ultra37000 features:

- · No fanout delays

- No expander delays

- No dedicated vs. I/O pin delays

- · No additional delay through PIM

- No penalty for using 0–16 product terms

- · No added delay for steering product terms

- · No added delay for sharing product terms

- No routing delays

- No output bypass delays

The simple timing model of the Ultra37000 family eliminates unexpected performance penalties.

The third programming option for Ultra37000 devices is to utilize the embedded controller or processor that already exists in the system. The Ultra37000 ISR software assists in this method by converting the device JEDEC maps into the ISR serial stream that contains the ISR instruction information and the addresses and data of locations to be programmed. The embedded controller then simply directs this ISR stream to the chain of Ultra37000 devices to complete the desired reconfiguring or diagnostic operations. Contact your local sales office for information on availability of this option. The fourth method for programming Ultra37000 devices is to use the same programmer that is currently being used to program FLASH370i devices.

For all pinout, electrical, and timing requirements, refer to device data sheets. For ISR cable and software specifications, refer to the UltraISR kit data sheet (CY3700i).

#### **Third-Party Programmers**

As with development software, Cypress support is available on a wide variety of third-party programmers. All major third-party programmers (including BP Micro, Data I/O, and SMS) support the Ultra37000 family.

## Logic Block Diagrams (continued)

### Inductance<sup>[5]</sup>

|   | Parameter | Description               | Test Conditions                        |   |   | 44-Lead<br>CLCC |   |   |   | 160-Lead<br>TQFP |    | Unit |

|---|-----------|---------------------------|----------------------------------------|---|---|-----------------|---|---|---|------------------|----|------|

| Ī |           | Maximum Pin<br>Inductance | V <sub>IN</sub> = 5.0V<br>at f = 1 MHz | 2 | 5 | 2               | 8 | 5 | 8 | 9                | 11 | nH   |

### Capacitance<sup>[5]</sup>

| Parameter        | Description                       | Test Conditions                                              | Max. | Unit |

|------------------|-----------------------------------|--------------------------------------------------------------|------|------|

| C <sub>I/O</sub> | Input/Output Capacitance          | V <sub>IN</sub> = 5.0V at f = 1 MHz at T <sub>A</sub> = 25°C | 10   | pF   |

| C <sub>CLK</sub> | Clock Signal Capacitance          | V <sub>IN</sub> = 5.0V at f = 1 MHz at T <sub>A</sub> = 25°C | 12   | pF   |

| C <sub>DP</sub>  | Dual-Function Pins <sup>[9]</sup> | V <sub>IN</sub> = 5.0V at f = 1 MHz at T <sub>A</sub> = 25°C | 16   | pF   |

### Endurance Characteristics<sup>[5]</sup>

| Parameter | Description                  | Test Conditions                              | Min.  | Тур.   | Unit   |

|-----------|------------------------------|----------------------------------------------|-------|--------|--------|

| Ν         | Minimum Reprogramming Cycles | Normal Programming Conditions <sup>[2]</sup> | 1,000 | 10,000 | Cycles |

### **3.3V Device Characteristics Maximum Ratings**

| (Above which the useful life may be impaired. For user guide-lines, not tested.) |

|----------------------------------------------------------------------------------|

| Storage Temperature65°C to +150°C                                                |

| Ambient Temperature with<br>Power Applied55°C to +125°C                          |

| Supply Voltage to Ground Potential0.5V to +4.6V                                  |

## DC Voltage Applied to Outputs in High-Z State .....-0.5V to +7.0V DC Input Voltage .....-0.5V to +7.0V Current into Outputs ...... 8 mA Static Discharge Voltage.....> 2001V (per MIL-STD-883, Method 3015) Latch-up Current.....> 200 mA

### **Operating Range**<sup>[2]</sup>

| Range                   | Ambient Temperature <sup>[2]</sup> | Junction Temperature | <b>V<sub>CC</sub></b> <sup>[10]</sup> |

|-------------------------|------------------------------------|----------------------|---------------------------------------|

| Commercial              | 0°C to +70°C                       | 0°C to +90°C         | 3.3V ± 0.3V                           |

| Industrial              | –40°C to +85°C                     | –40°C to +105°C      | 3.3V ± 0.3V                           |

| Military <sup>[3]</sup> | –55°C to +125°C                    | –55°C to +130°C      | 3.3V ± 0.3V                           |

### 3.3V Device Electrical Characteristics Over the Operating Range

| Parameter         | Description                                    | Test Conditions                                                                                  | Min. | Max. | Unit |

|-------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------|------|------|------|

| V <sub>OH</sub>   | Output HIGH Voltage                            | $V_{CC} = Min.$ $I_{OH} = -4 \text{ mA } (Com'I)^{[4]}$<br>$I_{OH} = -3 \text{ mA } (Mil)^{[4]}$ | 2.4  |      | V    |

| V <sub>OL</sub>   | Output LOW Voltage                             | $V_{CC} = Min.$ $I_{OL} = 8 \text{ mA } (Com'I)^{[4]}$<br>$I_{OL} = 6 \text{ mA } (MiI)^{[4]}$   | -    | 0.5  | V    |

| V <sub>IH</sub>   | Input HIGH Voltage                             | Guaranteed Input Logical HIGH Voltage for all Inputs <sup>[7]</sup>                              | 2.0  | 5.5  | V    |

| V <sub>IL</sub>   | Input LOW Voltage                              | Guaranteed Input Logical LOW Voltage for<br>all Inputs <sup>[7]</sup>                            | -0.5 | 0.8  | V    |

| I <sub>IX</sub>   | Input Load Current                             | $V_{I}$ = GND OR $V_{CC}$ , Bus-Hold Disabled                                                    | -10  | 10   | μA   |

| I <sub>OZ</sub>   | Output Leakage Current                         | V <sub>O</sub> = GND or V <sub>CC</sub> , Output Disabled,<br>Bus-Hold Disabled                  | -50  | 50   | μA   |

| I <sub>OS</sub>   | Output Short Circuit Current <sup>[5, 8]</sup> | V <sub>CC</sub> = Max., V <sub>OUT</sub> = 0.5V                                                  | -30  | -160 | mA   |

| I <sub>BHL</sub>  | Input Bus-Hold LOW Sustaining Current          | V <sub>CC</sub> = Min., V <sub>IL</sub> = 0.8V                                                   | +75  |      | μA   |

| I <sub>BHH</sub>  | Input Bus-Hold HIGH Sustaining Current         | V <sub>CC</sub> = Min., V <sub>IH</sub> = 2.0V                                                   | -75  |      | μA   |

| I <sub>BHLO</sub> | Input Bus-Hold LOW Overdrive Current           | V <sub>CC</sub> = Max.                                                                           |      | +500 | μΑ   |

| I <sub>BHHO</sub> | Input Bus-Hold HIGH Overdrive Current          | V <sub>CC</sub> = Max.                                                                           |      | -500 | μΑ   |

Notes:

9. Dual pins are I/O with JTAG pins. 10. For CY37064VP100-143AC, CY37064VP100-143BBC, CY37064VP44-143AC, CY37064VP48-143BAC; Operating Range: V<sub>CC</sub> is 3.3V± 0.16V.

## Switching Characteristics Over the Operating Range (continued)<sup>[12]</sup>

| 200 MHz                                 |       | 167 MHz |      | 154 MHz |      | 143 MHz |      | 125 MHz |      | 100 MHz |      | 83 MHz |      | 66 MHz |      |      |      |

|-----------------------------------------|-------|---------|------|---------|------|---------|------|---------|------|---------|------|--------|------|--------|------|------|------|

| Parameter                               | Min.  | Max.    | Min. | Max.    | Min. | Max.    | Min. | Мах.    | Min. | Мах.    | Min. | Мах.   | Min. | Max.   | Min. | Max. | Unit |

| t <sub>RO</sub> <sup>[13, 14, 15]</sup> |       | 12      |      | 13      |      | 13      |      | 14      |      | 15      |      | 18     |      | 21     |      | 26   | ns   |

| t <sub>PW</sub>                         | 8     |         | 8    |         | 8    |         | 8    |         | 10   |         | 12   |        | 15   |        | 20   |      | ns   |

| t <sub>PR</sub> <sup>[13]</sup>         | 10    |         | 10   |         | 10   |         | 10   |         | 12   |         | 14   |        | 17   |        | 22   |      | ns   |

| t <sub>PO</sub> <sup>[13, 14, 15]</sup> |       | 12      |      | 13      |      | 13      |      | 14      |      | 15      |      | 18     |      | 21     |      | 26   | ns   |

| User Option P                           | aram  | eters   |      |         |      |         |      |         |      |         |      |        |      |        |      |      |      |

| t <sub>LP</sub>                         |       | 2.5     |      | 2.5     |      | 2.5     |      | 2.5     |      | 2.5     |      | 2.5    |      | 2.5    |      | 2.5  | ns   |

| t <sub>SLEW</sub>                       |       | 3       |      | 3       |      | 3       |      | 3       |      | 3       |      | 3      |      | 3      |      | 3    | ns   |

| t <sub>3.3IO</sub> <sup>[19]</sup>      |       | 0.3     |      | 0.3     |      | 0.3     |      | 0.3     |      | 0.3     |      | 0.3    |      | 0.3    |      | 0.3  | ns   |

| JTAG Timing F                           | Param | neters  | ;    |         |      |         |      |         |      |         |      |        |      |        |      |      |      |

| t <sub>S JTAG</sub>                     | 0     |         | 0    |         | 0    |         | 0    |         | 0    |         | 0    |        | 0    |        | 0    |      | ns   |

| t <sub>H JTAG</sub>                     | 20    |         | 20   |         | 20   |         | 20   |         | 20   |         | 20   |        | 20   |        | 20   |      | ns   |

| <sup>t</sup> CO JTAG                    |       | 20      |      | 20      |      | 20      |      | 20      |      | 20      |      | 20     |      | 20     |      | 20   | ns   |

| f <sub>JTAG</sub>                       |       | 20      |      | 20      |      | 20      |      | 20      |      | 20      |      | 20     |      | 20     |      | 20   | MHz  |

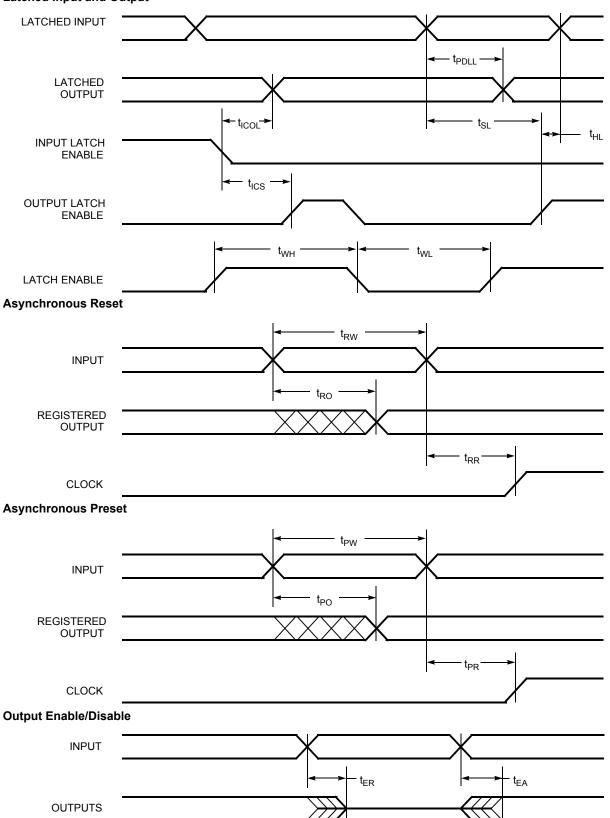

## **Switching Waveforms**

#### **Combinatorial Output**

### **Registered Output with Synchronous Clocking**

Note:

<sup>19.</sup> Only applicable to the 5V devices.

## Switching Waveforms (continued)

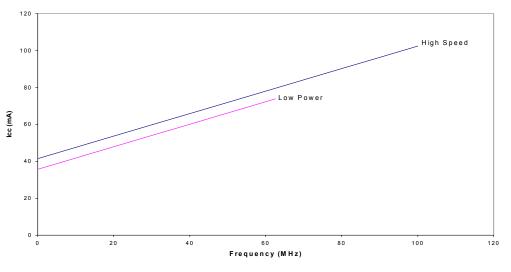

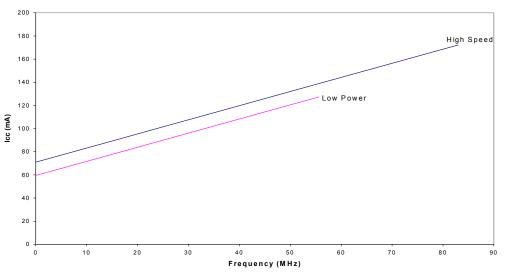

Typical 3.3V Power Consumption (continued) CY37192V

EAD-FRE

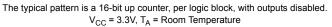

The typical pattern is a 16-bit up counter, per logic block, with outputs disabled.  $V_{CC}$  = 3.3V,  $T_{A}$  = Room Temperature

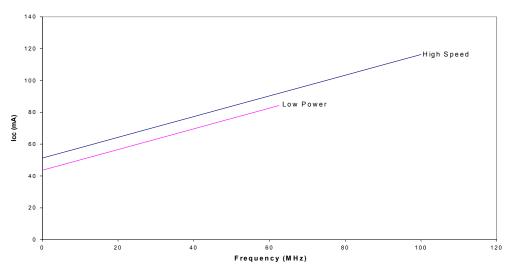

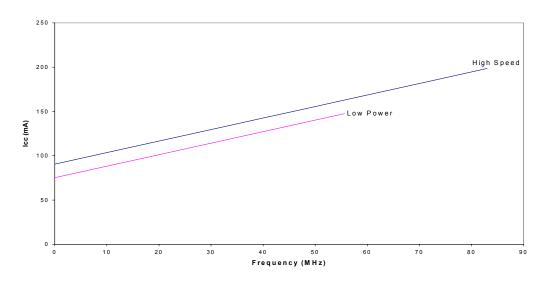

Typical 3.3V Power Consumption (continued) CY37384V

LEAD-FRE

The typical pattern is a 16-bit up counter, per logic block, with outputs disabled.  $V_{CC}$  = 3.3V,  $T_{A}$  = Room Temperature

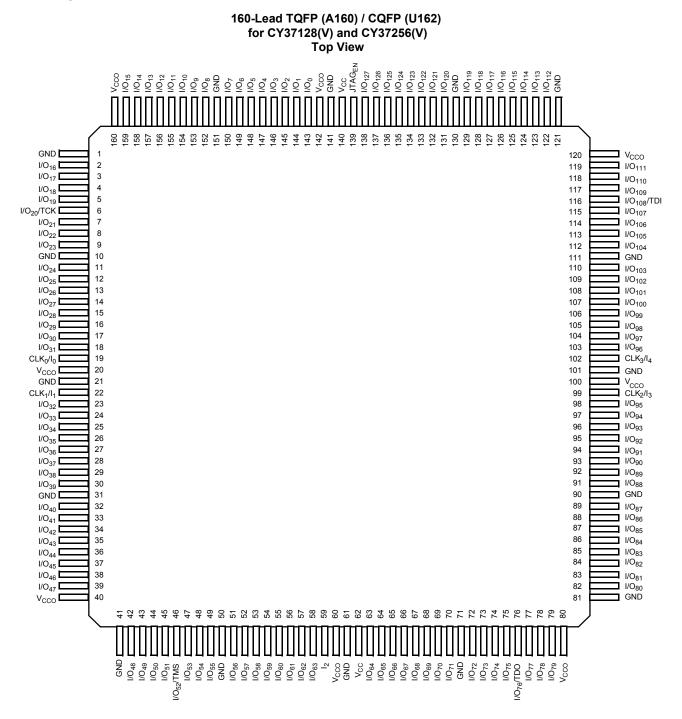

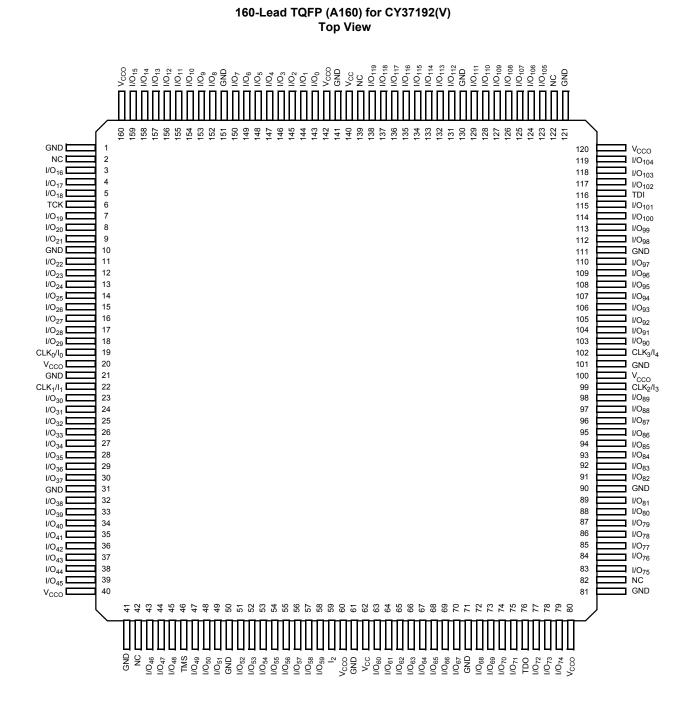

Pin Configurations<sup>[20]</sup> (continued)

Pin Configurations<sup>[20]</sup> (continued)

# Pin Configurations<sup>[20]</sup> (continued)

### 292-Ball PBGA (BG292) Top View

|   | 1                 | 2                                | 3                                | 4                 | 5                 | 6                 | 7                 | 8                 | 9                 | 10                 | 11                 | 12                 | 13                 | 14                 | 15                 | 16                 | 17                 | 18                               | 19                 | 20                 |   |

|---|-------------------|----------------------------------|----------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|----------------------------------|--------------------|--------------------|---|

| A | GND               | I/O <sub>21</sub>                | NC                               | I/O <sub>16</sub> | I/O <sub>12</sub> | I/O <sub>9</sub>  | I/O <sub>7</sub>  | I/O <sub>4</sub>  | I/O <sub>0</sub>  | I/O <sub>190</sub> | I/O <sub>189</sub> | I/O <sub>186</sub> | I/O <sub>182</sub> | NC                 | I/O <sub>178</sub> | I/O <sub>175</sub> | NC                 | NC                               | I/O <sub>169</sub> | I/O <sub>168</sub> | A |

| В | I/O <sub>23</sub> | I/O <sub>20</sub>                | I/O <sub>19</sub>                | I/O <sub>18</sub> | I/O <sub>15</sub> | I/O <sub>11</sub> | I/O <sub>8</sub>  | I/O <sub>5</sub>  | I/O <sub>1</sub>  | I/O <sub>191</sub> | I/O <sub>187</sub> | I/O <sub>185</sub> | I/O <sub>181</sub> | NC                 | NC                 | I/O <sub>174</sub> | I/O <sub>171</sub> | I/O <sub>170</sub>               | NC                 | I/O <sub>166</sub> | В |

| С | NC                | NC                               | I/O <sub>22</sub>                | NC                | I/O <sub>17</sub> | I/O <sub>14</sub> | I/O <sub>10</sub> | I/O <sub>6</sub>  | I/O <sub>2</sub>  | NC                 | I/O <sub>188</sub> | I/O <sub>184</sub> | I/O <sub>180</sub> | I/O <sub>179</sub> | I/O <sub>176</sub> | I/O <sub>173</sub> | I/O <sub>172</sub> | I/O <sub>167</sub>               | I/O <sub>165</sub> | I/O <sub>162</sub> | С |

| D | I/O <sub>24</sub> | NC                               | NC                               | GND               | NC                | V <sub>CCO</sub>  | I/O <sub>13</sub> | GND               | I/O <sub>3</sub>  | NC                 | V <sub>CC</sub>    | I/O <sub>183</sub> | GND                | I/O <sub>177</sub> | V <sub>CCO</sub>   | NC                 | GND                | I/O <sub>164</sub>               | TDI                | I/O <sub>160</sub> | D |

| Е | I/O <sub>27</sub> | I/O <sub>26</sub>                | I/O <sub>25</sub>                | NC                |                   |                   |                   |                   |                   |                    |                    |                    |                    |                    |                    |                    | I/O <sub>163</sub> | I/O <sub>161</sub>               | I/O <sub>159</sub> | I/O <sub>156</sub> | Е |

| F | I/O <sub>30</sub> | тск                              | I/O <sub>28</sub>                | V <sub>CCO</sub>  |                   |                   |                   |                   |                   |                    |                    |                    |                    |                    |                    |                    | V <sub>CCO</sub>   | I/O <sub>158</sub>               | NC                 | I/O <sub>154</sub> | F |

| G | I/O <sub>33</sub> | I/O <sub>32</sub>                | I/O <sub>31</sub>                | I/O <sub>29</sub> |                   |                   |                   |                   |                   |                    |                    |                    |                    |                    |                    |                    | I/O <sub>157</sub> | I/O <sub>155</sub>               | I/O <sub>153</sub> | I/O <sub>152</sub> | G |

| н | I/O <sub>35</sub> | NC                               | I/O <sub>34</sub>                | GND               |                   |                   |                   | GND               | GND               | GND                | GND                | GND                | GND                |                    |                    |                    | GND                | I/O <sub>151</sub>               | I/O <sub>150</sub> | I/O <sub>149</sub> | н |

| J | I/O <sub>39</sub> | I/O <sub>38</sub>                | I/O <sub>37</sub>                | I/O <sub>36</sub> |                   |                   |                   | GND               | GND               | GND                | GND                | GND                | GND                |                    |                    |                    | I/O <sub>148</sub> | I/O <sub>147</sub>               | I/O <sub>146</sub> | I/O <sub>145</sub> | J |

| к | I/O <sub>42</sub> | I/O <sub>40</sub>                | I/O <sub>41</sub>                | V <sub>CC</sub>   |                   |                   |                   | GND               | GND               | GND                | GND                | GND                | GND                |                    |                    |                    | I/O <sub>144</sub> | CLK <sub>3</sub> /I <sub>4</sub> | NC                 | NC                 | к |

| L | I/O <sub>43</sub> | I/O <sub>44</sub>                | I/O <sub>45</sub>                | I/O <sub>46</sub> |                   |                   |                   | GND               | GND               | GND                | GND                | GND                | GND                |                    |                    |                    | V <sub>CC</sub>    | CLK <sub>2</sub> /I <sub>3</sub> | I/O <sub>143</sub> | NC                 | L |

| М | I/O <sub>47</sub> | CLK <sub>0</sub> /I <sub>0</sub> | CLK <sub>1</sub> /I <sub>1</sub> | I/O <sub>48</sub> |                   |                   |                   | GND               | GND               | GND                | GND                | GND                | GND                |                    |                    |                    | I/O <sub>139</sub> | I/O <sub>140</sub>               | I/O <sub>141</sub> | I/O <sub>142</sub> | М |

| Ν | I/O <sub>49</sub> | I/O <sub>50</sub>                | I/O <sub>51</sub>                | GND               |                   |                   |                   | GND               | GND               | GND                | GND                | GND                | GND                |                    |                    |                    | GND                | I/O <sub>136</sub>               | I/O <sub>137</sub> | I/O <sub>138</sub> | N |

| Ρ | I/O <sub>52</sub> | I/O <sub>53</sub>                | I/O <sub>55</sub>                | I/O <sub>58</sub> |                   |                   |                   |                   |                   |                    |                    |                    |                    |                    |                    |                    | I/O <sub>131</sub> | I/O <sub>133</sub>               | I/O <sub>134</sub> | I/O <sub>135</sub> | Ρ |

| R | I/O <sub>54</sub> | I/O <sub>56</sub>                | I/O <sub>59</sub>                | V <sub>CCO</sub>  |                   |                   |                   |                   |                   |                    |                    |                    |                    |                    |                    |                    | V <sub>CCO</sub>   | I/O <sub>130</sub>               | NC                 | I/O <sub>132</sub> | R |

| т | I/O <sub>57</sub> | I/O <sub>60</sub>                | I/O <sub>62</sub>                | I/O <sub>65</sub> |                   |                   |                   |                   |                   |                    |                    |                    |                    |                    |                    |                    | I/O <sub>124</sub> | I/O <sub>127</sub>               | I/O <sub>128</sub> | I/O <sub>129</sub> | т |

| U | I/O <sub>61</sub> | I/O <sub>63</sub>                | I/O <sub>66</sub>                | GND               | I/O <sub>76</sub> | V <sub>CCO</sub>  | I/O <sub>82</sub> | GND               | I/O <sub>91</sub> | V <sub>CC</sub>    | I/O <sub>98</sub>  | I/O <sub>102</sub> | GND                | I/O <sub>112</sub> | V <sub>CCO</sub>   | NC                 | GND                | I/O <sub>123</sub>               | I/O <sub>122</sub> | I/O <sub>126</sub> | U |

| V | I/O <sub>64</sub> | I/O <sub>67</sub>                | I/O <sub>69</sub>                | I/O <sub>75</sub> | I/O <sub>78</sub> | I/O <sub>81</sub> | I/O <sub>85</sub> | I/O <sub>88</sub> | I/O <sub>92</sub> | I <sub>2</sub>     | I/O <sub>97</sub>  | I/O <sub>101</sub> | I/O <sub>105</sub> | I/O <sub>109</sub> | I/O <sub>113</sub> | TDO                | I/O <sub>114</sub> | I/O <sub>117</sub>               | I/O <sub>121</sub> | I/O <sub>125</sub> | v |

| W | I/O <sub>68</sub> | I/O <sub>70</sub>                | I/O <sub>72</sub>                | I/O <sub>74</sub> | I/O <sub>79</sub> | I/O <sub>83</sub> | I/O <sub>86</sub> | I/O <sub>89</sub> | I/O <sub>93</sub> | I/O <sub>95</sub>  | I/O <sub>96</sub>  | I/O <sub>100</sub> | I/O <sub>104</sub> | I/O <sub>107</sub> | I/O <sub>110</sub> | NC                 | NC                 | I/O <sub>115</sub>               | I/O <sub>118</sub> | I/O <sub>120</sub> | w |

| Y | I/O <sub>71</sub> | I/O <sub>73</sub>                | I/O <sub>77</sub>                | TMS               | I/O <sub>80</sub> | I/O <sub>84</sub> | I/O <sub>87</sub> | I/O <sub>90</sub> | I/O <sub>94</sub> | NC                 | NC                 | I/O <sub>99</sub>  | I/O <sub>103</sub> | I/O <sub>106</sub> | I/O <sub>108</sub> | I/O <sub>111</sub> | NC                 | NC                               | I/O <sub>116</sub> | I/O <sub>119</sub> | Y |

|   | 1                 | 2                                | 3                                | 4                 | 5                 | 6                 | 7                 | 8                 | 9                 | 10                 | 11                 | 12                 | 13                 | 14                 | 15                 | 16                 | 17                 | 18                               | 19                 | 20                 |   |

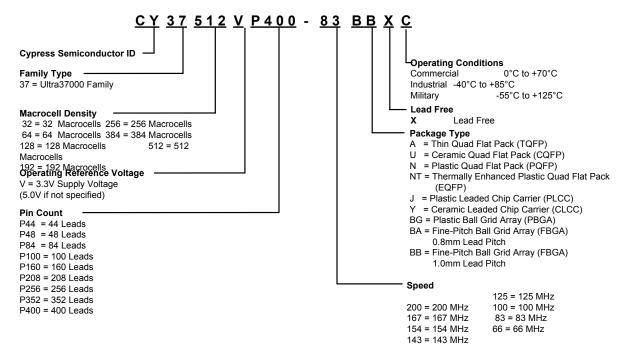

## **Ordering Information**

### **5.0V Ordering Information**

| Macrocells | Speed<br>(MHz) | Ordering Code      | Operating<br>Range |                                               |            |

|------------|----------------|--------------------|--------------------|-----------------------------------------------|------------|

| 32         | 200            | CY37032P44-200AC   | A44                | 44-Lead Thin Quad Flat Pack                   | Commercial |

|            |                | CY37032P44-200AXC  | A44                | 44-Lead Lead Free Thin Quad Flat Pack         | 1          |

|            |                | CY37032P44-200JC   | J67                | 44-Lead Plastic Leaded Chip Carrier           | 1          |

|            |                | CY37032P44-200JXC  | J67                | 44-Lead Lead Free Plastic Leaded Chip Carrier | 1          |

|            | 154            | CY37032P44-154AC   | A44                | 44-Lead Thin Quad Flat Pack                   | Commercial |

|            |                | CY37032P44-154JC   | J67                | 44-Lead Plastic Leaded Chip Carrier           | 1          |

|            |                | CY37032P44-154AI   | A44                | 44-Lead Thin Quad Flat Pack                   | Industrial |

|            |                | CY37032P44-154AXI  | A44                | 44-Lead Lead Free Thin Quad Flat Pack         | 1          |

|            |                | CY37032P44-154JI   | J67                | 44-Lead Plastic Leaded Chip Carrier           | 1          |

|            |                | CY37032P44-154JXI  | J67                | 44-Lead Lead Free Plastic Leaded Chip Carrier | 1          |

|            | 125            | CY37032P44-125AC   | A44                | 44-Lead Thin Quad Flat Pack                   | Commercial |

|            |                | CY37032P44-125AXC  | A44                | 44-Lead Lead Free Thin Quad Flat Pack         |            |

|            |                | CY37032P44-125JC   | J67                | 44-Lead Plastic Leaded Chip Carrier           | 1          |

|            |                | CY37032P44-125JXC  | J67                | 44-Lead Lead Free Plastic Leaded Chip Carrier | 1          |

|            |                | CY37032P44-125AI   | A44                | 44-Lead Thin Quad Flat Pack                   | Industrial |

|            |                | CY37032P44-125JI   | J67                | 44-Lead Plastic Leaded Chip Carrier           |            |

| 64         | 200            | CY37064P44-200AC   | A44                | 44-Lead Thin Quad Flat Pack                   | Commercial |

|            |                | CY37064P44-200AXC  | A44                | 44-Lead Lead Free Thin Quad Flat Pack         | 1          |

|            |                | CY37064P44-200JC   | J67                | 44-Lead Plastic Leaded Chip Carrier           |            |

|            |                | CY37064P44-200JXC  | J67                | 44-Lead Lead Free Plastic Leaded Chip Carrier | 1          |

|            |                | CY37064P84-200JC   | J83                | 84-Lead Plastic Leaded Chip Carrier           | 1          |

|            |                | CY37064P100-200AC  | A100               | 100-Lead Thin Quad Flat Pack                  | 1          |

|            |                | CY37064P100-200AXC | A100               | 100-Lead Lead Free Thin Quad Flat Pack        | 1          |

## 3.3V Ordering Information (continued)

| Macrocells | Speed<br>(MHz) | Ordering Code       | Package<br>Name | Package Type                           | Operating<br>Range |

|------------|----------------|---------------------|-----------------|----------------------------------------|--------------------|

| 256        | 100            | CY37256VP160-100AC  | A160            | 160-Lead Thin Quad Flat Pack           | Commercial         |

|            |                | CY37256VP160-100AXC | A160            | 160-Lead Lead Free Thin Quad Flat Pack |                    |

|            |                | CY37256VP208-100NC  | N208            | 208-Lead Plastic Quad Flat Pack        |                    |

|            |                | CY37256VP256-100BGC | BG292           | 292-Ball Plastic Ball Grid Array       |                    |

|            |                | CY37256VP256-100BBC | BB256           | 256-Ball Fine-Pitch Ball Grid Array    |                    |

|            |                | CY37256VP160-100AI  | A160            | 160-Lead Thin Quad Flat Pack           | Industrial         |

|            |                | CY37256VP160-100AXI | A160            | 160-Lead Lead Free Thin Quad Flat Pack |                    |

|            | 66             | CY37256VP160-66AC   | A160            | 160-Lead Thin Quad Flat Pack           | Commercial         |

|            |                | CY37256VP160-66AXC  | A160            | 160-Lead Lead Free Thin Quad Flat Pack |                    |

|            |                | CY37256VP208-66NC   | N208            | 208-Lead Plastic Quad Flat Pack        |                    |

|            |                | CY37256VP256-66BGC  | BG292           | 292-Ball Plastic Ball Grid Array       |                    |

|            |                | CY37256VP256-66BBC  | BB256           | 256-Ball Fine-Pitch Ball Grid Array    |                    |

|            |                | CY37256VP160-66AI   | A160            | 160-Lead Thin Quad Flat Pack           | Industrial         |

|            |                | CY37256VP256-66BGI  | BG292           | 292-Ball Plastic Ball Grid Array       |                    |

|            |                | CY37256VP256-66BBI  | BB256           | 256-Ball Fine-Pitch Ball Grid Array    |                    |

|            |                | 5962-9952401QZC     | U162            | 160-Lead Ceramic Quad Flat Pack        | Military           |

| 384        | 83             | CY37384VP208-83NC   | N208            | 208-Lead Plastic Quad Flat Pack        | Commercial         |

|            |                | CY37384VP256-83BGC  | BG292           | 292-Ball Plastic Ball Grid Array       |                    |

|            | 66             | CY37384VP208-66NC   | N208            | 208-Lead Plastic Quad Flat Pack        | Commercial         |

|            |                | CY37384VP256-66BGC  | BG292           | 292-Ball Plastic Ball Grid Array       |                    |

|            |                | CY37384VP208-66NI   | N208            | 208-Lead Plastic Quad Flat Pack        | Industrial         |

|            |                | CY37384VP256-66BGI  | BG292           | 292-Ball Plastic Ball Grid Array       |                    |

| 512        | 83             | CY37512VP208-83NC   | N208            | 208-Lead Plastic Quad Flat Pack        | Commercial         |

|            |                | CY37512VP256-83BGC  | BG292           | 292-Ball Plastic Ball Grid Array       |                    |

|            |                | CY37512VP352-83BGC  | BG388           | 388-Ball Plastic Ball Grid Array       |                    |

|            |                | CY37512VP400-83BBC  | BB400           | 400-Ball Fine-Pitch Ball Grid Array    |                    |

|            | 66             | CY37512VP208-66NC   | N208            | 208-Lead Plastic Quad Flat Pack        | Commercial         |

|            |                | CY37512VP256-66BGC  | BG292           | 292-Ball Plastic Ball Grid Array       |                    |

|            |                | CY37512VP352-66BGC  | BG388           | 388-Ball Plastic Ball Grid Array       |                    |

|            |                | CY37512VP400-66BBC  | BB400           | 400-Ball Fine-Pitch Ball Grid Array    |                    |

|            |                | CY37512VP208-66NI   | N208            | 208-Lead Plastic Quad Flat Pack        | Industrial         |

|            |                | CY37512VP256-66BGI  | BG292           | 292-Ball Plastic Ball Grid Array       |                    |

|            |                | CY37512VP352-66BGI  | BG388           | 388-Ball Plastic Ball Grid Array       |                    |

|            |                | CY37512VP400-66BBI  | BB400           | 400-Ball Fine-Pitch Ball Grid Array    |                    |

|            |                | 5962-9952601QZC     | U208            | 208-Lead Ceramic Quad Flat Pack        | Military           |

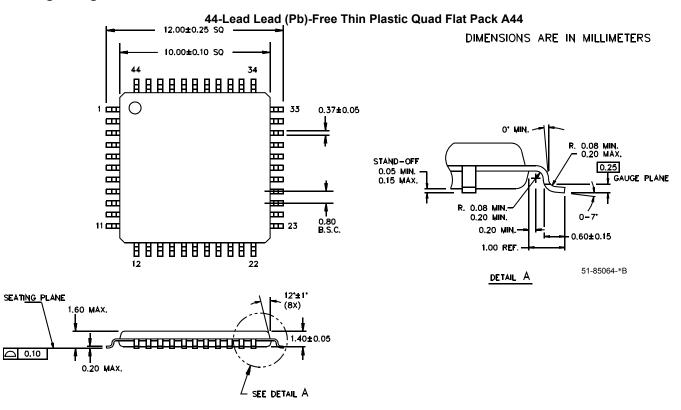

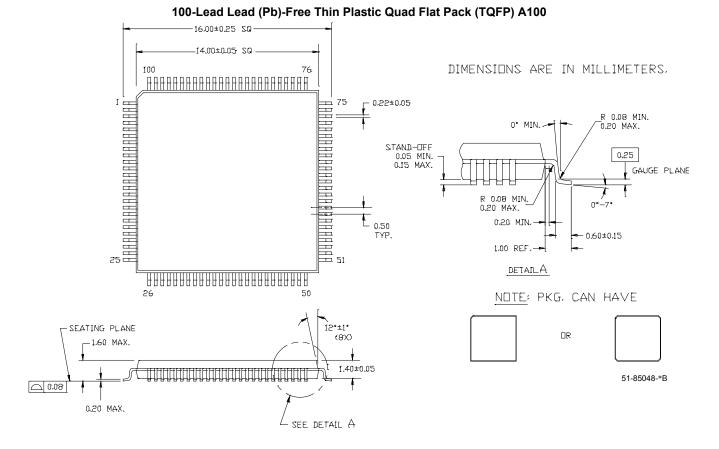

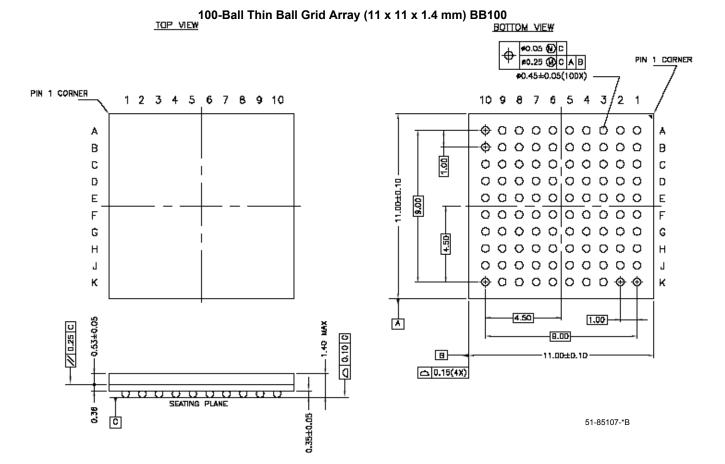

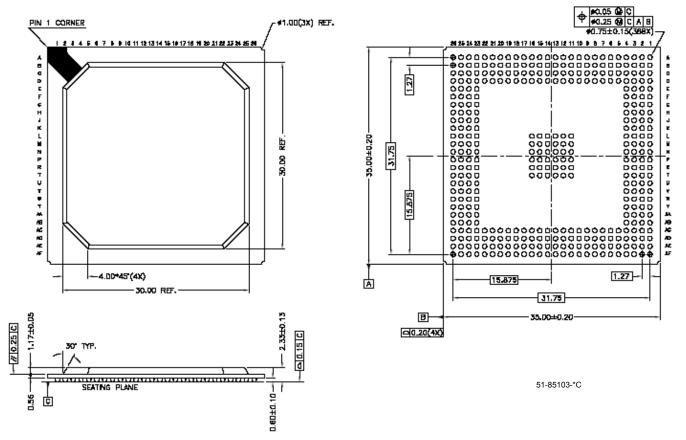

## Package Diagrams

44-Lead Lead (Pb)-Free Plastic Leaded Chip Carrier J67

DIMENSIONS IN INCHES MIN. 000 SEATING PLANE ٥ PIN #1 IDånar 39 1 0.013 0.023 <u>0.650</u> 0.658 <u>0.685</u> 0.695 ł 0.590 0.630 0045 0055 1 Ŧ **p** 5ð 0.023 0.033 28 18 0.020 NIN <u>0.650</u> 0.658 - | <u>0.090</u> 0.120 0.165 0.180 <u>0.685</u> 0.695 51-85003-\*A

## Package Diagrams (continued)

Package Diagrams (continued)

#### Document #: 38-03007 Rev. \*E

### Package Diagrams (continued)

### 388-Ball Plastic Ball Grid Array PBGA (35 x 35 x 2.33 mm) BG388