Welcome to **E-XFL.COM**

**Understanding Embedded - CPLDs (Complex Programmable Logic Devices)**

Embedded - CPLDs, or Complex Programmable Logic Devices, are highly versatile digital logic devices used in electronic systems. These programmable components are designed to perform complex logical operations and can be customized for specific applications. Unlike fixed-function ICs, CPLDs offer the flexibility to reprogram their configuration, making them an ideal choice for various embedded systems. They consist of a set of logic gates and programmable interconnects, allowing designers to implement complex logic circuits without needing custom hardware.

### **Applications of Embedded - CPLDs**

| Details                         |                                                                               |

|---------------------------------|-------------------------------------------------------------------------------|

|                                 |                                                                               |

| Product Status                  | Obsolete                                                                      |

| Programmable Type               | In-System Reprogrammable™ (ISR™) CMOS                                         |

| Delay Time tpd(1) Max           | 15 ns                                                                         |

| Voltage Supply - Internal       | 3V ~ 3.6V                                                                     |

| Number of Logic Elements/Blocks | -                                                                             |

| Number of Macrocells            | 128                                                                           |

| Number of Gates                 | -                                                                             |

| Number of I/O                   | 69                                                                            |

| Operating Temperature           | -40°C ~ 85°C (TA)                                                             |

| Mounting Type                   | Surface Mount                                                                 |

| Package / Case                  | 100-LQFP                                                                      |

| Supplier Device Package         | 100-TQFP (14x14)                                                              |

| Purchase URL                    | https://www.e-xfl.com/product-detail/infineon-technologies/cy37128vp100-83axi |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Selection Guide**

# 5.0V Selection Guide

### General Information

| Device  | Macrocells | Dedicated Inputs | I/O Pins    | Speed (t <sub>PD</sub> ) | Speed (f <sub>MAX</sub> ) |

|---------|------------|------------------|-------------|--------------------------|---------------------------|

| CY37032 | 32         | 5                | 32          | 6                        | 200                       |

| CY37064 | 64         | 5                | 32/64       | 6                        | 200                       |

| CY37128 | 128        | 5                | 64/128      | 6.5                      | 167                       |

| CY37192 | 192        | 5                | 120         | 7.5                      | 154                       |

| CY37256 | 256        | 5                | 128/160/192 | 7.5                      | 154                       |

| CY37384 | 384        | 5                | 160/192     | 10                       | 118                       |

| CY37512 | 512        | 5                | 160/192/264 | 10                       | 118                       |

## Speed Bins

| Device  | 200 | 167 | 154 | 143 | 125 | 100 | 83 | 66 |

|---------|-----|-----|-----|-----|-----|-----|----|----|

| CY37032 | Х   |     | Х   |     | Х   |     |    |    |

| CY37064 | Х   |     | Х   |     | Х   |     |    |    |

| CY37128 |     | Х   |     |     | Х   | Х   |    |    |

| CY37192 |     |     | Х   |     | Х   |     | Х  |    |

| CY37256 |     |     | Х   |     | Х   |     | Х  |    |

| CY37384 |     |     |     |     | Х   |     | Х  |    |

| CY37512 |     |     |     |     | Х   | Х   | Х  |    |

# Device-Package Offering and I/O Count

| Device  | 44-<br>Lead<br>TQFP | 44-<br>Lead<br>PLCC | 44-<br>Lead<br>CLCC | 84-<br>Lead<br>PLCC | 84-<br>Lead<br>CLCC | 100-<br>Lead<br>TQFP | 160-<br>Lead<br>TQFP | 160-<br>Lead<br>CQFP | 208-<br>Lead<br>PQFP | 208-<br>Lead<br>CQFP | 292-<br>Lead<br>PBGA | 388-<br>Lead<br>PBGA |

|---------|---------------------|---------------------|---------------------|---------------------|---------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| CY37032 | 37                  | 37                  |                     |                     |                     |                      |                      |                      |                      |                      |                      |                      |

| CY37064 | 37                  | 37                  | 37                  | 69                  |                     | 69                   |                      |                      |                      |                      |                      |                      |

| CY37128 |                     |                     |                     | 69                  | 69                  | 69                   | 133                  |                      |                      |                      |                      |                      |

| CY37192 |                     |                     |                     |                     |                     |                      | 125                  |                      |                      |                      |                      |                      |

| CY37256 |                     |                     |                     |                     |                     |                      | 133                  | 133                  | 165                  |                      | 197                  |                      |

| CY37384 |                     |                     |                     |                     |                     |                      |                      |                      | 165                  |                      | 197                  |                      |

| CY37512 |                     |                     |                     |                     |                     |                      |                      |                      | 165                  | 165                  | 197                  | 269                  |

## 3.3V Selection Guide

## General Information

| Device   | Macrocells | Dedicated Inputs | I/O Pins    | Speed (t <sub>PD</sub> ) | Speed (f <sub>MAX</sub> ) |

|----------|------------|------------------|-------------|--------------------------|---------------------------|

| CY37032V | 32         | 5                | 32          | 8.5                      | 143                       |

| CY37064V | 64         | 5                | 32/64       | 8.5                      | 143                       |

| CY37128V | 128        | 5                | 64/80/128   | 10                       | 125                       |

| CY37192V | 192        | 5                | 120         | 12                       | 100                       |

| CY37256V | 256        | 5                | 128/160/192 | 12                       | 100                       |

| CY37384V | 384        | 5                | 160/192     | 15                       | 83                        |

| CY37512V | 512        | 5                | 160/192/264 | 15                       | 83                        |

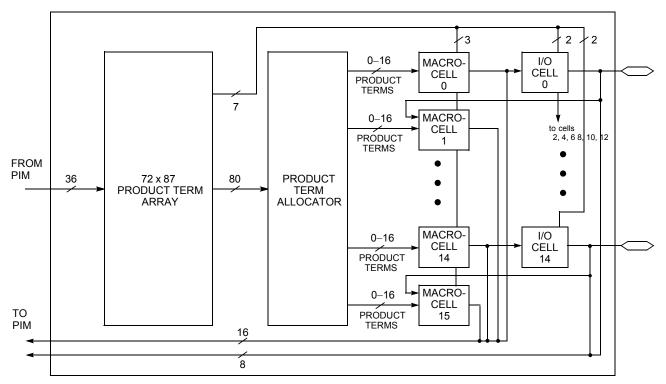

Figure 1. Logic Block with 50% Buried Macrocells

#### Low-Power Option

Each logic block can operate in high-speed mode for critical path performance, or in low-power mode for power conservation. The logic block mode is set by the user on a logic block by logic block basis.

#### **Product Term Allocator**

Through the product term allocator, software automatically distributes product terms among the 16 macrocells in the logic block as needed. A total of 80 product terms are available from the local product term array. The product term allocator provides two important capabilities without affecting performance: product term steering and product term sharing.

### Product Term Steering

Product term steering is the process of assigning product terms to macrocells as needed. For example, if one macrocell requires ten product terms while another needs just three, the product term allocator will "steer" ten product terms to one macrocell and three to the other. On Ultra37000 devices, product terms are steered on an individual basis. Any number between 0 and 16 product terms can be steered to any macrocell. Note that 0 product terms is useful in cases where a particular macrocell is unused or used as an input register.

#### Product Term Sharing

Product term sharing is the process of using the same product term among multiple macrocells. For example, if more than one output has one or more product terms in its equation that are common to other outputs, those product terms are only programmed once. The Ultra37000 product term allocator allows sharing across groups of four output macrocells in a

variable fashion. The software automatically takes advantage of this capability—the user does not have to intervene.

Note that neither product term sharing nor product term steering have any effect on the speed of the product. All worst-case steering and sharing configurations have been incorporated in the timing specifications for the Ultra37000 devices.

## Ultra37000 Macrocell

Within each logic block there are 16 macrocells. Macrocells can either be I/O Macrocells, which include an I/O Cell which is associated with an I/O pin, or buried Macrocells, which do not connect to an I/O. The combination of I/O Macrocells and buried Macrocells varies from device to device.

#### Buried Macrocell

Figure 2 displays the architecture of buried macrocells. The buried macrocell features a register that can be configured as combinatorial, a D flip-flop, a T flip-flop, or a level-triggered latch.

The register can be asynchronously set or asynchronously reset at the logic block level with the separate set and reset product terms. Each of these product terms features programmable polarity. This allows the registers to be set or reset based on an AND expression or an OR expression.

Clocking of the register is very flexible. Four global synchronous clocks and a product term clock are available to clock the register. Furthermore, each clock features programmable polarity so that registers can be triggered on falling as well as rising edges (see the Clocking section). Clock polarity is chosen at the logic block level.

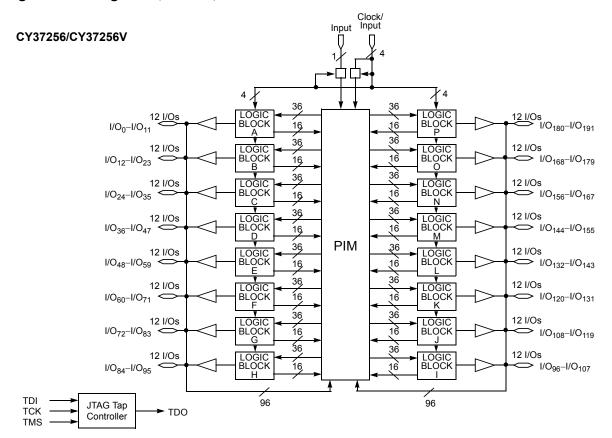

# Logic Block Diagrams (continued)

# Logic Block Diagrams (continued)

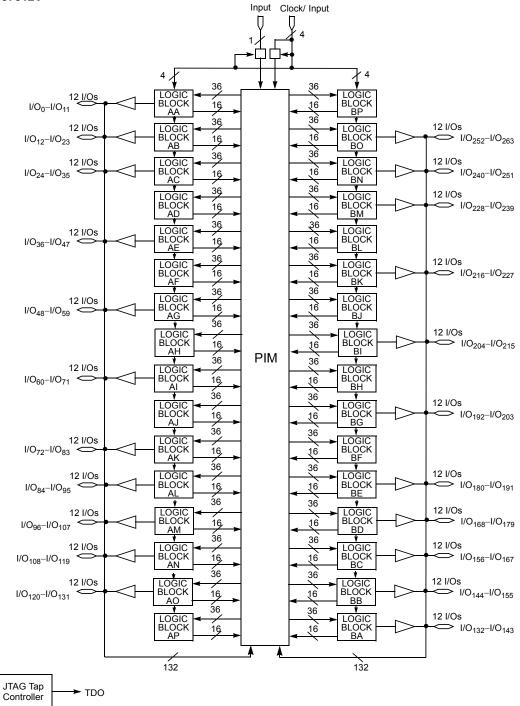

## CY37512/CY37512V

TDI

TCK

**TMS**

## Inductance<sup>[5]</sup>

| Parameter | Description               | Test Conditions                        | 44-<br>Lead<br>TQFP | 44-<br>Lead<br>PLCC | 44-<br>Lead<br>CLCC | 84-<br>Lead<br>PLCC | 84-<br>Lead<br>CLCC | 100-<br>Lead<br>TQFP | 160-<br>Lead<br>TQFP | 208-<br>Lead<br>PQFP | Unit |

|-----------|---------------------------|----------------------------------------|---------------------|---------------------|---------------------|---------------------|---------------------|----------------------|----------------------|----------------------|------|

|           | Maximum Pin<br>Inductance | V <sub>IN</sub> = 3.3V<br>at f = 1 MHz | 2                   | 5                   | 2                   | 8                   | 5                   | 8                    | 9                    | 11                   | nH   |

# Capacitance<sup>[5]</sup>

| Parameter        | Description                         | Test Conditions                                     | Max. | Unit |

|------------------|-------------------------------------|-----------------------------------------------------|------|------|

| C <sub>I/O</sub> | Input/Output Capacitance            | $V_{IN} = 3.3V$ at f = 1 MHz at $T_A = 25^{\circ}C$ | 8    | pF   |

| C <sub>CLK</sub> | Clock Signal Capacitance            | $V_{IN} = 3.3V$ at f = 1 MHz at $T_A = 25^{\circ}C$ | 12   | pF   |

| $C_{DP}$         | Dual Functional Pins <sup>[9]</sup> | $V_{IN} = 3.3V$ at f = 1 MHz at $T_A = 25^{\circ}C$ | 16   | pF   |

# **Endurance Characteristics**<sup>[5]</sup>

| Parameter | Description                  | Test Conditions                              | Min.  | Тур.   | Unit   |

|-----------|------------------------------|----------------------------------------------|-------|--------|--------|

| N         | Minimum Reprogramming Cycles | Normal Programming Conditions <sup>[2]</sup> | 1,000 | 10,000 | Cycles |

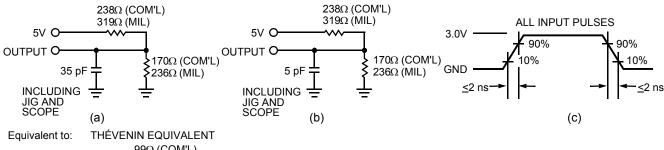

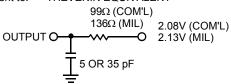

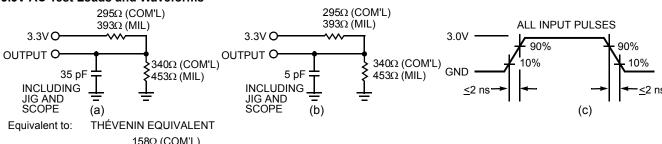

## **AC Characteristics**

#### 5.0V AC Test Loads and Waveforms

## 3.3V AC Test Loads and Waveforms

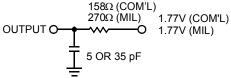

# Switching Waveforms (continued)

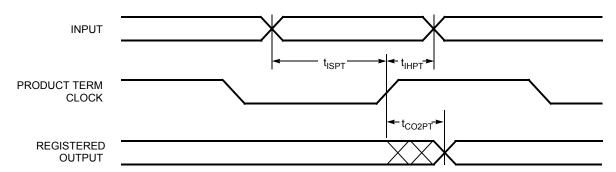

# Registered Output with Product Term Clocking Input Going Through the Array

## Registered Output with Product Term Clocking Input Coming From Adjacent Buried Register

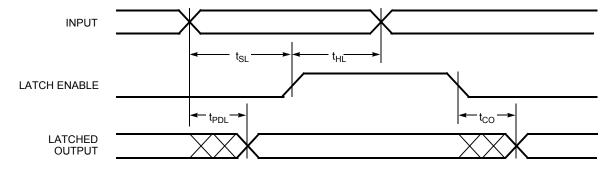

## **Latched Output**

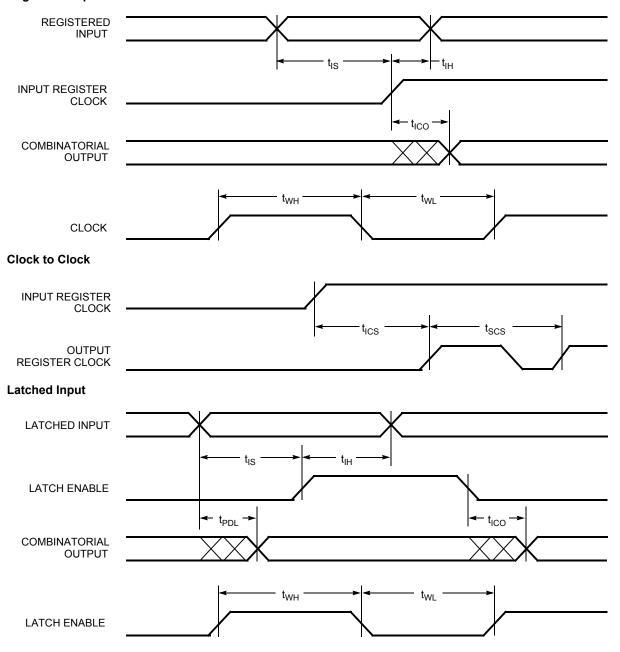

# Switching Waveforms (continued)

# **Registered Input**

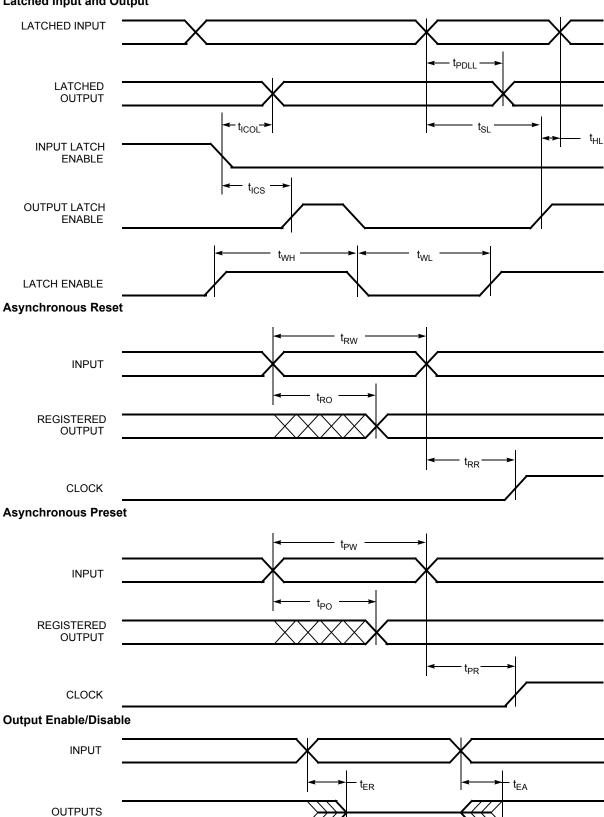

# Switching Waveforms (continued)

## **Latched Input and Output**

# **Power Consumption**

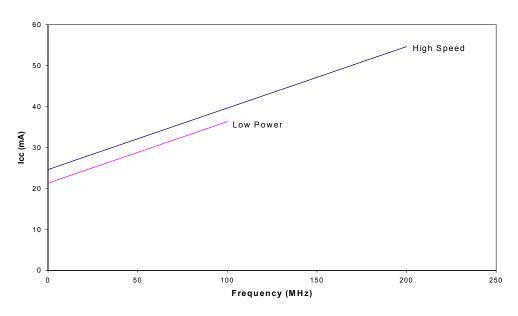

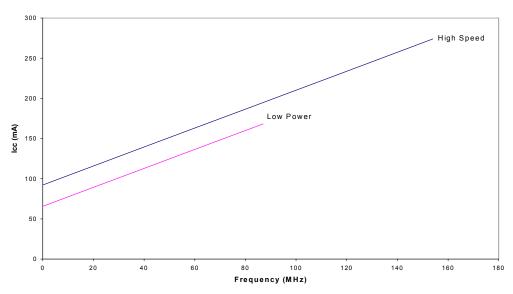

# Typical 5.0V Power Consumption CY37032

The typical pattern is a 16-bit up counter, per logic block, with outputs disabled.  $V_{CC} = 5.0V, \, T_A = Room \, Temperature$

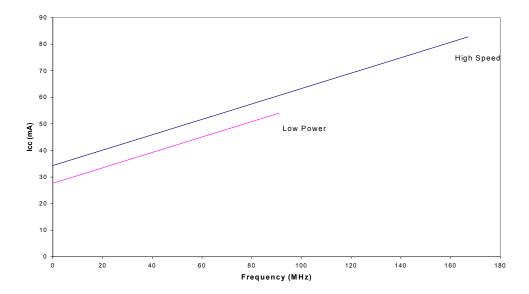

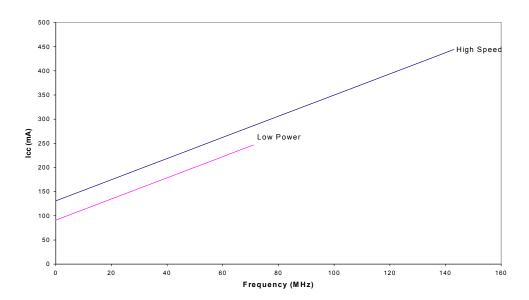

## CY37064

The typical pattern is a 16-bit up counter, per logic block, with outputs disabled.  $V_{CC} = 5.0V, \, T_A = Room \, Temperature$

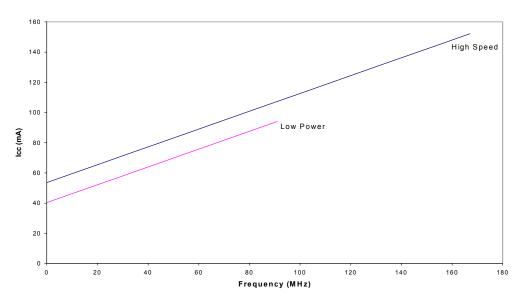

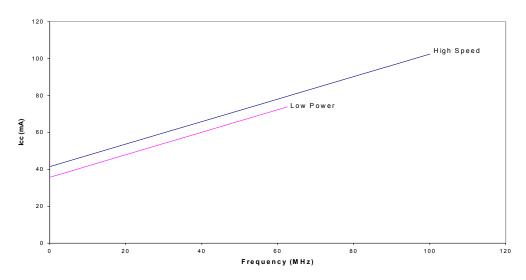

# **Typical 5.0V Power Consumption** (continued) **CY37128**

The typical pattern is a 16-bit up counter, per logic block, with outputs disabled.  $V_{CC} = 5.0V,\, T_A = Room\, Temperature$

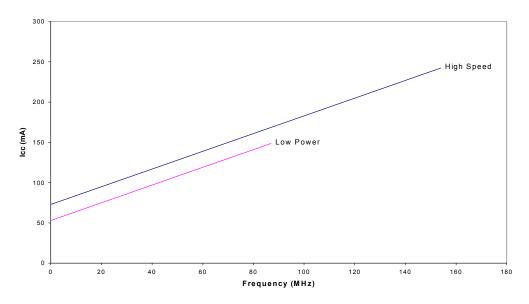

### CY37192

The typical pattern is a 16-bit up counter, per logic block, with outputs disabled.  $V_{CC}$  = 5.0V,  $T_A$  = Room Temperature

# **Typical 5.0V Power Consumption** (continued) **CY37256**

The typical pattern is a 16-bit up counter, per logic block, with outputs disabled.  $V_{CC} = 5.0V,\, T_A = Room\, Temperature$

### CY37384

The typical pattern is a 16-bit up counter, per logic block, with outputs disabled.  $V_{CC} = 5.0V,\, T_A = Room\, Temperature$

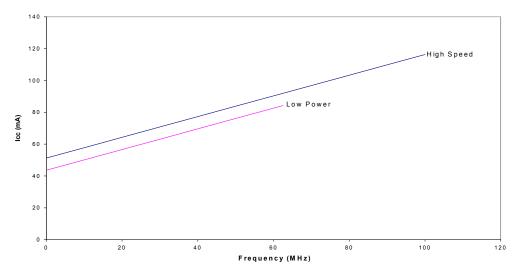

# **Typical 3.3V Power Consumption** (continued) **CY37192V**

The typical pattern is a 16-bit up counter, per logic block, with outputs disabled.  $V_{\rm CC}$  = 3.3V,  $T_{\rm A}$  = Room Temperature

## CY37256V

The typical pattern is a 16-bit up counter, per logic block, with outputs disabled.  $V_{\rm CC} = 3.3V,\,T_A = Room\,Temperature$

# Pin Configurations<sup>[20]</sup> (continued)

# 48-ball Fine-Pitch BGA (BA50) Top View

8 I/O<sub>3</sub> I/O<sub>1</sub> I/O<sub>30</sub> I/O<sub>5</sub> TCK V<sub>cc</sub> I/O<sub>31</sub>  $V_{CC}$ I/O<sub>27</sub> TDI  $V_{CC}$ I/O<sub>0</sub> CLK<sub>1</sub>/ I<sub>4</sub> CLK<sub>2</sub>/I<sub>0</sub> I/O<sub>7</sub> GND GND С I/O<sub>6</sub> I/O<sub>25</sub> I/O<sub>24</sub>  $I_3$ CLK<sub>3</sub>/ I<sub>2</sub> JTAG<sub>EN</sub> GND GND I/O<sub>23</sub> D I/O<sub>8</sub> I/O<sub>9</sub> I/O<sub>22</sub> CLK<sub>0</sub>/ I<sub>1</sub> I/O<sub>12</sub> I/O<sub>11</sub> I/O<sub>10</sub> I/O<sub>16</sub> I/O<sub>20</sub>  $V_{\text{CC}}$ I/O<sub>14</sub> I/O<sub>15</sub> I/O<sub>17</sub> I/O<sub>18</sub> I/O<sub>13</sub> TMS I/O<sub>19</sub> TDO

# Note:

20. For 3.3V versions (Ultra37000V),  $V_{CCO} = V_{CC}$ .

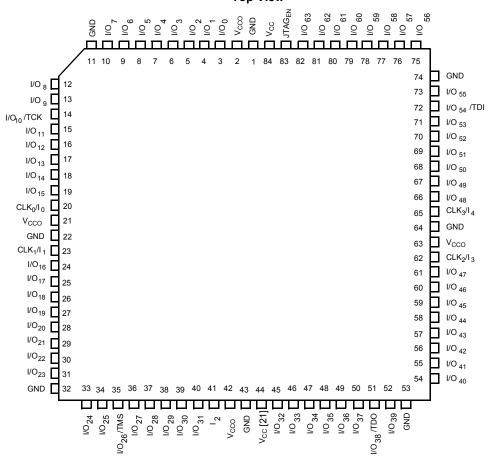

### 84-lead PLCC (J83) / CLCC (Y84) Top View

#### Note:

21. This pin is a N/C, but Cypress recommends that you connect it to V<sub>CC</sub> to ensure future compatibility.

Pin Configurations<sup>[20]</sup> (continued)

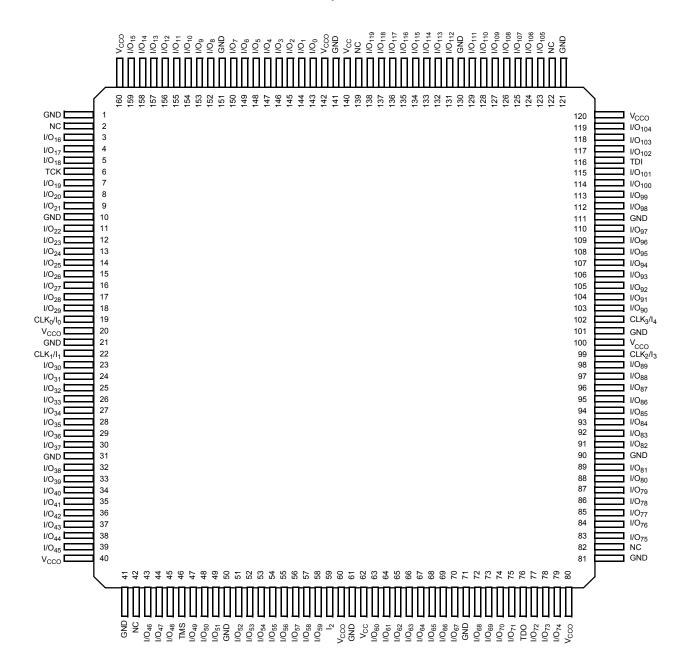

## 160-Lead TQFP (A160) for CY37192(V) Top View

Pin Configurations<sup>[20]</sup> (continued)

# 256-Ball Fine-Pitch BGA (BB256) Top View

|   | 1                 | 2                 | 3                 | 4                 | 5                                   | 6                 | 7                 | 8                 | 9                  | 10                 | 11                 | 12                                  | 13                 | 14                 | 15                 | 16                 |

|---|-------------------|-------------------|-------------------|-------------------|-------------------------------------|-------------------|-------------------|-------------------|--------------------|--------------------|--------------------|-------------------------------------|--------------------|--------------------|--------------------|--------------------|

| Α | GND               | GND               | I/O <sub>26</sub> | I/O <sub>24</sub> | I/O <sub>20</sub>                   | V <sub>CC</sub>   | I/O <sub>11</sub> | GND               | GND                | I/O <sub>186</sub> | V <sub>CC</sub>    | I/O <sub>177</sub>                  | I/O <sub>172</sub> | I/O <sub>167</sub> | GND                | GND                |

| В | GND               | I/O <sub>27</sub> | I/O <sub>25</sub> | I/O <sub>23</sub> | I/O <sub>19</sub>                   | I/O <sub>15</sub> | I/O <sub>10</sub> | GND               | GND                | I/O <sub>185</sub> | I/O <sub>181</sub> | I/O <sub>176</sub>                  | I/O <sub>171</sub> | I/O <sub>166</sub> | I/O <sub>165</sub> | GND                |

| С | I/O <sub>29</sub> | I/O <sub>28</sub> | NC                | I/O <sub>22</sub> | I/O <sub>18</sub>                   | I/O <sub>14</sub> | I/O <sub>9</sub>  | I/O <sub>4</sub>  | I/O <sub>191</sub> | I/O <sub>184</sub> | I/O <sub>180</sub> | I/O <sub>175</sub>                  | I/O <sub>170</sub> | NC                 | I/O <sub>163</sub> | I/O <sub>164</sub> |

| D | I/O <sub>32</sub> | I/O <sub>31</sub> | I/O <sub>30</sub> | NC                | I/O <sub>17</sub>                   | I/O <sub>13</sub> | I/O <sub>8</sub>  | I/O <sub>3</sub>  | I/O <sub>190</sub> | I/O <sub>183</sub> | I/O <sub>179</sub> | I/O <sub>174</sub>                  | I/O <sub>169</sub> | I/O <sub>160</sub> | I/O <sub>161</sub> | I/O <sub>162</sub> |

| E | I/O <sub>35</sub> | I/O <sub>34</sub> | I/O <sub>33</sub> | I/O <sub>21</sub> | I/O <sub>16</sub>                   | I/O <sub>12</sub> | I/O <sub>7</sub>  | I/O <sub>2</sub>  | I/O <sub>189</sub> | V <sub>CC</sub>    | I/O <sub>178</sub> | I/O <sub>173</sub>                  | I/O <sub>168</sub> | I/O <sub>157</sub> | I/O <sub>158</sub> | I/O <sub>159</sub> |

| F | V <sub>CC</sub>   | I/O <sub>38</sub> | I/O <sub>37</sub> | I/O <sub>36</sub> | TCK                                 | V <sub>CC</sub>   | I/O <sub>6</sub>  | I/O <sub>1</sub>  | I/O <sub>188</sub> | I/O <sub>182</sub> | V <sub>CC</sub>    | TDI                                 | I/O <sub>154</sub> | I/O <sub>155</sub> | I/O <sub>156</sub> | V <sub>CC</sub>    |

| G | I/O <sub>43</sub> | I/O <sub>42</sub> | I/O <sub>41</sub> | I/O <sub>40</sub> | V <sub>CC</sub>                     | I/O <sub>39</sub> | I/O <sub>5</sub>  | I/O <sub>0</sub>  | I/O <sub>187</sub> | I/O <sub>148</sub> | I/O <sub>149</sub> | CLK <sub>3</sub><br>/I <sub>4</sub> | I/O <sub>150</sub> | I/O <sub>151</sub> | I/O <sub>152</sub> | I/O <sub>153</sub> |

| Н | GND               | GND               | I/O <sub>47</sub> | I/O <sub>46</sub> | CLK <sub>0</sub><br>/I <sub>0</sub> | I/O <sub>45</sub> | I/O <sub>44</sub> | GND               | GND                | I/O <sub>144</sub> | I/O <sub>145</sub> | CLK <sub>2</sub><br>/I <sub>3</sub> | I/O <sub>146</sub> | I/O <sub>147</sub> | GND                | GND                |

| J | GND               | GND               | I/O <sub>51</sub> | I/O <sub>50</sub> | NC                                  | I/O <sub>49</sub> | I/O <sub>48</sub> | GND               | GND                | I/O <sub>140</sub> | I/O <sub>141</sub> | l <sub>2</sub>                      | I/O <sub>142</sub> | I/O <sub>143</sub> | GND                | GND                |

| K | I/O <sub>57</sub> | I/O <sub>56</sub> | I/O <sub>55</sub> | I/O <sub>54</sub> | CLK <sub>1</sub>                    | I/O <sub>53</sub> | I/O <sub>52</sub> | I/O <sub>91</sub> | I/O <sub>96</sub>  | I/O <sub>101</sub> | I/O <sub>135</sub> | V <sub>CC</sub>                     | I/O <sub>136</sub> | I/O <sub>137</sub> | I/O <sub>138</sub> | I/O <sub>139</sub> |

| L | V <sub>CC</sub>   | I/O <sub>60</sub> | I/O <sub>59</sub> | I/O <sub>58</sub> | TMS                                 | V <sub>CC</sub>   | I/O <sub>86</sub> | I/O <sub>92</sub> | I/O <sub>97</sub>  | I/O <sub>102</sub> | V <sub>CC</sub>    | TDO                                 | I/O <sub>132</sub> | I/O <sub>133</sub> | I/O <sub>134</sub> | V <sub>CC</sub>    |

| M | I/O <sub>63</sub> | I/O <sub>62</sub> | I/O <sub>61</sub> | I/O <sub>72</sub> | I/O <sub>77</sub>                   | I/O <sub>82</sub> | V <sub>CC</sub>   | I/O <sub>93</sub> | I/O <sub>98</sub>  | I/O <sub>103</sub> | I/O <sub>108</sub> | I/O <sub>112</sub>                  | I/O <sub>117</sub> | I/O <sub>129</sub> | I/O <sub>130</sub> | I/O <sub>131</sub> |

| N | I/O <sub>66</sub> | I/O <sub>65</sub> | I/O <sub>64</sub> | I/O <sub>73</sub> | I/O <sub>78</sub>                   | I/O <sub>83</sub> | I/O <sub>87</sub> | I/O <sub>94</sub> | I/O <sub>99</sub>  | I/O <sub>104</sub> | I/O <sub>109</sub> | I/O <sub>113</sub>                  | NC                 | I/O <sub>126</sub> | I/O <sub>127</sub> | I/O <sub>128</sub> |

| Р | I/O <sub>68</sub> | I/O <sub>67</sub> | NC                | I/O <sub>74</sub> | I/O79                               | I/O <sub>84</sub> | I/O <sub>88</sub> | I/O <sub>95</sub> | I/O <sub>100</sub> | I/O <sub>105</sub> | I/O <sub>110</sub> | I/O <sub>114</sub>                  | I/O <sub>118</sub> | NC                 | I/O <sub>124</sub> | I/O <sub>125</sub> |

| R | GND               | I/O <sub>69</sub> | I/O <sub>70</sub> | I/O <sub>75</sub> | I/O <sub>80</sub>                   | I/O <sub>85</sub> | I/O <sub>89</sub> | GND               | GND                | I/O <sub>106</sub> | I/O <sub>111</sub> | I/O <sub>115</sub>                  | I/O <sub>119</sub> | I/O <sub>121</sub> | I/O <sub>123</sub> | GND                |

| Т | GND               | GND               | I/O <sub>71</sub> | I/O <sub>76</sub> | I/O <sub>81</sub>                   | V <sub>CC</sub>   | I/O <sub>90</sub> | GND               | GND                | I/O <sub>107</sub> | V <sub>CC</sub>    | I/O <sub>116</sub>                  | I/O <sub>120</sub> | I/O <sub>122</sub> | GND                | GND                |

# Ultra37000 CPLD Family

# 5.0V Ordering Information (continued)

| Macrocells | Speed<br>(MHz) | Ordering Code      | Package<br>Name              | Package Type                                  | Operating<br>Range |  |  |  |

|------------|----------------|--------------------|------------------------------|-----------------------------------------------|--------------------|--|--|--|

| 64         | 154            | CY37064P44-154AC   | A44                          | 44-Lead Thin Quad Flat Pack                   | Commercial         |  |  |  |

|            |                | CY37064P44-154JC   | J67                          | 44-Lead Plastic Leaded Chip Carrier           | ]                  |  |  |  |

|            |                | CY37064P84-154JC   | J83                          | 84-Lead Plastic Leaded Chip Carrier           | ]                  |  |  |  |

|            |                | CY37064P100-154AC  | 100-Lead Thin Quad Flat Pack |                                               |                    |  |  |  |

|            |                | CY37064P44-154AI   | A44                          | 44-Lead Thin Quad Flat Pack                   | Industrial         |  |  |  |

|            |                | CY37064P44-154AXI  | A44                          | 44-Lead Lead Free Thin Quad Flat Pack         | ]                  |  |  |  |

|            |                | CY37064P44-154JI   | J67                          | 44-Lead Plastic Leaded Chip Carrier           |                    |  |  |  |

|            |                | CY37064P44-154JXI  | J67                          | 44-Lead Lead Free Plastic Leaded Chip Carrier |                    |  |  |  |

|            |                | CY37064P84-154JI   | J83                          | 84-Lead Plastic Leaded Chip Carrier           |                    |  |  |  |

|            |                | CY37064P100-154AI  | A100                         | 100-Lead Thin Quad Flat Pack                  | 1                  |  |  |  |

|            |                | 5962-9951902QYA    | Y67                          | 44-Lead Ceramic Leadless Chip Carrier         | Military           |  |  |  |

|            | 125            | CY37064P44-125AC   | A44                          | 44-Lead Thin Quad Flat Pack                   | Commercial         |  |  |  |

|            |                | CY37064P44-125AXC  | A44                          | 44-Lead Lead Free Thin Quad Flat Pack         | 1                  |  |  |  |

|            |                | CY37064P44-125JC   | J67                          | 44-Lead Plastic Leaded Chip Carrier           | 1                  |  |  |  |

|            |                | CY37064P44-125JXC  | J67                          | 44-Lead Lead Free Plastic Leaded Chip Carrier | 1                  |  |  |  |

|            |                | CY37064P84-125JC   | J83                          | 84-Lead Plastic Leaded Chip Carrier           | 1                  |  |  |  |

|            |                | CY37064P100-125AC  | A100                         | 100-Lead Thin Quad Flat Pack                  |                    |  |  |  |

|            |                | CY37064P100-125AXC | A100                         | 100-Lead Lead Free Thin Quad Flat Pack        |                    |  |  |  |

|            |                | CY37064P44-125AI   | A44                          | 44-Lead Thin Quad Flat Pack                   | Industrial         |  |  |  |

|            |                | CY37064P44-125AXI  | A44                          | 44-Lead Lead Free Thin Quad Flat Pack         | 1                  |  |  |  |

|            |                | CY37064P44-125JI   | J67                          | 44-Lead Plastic Leaded Chip Carrier           |                    |  |  |  |

|            |                | CY37064P84-125JI   | J83                          | 84-Lead Plastic Leaded Chip Carrier           |                    |  |  |  |

|            |                | CY37064P100-125AI  | A100                         | 100-Lead Thin Quad Flat Pack                  |                    |  |  |  |

|            |                | CY37064P100-125AXI | A100                         | 100-Lead Lead Free Thin Quad Flat Pack        |                    |  |  |  |

|            |                | 5962-9951901QYA    | Y67                          | 44-Lead Ceramic Leadless Chip Carrier         | Military           |  |  |  |

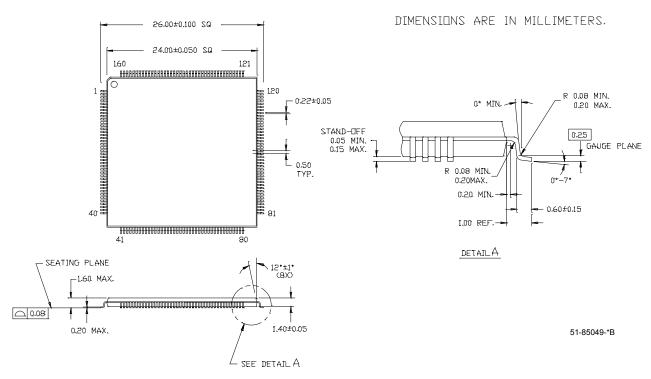

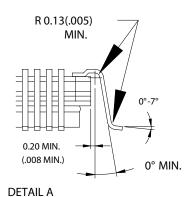

# 160-Lead Lead (Pb)-Free Thin Plastic Quad Flat Pack (24 x 24 x 1.4 mm) (TQFP) A160

## 208-Lead Ceramic Quad Flatpack (Cavity Up) U208

DIMENSIONS IN MM (INCH) REFERENCE JEDEC: N/A PKG. WEIGHT: 6-7gms

51-80105-\*B

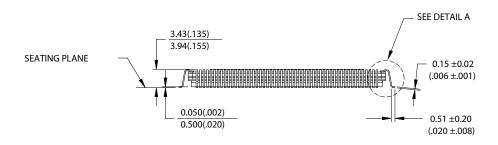

# 292-Ball Plastic Ball Grid Array PBGA (27 x 27 x 2.33 mm) BG292

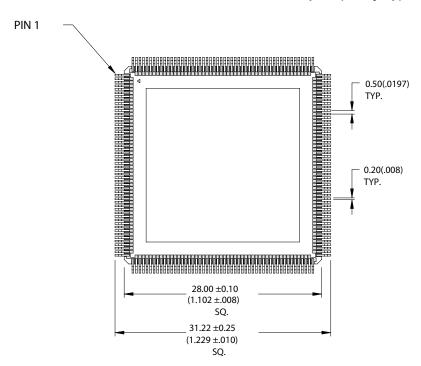

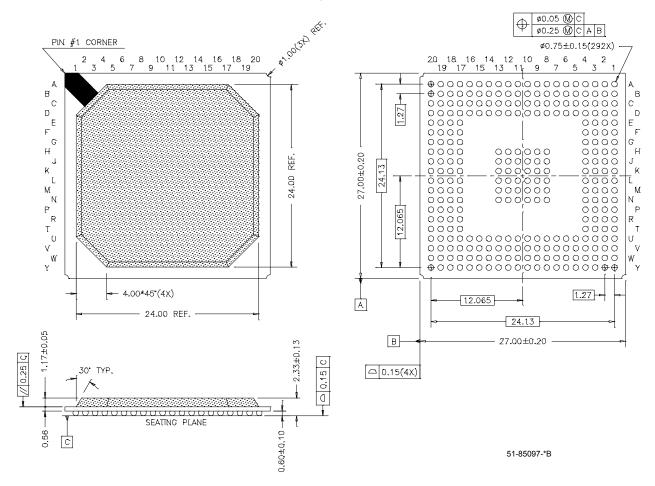

### 400-Ball FBGA (21 x 21 x 1.4 mm) BB400

ViewDraw and SpeedWave are trademarks of ViewLogic. Windows is a registered trademark of Microsoft Corporation. *Warp* is a registered trademark, and In-System Reprogrammable, ISR, *Warp* Professional, *Warp* Enterprise, and Ultra37000 are trademarks, of Cypress Semiconductor Corporation. All product and company names mentioned in this document are the trademarks of their respective holders.