Welcome to E-XFL.COM

### Understanding <u>Embedded - CPLDs (Complex</u> <u>Programmable Logic Devices)</u>

Embedded - CPLDs, or Complex Programmable Logic Devices, are highly versatile digital logic devices used in electronic systems. These programmable components are designed to perform complex logical operations and can be customized for specific applications. Unlike fixedfunction ICs, CPLDs offer the flexibility to reprogram their configuration, making them an ideal choice for various embedded systems. They consist of a set of logic gates and programmable interconnects, allowing designers to implement complex logic circuits without needing custom hardware.

#### **Applications of Embedded - CPLDs**

### Details

E·XFI

| Details                         |                                                                              |  |

|---------------------------------|------------------------------------------------------------------------------|--|

| Product Status                  | Obsolete                                                                     |  |

| Programmable Type               | In-System Reprogrammable <sup>™</sup> (ISR <sup>™</sup> ) CMOS               |  |

| Delay Time tpd(1) Max           | 15 ns                                                                        |  |

| Voltage Supply - Internal       | 4.5V ~ 5.5V                                                                  |  |

| Number of Logic Elements/Blocks | ·                                                                            |  |

| Number of Macrocells            | 192                                                                          |  |

| Number of Gates                 | -                                                                            |  |

| Number of I/O                   | 125                                                                          |  |

| Operating Temperature           | -40°C ~ 85°C (TA)                                                            |  |

| Mounting Type                   | Surface Mount                                                                |  |

| Package / Case                  | 160-LQFP                                                                     |  |

| Supplier Device Package         | 160-TQFP (24x24)                                                             |  |

| Purchase URL                    | https://www.e-xfl.com/product-detail/infineon-technologies/cy37192p160-83axi |  |

|                                 |                                                                              |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Ultra37000 CPLD Family

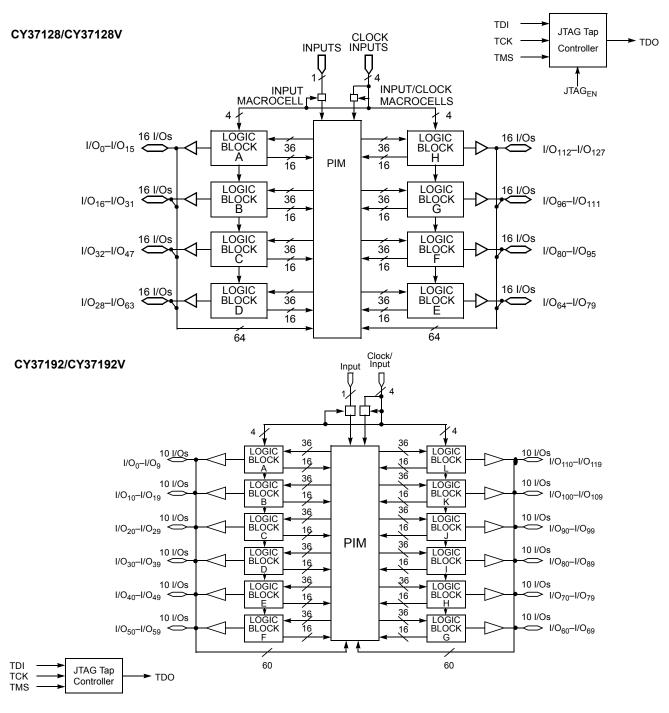

## Logic Block Diagrams (continued)

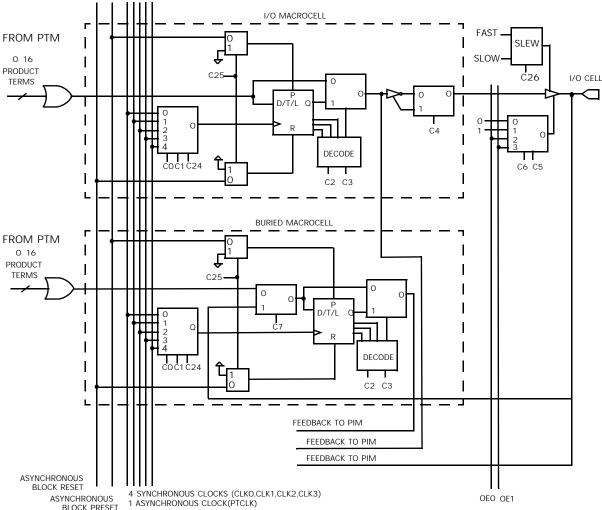

The buried macrocell also suppose input register capability. Bus Hold Capabilities on all I/Os The buried macrocell can be configured to act as an input sus-hold, which is an improved version of the popular internal register (D-type or latch) wentinsput comes from the I/O pin associated with the neighboring nomenal. The output of all buried macrocells is sent directly to the PIM regardless of configuration.

high-impedance state, thus educing system noise in bus-interface applications. Bus-hold additionally allows unused device pins to remain unconnected on the board,

## I/O Macrocell Figure 2 illustrates the atritecture of the macrocell. The

Figure 2 illustrates the cantecture of the macrocell. The which is particularly useful idigrprototyping as designers can I/O macrocell supports the same functions as the buried ute new signals to the device without cutting trace connecmacrocell with the addition of I/O capability. At the output of the solution of the output of the solution of the output of the solution of the solution of the addition of I/O capability. At the output of the solution of the

of allowing significant logic reduction to occur in many appliegrammable Slew Rate Control cations. Each output has a programmable configuration bit, which sets

The Ultra37000 macrocell feature feedback path to the PIM the output slew rate to fast or slow. For designs concerned with separate from the I/O pin in prath. This means that if the meeting FCC emissions standards the slow edge provides for macrocell is buried (fed back internally only), the associated wer system noise. For designs quiring very high perfor-I/O pin can still be used as an input.

Figure 2. I/O and Buried Macrocells

The third programming option for Ultra37000 devices is The fourth method for programming Ultra37000 devices is to utilize the embedded controller processor that already use the same programmer that currently being used to exists in the system. The Ultra37000 ISR software assistspinogram EASH 370i devices.

this method by converting the device JEDEC maps into the ISR serial stream that contains the ISR instruction information device data sheets. For ISR cable and software specifications, and the addresses and data of locations to be programmed effer to the UltraISR kit data sheet (CY3700i). The embedded controller then simply directs this ISR stream

to the chain of Ultra37000 devices to complete the desired

reconfiguring or diagnostic operations. Contact your local sales office for information on availability of this option.

As with development software, Cypress support is available on a wide variety of third-partogpammers. All major third-party programmers (including BP Micro, Data I/O, and SMS) support the Ultra37000 family.

## Ultra37000 CPLD Family

| 111                       |                  | 1                                   |

|---------------------------|------------------|-------------------------------------|

| Parameter <sup>[11]</sup> | V <sub>X</sub>   | Output Waveform Measurement Level   |

| ter()                     | 1.5V             | V <sub>OH</sub> 0.5V V <sub>X</sub> |

| ter(+)                    | 2.6V             | $V_{OL} \xrightarrow{0.5V} V_X$     |

| teA(+)                    | 1.5V             | V <sub>X</sub> 0.5V V <sub>OH</sub> |

| tea()                     | V <sub>the</sub> | $V_X \rightarrow V_{OL}$            |

### (d) Test Waveforms

## Switching CharacteristicsOver the Operating Rang<sup>[2]</sup>

| Parameter                        | Description                                                                                                                                                                                                                                           | Unit  |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Combinatorial Mod                | le Parameters                                                                                                                                                                                                                                         | •     |

| ቱ_[13, 14, 15]<br>ትD             | Input to Combinatorial Output                                                                                                                                                                                                                         | ns    |

| ФDL <sup>[13, 14, 15]</sup>      | Input to Output Through Transparent Input or Output Latch                                                                                                                                                                                             |       |

| ቱ <sub>011</sub> [13, 14, 15]    | Input to Output Through Transparent Input and Output Latches                                                                                                                                                                                          |       |

| t <sub>EA</sub> [13, 14, 15]     | Input to Output Enable                                                                                                                                                                                                                                | ns    |

| ŧ <sub>R</sub> [11, 13]          | Input to Output Disable                                                                                                                                                                                                                               | ns    |

| Input Register Par               | ameters                                                                                                                                                                                                                                               | •     |

| t <sub>WL</sub>                  | Clock or Latch Enable Input LOW Time                                                                                                                                                                                                                  | ns    |

| t <sub>WH</sub>                  | Clock or Latch Enabl Input HIGH Time <sup>8]</sup>                                                                                                                                                                                                    | ns    |

| ţs                               | Input Register or Latch Set-up Time                                                                                                                                                                                                                   | ns    |

| ţн                               | Input Register or Latch Hold Time                                                                                                                                                                                                                     | ns    |

| ŧco <sup>[13, 14, 15]</sup>      | Input Register Clock or Latch Enable to Combinatorial Output                                                                                                                                                                                          | 1     |

| ŧ <sub>COL</sub> [13, 14, 15]    | Input Register Clock or Latch Enable totput Through Transpant Output Latch                                                                                                                                                                            | ns    |

| Synchronous Cloc                 | king Parameters                                                                                                                                                                                                                                       |       |

| tco <sup>[14, 15]</sup>          | Synchronous Clock (CLK, CLK <sub>1</sub> , CLK <sub>2</sub> , or CLK <sub>3</sub> ) or Latch Enable to Output                                                                                                                                         | ns    |

| t <sub>s</sub> <sup>[13]</sup>   | Set-Up Time from Input to Sync. Clk (GLICLK <sub>1</sub> , CLK <sub>2</sub> , or CLK <sub>3</sub> ) or Latch Enable                                                                                                                                   | ns    |

| ų                                | Register or Latch Data Hold Time                                                                                                                                                                                                                      | ns    |

| tco2 <sup>[13, 14, 15]</sup>     | Output Synchronous Clock (CbKCLK <sub>1</sub> , CLK <sub>2</sub> , or CLK <sub>3</sub> ) or Latch Enable to Combinatorial Outputs Delay (Through Logic Array)                                                                                         |       |

| t <sub>SCS</sub> <sup>[13]</sup> | Output Synchronous Clock (CbKCLK <sub>1</sub> , CLK <sub>2</sub> , or CLK <sub>3</sub> ) or Latch Enable to Output Synchron Clock (CLK <sub>0</sub> CLK <sub>1</sub> , CLK <sub>2</sub> , or CLK <sub>3</sub> ) or Latch Enable (Through Logic Array) | อนธร  |

| t <sub>SL</sub> [13]             | Set-Up Time from Input Through Transparentdbato Output Register Synchronous Clock (CCLK $_1$ , CLK $_2$ , or CLK $_3$ ) or Latch Enable                                                                                                               | LKns  |

| ΨL                               | Hold Time for Input Through Transparent Latch from Output Register Synchronous Clock $CLK_1$ , $CLK_2$ , or $CLK_3$ ) or Latch Enable                                                                                                                 | (CH4K |

Notes:

11.  $t_{ER}$  measured with 5-pF AC Test Load apple theasured with 35-pF AC Test Load. 12. All AC parameters are measured with two outputs switching and 35-pF AC Test Load. 13. Logic Blocks operating trow-PowerMode, add  $t_p$  to this spec. 14. Outputs using Slow Output Slew Rate,  $add_{3,10}$  to this spec. 15. When  $V_{CCO} = 3.3V$ , add  $\frac{1}{3,310}$  to this spec.