Welcome to **E-XFL.COM**

**Understanding Embedded - CPLDs (Complex Programmable Logic Devices)**

Embedded - CPLDs, or Complex Programmable Logic Devices, are highly versatile digital logic devices used in electronic systems. These programmable components are designed to perform complex logical operations and can be customized for specific applications. Unlike fixed-function ICs, CPLDs offer the flexibility to reprogram their configuration, making them an ideal choice for various embedded systems. They consist of a set of logic gates and programmable interconnects, allowing designers to implement complex logic circuits without needing custom hardware.

### **Applications of Embedded - CPLDs**

| Details                         |                                                                               |

|---------------------------------|-------------------------------------------------------------------------------|

| Product Status                  | Obsolete                                                                      |

| Programmable Type               | In-System Reprogrammable™ (ISR™) CMOS                                         |

| Delay Time tpd(1) Max           | 7.5 ns                                                                        |

| Voltage Supply - Internal       | 4.75V ~ 5.25V                                                                 |

| Number of Logic Elements/Blocks | -                                                                             |

| Number of Macrocells            | 256                                                                           |

| Number of Gates                 | -                                                                             |

| Number of I/O                   | 197                                                                           |

| Operating Temperature           | 0°C ~ 70°C (TA)                                                               |

| Mounting Type                   | Surface Mount                                                                 |

| Package / Case                  | 292-BGA                                                                       |

| Supplier Device Package         | 292-PBGA (27x27)                                                              |

| Purchase URL                    | https://www.e-xfl.com/product-detail/infineon-technologies/cy37256p256-154bgc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

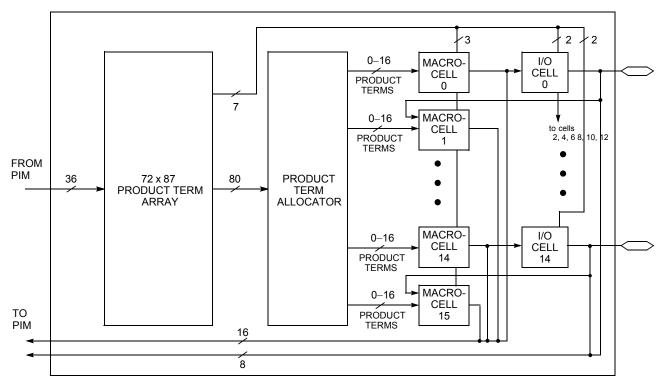

Figure 1. Logic Block with 50% Buried Macrocells

#### Low-Power Option

Each logic block can operate in high-speed mode for critical path performance, or in low-power mode for power conservation. The logic block mode is set by the user on a logic block by logic block basis.

#### **Product Term Allocator**

Through the product term allocator, software automatically distributes product terms among the 16 macrocells in the logic block as needed. A total of 80 product terms are available from the local product term array. The product term allocator provides two important capabilities without affecting performance: product term steering and product term sharing.

### Product Term Steering

Product term steering is the process of assigning product terms to macrocells as needed. For example, if one macrocell requires ten product terms while another needs just three, the product term allocator will "steer" ten product terms to one macrocell and three to the other. On Ultra37000 devices, product terms are steered on an individual basis. Any number between 0 and 16 product terms can be steered to any macrocell. Note that 0 product terms is useful in cases where a particular macrocell is unused or used as an input register.

#### Product Term Sharing

Product term sharing is the process of using the same product term among multiple macrocells. For example, if more than one output has one or more product terms in its equation that are common to other outputs, those product terms are only programmed once. The Ultra37000 product term allocator allows sharing across groups of four output macrocells in a

variable fashion. The software automatically takes advantage of this capability—the user does not have to intervene.

Note that neither product term sharing nor product term steering have any effect on the speed of the product. All worst-case steering and sharing configurations have been incorporated in the timing specifications for the Ultra37000 devices.

### Ultra37000 Macrocell

Within each logic block there are 16 macrocells. Macrocells can either be I/O Macrocells, which include an I/O Cell which is associated with an I/O pin, or buried Macrocells, which do not connect to an I/O. The combination of I/O Macrocells and buried Macrocells varies from device to device.

#### **Buried Macrocell**

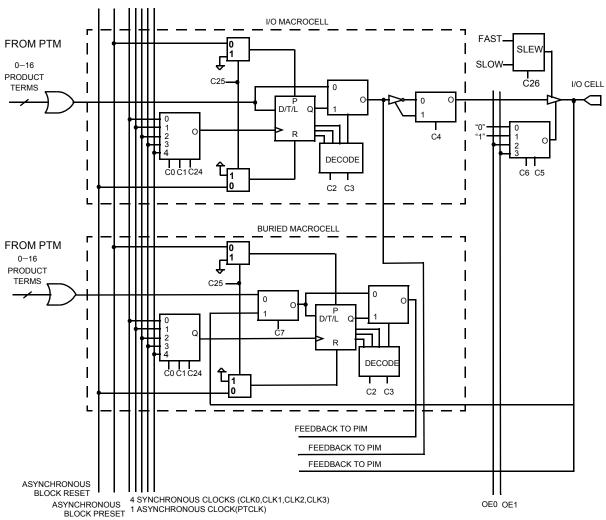

Figure 2 displays the architecture of buried macrocells. The buried macrocell features a register that can be configured as combinatorial, a D flip-flop, a T flip-flop, or a level-triggered latch.

The register can be asynchronously set or asynchronously reset at the logic block level with the separate set and reset product terms. Each of these product terms features programmable polarity. This allows the registers to be set or reset based on an AND expression or an OR expression.

Clocking of the register is very flexible. Four global synchronous clocks and a product term clock are available to clock the register. Furthermore, each clock features programmable polarity so that registers can be triggered on falling as well as rising edges (see the Clocking section). Clock polarity is chosen at the logic block level.

The buried macrocell also supports input register capability. The buried macrocell can be configured to act as an input register (D-type or latch) whose input comes from the I/O pin associated with the neighboring macrocell. The output of all buried macrocells is sent directly to the PIM regardless of its configuration.

#### I/O Macrocell

Figure 2 illustrates the architecture of the I/O macrocell. The I/O macrocell supports the same functions as the buried macrocell with the addition of I/O capability. At the output of the macrocell, a polarity control mux is available to select active LOW or active HIGH signals. This has the added advantage of allowing significant logic reduction to occur in many applications.

The Ultra37000 macrocell features a feedback path to the PIM separate from the I/O pin input path. This means that if the macrocell is buried (fed back internally only), the associated I/O pin can still be used as an input.

#### Bus Hold Capabilities on all I/Os

Bus-hold, which is an improved version of the popular internal pull-up resistor, is a weak latch connected to the pin that does not degrade the device's performance. As a latch, bus-hold maintains the last state of a pin when the pin is placed in a high-impedance state, thus reducing system noise in bus-interface applications. Bus-hold additionally allows unused device pins to remain unconnected on the board, which is particularly useful during prototyping as designers can route new signals to the device without cutting trace connections to  $V_{\rm CC}$  or GND. For more information, see the application note  $Understanding\ Bus-Hold—A\ Feature\ of\ Cypress\ CPLDs$ .

#### Programmable Slew Rate Control

Each output has a programmable configuration bit, which sets the output slew rate to fast or slow. For designs concerned with meeting FCC emissions standards the slow edge provides for lower system noise. For designs requiring very high performance the fast edge rate provides maximum system performance.

Figure 2. I/O and Buried Macrocells

# Ultra37000 CPLD Family

# **5.0V Device Characteristics Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.) Storage Temperature ......-65°C to +150°C

Ambient Temperature with

Power Applied ......55°C to +125°C

Supply Voltage to Ground Potential ...... -0.5V to +7.0V

| DC Voltage Applied to Outputs                          | 0.5)/47.0)/    |

|--------------------------------------------------------|----------------|

| in High-Z State                                        | –0.5V to +7.0V |

| DC Input Voltage                                       | 0.5V to +7.0V  |

| DC Program Voltage                                     | 4.5 to 5.5V    |

| Current into Outputs                                   | 16 mA          |

| Static Discharge Voltage(per MIL-STD-883, Method 3015) | > 2001V        |

| Latch-up Current                                       | > 200 mA       |

# Operating Range<sup>[2]</sup>

| Range                   | Ambient Temperature <sup>[2]</sup> | Junction Temperature | Output Condition | V <sub>cc</sub> | V <sub>cco</sub> |

|-------------------------|------------------------------------|----------------------|------------------|-----------------|------------------|

| Commercial              | 0°C to +70°C                       | 0°C to +90°C         | 5V               | 5V ± 0.25V      | 5V ± 0.25V       |

|                         |                                    |                      | 3.3V             | 5V ± 0.25V      | $3.3V\pm0.3V$    |

| Industrial              | –40°C to +85°C                     | –40°C to +105°C      | 5V               | 5V ± 0.5V       | 5V ± 0.5V        |

|                         |                                    |                      | 3.3V             | $5V \pm 0.5V$   | $3.3V\pm0.3V$    |

| Military <sup>[3]</sup> | –55°C to +125°C                    | –55°C to +130°C      | 5V               | $5V \pm 0.5V$   | 5V ± 0.5V        |

|                         |                                    |                      | 3.3V             | 5V ± 0.5V       | $3.3V\pm0.3V$    |

# **5.0V Device Electrical Characteristics** Over the Operating Range

| Parameter         | Description                                   | Test Cor                                       | nditions                                           | Min.           | Тур. | Max.        | Unit |

|-------------------|-----------------------------------------------|------------------------------------------------|----------------------------------------------------|----------------|------|-------------|------|

| V <sub>OH</sub>   | Output HIGH Voltage                           | V <sub>CC</sub> = Min.                         | $I_{OH} = -3.2 \text{ mA (Com'l/Ind)}^{[4]}$       | 2.4            |      |             | V    |

|                   |                                               |                                                | $I_{OH} = -2.0 \text{ mA } (Mil)^{[4]}$            | 2.4            |      |             | V    |

| V <sub>OHZ</sub>  | Output HIGH Voltage with                      | V <sub>CC</sub> = Max.                         | $I_{OH} = 0  \mu A  (Com'l)^{[6]}$                 |                |      | 4.2         | V    |

|                   | Output Disabled <sup>[5]</sup>                |                                                | $I_{OH} = 0 \mu A (Ind/Mil)^{[6]}$                 |                |      | 4.5         | V    |

|                   |                                               |                                                | $I_{OH} = -100  \mu A  (Com'I)^{[6]}$              |                |      | 3.6         | V    |

|                   |                                               |                                                | $I_{OH} = -150  \mu A  (Ind/Mil)^{[6]}$            |                |      | 3.6         | V    |

| $V_{OL}$          | Output LOW Voltage                            | V <sub>CC</sub> = Min.                         | I <sub>OL</sub> = 16 mA (Com'l/Ind) <sup>[4]</sup> |                |      | 0.5         | V    |

|                   |                                               |                                                | I <sub>OL</sub> = 12 mA (Mil) <sup>[4]</sup>       |                |      | 0.5         | V    |

| V <sub>IH</sub>   | Input HIGH Voltage                            | Guaranteed Input Logical HIG                   | GH Voltage for all Inputs <sup>[7]</sup>           | 2.0            |      | $V_{CCmax}$ | V    |

| $V_{IL}$          | Input LOW Voltage                             | Guaranteed Input Logical LO                    | W Voltage for all Inputs <sup>[7]</sup>            | -0.5           |      | 0.8         | V    |

| I <sub>IX</sub>   | Input Load Current                            | $V_I$ = GND OR $V_{CC}$ , Bus-Hold             | Disabled                                           | -10            |      | 10          | μА   |

| I <sub>OZ</sub>   | Output Leakage Current                        | $V_O$ = GND or $V_{CC}$ , Output Di            | sabled, Bus-Hold Disabled                          | -50            |      | 50          | μА   |

| Ios               | Output Short Circuit Current <sup>[5,8]</sup> | $V_{CC}$ = Max., $V_{OUT}$ = 0.5V              |                                                    | -30            |      | -160        | mA   |

| I <sub>BHL</sub>  | Input Bus-Hold LOW<br>Sustaining Current      | V <sub>CC</sub> = Min., V <sub>IL</sub> = 0.8V |                                                    | +75            |      |             | μА   |

| I <sub>ВНН</sub>  | Input Bus-Hold HIGH Sustaining Current        | V <sub>CC</sub> = Min., V <sub>IH</sub> = 2.0V |                                                    | <del>-75</del> |      |             | μА   |

| I <sub>BHLO</sub> | Input Bus-Hold LOW<br>Overdrive Current       | V <sub>CC</sub> = Max.                         |                                                    |                |      | +500        | μА   |

| Івнно             | Input Bus-Hold HIGH<br>Overdrive Current      | V <sub>CC</sub> = Max.                         |                                                    |                |      | -500        | μА   |

- Normal Programming Conditions apply across Ambient Temperature Range for specified programming methods. For more information on programming the Ultra37000 Family devices, please refer to the Application Note titled "An Introduction to In System Reprogramming with the Ultra37000."

- 3. TA is the "Instant On" case temperature.

- 4. I<sub>OH</sub> = -2 mA, I<sub>OL</sub> = 2 mA for TDO.

5. Tested initially and after any design or process changes that may affect these parameters.

- When the I/O is output disabled, the bus-hold circuit can weakly pull the I/O to above 3.6V if no leakage current is allowed. Note that all I/Os are output disabled during ISR programming. Refer to the application note "Understanding Bus-Hold" for additional information.

- These are absolute values with respect to device ground. All overshoots due to system or tester noise are included.

- Not more than one output should be tested at a time. Duration of the short circuit should not exceed 1 second. V<sub>OUT</sub> = 0.5V has been chosen to avoid test problems caused by tester ground degradation.

### Inductance<sup>[5]</sup>

| Parameter | Description               | Test Conditions                        | 44-<br>Lead<br>TQFP | 44-<br>Lead<br>PLCC | 44-<br>Lead<br>CLCC | 84-<br>Lead<br>PLCC | 84-<br>Lead<br>CLCC | 100-<br>Lead<br>TQFP | 160-<br>Lead<br>TQFP | 208-<br>Lead<br>PQFP | Unit |

|-----------|---------------------------|----------------------------------------|---------------------|---------------------|---------------------|---------------------|---------------------|----------------------|----------------------|----------------------|------|

|           | Maximum Pin<br>Inductance | V <sub>IN</sub> = 3.3V<br>at f = 1 MHz | 2                   | 5                   | 2                   | 8                   | 5                   | 8                    | 9                    | 11                   | nΗ   |

# Capacitance<sup>[5]</sup>

| Parameter        | Description                         | Test Conditions                                     | Max. | Unit |

|------------------|-------------------------------------|-----------------------------------------------------|------|------|

| C <sub>I/O</sub> | Input/Output Capacitance            | $V_{IN}$ = 3.3V at f = 1 MHz at $T_A$ = 25°C        | 8    | pF   |

| C <sub>CLK</sub> | Clock Signal Capacitance            | $V_{IN}$ = 3.3V at f = 1 MHz at $T_A$ = 25°C        | 12   | pF   |

| C <sub>DP</sub>  | Dual Functional Pins <sup>[9]</sup> | $V_{IN} = 3.3V$ at f = 1 MHz at $T_A = 25^{\circ}C$ | 16   | pF   |

# **Endurance Characteristics**<sup>[5]</sup>

| Parameter | Description                  | Test Conditions                              | Min.  | Тур.   | Unit   |

|-----------|------------------------------|----------------------------------------------|-------|--------|--------|

| N         | Minimum Reprogramming Cycles | Normal Programming Conditions <sup>[2]</sup> | 1,000 | 10,000 | Cycles |

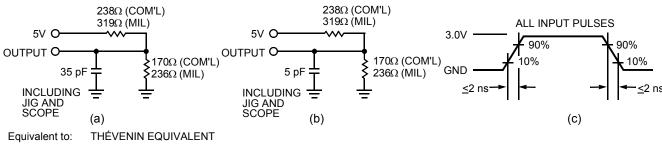

## **AC Characteristics**

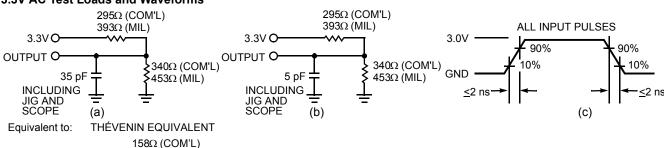

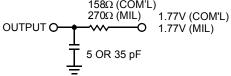

#### 5.0V AC Test Loads and Waveforms

# 3.3V AC Test Loads and Waveforms

# Ultra37000 CPLD Family

# $\textbf{Switching Characteristics} \ \, \text{Over the Operating Range (continued)}^{[12]}$

| Parameter                                  | Description                                                                                                                                                                     | Unit |

|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Product Term Clo                           | cking Parameters                                                                                                                                                                | 1    |

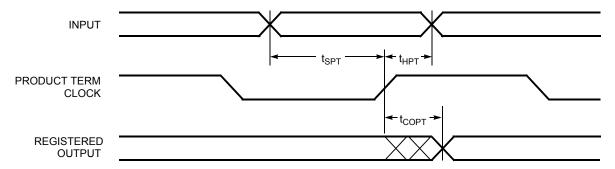

| t <sub>COPT</sub> [13, 14, 15]             | Product Term Clock or Latch Enable (PTCLK) to Output                                                                                                                            | ns   |

| t <sub>SPT</sub>                           | Set-Up Time from Input to Product Term Clock or Latch Enable (PTCLK)                                                                                                            | ns   |

| t <sub>HPT</sub>                           | Register or Latch Data Hold Time                                                                                                                                                | ns   |

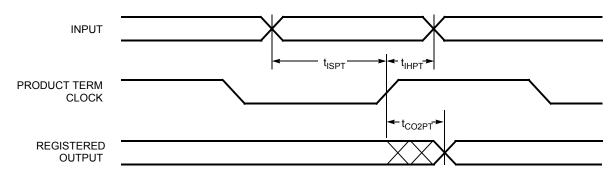

| t <sub>ISPT</sub> <sup>[13]</sup>          | Set-Up Time for Buried Register used as an Input Register from Input to Product Term Clock or Latch Enable (PTCLK)                                                              | ns   |

| t <sub>IHPT</sub>                          | Buried Register Used as an Input Register or Latch Data Hold Time                                                                                                               | ns   |

| t <sub>CO2PT</sub> <sup>[13, 14, 15]</sup> | Product Term Clock or Latch Enable (PTCLK) to Output Delay (Through Logic Array)                                                                                                | ns   |

| Pipelined Mode P                           | arameters                                                                                                                                                                       | 1    |

| t <sub>ICS</sub> <sup>[13]</sup>           | Input Register Synchronous Clock ( $CLK_0$ , $CLK_1$ , $CLK_2$ , or $CLK_3$ ) to Output Register Synchronous Clock ( $CLK_0$ , $CLK_1$ , $CLK_2$ , or $CLK_3$ )                 | ns   |

| Operating Freque                           | ncy Parameters                                                                                                                                                                  |      |

| f <sub>MAX1</sub>                          | Maximum Frequency with Internal Feedback (Lesser of $1/t_{SCS}$ , $1/(t_{S} + t_{H})$ , or $1/t_{CO}$ ) <sup>[5]</sup>                                                          | MHz  |

| f <sub>MAX2</sub>                          | Maximum Frequency Data Path in Output Registered/Latched Mode (Lesser of $1/(t_W + t_W)$ , $1/(t_S + t_H)$ , or $1/(t_{CO})^{[5]}$                                              | MHz  |

| f <sub>MAX3</sub>                          | Maximum Frequency with External Feedback (Lesser of 1/(t <sub>CO</sub> + t <sub>S</sub> ) or 1/(t <sub>WL</sub> + t <sub>WH</sub> ) <sup>[5]</sup>                              | MHz  |

| f <sub>MAX4</sub>                          | Maximum Frequency in Pipelined Mode (Lesser of 1/( $t_{CO}$ + $t_{IS}$ ), 1/ $t_{ICS}$ , 1/( $t_{WL}$ + $t_{WH}$ ), 1/( $t_{IS}$ + $t_{IH}$ ), or 1/ $t_{SCS}$ ) <sup>[5]</sup> | MHz  |

| Reset/Preset Para                          | ameters                                                                                                                                                                         |      |

| t <sub>RW</sub>                            | Asynchronous Reset Width <sup>[5]</sup>                                                                                                                                         | ns   |

| t <sub>RR</sub> <sup>[13]</sup>            | Asynchronous Reset Recovery Time <sup>[5]</sup>                                                                                                                                 | ns   |

| t <sub>RO</sub> <sup>[13, 14, 15]</sup>    | Asynchronous Reset to Output                                                                                                                                                    | ns   |

| t <sub>PW</sub>                            | Asynchronous Preset Width <sup>[5]</sup>                                                                                                                                        | ns   |

| t <sub>PR</sub> <sup>[13]</sup>            | Asynchronous Preset Recovery Time <sup>[5]</sup>                                                                                                                                | ns   |

| t <sub>PO</sub> <sup>[13, 14, 15]</sup>    | Asynchronous Preset to Output                                                                                                                                                   | ns   |

| <b>User Option Para</b>                    | meters                                                                                                                                                                          |      |

| t <sub>LP</sub>                            | Low Power Adder                                                                                                                                                                 | ns   |

| t <sub>SLEW</sub>                          | Slow Output Slew Rate Adder                                                                                                                                                     | ns   |

| t <sub>3.310</sub>                         | 3.3V I/O Mode Timing Adder <sup>[5]</sup>                                                                                                                                       | ns   |

| JTAG Timing Pa                             | rameters                                                                                                                                                                        | •    |

| t <sub>S JTAG</sub>                        | Set-up Time from TDI and TMS to TCK <sup>[5]</sup>                                                                                                                              | ns   |

| t <sub>H JTAG</sub>                        | Hold Time on TDI and TMS <sup>[5]</sup>                                                                                                                                         | ns   |

| t <sub>CO JTAG</sub>                       | Falling Edge of TCK to TDO <sup>[5]</sup>                                                                                                                                       | ns   |

| $f_{JTAG}$                                 | Maximum JTAG Tap Controller Frequency <sup>[5]</sup>                                                                                                                            | ns   |

# Switching Characteristics Over the Operating Range [12]

|                                         | 200   | MHz    | 167   | MHz   | 154  | MHz  | 143  | MHz  | 125                 | MHz                 | 100 N               | ЛHz                 | 83 M                | Hz                | 66 1 | ИHz  |      |

|-----------------------------------------|-------|--------|-------|-------|------|------|------|------|---------------------|---------------------|---------------------|---------------------|---------------------|-------------------|------|------|------|

| Parameter                               | Min.  | Мах.   | Min.  | Мах.  | Min. | Мах. | Min. | Мах. | Min.                | Мах.                | Min.                | Мах.                | Min.                | Мах.              | Min. | Мах. | Unit |

| Combinatorial                           | Mod   | e Para | amete | rs    |      |      |      |      |                     |                     |                     |                     |                     |                   |      |      | •    |

| t <sub>PD</sub> <sup>[13, 14, 15]</sup> |       | 6      |       | 6.5   |      | 7.5  |      | 8.5  |                     | 10                  |                     | 12                  |                     | 15                |      | 20   | ns   |

| t <sub>PDL</sub> [13, 14, 15]           |       | 11     |       | 12.5  |      | 14.5 |      | 16   |                     | 16.5                |                     | 17                  |                     | 19                |      | 22   | ns   |

| t <sub>PDI I</sub> [13, 14, 15]         |       | 12     |       | 13.5  |      | 15.5 |      | 17   |                     | 17.5                |                     | 18                  |                     | 20                |      | 24   | ns   |

| t <sub>EA</sub> <sup>[13, 14, 15]</sup> |       | 8      |       | 8.5   |      | 11   |      | 13   |                     | 14                  |                     | 16                  |                     | 19                |      | 24   | ns   |

| t <sub>ER</sub> <sup>[11, 13]</sup>     |       | 8      |       | 8.5   |      | 11   |      | 13   |                     | 14                  |                     | 16                  |                     | 19                |      | 24   | ns   |

| Input Register                          | Para  | meter  | s     |       |      |      |      | •    |                     |                     |                     |                     |                     | •                 |      |      |      |

| t <sub>WL</sub>                         | 2.5   |        | 2.5   |       | 2.5  |      | 2.5  |      | 3                   |                     | 3                   |                     | 4                   |                   | 5    |      | ns   |

| t <sub>WH</sub>                         | 2.5   |        | 2.5   |       | 2.5  |      | 2.5  |      | 3                   |                     | 3                   |                     | 4                   |                   | 5    |      | ns   |

| t <sub>IS</sub>                         | 2     |        | 2     |       | 2    |      | 2    |      | 2                   |                     | 2.5                 |                     | 3                   |                   | 4    |      | ns   |

| t <sub>IH</sub>                         | 2     |        | 2     |       | 2    |      | 2    |      | 2                   |                     | 2.5                 |                     | 3                   |                   | 4    |      | ns   |

| t <sub>ICO</sub> [13, 14, 15]           |       | 11     |       | 11    |      | 11   |      | 12.5 |                     | 12.5                |                     | 16                  |                     | 19                |      | 24   | ns   |

| t <sub>ICOL</sub> [13, 14, 15]          |       | 12     |       | 12    |      | 12   |      | 14   |                     | 16                  |                     | 18                  |                     | 21                |      | 26   | ns   |

| Synchronous                             | Clock | king P | aram  | eters |      |      |      |      | •                   |                     |                     |                     |                     |                   |      |      | •    |

| t <sub>CO</sub> [14, 15]                |       | 4      |       | 4     |      | 4.5  |      | 6    |                     | 6.5 <sup>[16]</sup> |                     | 6.5 <sup>[17]</sup> |                     | 8 <sup>[18]</sup> |      | 10   | ns   |

| t <sub>S</sub> <sup>[13]</sup>          | 4     |        | 4     |       | 5    |      | 5    |      | 5.5 <sup>[16]</sup> |                     | 6 <sup>[17]</sup>   |                     | 8 <sup>[18]</sup>   |                   | 10   |      | ns   |

| t <sub>H</sub>                          | 0     |        | 0     |       | 0    |      | 0    |      | 0                   |                     | 0                   |                     | 0                   |                   | 0    |      | ns   |

| t <sub>CO2</sub> [13, 14, 15]           |       | 9.5    |       | 10    |      | 11   |      | 12   |                     | 14                  |                     | 16                  |                     | 19                |      | 24   | ns   |

| t <sub>SCS</sub> <sup>[13]</sup>        | 5     |        | 6     |       | 6.5  |      | 7    |      | 8 <sup>[16]</sup>   |                     | 10                  |                     | 12                  |                   | 15   |      | ns   |

| t <sub>SL</sub> <sup>[13]</sup>         | 7.5   |        | 7.5   |       | 8.5  |      | 9    |      | 10                  |                     | 12                  |                     | 15                  |                   | 15   |      | ns   |

| t <sub>HL</sub>                         | 0     |        | 0     |       | 0    |      | 0    |      | 0                   |                     | 0                   |                     | 0                   |                   | 0    |      | ns   |

| Product Term                            | Clock | king P | aram  | eters |      |      |      | •    |                     |                     |                     |                     |                     | •                 |      |      |      |

| t <sub>COPT</sub> [13, 14, 15]          |       | 7      |       | 10    |      | 10   |      | 13   |                     | 13                  |                     | 13                  |                     | 15                |      | 20   | ns   |

| t <sub>SPT</sub>                        | 2.5   |        | 2.5   |       | 2.5  |      | 3    |      | 5                   |                     | 5.5                 |                     | 6                   |                   | 7    |      | ns   |

| t <sub>HPT</sub>                        | 2.5   |        | 2.5   |       | 2.5  |      | 3    |      | 5                   |                     | 5.5                 |                     | 6                   |                   | 7    |      | ns   |

| t <sub>ISPT</sub> <sup>[13]</sup>       | 0     |        | 0     |       | 0    |      | 0    |      | 0                   |                     | 0                   |                     | 0                   |                   | 0    |      | ns   |

| t <sub>IHPT</sub>                       | 6     |        | 6.5   |       | 6.5  |      | 7.5  |      | 9                   |                     | 11                  |                     | 14                  |                   | 19   |      | ns   |

| t <sub>CO2PT</sub> [13, 14, 15]         |       | 12     |       | 14    |      | 15   |      | 19   |                     | 19                  |                     | 21                  |                     | 24                |      | 30   | ns   |

| Pipelined Mo                            | de Pa | rame   | ters  |       |      |      |      | I    | <u>I</u>            |                     |                     |                     |                     | I                 |      |      | 1    |

| t <sub>ICS</sub> <sup>[13]</sup>        | 5     |        | 6     |       | 6    |      | 7    |      | 8 <sup>[16]</sup>   |                     | 10                  |                     | 12                  |                   | 15   |      | ns   |

| Operating Free                          |       | cy Pa  |       | ers   |      |      |      |      |                     |                     |                     |                     |                     |                   |      |      |      |

| f <sub>MAX1</sub>                       | 200   |        | 167   |       | 154  |      | 143  |      | 125 <sup>[16]</sup> |                     | 100                 |                     | 83                  |                   | 66   |      | MHz  |

| f <sub>MAX2</sub>                       | 200   |        | 200   |       | 200  |      | 167  |      | 154                 |                     | 153 <sup>[17]</sup> |                     | 125 <sup>[18]</sup> |                   | 100  |      | MHz  |

| f <sub>MAX3</sub>                       | 125   |        | 125   |       | 105  |      | 91   |      | 83                  |                     | 80 <sup>[17]</sup>  |                     | 62.5                |                   | 50   |      | MHz  |

| f <sub>MAX4</sub>                       | 167   |        | 167   |       | 154  |      | 125  |      | 118                 |                     | 100                 |                     | 83                  |                   | 66   |      | MHz  |

| Reset/Preset F                          | aram  | neters |       |       |      |      |      |      |                     |                     |                     |                     |                     |                   |      |      |      |

| t <sub>RW</sub>                         | 8     |        | 8     |       | 8    |      | 8    |      | 10                  |                     | 12                  |                     | 15                  |                   | 20   |      | ns   |

| t <sub>RR</sub> <sup>[13]</sup>         | 10    |        | 10    |       | 10   |      | 10   |      | 12                  |                     | 14                  |                     | 17                  |                   | 22   |      | ns   |

| Notes:                                  |       |        |       |       |      |      |      | -    |                     |                     |                     |                     |                     | -                 |      |      |      |

<sup>16.</sup> The following values correspond to the CY37512 and CY37384 devices:  $t_{\rm CO}$  = 5 ns,  $t_{\rm SCS}$  = 8.5 ns,  $t_{\rm ICS}$  = 8.5 n

# Switching Waveforms (continued)

# Registered Output with Product Term Clocking Input Going Through the Array

# Registered Output with Product Term Clocking Input Coming From Adjacent Buried Register

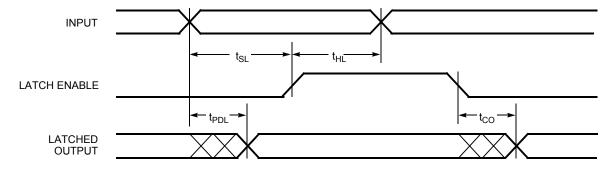

## **Latched Output**

# Switching Waveforms (continued)

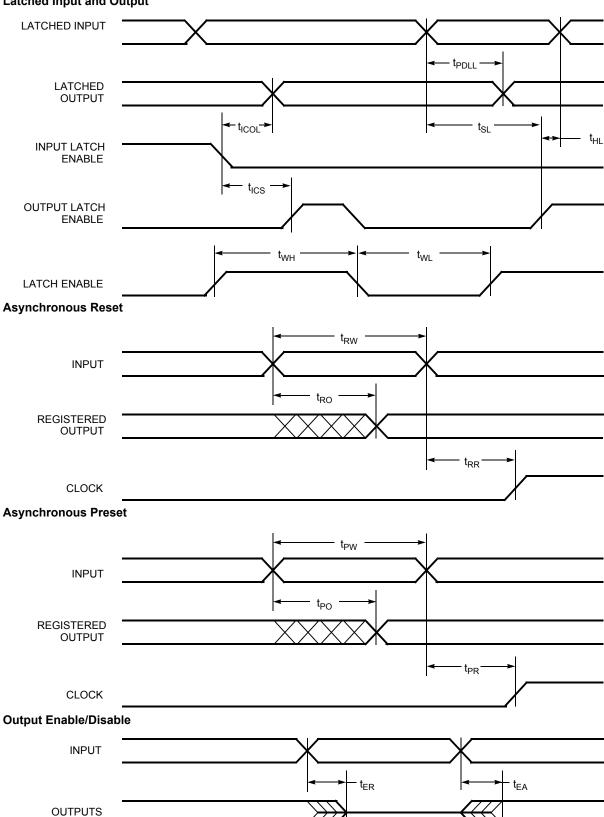

# **Latched Input and Output**

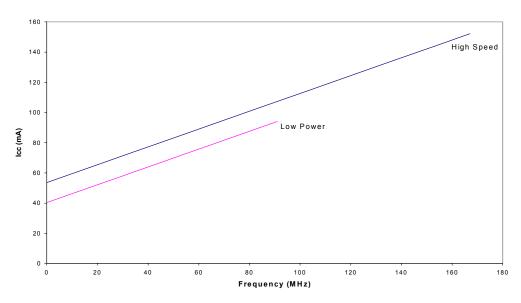

# **Typical 5.0V Power Consumption** (continued) **CY37128**

The typical pattern is a 16-bit up counter, per logic block, with outputs disabled.  $V_{CC} = 5.0V,\, T_A = Room\, Temperature$

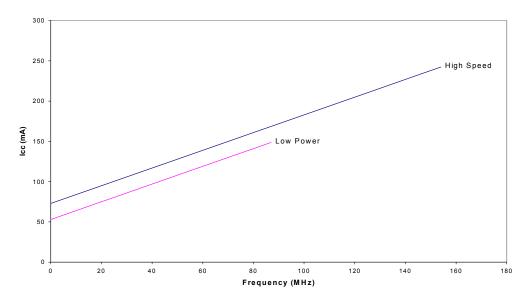

### CY37192

The typical pattern is a 16-bit up counter, per logic block, with outputs disabled.  $V_{CC}$  = 5.0V,  $T_A$  = Room Temperature

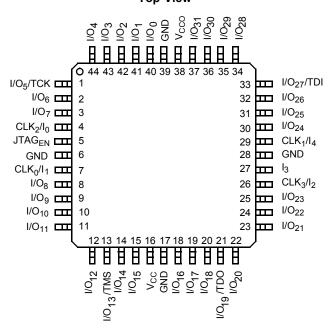

# 44-pin TQFP (A44) Top View

# 44-pin PLCC (J67) / CLCC (Y67) Top View

Pin Configurations<sup>[20]</sup> (continued)

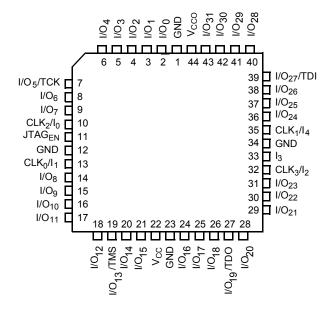

## 160-Lead TQFP (A160) / CQFP (U162) for CY37128(V) and CY37256(V) Top View

Pin Configurations<sup>[20]</sup> (continued)

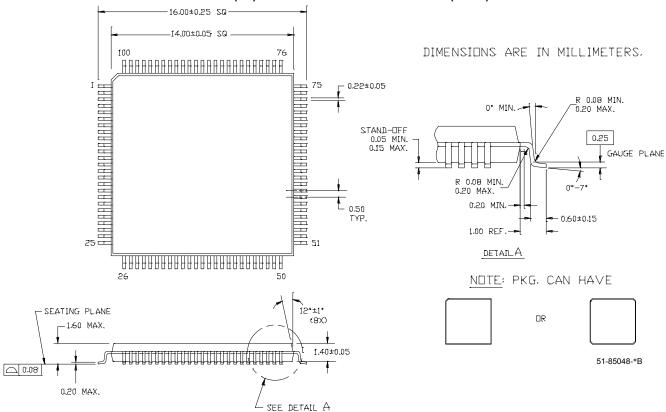

# 256-Ball Fine-Pitch BGA (BB256) Top View

|   | 1                 | 2                 | 3                 | 4                 | 5                                   | 6                 | 7                 | 8                 | 9                  | 10                 | 11                 | 12                                  | 13                 | 14                 | 15                 | 16                 |

|---|-------------------|-------------------|-------------------|-------------------|-------------------------------------|-------------------|-------------------|-------------------|--------------------|--------------------|--------------------|-------------------------------------|--------------------|--------------------|--------------------|--------------------|

| Α | GND               | GND               | I/O <sub>26</sub> | I/O <sub>24</sub> | I/O <sub>20</sub>                   | V <sub>CC</sub>   | I/O <sub>11</sub> | GND               | GND                | I/O <sub>186</sub> | V <sub>CC</sub>    | I/O <sub>177</sub>                  | I/O <sub>172</sub> | I/O <sub>167</sub> | GND                | GND                |

| В | GND               | I/O <sub>27</sub> | I/O <sub>25</sub> | I/O <sub>23</sub> | I/O <sub>19</sub>                   | I/O <sub>15</sub> | I/O <sub>10</sub> | GND               | GND                | I/O <sub>185</sub> | I/O <sub>181</sub> | I/O <sub>176</sub>                  | I/O <sub>171</sub> | I/O <sub>166</sub> | I/O <sub>165</sub> | GND                |

| С | I/O <sub>29</sub> | I/O <sub>28</sub> | NC                | I/O <sub>22</sub> | I/O <sub>18</sub>                   | I/O <sub>14</sub> | I/O <sub>9</sub>  | I/O <sub>4</sub>  | I/O <sub>191</sub> | I/O <sub>184</sub> | I/O <sub>180</sub> | I/O <sub>175</sub>                  | I/O <sub>170</sub> | NC                 | I/O <sub>163</sub> | I/O <sub>164</sub> |

| D | I/O <sub>32</sub> | I/O <sub>31</sub> | I/O <sub>30</sub> | NC                | I/O <sub>17</sub>                   | I/O <sub>13</sub> | I/O <sub>8</sub>  | I/O <sub>3</sub>  | I/O <sub>190</sub> | I/O <sub>183</sub> | I/O <sub>179</sub> | I/O <sub>174</sub>                  | I/O <sub>169</sub> | I/O <sub>160</sub> | I/O <sub>161</sub> | I/O <sub>162</sub> |

| E | I/O <sub>35</sub> | I/O <sub>34</sub> | I/O <sub>33</sub> | I/O <sub>21</sub> | I/O <sub>16</sub>                   | I/O <sub>12</sub> | I/O <sub>7</sub>  | I/O <sub>2</sub>  | I/O <sub>189</sub> | V <sub>CC</sub>    | I/O <sub>178</sub> | I/O <sub>173</sub>                  | I/O <sub>168</sub> | I/O <sub>157</sub> | I/O <sub>158</sub> | I/O <sub>159</sub> |

| F | V <sub>CC</sub>   | I/O <sub>38</sub> | I/O <sub>37</sub> | I/O <sub>36</sub> | TCK                                 | V <sub>CC</sub>   | I/O <sub>6</sub>  | I/O <sub>1</sub>  | I/O <sub>188</sub> | I/O <sub>182</sub> | V <sub>CC</sub>    | TDI                                 | I/O <sub>154</sub> | I/O <sub>155</sub> | I/O <sub>156</sub> | V <sub>CC</sub>    |

| G | I/O <sub>43</sub> | I/O <sub>42</sub> | I/O <sub>41</sub> | I/O <sub>40</sub> | V <sub>CC</sub>                     | I/O <sub>39</sub> | I/O <sub>5</sub>  | I/O <sub>0</sub>  | I/O <sub>187</sub> | I/O <sub>148</sub> | I/O <sub>149</sub> | CLK <sub>3</sub><br>/I <sub>4</sub> | I/O <sub>150</sub> | I/O <sub>151</sub> | I/O <sub>152</sub> | I/O <sub>153</sub> |

| Н | GND               | GND               | I/O <sub>47</sub> | I/O <sub>46</sub> | CLK <sub>0</sub><br>/I <sub>0</sub> | I/O <sub>45</sub> | I/O <sub>44</sub> | GND               | GND                | I/O <sub>144</sub> | I/O <sub>145</sub> | CLK <sub>2</sub><br>/I <sub>3</sub> | I/O <sub>146</sub> | I/O <sub>147</sub> | GND                | GND                |

| J | GND               | GND               | I/O <sub>51</sub> | I/O <sub>50</sub> | NC                                  | I/O <sub>49</sub> | I/O <sub>48</sub> | GND               | GND                | I/O <sub>140</sub> | I/O <sub>141</sub> | l <sub>2</sub>                      | I/O <sub>142</sub> | I/O <sub>143</sub> | GND                | GND                |

| K | I/O <sub>57</sub> | I/O <sub>56</sub> | I/O <sub>55</sub> | I/O <sub>54</sub> | CLK <sub>1</sub>                    | I/O <sub>53</sub> | I/O <sub>52</sub> | I/O <sub>91</sub> | I/O <sub>96</sub>  | I/O <sub>101</sub> | I/O <sub>135</sub> | V <sub>CC</sub>                     | I/O <sub>136</sub> | I/O <sub>137</sub> | I/O <sub>138</sub> | I/O <sub>139</sub> |

| L | V <sub>CC</sub>   | I/O <sub>60</sub> | I/O <sub>59</sub> | I/O <sub>58</sub> | TMS                                 | V <sub>CC</sub>   | I/O <sub>86</sub> | I/O <sub>92</sub> | I/O <sub>97</sub>  | I/O <sub>102</sub> | V <sub>CC</sub>    | TDO                                 | I/O <sub>132</sub> | I/O <sub>133</sub> | I/O <sub>134</sub> | V <sub>CC</sub>    |

| M | I/O <sub>63</sub> | I/O <sub>62</sub> | I/O <sub>61</sub> | I/O <sub>72</sub> | I/O <sub>77</sub>                   | I/O <sub>82</sub> | V <sub>CC</sub>   | I/O <sub>93</sub> | I/O <sub>98</sub>  | I/O <sub>103</sub> | I/O <sub>108</sub> | I/O <sub>112</sub>                  | I/O <sub>117</sub> | I/O <sub>129</sub> | I/O <sub>130</sub> | I/O <sub>131</sub> |

| N | I/O <sub>66</sub> | I/O <sub>65</sub> | I/O <sub>64</sub> | I/O <sub>73</sub> | I/O <sub>78</sub>                   | I/O <sub>83</sub> | I/O <sub>87</sub> | I/O <sub>94</sub> | I/O <sub>99</sub>  | I/O <sub>104</sub> | I/O <sub>109</sub> | I/O <sub>113</sub>                  | NC                 | I/O <sub>126</sub> | I/O <sub>127</sub> | I/O <sub>128</sub> |

| Р | I/O <sub>68</sub> | I/O <sub>67</sub> | NC                | I/O <sub>74</sub> | I/O79                               | I/O <sub>84</sub> | I/O <sub>88</sub> | I/O <sub>95</sub> | I/O <sub>100</sub> | I/O <sub>105</sub> | I/O <sub>110</sub> | I/O <sub>114</sub>                  | I/O <sub>118</sub> | NC                 | I/O <sub>124</sub> | I/O <sub>125</sub> |

| R | GND               | I/O <sub>69</sub> | I/O <sub>70</sub> | I/O <sub>75</sub> | I/O <sub>80</sub>                   | I/O <sub>85</sub> | I/O <sub>89</sub> | GND               | GND                | I/O <sub>106</sub> | I/O <sub>111</sub> | I/O <sub>115</sub>                  | I/O <sub>119</sub> | I/O <sub>121</sub> | I/O <sub>123</sub> | GND                |

| Т | GND               | GND               | I/O <sub>71</sub> | I/O <sub>76</sub> | I/O <sub>81</sub>                   | V <sub>CC</sub>   | I/O <sub>90</sub> | GND               | GND                | I/O <sub>107</sub> | V <sub>CC</sub>    | I/O <sub>116</sub>                  | I/O <sub>120</sub> | I/O <sub>122</sub> | GND                | GND                |

# Ultra37000 CPLD Family

# 5.0V Ordering Information (continued)

| Macrocells | Speed<br>(MHz) | Ordering Code      | Package<br>Name | Package Type                                  | Operating<br>Range |

|------------|----------------|--------------------|-----------------|-----------------------------------------------|--------------------|

| 128        | 167            | CY37128P84-167JC   | J83             | 84-Lead Plastic Leaded Chip Carrier           | Commercial         |

|            |                | CY37128P84-167JXC  | J83             | 84-Lead Lead Free Plastic Leaded Chip Carrier | 1                  |

|            |                | CY37128P100-167AC  | A100            | 100-Lead Thin Quad Flat Pack                  |                    |

|            |                | CY37128P100-167AXC | A100            | 100-Lead Lead Free Thin Quad Flat Pack        |                    |

|            |                | CY37128P160-167AC  | A160            | 160-Lead Thin Quad Flat Pack                  |                    |

|            |                | CY37128P160-167AXC | A160            | 160-Lead Lead Free Thin Quad Flat Pack        |                    |

|            | 125            | CY37128P84-125JC   | J83             | 84-Lead Plastic Leaded Chip Carrier           | Commercia          |

|            |                | CY37128P84-125JXC  | J83             | 84-Lead Lead Free Plastic Leaded Chip Carrier |                    |

|            |                | CY37128P100-125AC  | A100            | 100-Lead Thin Quad Flat Pack                  |                    |

|            |                | CY37128P100-125AXC | A100            | 100-Lead Lead Free Thin Quad Flat Pack        |                    |

|            |                | CY37128P160-125AC  | A160            | 160-Lead Thin Quad Flat Pack                  |                    |

|            |                | CY37128P160-125AXC | A160            | 160-Lead Lead Free Thin Quad Flat Pack        |                    |

|            |                | CY37128P84-125JI   | J83             | 84-Lead Plastic Leaded Chip Carrier           | Industrial         |

|            |                | CY37128P84-125JXI  | J83             | 84-Lead Lead Free Plastic Leaded Chip Carrier |                    |

|            |                | CY37128P100-125AI  | A100            | 100-Lead Thin Quad Flat Pack                  |                    |

|            |                | CY37128P100-125AXI | A100            | 100-Lead Lead Free Thin Quad Flat Pack        | 1                  |

|            |                | CY37128P160-125AI  | A160            | 160-Lead Thin Quad Flat Pack                  | 1                  |

|            |                | CY37128P160-125AXI | A160            | 160-Lead Lead Free Thin Quad Flat Pack        | 1                  |

|            |                | 5962-9952102QYA    | Y84             | 84-Lead Ceramic Leaded Chip Carrier           | Military           |

|            | 100            | CY37128P84-100JC   | J83             | 84-Lead Plastic Leaded Chip Carrier           | Commercia          |

|            |                | CY37128P84-100JXC  | J83             | 84-Lead Lead Free Plastic Leaded Chip Carrier | 1                  |

|            |                | CY37128P100-100AC  | A100            | 100-Lead Thin Quad Flat Pack                  | +                  |

|            |                | CY37128P100-100AXC | A100            | 100-Lead Lead Free Thin Quad Flat Pack        | 1                  |

|            |                | CY37128P160-100AC  | A160            | 160-Lead Thin Quad Flat Pack                  | +                  |

|            |                | CY37128P160-100AXC | A160            | 160-Lead Lead Free Thin Quad Flat Pack        | =                  |

|            |                | CY37128P84-100JI   | J83             | 84-Lead Plastic Leaded Chip Carrier           | Industrial         |

|            |                | CY37128P100-100AI  | A100            | 100-Lead Thin Quad Flat Pack                  | =                  |

|            |                | CY37128P100-100AXI | A100            | 100-Lead Lead Free Thin Quad Flat Pack        | =                  |

|            |                | CY37128P160-100AI  | A160            | 160-Lead Thin Quad Flat Pack                  |                    |

|            |                | 5962-9952101QYA    | Y84             | 84-Lead Ceramic Leaded Chip Carrier           | Military           |

| 192        | 154            | CY37192P160-154AC  | A160            | 160-Lead Thin Quad Flat Pack                  | Commercia          |

| -          |                | CY37192P160-154AXC | A160            | 160-Lead Lead Free Thin Quad Flat Pack        |                    |

|            | 125            | CY37192P160-125AC  | A160            | 160-Lead Thin Quad Flat Pack                  | Commercia          |

|            |                | CY37192P160-125AXC | A160            | 160-Lead Lead Free Thin Quad Flat Pack        | +                  |

|            |                | CY37192P160-125AI  | A160            | 160-Lead Thin Quad Flat Pack                  | Industrial         |

|            |                | CY37192P160-125AXI | A160            | 160-Lead Lead Free Thin Quad Flat Pack        | 1                  |

|            | 83             | CY37192P160-83AC   | A160            | 160-Lead Thin Quad Flat Pack                  | Commercia          |

|            | -              | CY37192P160-83AXC  | A160            | 160-Lead Lead Free Thin Quad Flat Pack        | †                  |

|            |                | CY37192P160-83AI   | A160            | 160-Lead Thin Quad Flat Pack                  | Industrial         |

|            |                | CY37192P160-83AXI  | A160            | 160-Lead Lead Free Thin Quad Flat Pack        | +                  |

# Ultra37000 CPLD Family

# 3.3V Ordering Information (continued)

| Macrocells | Speed<br>(MHz) | Ordering Code       | Package<br>Name | Package Type                           | Operating<br>Range |  |  |

|------------|----------------|---------------------|-----------------|----------------------------------------|--------------------|--|--|

| 64         | 143            | CY37064VP44-143AC   | A44             | 44-Lead Thin Quad Flatpack             | Commercia          |  |  |

|            |                | CY37064VP44-143AXC  | A44             | 44-Lead Lead Free Thin Quad Flatpack   |                    |  |  |

|            |                | CY37064VP48-143BAC  | BA50            | 48-Ball Fine-Pitch Ball Grid Array     |                    |  |  |

|            |                | CY37064VP100-143AC  | A100            | 100-Lead Thin Quad Flatpack            |                    |  |  |

|            |                | CY37064VP100-143AXC | A100            | 100-Lead Lead Free Thin Quad Flatpack  |                    |  |  |

|            |                | CY37064VP100-143BBC | BB100           | 100-Ball Fine-Pitch Ball Grid Array    |                    |  |  |

|            | 100            | CY37064VP44-100AC   | A44             | 44-Lead Thin Quad Flatpack             | Commercia          |  |  |

|            |                | CY37064VP44-100AXC  | A44             | 44-Lead Lead Free Thin Quad Flatpack   |                    |  |  |

|            |                | CY37064VP48-100BAC  | BA50            | 48-Ball Fine-Pitch Ball Grid Array     |                    |  |  |

|            |                | CY37064VP100-100AC  | A100            | 100-Lead Thin Quad Flatpack            |                    |  |  |

|            |                | CY37064VP100-100AXC | A100            | 100-Lead Lead Free Thin Quad Flatpack  |                    |  |  |

|            |                | CY37064VP100-100BBC | BB100           | 100-Ball Fine-Pitch Ball Grid Array    |                    |  |  |

|            |                | CY37064VP44-100AI   | A44             | 44-Lead Thin Quad Flatpack             | Industrial         |  |  |

|            |                | CY37064VP44-100AXI  | A44             | 44-Lead Lead Free Thin Quad Flatpack   |                    |  |  |

|            |                | CY37064VP48-100BAI  | BA50            | 48-Ball Fine-Pitch Ball Grid Array     |                    |  |  |

|            |                | CY37064VP100-100BBI | BB100           | 100-Ball Fine-Pitch Ball Grid Array    |                    |  |  |

|            |                | CY37064VP100-100AI  | A100            | 100-Lead Thin Quad Flatpack            |                    |  |  |

|            |                | CY37064VP100-100AXI | A100            | 100-Lead Lead Free Thin Quad Flatpack  |                    |  |  |

|            |                | 5962-9952001QYA     | Y67             | 44-Lead Ceramic Leaded Chip Carrier    | Military           |  |  |

| 128        | 125            | CY37128VP100-125AC  | A100            | 100-Lead Thin Quad Flat Pack           | Commercia          |  |  |

|            |                | CY37128VP100-125AXC | A100            | 100-Lead Lead Free Thin Quad Flat Pack |                    |  |  |

|            |                | CY37128VP100-125BBC | BB100           | 100-Ball Fine-Pitch Ball Grid Array    |                    |  |  |

|            |                | CY37128VP160-125AC  | A160            | 160-Lead Thin Quad Flat Pack           |                    |  |  |

|            |                | CY37128VP160-125AXC | A160            | 160-Lead Lead Free Thin Quad Flat Pack |                    |  |  |

|            |                | CY37128VP160-125AI  | A160            | 160-Lead Thin Quad Flat Pack           | Industrial         |  |  |

|            |                | CY37128VP160-125AXI | A160            | 160-Lead Lead Free Thin Quad Flat Pack |                    |  |  |

|            | 83             | CY37128VP100-83AC   | A100            | 100-Lead Thin Quad Flat Pack           | Commercia          |  |  |

|            |                | CY37128VP100-83AXC  | A100            | 100-Lead Lead Free Thin Quad Flat Pack |                    |  |  |

|            |                | CY37128VP100-83BBC  | BB100           | 100-Ball Fine-Pitch Ball Grid Array    |                    |  |  |

|            |                | CY37128VP160-83AC   | A160            | 160-Lead Thin Quad Flat Pack           |                    |  |  |

|            |                | CY37128VP160-83AXC  | A160            | 160-Lead Lead Free Thin Quad Flat Pack |                    |  |  |

|            |                | CY37128VP100-83AI   | A100            | 100-Lead Thin Quad Flat Pack           | Industrial         |  |  |

|            |                | CY37128VP100-83AXI  | A100            | 100-Lead Lead Free Thin Quad Flat Pack |                    |  |  |

|            |                | CY37128VP100-83BBI  | BB100           | 100-Ball Fine-Pitch Ball Grid Array    |                    |  |  |

|            |                | CY37128VP160-83AI   | A160            | 160-Lead Thin Quad Flat Pack           |                    |  |  |

|            |                | CY37128VP160-83AXI  | A160            | 160-Lead Lead Free Thin Quad Flat Pack |                    |  |  |

|            |                | 5962-9952201QYA     | Y84             | 84-Lead Ceramic Leaded Chip Carrier    | Military           |  |  |

| 192        | 100            | CY37192VP160-100AC  | A160            | 160-Lead Thin Quad Flat Pack           | Commercia          |  |  |

|            |                | CY37192VP160-100AXC | A160            | 160-Lead Lead Free Thin Quad Flat Pack |                    |  |  |

|            | 66             | CY37192VP160-66AC   |                 |                                        |                    |  |  |

|            |                | CY37192VP160-66AXC  | A160            | 160-Lead Lead Free Thin Quad Flat Pack | Commercia          |  |  |

|            |                | CY37192VP160-66AI   | A160            | 160-Lead Thin Quad Flat Pack           | Industrial         |  |  |

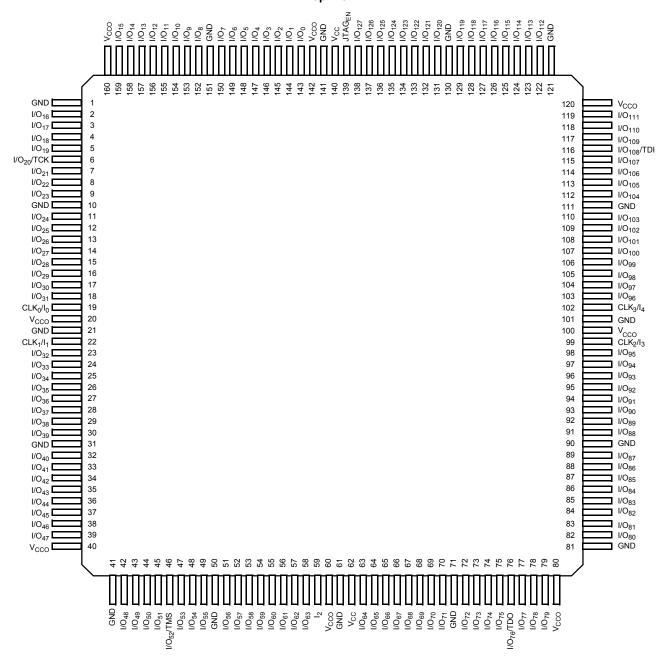

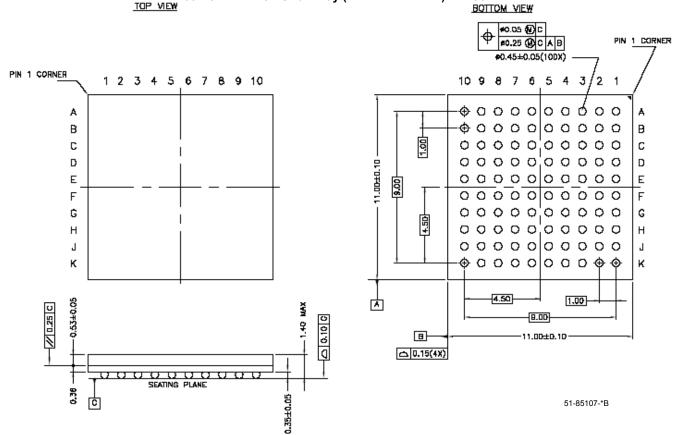

# 100-Lead Lead (Pb)-Free Thin Plastic Quad Flat Pack (TQFP) A100

# 100-Ball Thin Ball Grid Array (11 x 11 x 1.4 mm) BB100

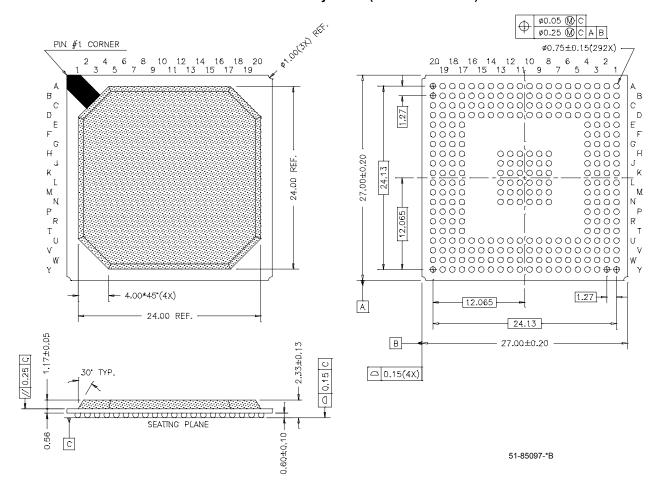

# 292-Ball Plastic Ball Grid Array PBGA (27 x 27 x 2.33 mm) BG292

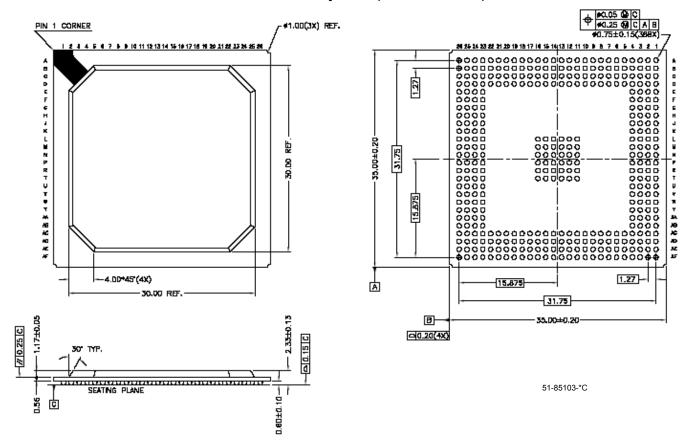

## 388-Ball Plastic Ball Grid Array PBGA (35 x 35 x 2.33 mm) BG388

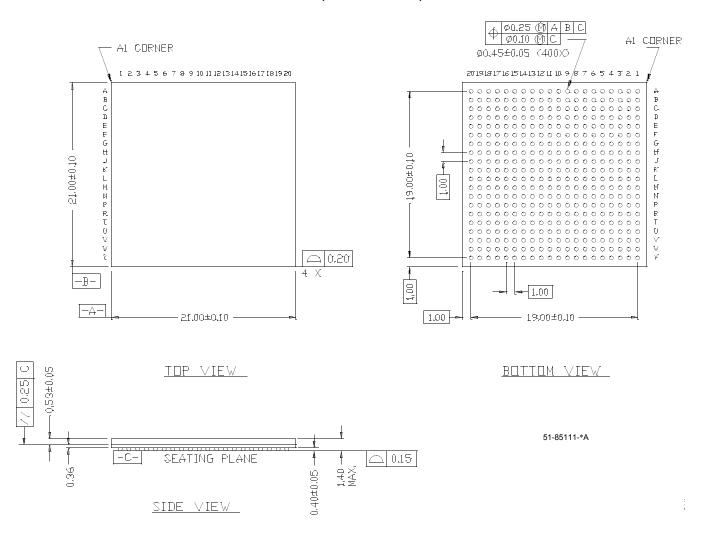

### 400-Ball FBGA (21 x 21 x 1.4 mm) BB400

ViewDraw and SpeedWave are trademarks of ViewLogic. Windows is a registered trademark of Microsoft Corporation. *Warp* is a registered trademark, and In-System Reprogrammable, ISR, *Warp* Professional, *Warp* Enterprise, and Ultra37000 are trademarks, of Cypress Semiconductor Corporation. All product and company names mentioned in this document are the trademarks of their respective holders.

# Addendum

# 3.3V Operating Range

(CY37064VP100-143AC, CY37064VP100-143BBC, CY37064VP44-143AC, CY37064VP48-143BAC)

| Range      | Ambient Temperature <sup>[2]</sup> | Junction Temperature | V <sub>CC</sub> |

|------------|------------------------------------|----------------------|-----------------|

| Commercial | 0°C to +70°C                       | 0°C to +90°C         | 3.3V ± 0.16V    |