Welcome to **E-XFL.COM**

**Understanding Embedded - CPLDs (Complex Programmable Logic Devices)**

Embedded - CPLDs, or Complex Programmable Logic Devices, are highly versatile digital logic devices used in electronic systems. These programmable components are designed to perform complex logical operations and can be customized for specific applications. Unlike fixed-function ICs, CPLDs offer the flexibility to reprogram their configuration, making them an ideal choice for various embedded systems. They consist of a set of logic gates and programmable interconnects, allowing designers to implement complex logic circuits without needing custom hardware.

#### **Applications of Embedded - CPLDs**

| Details                         |                                                                                |

|---------------------------------|--------------------------------------------------------------------------------|

| Product Status                  | Obsolete                                                                       |

| Programmable Type               | In-System Reprogrammable™ (ISR™) CMOS                                          |

| Delay Time tpd(1) Max           | 12 ns                                                                          |

| Voltage Supply - Internal       | 3V ~ 3.6V                                                                      |

| Number of Logic Elements/Blocks | -                                                                              |

| Number of Macrocells            | 256                                                                            |

| Number of Gates                 | -                                                                              |

| Number of I/O                   | 133                                                                            |

| Operating Temperature           | -40°C ~ 85°C (TA)                                                              |

| Mounting Type                   | Surface Mount                                                                  |

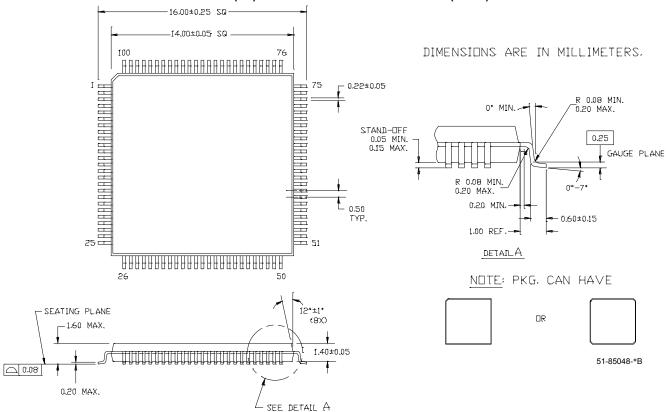

| Package / Case                  | 160-LQFP                                                                       |

| Supplier Device Package         | 160-TQFP (24x24)                                                               |

| Purchase URL                    | https://www.e-xfl.com/product-detail/infineon-technologies/cy37256vp160-100axi |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Selection Guide**

# 5.0V Selection Guide

#### General Information

| Device  | Macrocells | Dedicated Inputs | I/O Pins    | Speed (t <sub>PD</sub> ) | Speed (f <sub>MAX</sub> ) |

|---------|------------|------------------|-------------|--------------------------|---------------------------|

| CY37032 | 32         | 5                | 32          | 6                        | 200                       |

| CY37064 | 64         | 5                | 32/64       | 6                        | 200                       |

| CY37128 | 128        | 5                | 64/128      | 6.5                      | 167                       |

| CY37192 | 192        | 5                | 120         | 7.5                      | 154                       |

| CY37256 | 256        | 5                | 128/160/192 | 7.5                      | 154                       |

| CY37384 | 384        | 5                | 160/192     | 10                       | 118                       |

| CY37512 | 512        | 5                | 160/192/264 | 10                       | 118                       |

# Speed Bins

| Device  | 200 | 167 | 154 | 143 | 125 | 100 | 83 | 66 |

|---------|-----|-----|-----|-----|-----|-----|----|----|

| CY37032 | Х   |     | Х   |     | Х   |     |    |    |

| CY37064 | Х   |     | Х   |     | Х   |     |    |    |

| CY37128 |     | Х   |     |     | Х   | Х   |    |    |

| CY37192 |     |     | Х   |     | Х   |     | Х  |    |

| CY37256 |     |     | Х   |     | Х   |     | Х  |    |

| CY37384 |     |     |     |     | Х   |     | Х  |    |

| CY37512 |     |     |     |     | Х   | Х   | Х  |    |

# Device-Package Offering and I/O Count

| Device  | 44-<br>Lead<br>TQFP | 44-<br>Lead<br>PLCC | 44-<br>Lead<br>CLCC | 84-<br>Lead<br>PLCC | 84-<br>Lead<br>CLCC | 100-<br>Lead<br>TQFP | 160-<br>Lead<br>TQFP | 160-<br>Lead<br>CQFP | 208-<br>Lead<br>PQFP | 208-<br>Lead<br>CQFP | 292-<br>Lead<br>PBGA | 388-<br>Lead<br>PBGA |

|---------|---------------------|---------------------|---------------------|---------------------|---------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| CY37032 | 37                  | 37                  |                     |                     |                     |                      |                      |                      |                      |                      |                      |                      |

| CY37064 | 37                  | 37                  | 37                  | 69                  |                     | 69                   |                      |                      |                      |                      |                      |                      |

| CY37128 |                     |                     |                     | 69                  | 69                  | 69                   | 133                  |                      |                      |                      |                      |                      |

| CY37192 |                     |                     |                     |                     |                     |                      | 125                  |                      |                      |                      |                      |                      |

| CY37256 |                     |                     |                     |                     |                     |                      | 133                  | 133                  | 165                  |                      | 197                  |                      |

| CY37384 |                     |                     |                     |                     |                     |                      |                      |                      | 165                  |                      | 197                  |                      |

| CY37512 |                     |                     |                     |                     |                     |                      |                      |                      | 165                  | 165                  | 197                  | 269                  |

# 3.3V Selection Guide

# General Information

| Device   | Macrocells | Dedicated Inputs | I/O Pins    | Speed (t <sub>PD</sub> ) | Speed (f <sub>MAX</sub> ) |

|----------|------------|------------------|-------------|--------------------------|---------------------------|

| CY37032V | 32         | 5                | 32          | 8.5                      | 143                       |

| CY37064V | 64         | 5                | 32/64       | 8.5                      | 143                       |

| CY37128V | 128        | 5                | 64/80/128   | 10                       | 125                       |

| CY37192V | 192        | 5                | 120         | 12                       | 100                       |

| CY37256V | 256        | 5                | 128/160/192 | 12                       | 100                       |

| CY37384V | 384        | 5                | 160/192     | 15                       | 83                        |

| CY37512V | 512        | 5                | 160/192/264 | 15                       | 83                        |

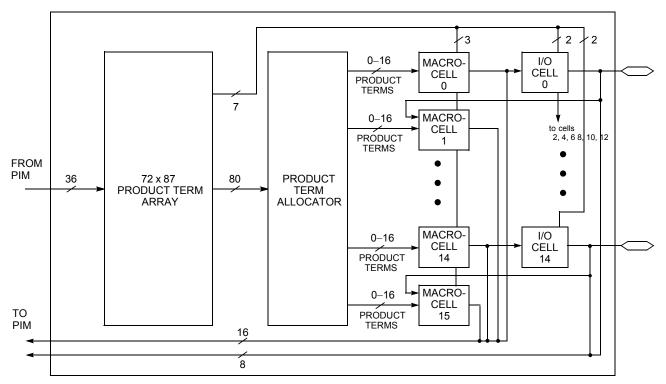

Figure 1. Logic Block with 50% Buried Macrocells

#### Low-Power Option

Each logic block can operate in high-speed mode for critical path performance, or in low-power mode for power conservation. The logic block mode is set by the user on a logic block by logic block basis.

#### **Product Term Allocator**

Through the product term allocator, software automatically distributes product terms among the 16 macrocells in the logic block as needed. A total of 80 product terms are available from the local product term array. The product term allocator provides two important capabilities without affecting performance: product term steering and product term sharing.

#### Product Term Steering

Product term steering is the process of assigning product terms to macrocells as needed. For example, if one macrocell requires ten product terms while another needs just three, the product term allocator will "steer" ten product terms to one macrocell and three to the other. On Ultra37000 devices, product terms are steered on an individual basis. Any number between 0 and 16 product terms can be steered to any macrocell. Note that 0 product terms is useful in cases where a particular macrocell is unused or used as an input register.

#### Product Term Sharing

Product term sharing is the process of using the same product term among multiple macrocells. For example, if more than one output has one or more product terms in its equation that are common to other outputs, those product terms are only programmed once. The Ultra37000 product term allocator allows sharing across groups of four output macrocells in a

variable fashion. The software automatically takes advantage of this capability—the user does not have to intervene.

Note that neither product term sharing nor product term steering have any effect on the speed of the product. All worst-case steering and sharing configurations have been incorporated in the timing specifications for the Ultra37000 devices.

### Ultra37000 Macrocell

Within each logic block there are 16 macrocells. Macrocells can either be I/O Macrocells, which include an I/O Cell which is associated with an I/O pin, or buried Macrocells, which do not connect to an I/O. The combination of I/O Macrocells and buried Macrocells varies from device to device.

#### Buried Macrocell

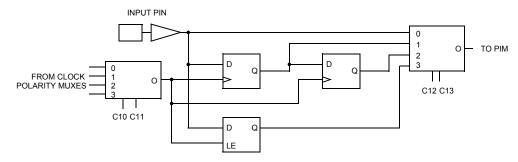

Figure 2 displays the architecture of buried macrocells. The buried macrocell features a register that can be configured as combinatorial, a D flip-flop, a T flip-flop, or a level-triggered latch.

The register can be asynchronously set or asynchronously reset at the logic block level with the separate set and reset product terms. Each of these product terms features programmable polarity. This allows the registers to be set or reset based on an AND expression or an OR expression.

Clocking of the register is very flexible. Four global synchronous clocks and a product term clock are available to clock the register. Furthermore, each clock features programmable polarity so that registers can be triggered on falling as well as rising edges (see the Clocking section). Clock polarity is chosen at the logic block level.

Figure 3. Input Macrocell

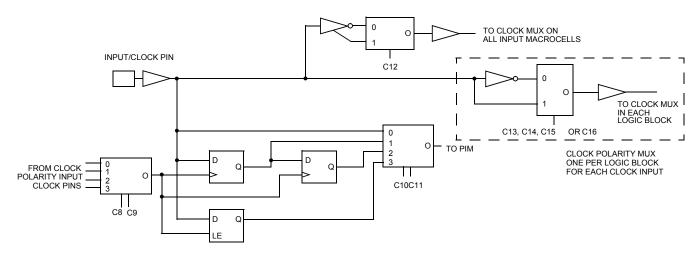

Figure 4. Input/Clock Macrocell

#### Clocking

Each I/O and buried macrocell has access to four synchronous clocks (CLK0, CLK1, CLK2 and CLK3) as well as an asynchronous product term clock PTCLK. Each input macrocell has access to all four synchronous clocks.

### Dedicated Inputs/Clocks

Five pins on each member of the Ultra37000 family are designated as input-only. There are two types of dedicated inputs on Ultra37000 devices: input pins and input/clock pins. Figure 3 illustrates the architecture for input pins. Four input options are available for the user: combinatorial, registered, double-registered, or latched. If a registered or latched option is selected, any one of the input clocks can be selected for control

Figure 4 illustrates the architecture for the input/clock pins. Like the input pins, input/clock pins can be combinatorial, registered, double-registered, or latched. In addition, these pins feed the clocking structures throughout the device. The clock path at the input has user-configurable polarity.

#### Product Term Clocking

In addition to the four synchronous clocks, the Ultra37000 family also has a product term clock for asynchronous clocking. Each logic block has an independent product term clock which is available to all 16 macrocells. Each product term clock also supports user configurable polarity selection.

#### **Timing Model**

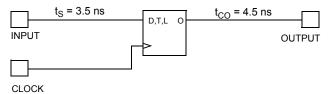

One of the most important features of the Ultra37000 family is the simplicity of its timing. All delays are worst case and system performance is unaffected by the features used. *Figure 5* illustrates the true timing model for the 167-MHz devices in high speed mode. For combinatorial paths, any input to any output incurs a 6.5-ns worst-case delay regardless of the amount of logic used. For synchronous systems, the input set-up time to the output macrocells for any input is 3.5 ns and the clock to output time is also 4.0 ns. These measurements are for any output and synchronous clock, regardless of the logic used.

The Ultra37000 features:

- · No fanout delays

- · No expander delays

- · No dedicated vs. I/O pin delays

- · No additional delay through PIM

- No penalty for using 0–16 product terms

- · No added delay for steering product terms

- · No added delay for sharing product terms

- · No routing delays

- · No output bypass delays

The simple timing model of the Ultra37000 family eliminates unexpected performance penalties.

# **Ultra37000 CPLD Family**

resources for pinout flexibility, and a simple timing model for consistent system performance.

####

#### REGISTERED SIGNAL

Figure 5. Timing Model for CY37128

#### JTAG and PCI Standards

#### **PCI Compliance**

5V operation of the Ultra37000 is fully compliant with the PCI Local Bus Specification published by the PCI Special Interest Group. The 3.3V products meet all PCI requirements except for the output 3.3V clamp, which is in direct conflict with 5V tolerance. The Ultra37000 family's simple and predictable timing model ensures compliance with the PCI AC specifications independent of the design.

#### **IEEE 1149.1-compliant JTAG**

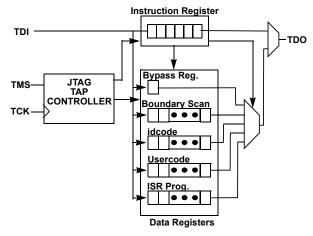

The Ultra37000 family has an IEEE 1149.1 JTAG interface for both Boundary Scan and ISR.

#### Boundary Scan

The Ultra37000 family supports Bypass, Sample/Preload, Extest, Idcode, and Usercode boundary scan instructions. The JTAG interface is shown in *Figure 6*.

Figure 6. JTAG Interface

#### In-System Reprogramming (ISR)

In-System Reprogramming is the combination of the capability to program or reprogram a device on-board, and the ability to support design changes without changing the system timing or device pinout. This combination means design changes during debug or field upgrades do not cause board respins. The Ultra37000 family implements ISR by providing a JTAG compliant interface for on-board programming, robust routing

### **Development Software Support**

#### Warp

Warp is a state-of-the-art compiler and complete CPLD design tool. For design entry, Warp provides an IEEE-STD-1076/1164 VHDL text editor, an IEEE-STD-1364 Verilog text editor, and a graphical finite state machine editor. It provides optimized synthesis and fitting by replacing basic circuits with ones pre-optimized for the target device, by implementing logic in unused memory and by perfect communication between fitting and synthesis. To facilitate design and debugging, Warp provides graphical timing simulation and analysis.

#### Warp Professional™

*Warp* Professional contains several additional features. It provides an extra method of design entry with its graphical block diagram editor. It allows up to 5 ms timing simulation instead of only 2 ms. It allows comparison of waveforms before and after design changes.

### Warp Enterprise™

Warp Enterprise provides even more features. It provides unlimited timing simulation and source-level behavioral simulation as well as a debugger. It has the ability to generate graphical HDL blocks from HDL text. It can even generate testbenches.

Warp is available for PC and UNIX platforms. Some features are not available in the UNIX version. For further information see the Warp for PC, Warp for UNIX, Warp Professional and Warp Enterprise data sheets on Cypress's web site (www.cypress.com).

#### **Third-Party Software**

Although *Warp* is a complete CPLD development tool on its own, it interfaces with nearly every third party EDA tool. All major third-party software vendors provide support for the Ultra37000 family of devices. Refer to the third-party software data sheet or contact your local sales office for a list of currently supported third-party vendors.

#### **Programming**

There are four programming options available for Ultra37000 devices. The first method is to use a PC with the 37000 UltraISR programming cable and software. With this method, the ISR pins of the Ultra37000 devices are routed to a connector at the edge of the printed circuit board. The 37000 UltraISR programming cable is then connected between the parallel port of the PC and this connector. A simple configuration file instructs the ISR software of the programming operations to be performed on each of the Ultra37000 devices in the system. The ISR software then automatically completes all of the necessary data manipulations required to accomplish the programming, reading, verifying, and other ISR functions. For more information on the Cypress ISR Interface, see the ISR Programming Kit data sheet (CY3700i).

The second method for programming Ultra37000 devices is on automatic test equipment (ATE). This is accomplished through a file created by the ISR software. Check the Cypress website for the latest ISR software download information.

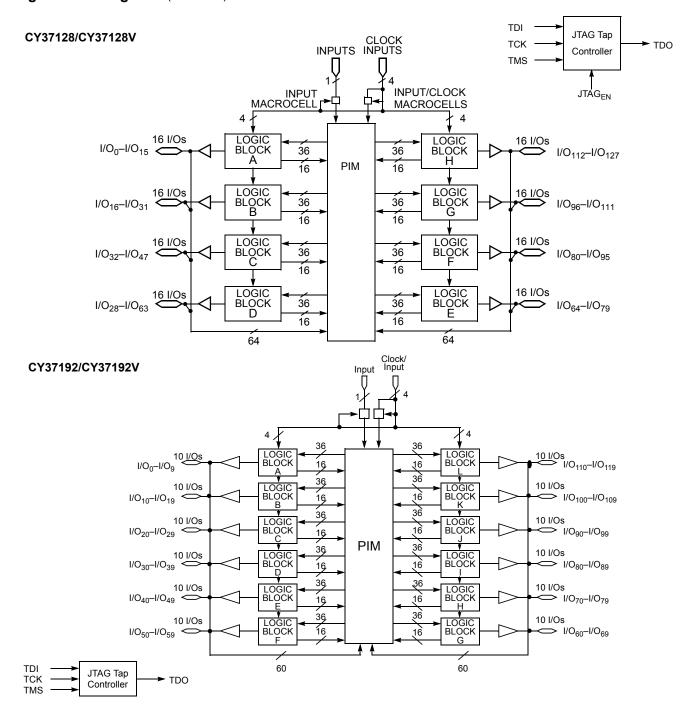

# Logic Block Diagrams (continued)

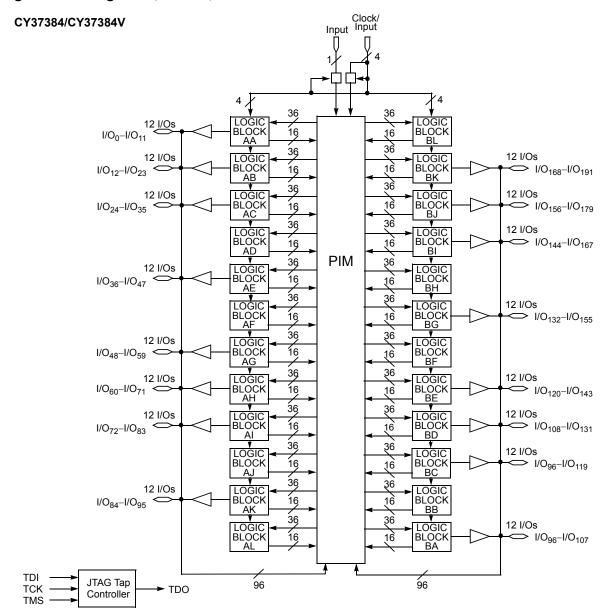

# Logic Block Diagrams (continued)

### Inductance<sup>[5]</sup>

| Parameter | Description               | Test Conditions                        | 44-<br>Lead<br>TQFP | 44-<br>Lead<br>PLCC | 44-<br>Lead<br>CLCC | 84-<br>Lead<br>PLCC | 84-<br>Lead<br>CLCC | 100-<br>Lead<br>TQFP | 160-<br>Lead<br>TQFP | 208-<br>Lead<br>PQFP | Unit |

|-----------|---------------------------|----------------------------------------|---------------------|---------------------|---------------------|---------------------|---------------------|----------------------|----------------------|----------------------|------|

|           | Maximum Pin<br>Inductance | V <sub>IN</sub> = 3.3V<br>at f = 1 MHz | 2                   | 5                   | 2                   | 8                   | 5                   | 8                    | 9                    | 11                   | nΗ   |

# Capacitance<sup>[5]</sup>

| Parameter        | Description                         | Test Conditions                                     | Max. | Unit |

|------------------|-------------------------------------|-----------------------------------------------------|------|------|

| C <sub>I/O</sub> | Input/Output Capacitance            | $V_{IN}$ = 3.3V at f = 1 MHz at $T_A$ = 25°C        | 8    | pF   |

| C <sub>CLK</sub> | Clock Signal Capacitance            | $V_{IN}$ = 3.3V at f = 1 MHz at $T_A$ = 25°C        | 12   | pF   |

| C <sub>DP</sub>  | Dual Functional Pins <sup>[9]</sup> | $V_{IN} = 3.3V$ at f = 1 MHz at $T_A = 25^{\circ}C$ | 16   | pF   |

# **Endurance Characteristics**<sup>[5]</sup>

| Parameter | Description                  | Test Conditions                              | Min.  | Тур.   | Unit   |

|-----------|------------------------------|----------------------------------------------|-------|--------|--------|

| N         | Minimum Reprogramming Cycles | Normal Programming Conditions <sup>[2]</sup> | 1,000 | 10,000 | Cycles |

### **AC Characteristics**

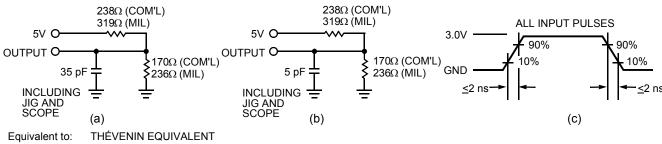

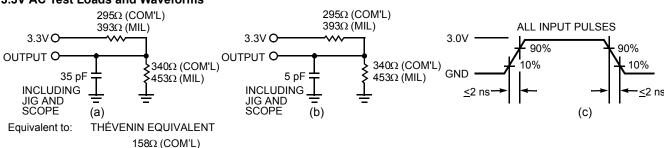

#### 5.0V AC Test Loads and Waveforms

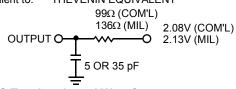

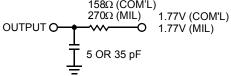

# 3.3V AC Test Loads and Waveforms

# Switching Characteristics Over the Operating Range [12]

|                                         | 200   | MHz    | 167   | MHz   | 154  | MHz  | 143  | MHz  | 125                 | MHz                 | 100 N               | ЛHz                 | 83 M                | Hz                | 66 1 | ИHz  |      |

|-----------------------------------------|-------|--------|-------|-------|------|------|------|------|---------------------|---------------------|---------------------|---------------------|---------------------|-------------------|------|------|------|

| Parameter                               | Min.  | Мах.   | Min.  | Мах.  | Min. | Мах. | Min. | Мах. | Min.                | Мах.                | Min.                | Мах.                | Min.                | Мах.              | Min. | Мах. | Unit |

| Combinatorial                           | Mod   | e Para | amete | rs    |      |      |      |      |                     |                     |                     |                     |                     |                   |      |      | •    |

| t <sub>PD</sub> <sup>[13, 14, 15]</sup> |       | 6      |       | 6.5   |      | 7.5  |      | 8.5  |                     | 10                  |                     | 12                  |                     | 15                |      | 20   | ns   |

| t <sub>PDL</sub> [13, 14, 15]           |       | 11     |       | 12.5  |      | 14.5 |      | 16   |                     | 16.5                |                     | 17                  |                     | 19                |      | 22   | ns   |

| t <sub>PDI 1</sub> [13, 14, 15]         |       | 12     |       | 13.5  |      | 15.5 |      | 17   |                     | 17.5                |                     | 18                  |                     | 20                |      | 24   | ns   |

| t <sub>EA</sub> <sup>[13, 14, 15]</sup> |       | 8      |       | 8.5   |      | 11   |      | 13   |                     | 14                  |                     | 16                  |                     | 19                |      | 24   | ns   |

| t <sub>ER</sub> <sup>[11, 13]</sup>     |       | 8      |       | 8.5   |      | 11   |      | 13   |                     | 14                  |                     | 16                  |                     | 19                |      | 24   | ns   |

| Input Register                          | Para  | meter  | s     |       |      |      |      | •    |                     |                     |                     |                     |                     | •                 |      |      |      |

| t <sub>WL</sub>                         | 2.5   |        | 2.5   |       | 2.5  |      | 2.5  |      | 3                   |                     | 3                   |                     | 4                   |                   | 5    |      | ns   |

| t <sub>WH</sub>                         | 2.5   |        | 2.5   |       | 2.5  |      | 2.5  |      | 3                   |                     | 3                   |                     | 4                   |                   | 5    |      | ns   |

| t <sub>IS</sub>                         | 2     |        | 2     |       | 2    |      | 2    |      | 2                   |                     | 2.5                 |                     | 3                   |                   | 4    |      | ns   |

| t <sub>IH</sub>                         | 2     |        | 2     |       | 2    |      | 2    |      | 2                   |                     | 2.5                 |                     | 3                   |                   | 4    |      | ns   |

| t <sub>ICO</sub> [13, 14, 15]           |       | 11     |       | 11    |      | 11   |      | 12.5 |                     | 12.5                |                     | 16                  |                     | 19                |      | 24   | ns   |

| t <sub>ICOL</sub> [13, 14, 15]          |       | 12     |       | 12    |      | 12   |      | 14   |                     | 16                  |                     | 18                  |                     | 21                |      | 26   | ns   |

| Synchronous                             | Clock | king P | aram  | eters |      |      |      |      | •                   |                     |                     |                     |                     |                   |      |      | ,    |

| t <sub>CO</sub> [14, 15]                |       | 4      |       | 4     |      | 4.5  |      | 6    |                     | 6.5 <sup>[16]</sup> |                     | 6.5 <sup>[17]</sup> |                     | 8 <sup>[18]</sup> |      | 10   | ns   |

| t <sub>S</sub> <sup>[13]</sup>          | 4     |        | 4     |       | 5    |      | 5    |      | 5.5 <sup>[16]</sup> |                     | 6 <sup>[17]</sup>   |                     | 8 <sup>[18]</sup>   |                   | 10   |      | ns   |

| t <sub>H</sub>                          | 0     |        | 0     |       | 0    |      | 0    |      | 0                   |                     | 0                   |                     | 0                   |                   | 0    |      | ns   |

| t <sub>CO2</sub> [13, 14, 15]           |       | 9.5    |       | 10    |      | 11   |      | 12   |                     | 14                  |                     | 16                  |                     | 19                |      | 24   | ns   |

| t <sub>SCS</sub> <sup>[13]</sup>        | 5     |        | 6     |       | 6.5  |      | 7    |      | 8 <sup>[16]</sup>   |                     | 10                  |                     | 12                  |                   | 15   |      | ns   |

| t <sub>SL</sub> <sup>[13]</sup>         | 7.5   |        | 7.5   |       | 8.5  |      | 9    |      | 10                  |                     | 12                  |                     | 15                  |                   | 15   |      | ns   |

| t <sub>HL</sub>                         | 0     |        | 0     |       | 0    |      | 0    |      | 0                   |                     | 0                   |                     | 0                   |                   | 0    |      | ns   |

| Product Term                            | Clock | king P | aram  | eters |      |      |      | •    |                     |                     |                     |                     |                     | •                 |      |      |      |

| t <sub>COPT</sub> [13, 14, 15]          |       | 7      |       | 10    |      | 10   |      | 13   |                     | 13                  |                     | 13                  |                     | 15                |      | 20   | ns   |

| t <sub>SPT</sub>                        | 2.5   |        | 2.5   |       | 2.5  |      | 3    |      | 5                   |                     | 5.5                 |                     | 6                   |                   | 7    |      | ns   |

| t <sub>HPT</sub>                        | 2.5   |        | 2.5   |       | 2.5  |      | 3    |      | 5                   |                     | 5.5                 |                     | 6                   |                   | 7    |      | ns   |

| t <sub>ISPT</sub> <sup>[13]</sup>       | 0     |        | 0     |       | 0    |      | 0    |      | 0                   |                     | 0                   |                     | 0                   |                   | 0    |      | ns   |

| t <sub>IHPT</sub>                       | 6     |        | 6.5   |       | 6.5  |      | 7.5  |      | 9                   |                     | 11                  |                     | 14                  |                   | 19   |      | ns   |

| t <sub>CO2PT</sub> [13, 14, 15]         |       | 12     |       | 14    |      | 15   |      | 19   |                     | 19                  |                     | 21                  |                     | 24                |      | 30   | ns   |

| Pipelined Mo                            | de Pa | rame   | ters  |       |      |      |      | I    | <u>I</u>            |                     |                     |                     |                     | I                 |      |      | 1    |

| t <sub>ICS</sub> <sup>[13]</sup>        | 5     |        | 6     |       | 6    |      | 7    |      | 8 <sup>[16]</sup>   |                     | 10                  |                     | 12                  |                   | 15   |      | ns   |

| Operating Free                          |       | cy Pa  |       | ers   |      |      |      |      |                     |                     |                     |                     |                     |                   |      |      |      |

| f <sub>MAX1</sub>                       | 200   |        | 167   |       | 154  |      | 143  |      | 125 <sup>[16]</sup> |                     | 100                 |                     | 83                  |                   | 66   |      | MHz  |

| f <sub>MAX2</sub>                       | 200   |        | 200   |       | 200  |      | 167  |      | 154                 |                     | 153 <sup>[17]</sup> |                     | 125 <sup>[18]</sup> |                   | 100  |      | MHz  |

| f <sub>MAX3</sub>                       | 125   |        | 125   |       | 105  |      | 91   |      | 83                  |                     | 80 <sup>[17]</sup>  |                     | 62.5                |                   | 50   |      | MHz  |

| f <sub>MAX4</sub>                       | 167   |        | 167   |       | 154  |      | 125  |      | 118                 |                     | 100                 |                     | 83                  |                   | 66   |      | MHz  |

| Reset/Preset F                          | aram  | neters |       |       |      |      |      |      |                     |                     |                     |                     |                     |                   |      |      |      |

| t <sub>RW</sub>                         | 8     |        | 8     |       | 8    |      | 8    |      | 10                  |                     | 12                  |                     | 15                  |                   | 20   |      | ns   |

| t <sub>RR</sub> <sup>[13]</sup>         | 10    |        | 10    |       | 10   |      | 10   |      | 12                  |                     | 14                  |                     | 17                  |                   | 22   |      | ns   |

| Notes:                                  |       |        |       |       |      |      |      | -    |                     |                     |                     |                     |                     | -                 |      |      |      |

<sup>16.</sup> The following values correspond to the CY37512 and CY37384 devices:  $t_{\rm CO}$  = 5 ns,  $t_{\rm SCS}$  = 8.5 ns,  $t_{\rm ICS}$  = 8.5 n

# $\textbf{Switching Characteristics} \ \, \text{Over the Operating Range (continued)}^{[12]}$

|                                         | 200   | MHz    | 167  | MHz  | 154  | MHz  | 143  | MHz  | 125 I | MHz  | 100 N | ИHz  | 83 MHz |      | 66 MHz |      |      |

|-----------------------------------------|-------|--------|------|------|------|------|------|------|-------|------|-------|------|--------|------|--------|------|------|

| Parameter                               | Min.  | Мах.   | Min. | Мах. | Min. | Мах. | Min. | Мах. | Min.  | Мах. | Min.  | Мах. | Min.   | Мах. | Min.   | Мах. | Unit |

| t <sub>RO</sub> <sup>[13, 14, 15]</sup> |       | 12     |      | 13   |      | 13   |      | 14   |       | 15   |       | 18   |        | 21   |        | 26   | ns   |

| $t_{PW}$                                | 8     |        | 8    |      | 8    |      | 8    |      | 10    |      | 12    |      | 15     |      | 20     |      | ns   |

| t <sub>PR</sub> <sup>[13]</sup>         | 10    |        | 10   |      | 10   |      | 10   |      | 12    |      | 14    |      | 17     |      | 22     |      | ns   |

| t <sub>PO</sub> <sup>[13, 14, 15]</sup> |       | 12     |      | 13   |      | 13   |      | 14   |       | 15   |       | 18   |        | 21   |        | 26   | ns   |

| User Option P                           | aram  | eters  |      |      |      |      |      |      |       |      |       |      |        |      |        |      | •    |

| t <sub>LP</sub>                         |       | 2.5    |      | 2.5  |      | 2.5  |      | 2.5  |       | 2.5  |       | 2.5  |        | 2.5  |        | 2.5  | ns   |

| t <sub>SLEW</sub>                       |       | 3      |      | 3    |      | 3    |      | 3    |       | 3    |       | 3    |        | 3    |        | 3    | ns   |

| t <sub>3.3IO</sub> <sup>[19]</sup>      |       | 0.3    |      | 0.3  |      | 0.3  |      | 0.3  |       | 0.3  |       | 0.3  |        | 0.3  |        | 0.3  | ns   |

| JTAG Timing F                           | Paran | neters |      |      |      |      |      |      |       |      |       |      |        |      |        |      | •    |

| t <sub>S JTAG</sub>                     | 0     |        | 0    |      | 0    |      | 0    |      | 0     |      | 0     |      | 0      |      | 0      |      | ns   |

| t <sub>H JTAG</sub>                     | 20    |        | 20   |      | 20   |      | 20   |      | 20    |      | 20    |      | 20     |      | 20     |      | ns   |

| t <sub>CO JTAG</sub>                    |       | 20     |      | 20   |      | 20   |      | 20   |       | 20   |       | 20   |        | 20   |        | 20   | ns   |

| $f_{JTAG}$                              |       | 20     |      | 20   |      | 20   |      | 20   |       | 20   |       | 20   |        | 20   |        | 20   | MHz  |

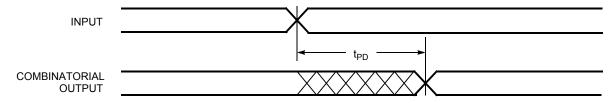

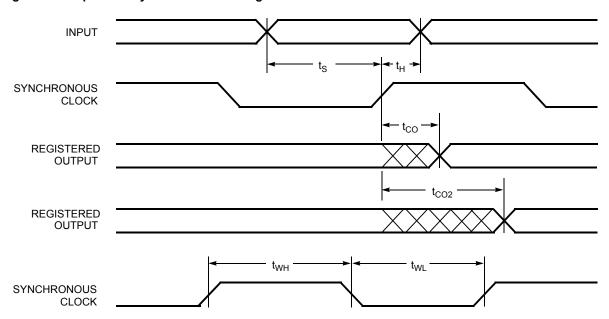

# **Switching Waveforms**

# **Combinatorial Output**

# **Registered Output with Synchronous Clocking**

#### Note:

19. Only applicable to the 5V devices.

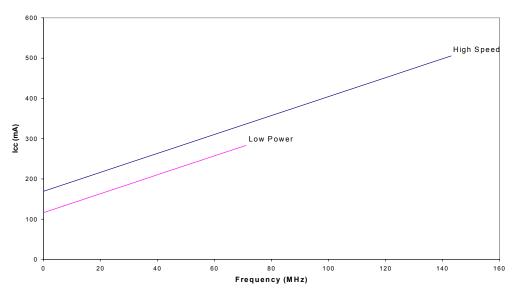

# **Typical 5.0V Power Consumption** (continued) **CY37512**

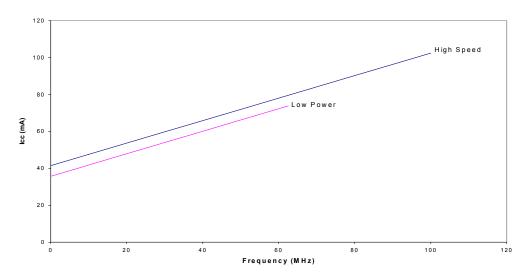

The typical pattern is a 16-bit up counter, per logic block, with outputs disabled.  $V_{CC} = 5.0V, \, T_A = Room \, Temperature$

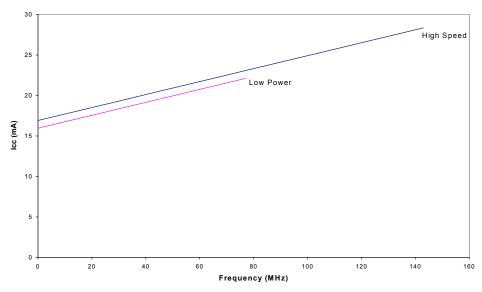

# Typical 3.3V Power Consumption CY37032V

The typical pattern is a 16-bit up counter, per logic block, with outputs disabled.  $V_{CC} = 3.3V,\, T_A = Room\, Temperature$

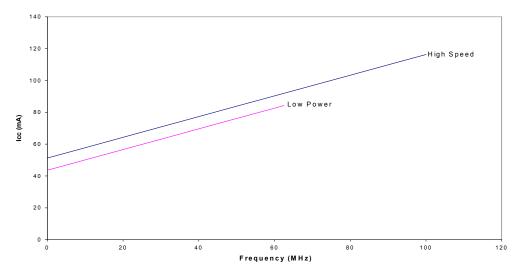

# **Typical 3.3V Power Consumption** (continued) **CY37192V**

The typical pattern is a 16-bit up counter, per logic block, with outputs disabled.  $V_{\rm CC}$  = 3.3V,  $T_{\rm A}$  = Room Temperature

### CY37256V

The typical pattern is a 16-bit up counter, per logic block, with outputs disabled.  $V_{\rm CC} = 3.3V,\,T_A = Room\,Temperature$

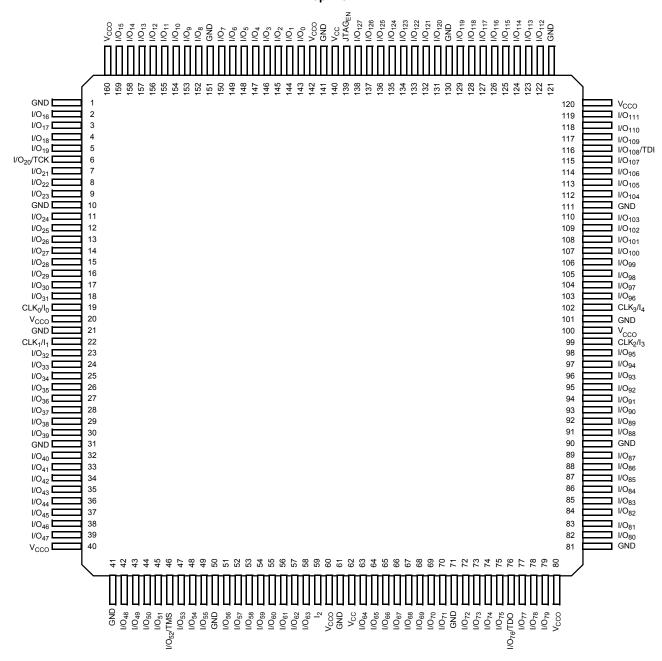

Pin Configurations<sup>[20]</sup> (continued)

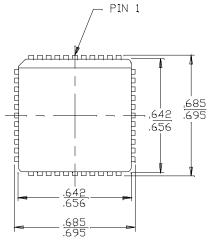

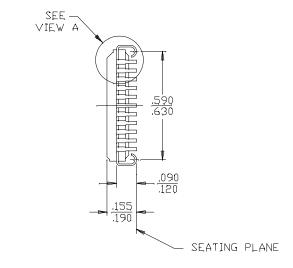

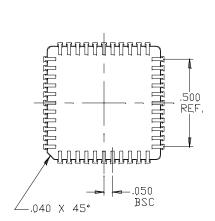

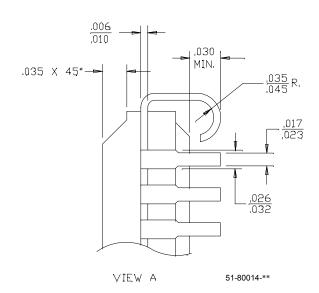

### 160-Lead TQFP (A160) / CQFP (U162) for CY37128(V) and CY37256(V) Top View

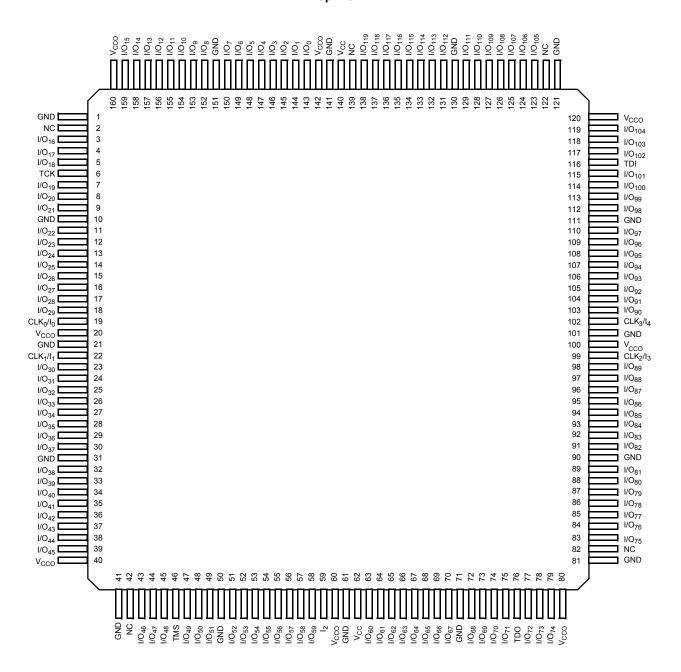

Pin Configurations<sup>[20]</sup> (continued)

### 160-Lead TQFP (A160) for CY37192(V) Top View

# Pin Configurations<sup>[20]</sup> (continued)

# 400-Ball Fine-Pitch BGA (BB400) Top View

| Α | GND               | GND               | NC                 | I/O <sub>17</sub>  | I/O <sub>16</sub>  | I/O <sub>14</sub>  | I/O <sub>29</sub>                   | V <sub>CC</sub>    | I/O <sub>11</sub>  | GND                | GND                | I/O <sub>257</sub> | V <sub>CC</sub>    | I/O <sub>239</sub>                  | I/O <sub>233</sub> | I/O <sub>232</sub> | I/O <sub>230</sub> | NC                 | GND                | GND                |

|---|-------------------|-------------------|--------------------|--------------------|--------------------|--------------------|-------------------------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|-------------------------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| В | GND               | GND               | GND                | NC                 | I/O <sub>15</sub>  | I/O <sub>13</sub>  | I/O <sub>28</sub>                   | V <sub>CC</sub>    | I/O <sub>10</sub>  | GND                | GND                | I/O <sub>256</sub> | V <sub>CC</sub>    | I/O <sub>238</sub>                  | I/O <sub>231</sub> | I/O <sub>229</sub> | NC                 | GND                | GND                | GND                |

| С | NC                | GND               | GND                | GND                | I/O <sub>20</sub>  | I/O <sub>12</sub>  | I/O <sub>27</sub>                   | V <sub>CC</sub>    | I/O <sub>9</sub>   | GND                | GND                | I/O <sub>255</sub> | V <sub>CC</sub>    | I/O <sub>237</sub>                  | I/O <sub>228</sub> | I/O <sub>245</sub> | GND                | GND                | GND                | NC                 |

| D | I/O <sub>44</sub> | NC                | GND                | I/O <sub>21</sub>  | I/O <sub>19</sub>  | I/O <sub>18</sub>  | I/O <sub>26</sub>                   | I/O <sub>25</sub>  | I/O <sub>8</sub>   | GND                | GND                | I/O <sub>254</sub> | I/O <sub>235</sub> | I/O <sub>236</sub>                  | I/O <sub>251</sub> | I/O <sub>244</sub> | I/O <sub>243</sub> | GND                | NC                 | I/O <sub>227</sub> |

| Е | I/O <sub>46</sub> | I/O <sub>43</sub> | I/O <sub>23</sub>  | I/O <sub>22</sub>  | NC                 | I/O <sub>35</sub>  | I/O <sub>34</sub>                   | I/O <sub>24</sub>  | I/O <sub>7</sub>   | I/O <sub>4</sub>   | I/O <sub>263</sub> | I/O <sub>253</sub> | I/O <sub>234</sub> | I/O <sub>250</sub>                  | I/O <sub>248</sub> | NC                 | I/O <sub>241</sub> | I/O <sub>242</sub> | I/O <sub>225</sub> | I/O <sub>226</sub> |

| F | I/O <sub>47</sub> | I/O <sub>45</sub> | I/O <sub>42</sub>  | I/O <sub>41</sub>  | I/O <sub>40</sub>  | NC                 | I/O <sub>33</sub>                   | I/O <sub>32</sub>  | I/O <sub>6</sub>   | I/O <sub>3</sub>   | I/O <sub>262</sub> | I/O <sub>252</sub> | I/O <sub>249</sub> | I/O <sub>247</sub>                  | I/O <sub>220</sub> | I/O <sub>221</sub> | I/O <sub>240</sub> | I/O <sub>222</sub> | I/O <sub>223</sub> | I/O <sub>224</sub> |

| G | I/O <sub>53</sub> | I/O <sub>52</sub> | I/O <sub>51</sub>  | I/O <sub>50</sub>  | I/O <sub>39</sub>  | I/O <sub>38</sub>  | I/O <sub>37</sub>                   | I/O <sub>31</sub>  | I/O <sub>5</sub>   | I/O <sub>2</sub>   | I/O <sub>261</sub> | V <sub>CC</sub>    | I/O <sub>246</sub> | I/O <sub>217</sub>                  | I/O <sub>218</sub> | I/O <sub>219</sub> | I/O <sub>212</sub> | I/O <sub>213</sub> | I/O <sub>214</sub> | I/O <sub>215</sub> |

| Н | V <sub>CC</sub>   | V <sub>CC</sub>   | V <sub>CC</sub>    | I/O <sub>49</sub>  | I/O <sub>48</sub>  | I/O <sub>36</sub>  | TCK                                 | V <sub>CC</sub>    | I/O <sub>30</sub>  | I/O <sub>1</sub>   | I/O <sub>259</sub> | I/O <sub>260</sub> | V <sub>CC</sub>    | TDI                                 | I/O <sub>216</sub> | I/O <sub>210</sub> | I/O <sub>211</sub> | V <sub>CC</sub>    | V <sub>CC</sub>    | V <sub>CC</sub>    |

| J | I/O <sub>59</sub> | I/O <sub>58</sub> | I/O <sub>57</sub>  | I/O <sub>56</sub>  | I/O <sub>55</sub>  | I/O <sub>54</sub>  | V <sub>CC</sub>                     | I/O <sub>62</sub>  | I/O <sub>60</sub>  | I/O <sub>0</sub>   | I/O <sub>258</sub> | I/O <sub>202</sub> | I/O <sub>203</sub> | CLK <sub>3</sub><br>/I <sub>4</sub> | I/O <sub>204</sub> | I/O <sub>205</sub> | I/O <sub>206</sub> | I/O <sub>207</sub> | I/O <sub>208</sub> | I/O <sub>209</sub> |

| K | GND               | GND               | GND                | GND                | I/O <sub>65</sub>  | I/O <sub>64</sub>  | CLK <sub>0</sub><br>/I <sub>0</sub> | I/O <sub>63</sub>  | I/O <sub>61</sub>  | GND                | GND                | I/O <sub>198</sub> | I/O <sub>199</sub> | CLK <sub>2</sub><br>/I <sub>3</sub> | I/O <sub>200</sub> | I/O <sub>201</sub> | GND                | GND                | GND                | GND                |

| L | GND               | GND               | GND                | GND                | I/O <sub>69</sub>  | I/O <sub>68</sub>  | NC                                  | I/O <sub>67</sub>  | I/O <sub>66</sub>  | GND                | GND                | I/O <sub>193</sub> | I/O <sub>195</sub> | l <sub>2</sub>                      | I/O <sub>196</sub> | I/O <sub>197</sub> | GND                | GND                | GND                | GND                |

| М | I/O <sub>89</sub> | I/O <sub>88</sub> | I/O <sub>87</sub>  | I/O <sub>86</sub>  | I/O <sub>85</sub>  | I/O <sub>84</sub>  | CLK <sub>1</sub><br>/I <sub>1</sub> | I/O <sub>71</sub>  | I/O <sub>70</sub>  | I/O <sub>126</sub> | I/O <sub>132</sub> | I/O <sub>192</sub> | I/O <sub>194</sub> | V <sub>CC</sub>                     | I/O <sub>174</sub> | I/O <sub>175</sub> | I/O <sub>176</sub> | I/O <sub>177</sub> | I/O <sub>178</sub> | I/O <sub>179</sub> |

| N | V <sub>CC</sub>   | V <sub>CC</sub>   | V <sub>CC</sub>    | I/O <sub>91</sub>  | I/O <sub>90</sub>  | I/O <sub>72</sub>  | TMS                                 | V <sub>CC</sub>    | I/O <sub>128</sub> | I/O <sub>127</sub> | I/O <sub>133</sub> | I/O <sub>162</sub> | V <sub>CC</sub>    | TDO                                 | I/O <sub>180</sub> | I/O <sub>168</sub> | I/O <sub>169</sub> | V <sub>CC</sub>    | V <sub>CC</sub>    | V <sub>CC</sub>    |

| Р | I/O <sub>95</sub> | I/O <sub>94</sub> | I/O <sub>93</sub>  | I/O <sub>92</sub>  | I/O <sub>75</sub>  | I/O <sub>74</sub>  | I/O <sub>73</sub>                   | I/O <sub>114</sub> | V <sub>CC</sub>    | I/O <sub>129</sub> | I/O <sub>134</sub> | I/O <sub>137</sub> | I/O <sub>163</sub> | I/O <sub>181</sub>                  | I/O <sub>182</sub> | I/O <sub>183</sub> | I/O <sub>170</sub> | I/O <sub>171</sub> | I/O <sub>172</sub> | I/O <sub>173</sub> |

| R | I/O <sub>80</sub> | I/O <sub>79</sub> | I/O <sub>78</sub>  | I/O <sub>108</sub> | I/O <sub>77</sub>  | I/O <sub>76</sub>  | I/O <sub>115</sub>                  | I/O <sub>117</sub> | I/O <sub>120</sub> | I/O <sub>130</sub> | I/O <sub>135</sub> | I/O <sub>138</sub> | I/O <sub>164</sub> | I/O <sub>165</sub>                  | NC                 | I/O <sub>184</sub> | I/O <sub>185</sub> | I/O <sub>186</sub> | I/O <sub>189</sub> | I/O <sub>191</sub> |

| T | I/O <sub>82</sub> | I/O <sub>81</sub> | I/O <sub>110</sub> | I/O <sub>109</sub> | NC                 | I/O <sub>116</sub> | I/O <sub>118</sub>                  | I/O <sub>102</sub> | I/O <sub>121</sub> | I/O <sub>131</sub> | I/O <sub>136</sub> | I/O <sub>139</sub> | I/O <sub>156</sub> | I/O <sub>166</sub>                  | I/O <sub>167</sub> | NC                 | I/O <sub>154</sub> | I/O <sub>155</sub> | I/O <sub>187</sub> | I/O <sub>190</sub> |

| U | I/O <sub>83</sub> | NC                | GND                | I/O <sub>111</sub> | I/O <sub>112</sub> | I/O <sub>119</sub> | I/O <sub>104</sub>                  | I/O <sub>103</sub> | I/O <sub>122</sub> | GND                | GND                | I/O <sub>140</sub> | I/O <sub>157</sub> | I/O <sub>158</sub>                  | I/O <sub>150</sub> | I/O <sub>151</sub> | I/O <sub>153</sub> | GND                | NC                 | I/O <sub>188</sub> |

| V | NC                | GND               | GND                | GND                | I/O <sub>113</sub> | I/O <sub>96</sub>  | I/O <sub>105</sub>                  | V <sub>CC</sub>    | I/O <sub>123</sub> | GND                | GND                | I/O <sub>141</sub> | V <sub>CC</sub>    | I/O <sub>159</sub>                  | I/O14<br>4         | I/O <sub>152</sub> | GND                | GND                | GND                | NC                 |

| W | GND               | GND               | GND                | NC                 | I/O <sub>97</sub>  | I/O <sub>99</sub>  | I/O <sub>106</sub>                  | V <sub>CC</sub>    | I/O <sub>124</sub> | GND                | GND                | I/O <sub>142</sub> | V <sub>CC</sub>    | I/O <sub>160</sub>                  | I/O <sub>145</sub> | I/O <sub>147</sub> | NC                 | GND                | GND                | GND                |

| Υ | GND               | GND               | NC                 | I/O <sub>98</sub>  | I/O <sub>100</sub> | I/O <sub>101</sub> | I/O <sub>107</sub>                  | V <sub>CC</sub>    | I/O <sub>125</sub> | GND                | GND                | I/O <sub>143</sub> | V <sub>CC</sub>    | I/O <sub>161</sub>                  | I/O <sub>146</sub> | I/O <sub>148</sub> | I/O <sub>149</sub> | NC                 | GND                | GND                |

# Ultra37000 CPLD Family

# 5.0V Ordering Information (continued)

| Macrocells | Speed<br>(MHz) | Ordering Code      | Package<br>Name | Package Type                                  | Operating Range |

|------------|----------------|--------------------|-----------------|-----------------------------------------------|-----------------|

| 64         | 154            | CY37064P44-154AC   | A44             | 44-Lead Thin Quad Flat Pack                   | Commercial      |

|            |                | CY37064P44-154JC   | J67             | 44-Lead Plastic Leaded Chip Carrier           |                 |

|            |                | CY37064P84-154JC   | J83             | 84-Lead Plastic Leaded Chip Carrier           |                 |

|            |                | CY37064P100-154AC  | A100            | 100-Lead Thin Quad Flat Pack                  |                 |

|            |                | CY37064P44-154AI   | A44             | 44-Lead Thin Quad Flat Pack                   | Industrial      |

|            |                | CY37064P44-154AXI  | A44             | 44-Lead Lead Free Thin Quad Flat Pack         |                 |

|            |                | CY37064P44-154JI   | J67             | 44-Lead Plastic Leaded Chip Carrier           |                 |

|            |                | CY37064P44-154JXI  | J67             | 44-Lead Lead Free Plastic Leaded Chip Carrier |                 |

|            |                | CY37064P84-154JI   | J83             | 84-Lead Plastic Leaded Chip Carrier           |                 |

|            |                | CY37064P100-154AI  | A100            | 100-Lead Thin Quad Flat Pack                  |                 |

|            |                | 5962-9951902QYA    | Y67             | 44-Lead Ceramic Leadless Chip Carrier         | Military        |

|            | 125            | CY37064P44-125AC   | A44             | 44-Lead Thin Quad Flat Pack                   | Commercial      |

|            |                | CY37064P44-125AXC  | A44             | 44-Lead Lead Free Thin Quad Flat Pack         |                 |

|            |                | CY37064P44-125JC   | J67             | 44-Lead Plastic Leaded Chip Carrier           |                 |

|            |                | CY37064P44-125JXC  | J67             | 44-Lead Lead Free Plastic Leaded Chip Carrier |                 |

|            |                | CY37064P84-125JC   | J83             | 84-Lead Plastic Leaded Chip Carrier           |                 |

|            |                | CY37064P100-125AC  | A100            | 100-Lead Thin Quad Flat Pack                  |                 |

|            |                | CY37064P100-125AXC | A100            | 100-Lead Lead Free Thin Quad Flat Pack        |                 |

|            |                | CY37064P44-125AI   | A44             | 44-Lead Thin Quad Flat Pack                   | Industrial      |

|            |                | CY37064P44-125AXI  | A44             | 44-Lead Lead Free Thin Quad Flat Pack         |                 |

|            |                | CY37064P44-125JI   | J67             | 44-Lead Plastic Leaded Chip Carrier           | 1               |

|            |                | CY37064P84-125JI   | J83             | 84-Lead Plastic Leaded Chip Carrier           | 1               |

|            |                | CY37064P100-125AI  | A100            | 100-Lead Thin Quad Flat Pack                  | 1               |

|            |                | CY37064P100-125AXI | A100            | 100-Lead Lead Free Thin Quad Flat Pack        | 1               |

|            |                | 5962-9951901QYA    | Y67             | 44-Lead Ceramic Leadless Chip Carrier         | Military        |

# Ultra37000 CPLD Family

# 3.3V Ordering Information (continued)

| Macrocells | Speed<br>(MHz) | Ordering Code       | Package<br>Name | Package Type                           | Operating<br>Range |

|------------|----------------|---------------------|-----------------|----------------------------------------|--------------------|

| 256        | 100            | CY37256VP160-100AC  | A160            | 160-Lead Thin Quad Flat Pack           | Commercial         |

|            |                | CY37256VP160-100AXC | A160            | 160-Lead Lead Free Thin Quad Flat Pack |                    |

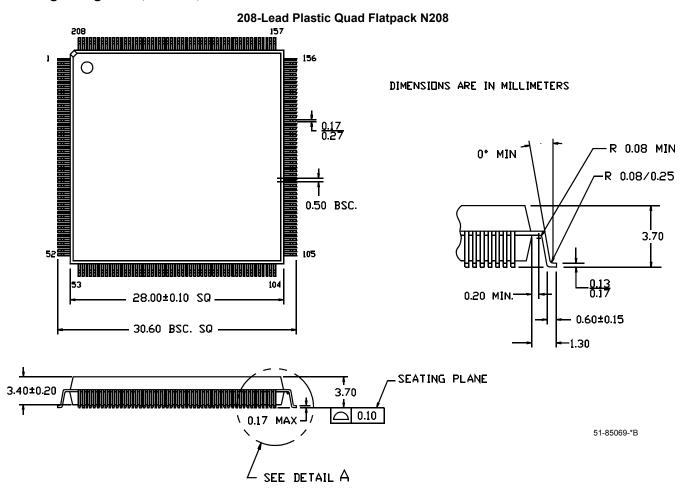

|            |                | CY37256VP208-100NC  | N208            | 208-Lead Plastic Quad Flat Pack        |                    |

|            |                | CY37256VP256-100BGC | BG292           | 292-Ball Plastic Ball Grid Array       |                    |

|            |                | CY37256VP256-100BBC | BB256           | 256-Ball Fine-Pitch Ball Grid Array    |                    |

|            |                | CY37256VP160-100AI  | A160            | 160-Lead Thin Quad Flat Pack           | Industrial         |

|            |                | CY37256VP160-100AXI | A160            | 160-Lead Lead Free Thin Quad Flat Pack |                    |

|            | 66             | CY37256VP160-66AC   | A160            | 160-Lead Thin Quad Flat Pack           | Commercial         |

|            |                | CY37256VP160-66AXC  | A160            | 160-Lead Lead Free Thin Quad Flat Pack |                    |

|            |                | CY37256VP208-66NC   | N208            | 208-Lead Plastic Quad Flat Pack        |                    |

|            |                | CY37256VP256-66BGC  | BG292           | 292-Ball Plastic Ball Grid Array       |                    |

|            |                | CY37256VP256-66BBC  | BB256           | 256-Ball Fine-Pitch Ball Grid Array    |                    |

|            |                | CY37256VP160-66AI   | A160            | 160-Lead Thin Quad Flat Pack           | Industrial         |

|            |                | CY37256VP256-66BGI  | BG292           | 292-Ball Plastic Ball Grid Array       |                    |

|            |                | CY37256VP256-66BBI  | BB256           | 256-Ball Fine-Pitch Ball Grid Array    |                    |

|            |                | 5962-9952401QZC     | U162            | 160-Lead Ceramic Quad Flat Pack        | Military           |

| 384        | 83             | CY37384VP208-83NC   | N208            | 208-Lead Plastic Quad Flat Pack        | Commercial         |

|            |                | CY37384VP256-83BGC  | BG292           | 292-Ball Plastic Ball Grid Array       |                    |

|            | 66             | CY37384VP208-66NC   | N208            | 208-Lead Plastic Quad Flat Pack        | Commercial         |

|            |                | CY37384VP256-66BGC  | BG292           | 292-Ball Plastic Ball Grid Array       |                    |

|            |                | CY37384VP208-66NI   | N208            | 208-Lead Plastic Quad Flat Pack        | Industrial         |

|            |                | CY37384VP256-66BGI  | BG292           | 292-Ball Plastic Ball Grid Array       |                    |

| 512        | 83             | CY37512VP208-83NC   | N208            | 208-Lead Plastic Quad Flat Pack        | Commercial         |

|            |                | CY37512VP256-83BGC  | BG292           | 292-Ball Plastic Ball Grid Array       |                    |

|            |                | CY37512VP352-83BGC  | BG388           | 388-Ball Plastic Ball Grid Array       |                    |

|            |                | CY37512VP400-83BBC  | BB400           | 400-Ball Fine-Pitch Ball Grid Array    |                    |

|            | 66             | CY37512VP208-66NC   | N208            | 208-Lead Plastic Quad Flat Pack        | Commercial         |

|            |                | CY37512VP256-66BGC  | BG292           | 292-Ball Plastic Ball Grid Array       |                    |

|            |                | CY37512VP352-66BGC  | BG388           | 388-Ball Plastic Ball Grid Array       |                    |

|            |                | CY37512VP400-66BBC  | BB400           | 400-Ball Fine-Pitch Ball Grid Array    |                    |

|            |                | CY37512VP208-66NI   | N208            | 208-Lead Plastic Quad Flat Pack        | Industrial         |

|            |                | CY37512VP256-66BGI  | BG292           | 292-Ball Plastic Ball Grid Array       |                    |

|            |                | CY37512VP352-66BGI  | BG388           | 388-Ball Plastic Ball Grid Array       |                    |

|            |                | CY37512VP400-66BBI  | BB400           | 400-Ball Fine-Pitch Ball Grid Array    |                    |

|            |                | 5962-9952601QZC     | U208            | 208-Lead Ceramic Quad Flat Pack        | Military           |

# 44-Lead Ceramic Leaded Chip Carrier Y67

# 100-Lead Lead (Pb)-Free Thin Plastic Quad Flat Pack (TQFP) A100

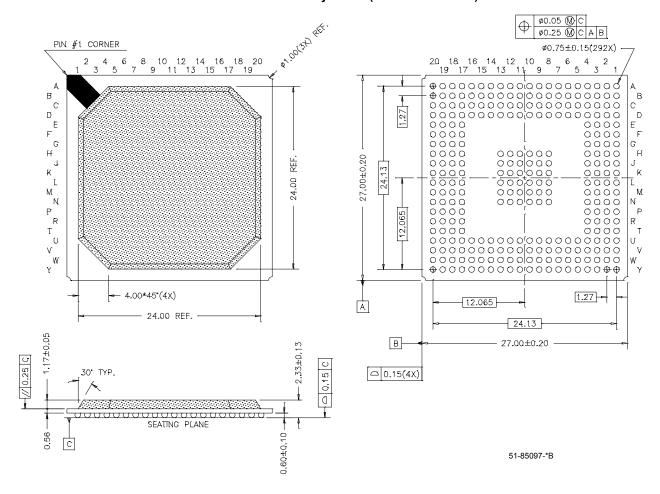

# 292-Ball Plastic Ball Grid Array PBGA (27 x 27 x 2.33 mm) BG292