#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | H8S/2000                                                                      |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 26MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, SCI                                                         |

| Peripherals                | POR, PWM, WDT                                                                 |

| Number of I/O              | 104                                                                           |

| Program Memory Size        | 512KB (512K x 8)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 32K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                     |

| Data Converters            | A/D 16x10b; D/A 2x8b                                                          |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 176-LFBGA                                                                     |

| Supplier Device Package    | 176-LFBGA (13x13)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2506br26dv |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Section 2 CPU

| Origin of                |                                                      |                  | Vector Address* |                |          |

|--------------------------|------------------------------------------------------|------------------|-----------------|----------------|----------|

| Interrupt<br>Source      | Interrupt Source                                     | Vector<br>Number | Advanced Mode   | -<br>IPR       | Priority |

| SCI channel 2            | TXI2 (transmit data empty 2)                         | 90               | H'0168          | IPRK2 to IPRK0 | High     |

|                          | TEI2 (transmit end 2)                                | 91               | H'016C          | _              | <b>≜</b> |

| 8-bit timer              | CMIA2 (compare-match A2)                             | 92               | H'0170          | IPRL6 to IPRL4 | _        |

| channel 2                | CMIB2 (compare-match B2)                             | 93               | H'0174          | -              |          |

|                          | OVI2 (overflow 2)                                    | 94               | H'0178          | -              |          |

| _                        | Reserved                                             | 95               | H'017C          | -              |          |

| 8-bit timer              | CMIA3 (compare-match A3)                             | 96               | H'0180          | -              |          |

| channel 3                | CMIB3 (compare-match B3)                             | 97               | H'0184          | -              |          |

|                          | OVI3 (overflow 3)                                    | 98               | H'0188          | -              |          |

|                          | Reserved                                             | 99               | H'018C          | -              |          |

| IEB                      | IERSI (reception status)                             | 104              | H'01A0          | IPRM6 to IPRM4 | -        |

| (H8S/2552<br>Group only) | IERxI (RxRDY)                                        | 105              | H'01A4          | -              |          |

| Group only)              | IETxI (TxRDY)                                        | 106              | H'01A8          | -              |          |

|                          | IETSI (transmission status)                          | 107              | H'01AC          | -              |          |

| HCAN                     | ERS0, OVR0, RM1, SLE0                                | 108              | H'01B0          | IPRM2 to IPRM0 | -        |

| (H8S/2556<br>Group only) | RM0                                                  | 109              | H'01B4          | -              |          |

| IIC2 channel 0           | IICI0 (1-byte transmission/<br>reception completion) | 110              | H'01B8          | -              |          |

| IIC2 channel 1           | IICI1 (1-byte transmission/<br>reception completion) | 111              | H'01BC          | -              |          |

| SCI channel 3            | ERI3 (receive error 3)                               | 120              | H'01E0          | IPRO6 to IPRO4 | -        |

|                          | RXI3 (receive completion 3)                          | 121              | H'01E4          | -              |          |

|                          | TXI3 (transmit data empty 3)                         | 122              | H'01E8          | -              |          |

|                          | TEI3 (transmit end 3)                                | 123              | H'01EC          | -              |          |

| SCI channel 4            | ERI4 (receive error 4)                               | 124              | H'01F0          | IPRO2 to IPRO0 | -        |

|                          | RXI4 (receive completion 4)                          | 125              | H'01F4          | _              |          |

|                          | TXI4 (transmit data empty 4)                         | 126              | H'01F8          | _              | Ļ        |

|                          | TEI4 (transmit end 4)                                | 127              | H'01FC          | -              | Low      |

RENESAS

Note: \* Indicates lower 16 bits of the start address.

## 7.2 Input/Output Pins

Table 7.1 summarizes the pins of the bus controller.

### Table 7.1Pin Configuration

| Name                                     | Symbol                                              | I/O    | Function                                                                                                                  |

|------------------------------------------|-----------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------|

| Address strove                           | ĀS                                                  | Output | Strobe signal indicating that address output on address bus is enabled.                                                   |

| Read                                     | RD                                                  | Output | Strobe signal indicating that external address space is being read.                                                       |

| High write                               | HWR                                                 | Output | Strobe signal indicating that external address space is to be written, and upper half (D15 to D8) of data bus is enabled. |

| Low write                                | LWR                                                 | Output | Strobe signal indicating that external address space is to be written, and lower half (D7 to D0) of data bus is enabled.  |

| Chip select 0 to 7                       | $\overline{\text{CS0}}$ to $\overline{\text{CS7}}*$ | Output | Strobe signal indicating that areas 0 to 7 are selected.                                                                  |

| Wait                                     | WAIT                                                | Input  | Wait request signal when accessing external 3-state access space.                                                         |

| Bus mastership request                   | BREQ                                                | Input  | Request signal that releases bus to external device.                                                                      |

| Bus mastership<br>request<br>acknowledge | BACK                                                | Output | Acknowledge signal indicating that bus has been released.                                                                 |

Note: \*  $\overline{\text{CS1}}$  and  $\overline{\text{CS2}}$  are not provided in the H8S/2556 Group.

## 7.3 **Register Descriptions**

The bus controller has the following registers.

- Bus width control register (ABWCR)

- Access state control register (ASTCR)

- Wait control register H (WCRH)

- Wait control register L (WCRL)

- Bus control register H (BCRH)

- Bus control register L (BCRL)

- Pin function control register (PFCR)

#### 7.3.3 Wait Control Registers H and L (WCRH, WCRL)

WCRH and WCRL select the number of program wait states for each area.

Program wait states are not inserted in the case of on-chip memory or internal I/O registers.

• WCRH

|     |          | Initial |     |                                                                                                                                                |

|-----|----------|---------|-----|------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Bit Name | Value   | R/W | Description                                                                                                                                    |

| 7   | W71      | 1       | R/W | Area 7 Wait Control 1 and 0                                                                                                                    |

| 6   | W70      | 1       | R/W | These bits select the number of program wait states when area 7 in external address space is accessed while the AST7 bit in ASTCR is set to 1. |

|     |          |         |     | 00: Program wait states are not inserted                                                                                                       |

|     |          |         |     | 01: 1 program wait state is inserted                                                                                                           |

|     |          |         |     | 10: 2 program wait states are inserted                                                                                                         |

|     |          |         |     | 11: 3 program wait states are inserted                                                                                                         |

| 5   | W61      | 1       | R/W | Area 6 Wait Control 1 and 0                                                                                                                    |

| 4   | W60      | 1       | R/W | These bits select the number of program wait states when area 6 in external address space is accessed while the AST6 bit in ASTCR is set to 1. |

|     |          |         |     | 00: Program wait states are not inserted                                                                                                       |

|     |          |         |     | 01: 1 program wait state is inserted                                                                                                           |

|     |          |         |     | 10: 2 program wait states are inserted                                                                                                         |

|     |          |         |     | 11: 3 program wait states are inserted                                                                                                         |

| 3   | W51      | 1       | R/W | Area 5 Wait Control 1 and 0                                                                                                                    |

| 2   | W50      | 1       | R/W | These bits select the number of program wait states when area 5 in external address space is accessed while the AST5 bit in ASTCR is set to 1. |

|     |          |         |     | 00: Program wait states are not inserted                                                                                                       |

|     |          |         |     | 01: 1 program wait state is inserted                                                                                                           |

|     |          |         |     | 10: 2 program wait states are inserted                                                                                                         |

|     |          |         |     | 11: 3 program wait states are inserted                                                                                                         |

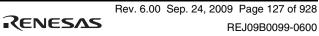

Write after Read: If an external write occurs after an external read while the ICIS0 bit in BCRH is set to 1, an idle cycle is inserted at the start of the write cycle.

Figure 7.28 shows an example of the operation in this case. In this example, bus cycle A is a read cycle from ROM with a long output floating time, and bus cycle B is a CPU write cycle. In (a), an idle cycle is not inserted, and a collision occurs in cycle B between the read data from ROM and the CPU write data. In (b), an idle cycle is inserted, and a data collision is prevented.

Figure 7.28 Example of Idle Cycle Operation (2)

# 9.13 Port F

Port F is an 8-bit I/O port and has the following registers.

- Port F data direction register (PFDDR)

- Port F data register (PFDR)

- Port F register (PORTF)

### 9.13.1 Port F Data Direction Register (PFDDR)

PFDDR specifies input or output the port F pins using the individual bits. PFDDR cannot be read; if it is, the read value is undefined. Since this register is a write-only register, bit-manipulation instructions should not be used when writing. See section 2.9.4, Access Method for Registers with Write-only Bits.

| Bit | Bit Name | Initial Value | R/W | Description                                                                                                |

|-----|----------|---------------|-----|------------------------------------------------------------------------------------------------------------|

| 7   | PF7DDR   | 0/1*          | W   | When a pin is specified as a general purpose I/O                                                           |

| 6   | PF6DDR   | 0             | W   | port, setting this bit to 1 makes the corresponding port F pin an output pin. Clearing this bit to 0 makes |

| 5   | PF5DDR   | 0             | W   | the pin an input pin.                                                                                      |

| 4   | PF4DDR   | 0             | W   |                                                                                                            |

| 3   | PF3DDR   | 0             | W   |                                                                                                            |

| 2   | PF2DDR   | 0             | W   |                                                                                                            |

| 1   | PF1DDR   | 0             | W   |                                                                                                            |

| 0   | PF0DDR   | 0             | W   |                                                                                                            |

Note: \* PF7DDR is initialized to 1 in mode 6 and 0 in mode 7.

#### 10.3.1 Timer Control Register (TCR)

The TCR registers control the TCNT operation for each channel. The TPU has a total of six TCR registers, one for each channel (channels 0 to 5). TCR register settings should be conducted only when TCNT operation is stopped.

| Bit | Bit Name | Initial<br>value | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|----------|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CCLR2    | 0                | R/W | Counter Clear 2 to 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6   | CCLR1    | 0                | R/W | These bits select the TCNT counter clearing source. See                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5   | CCLR0    | 0                | R/W | tables 10.3 and 10.4 for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4   | CKEG1    | 0                | R/W | Clock Edge 1 and 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3   | CKEG0    | 0                | R/W | These bits select the input clock edge. When the input clock is counted using both edges, the input clock period is halved (e.g. $\phi/4$ both edges = $\phi/2$ rising edge). If phase counting mode is used on channels 1, 2, 4, and 5, this setting is ignored and the phase counting mode setting has priority. Internal clock edge selection is valid when the input clock is $\phi/4$ or slower. This setting is ignored if the input clock is $\phi/4$ , or when overflow/underflow of another channel is selected. (The clock is counted at the falling edge when $\phi/1$ is selected.) |

|     |          |                  |     | 00: Count at rising edge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |          |                  |     | 01: Count at falling edge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |          |                  |     | 1X: Count at both edges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |          |                  |     | Legend:<br>X: Don't care                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2   | TPSC2    | 0                | R/W | Time Prescaler 2 to 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1   | TPSC1    | 0                | R/W | These bits select the TCNT counter clock. The clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0   | TPSC0    | 0                | R/W | source can be selected independently for each channel.<br>See tables 10.5 to 10.10 for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

• TIORH\_0, TIOR\_1, TIOR\_2, TIORH\_3, TIOR\_4, TIOR\_5

| Bit | Bit Name | Initial<br>value | R/W | Description                                            |

|-----|----------|------------------|-----|--------------------------------------------------------|

| 7   | IOB3     | 0                | R/W | I/O Control B3 to B0                                   |

| 6   | IOB2     | 0                | R/W | Specify the function of TGRB. See tables 10.12, 10.14, |

| 5   | IOB1     | 0                | R/W | 10.15, 10.16, 10.18, and 10.19 for details.            |

| 4   | IOB0     | 0                | R/W |                                                        |

| 3   | IOA3     | 0                | R/W | I/O Control A3 to A0                                   |

| 2   | IOA2     | 0                | R/W | Specify the function of TGRA. See tables 10.20, 10,22, |

| 1   | IOA1     | 0                | R/W | 10.23, 10.24, 10.26, and 10.27 for details.            |

| 0   | IOA0     | 0                | R/W |                                                        |

• TIORL\_0, TIORL\_3

| Bit | Bit Name | Initial<br>value | R/W | Description                                               |

|-----|----------|------------------|-----|-----------------------------------------------------------|

| 7   | IOD3     | 0                | R/W | I/O Control D3 to D0                                      |

| 6   | IOD2     | 0                | R/W | Specify the function of TGRD. See tables 10.13, and 10.17 |

| 5   | IOD1     | 0                | R/W | for details.                                              |

| 4   | IOD0     | 0                | R/W |                                                           |

| 3   | IOC3     | 0                | R/W | I/O Control C3 to C0                                      |

| 2   | IOC2     | 0                | R/W | Specify the function of TGRC. See tables 10.21, and 10.25 |

| 1   | IOC1     | 0                | R/W | for details.                                              |

| 0   | IOC0     | 0                | R/W |                                                           |

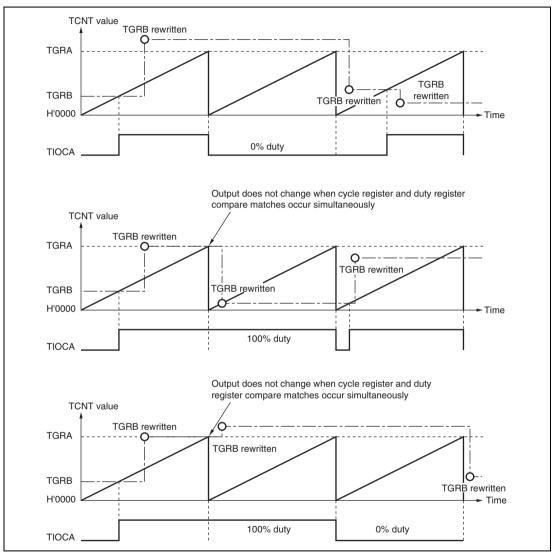

Figure 10.23 shows examples of PWM waveform output with 0% duty and 100% duty in PWM mode.

Figure 10.23 Example of PWM Mode Operation (3)

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                                                                                                |

|-----|----------|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ICE      | 0                | R/W | I <sup>2</sup> C Bus Interface Enable                                                                                                                                                                                                                                                                                                                                      |

|     |          |                  |     | 0: This module is halted. (SCL and SDA pins are set to port function.)                                                                                                                                                                                                                                                                                                     |

|     |          |                  |     | 1: This bit is enabled for transfer operations. (SCL and SDA pins are bus drive state.)                                                                                                                                                                                                                                                                                    |

| 6   | RCVD     | 0                | R/W | Reception Disable                                                                                                                                                                                                                                                                                                                                                          |

|     |          |                  |     | This bit enables or disables the next receive operation while TRS is 0 and until ICDRR is read.                                                                                                                                                                                                                                                                            |

|     |          |                  |     | 0: Enables next reception                                                                                                                                                                                                                                                                                                                                                  |

|     |          |                  |     | 1: Disables next reception                                                                                                                                                                                                                                                                                                                                                 |

| 5   | MST      | 0                | R/W | Master/Slave Select                                                                                                                                                                                                                                                                                                                                                        |

| 4   | TRS      | 0                | R/W | Transmit/Receive Select                                                                                                                                                                                                                                                                                                                                                    |

|     |          |                  |     | In master mode with the I <sup>2</sup> C bus format, when arbitration is<br>lost, MST and TRS are both reset by hardware, causing a<br>transition to slave receive mode. Modification of the TRS<br>bit should be made between transfer frames.                                                                                                                            |

|     |          |                  |     | After data receive has been started in slave receive mode,<br>when the first seven bits of the receive data agree with the<br>slave address that is set to SAR and the eighth bit is 1,<br>TRS is automatically set to 1. If an overrun error occurs in<br>master mode with the clock synchronous serial format,<br>MST is cleared to 0 and slave receive mode is entered. |

|     |          |                  |     | Operating modes are described below according to MST<br>and TRS combination. When clocked synchronous serial<br>format is selected and MST is 1, clock is output.                                                                                                                                                                                                          |

|     |          |                  |     | 00: Slave receive mode                                                                                                                                                                                                                                                                                                                                                     |

|     |          |                  |     | 01: Slave transmit mode                                                                                                                                                                                                                                                                                                                                                    |

|     |          |                  |     | 10: Master receive mode                                                                                                                                                                                                                                                                                                                                                    |

|     |          |                  |     | 11: Master transmit mode                                                                                                                                                                                                                                                                                                                                                   |

| 3   | CKS3     | 0                | R/W | Transfer Clock Select 3 to 0                                                                                                                                                                                                                                                                                                                                               |

| 2   | CKS2     | 0                | R/W | Set these bits according to the necessary transfer rate in                                                                                                                                                                                                                                                                                                                 |

| 1   | CKS1     | 0                | R/W | master mode (see table 14.2). During slave mode, these bits are specified to ensure enough time for data setup in                                                                                                                                                                                                                                                          |

| 0   | CKS0     | 0                | R/W | transmit mode. When CKS3 is 0, the time is 10 tcyc, and CKS3 is 1, 20 tcyc.                                                                                                                                                                                                                                                                                                |

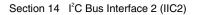

Figure 14.7 Master Receive Mode Operation Timing (1)

#### 17.3.4 IEBus Master Unit Address Register 1 (IEAR1)

IEAR1 sets the lower 4 bits of the master unit address and communications mode. In master communications, the master unit address becomes the master address field value. In slave communications, the master unit address is compared with the received slave address field.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                          |

|-----|----------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIL | Bit Name | value            | R/W | Description                                                                                                                                                                                                                                                                                          |

| 7   | IAR3     | 0                | R/W | Lower 4 Bits of IEBus Master Unit Address                                                                                                                                                                                                                                                            |

| 6   | IAR2     | 0                | R/W | Set the lower 4 bits of the master unit address.                                                                                                                                                                                                                                                     |

| 5   | IAR1     | 0                | R/W |                                                                                                                                                                                                                                                                                                      |

| 4   | IAR0     | 0                | R/W |                                                                                                                                                                                                                                                                                                      |

| 3   | IMD1     | 0                | R/W | IEBus Communications Mode                                                                                                                                                                                                                                                                            |

| 2   | IMD0     | 0                | R/W | Set IEBus communications mode.                                                                                                                                                                                                                                                                       |

|     |          |                  |     | 00: Communications mode 0                                                                                                                                                                                                                                                                            |

|     |          |                  |     | 01: Communications mode 1                                                                                                                                                                                                                                                                            |

|     |          |                  |     | 10: Communications mode 2                                                                                                                                                                                                                                                                            |

|     |          |                  |     | 11: Setting prohibited                                                                                                                                                                                                                                                                               |

| 1   | _        | 0                |     | Reserved                                                                                                                                                                                                                                                                                             |

|     |          |                  |     | This bit is always read as 0 and cannot be modified.                                                                                                                                                                                                                                                 |

| 0   | STE      | 0                | R/W | Slave Transmission Setting                                                                                                                                                                                                                                                                           |

|     |          |                  |     | Sets bit 4 in the slave status register. Transmitting the slave status register informs the master unit that the slave transmission enabled state is entered by setting this bit to 1. Note that this bit only sets the slave status register value and does not affect slave transmission directly. |

|     |          |                  |     | 0: Bit 4 in the slave status register is 0 (slave transmission stop state)                                                                                                                                                                                                                           |

|     |          |                  |     | 1: Bit 4 in the slave status register is 1 (slave transmission enabled state)                                                                                                                                                                                                                        |

## (4) RO Flag

When retransfer is performed up to the maximum number of transfer bytes defined by the protocol because of reception of a NAK from the receive side during data field transmission, the number of transferred bytes may be less than that of bytes specified by the message length. At this time the RO flag is set. Moreover, when the value of the message length bits is greater than the maximum number of transfer bytes, the RO flag is also set. The RO flag is not set if the maximum number of transfer bytes defined by the protocol is specified (for example, 32-byte message length is specified in mode 1) and the transfer is performed correctly.

If the RO flag is set to 1, the TxE flag is set to 1 and the wait state is entered.

### (5) ACK Flag

- If a NAK is received in an acknowledge bit before the message length field transmission, the ACK flag is set, the TxE flag is set, and then the wait state is entered.

- If a NAK is received in an acknowledge bit of the data field, data is automatically retransmitted up to the maximum number of transfer bytes defined by the protocol. If an ACK is received in an acknowledge bit during retransfer and the following data is transmitted correctly, the ACK flag is not set. If a NAK is received in the last data transfer during the retransfer for the maximum number of transfer bytes, the ACK flag is set to 1 and the wait state is entered.

- Note: Even if a NAK is received from the receive side during the data field transmission, retransfer is performed up to the maximum number of transfer bytes defined by the protocol, and the number of transferred bytes is less than that of bytes specified by the message length bits, an ACK may be received in the acknowledge bit in the last data transfer. In this case, the ACK flag is not set although the RO flag is set.

### 17.6.5 Error Flags in IEREF

### (1) OVE Flag

When the OVE flag is set, the RxE flag is also set. If an overrun error is cleared and the OVE flag is also cleared, the IEBus receive operation is continued. For details, see section 17.6.3, RxRDY Flag and Overrun Error.

### (2) RTME Flag

If a timing error occurs during data reception after reception starts (the RxS flag is set to 1), the RTME flag is set to 1, RxE flag is set to 1, and the wait state is entered. When a timing error occurs before reception starts, this flag is not set and the reception frame is discarded.

RENESAS

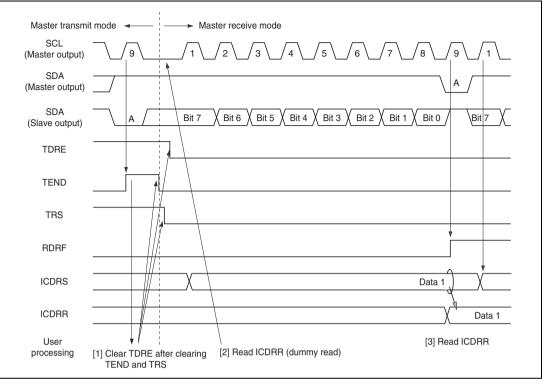

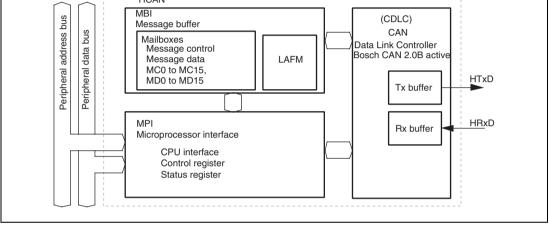

Figure 18.1 HCAN Block Diagram

• Message Buffer Interface (MBI)

The MBI, consisting of mailboxes and a local acceptance filter mask (LAFM), stores CAN transmit/receive messages (identifiers, data, etc.) Transmit messages are written by the CPU. For receive messages, the data received by the CDLC is stored automatically.

• Microprocessor Interface (MPI)

The MPI, consisting of a bus interface, control register, status register, etc., controls HCAN internal data, status, and so forth.

• CAN Data Link Controller (CDLC)

The CDLC transmits and receives of messages conforming to the Bosch CAN Ver. 2.0B active standard (data frames, remote frames, error frames, overload frames, inter-frame spacing), as well as CRC checking, bus arbitration, and other functions.

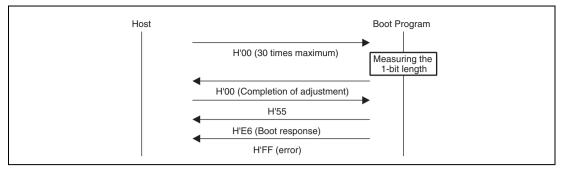

Figure 20.24 Bit-Rate-Adjustment Sequence

#### (3) Communications Protocol

After adjustment of the bit rate, the protocol for communications between the host and the boot program is as shown below.

1. One-byte commands and one-byte responses

These commands and responses are comprised of a single byte. These are consists of the inquiries and the ACK for successful completion.

2. n-byte commands or n-byte responses

These commands and responses are comprised of n bytes of data. These are selections and responses to inquiries.

The amount of programming data is not included under this heading because it is determined in another command.

3. Error response

The error response is a response to inquiries that consists of an error response and an error code. The response comes in two bytes.

4. Programming of 128 bytes

The size is not specified in commands. The size of n is indicated in response to the programming unit inquiry.

5. Memory read response

This response consists of four bytes of data.

• SUM (one byte): Sum check for data being transmitted

### (14) User-Program Sum Check

The boot program will return the byte-by-byte total of the contents of the bytes of the user program.

Command H'4B

• Command, H'4B, (one byte): Sum check for user program

| Response | H'5B | Size | Checksum of user program | SUM |

|----------|------|------|--------------------------|-----|

|          |      |      |                          |     |

- Response, H'5B, (one byte): Response to the sum check of the user program

- Size (one byte): The number of bytes that represents the checksum This is fixed to 4.

- Checksum of user boot program (four bytes): Checksum of user MATs The total of the data is obtained in byte units.

- SUM (one byte): Sum check for data being transmitted

#### (15) User Boot MAT Blank Check

The boot program will check whether or not all user boot MATs are blank and return the result.

Command H'4C

• Command, H'4C, (one byte): Blank check for user boot MAT

### Response H'06

• Response, H'06, (one byte): Response to the blank check of user boot MAT If all user MATs are blank (H'FF), the boot program will return ACK.

Error Response

H'CC H'52

- Error Response, H'CC, (one byte): Response to blank check for user boot MAT

- Error Code, H'52, (one byte): Erasure has not been completed.

### (16) User MAT Blank Check

The boot program will check whether or not all user MATs are blank and return the result.

Command H'4D

• Command, H'4D, (one byte): Blank check for user MATs

| Register<br>Abbreviation | Bit 7          | Bit 6          | Bit 5          | Bit 4        | Bit 3          | Bit 2          | Bit 1          | Bit 0          | Module |

|--------------------------|----------------|----------------|----------------|--------------|----------------|----------------|----------------|----------------|--------|

| TCSR_0                   | OVF            | WT / ĪT        | TME            | _            | _              | CKS2           | CKS1           | CKS0           | WDT_0  |

| TCNT_0                   | Bit7           | Bit6           | Bit5           | Bit4         | Bit3           | Bit2           | Bit1           | Bit0           | -      |

| RSTCSR                   | WOVF           | RSTE           | RSTS           | _            | _              | _              | _              | _              | -      |

| SMR_0*1                  | C/Ā<br>(GM)    | CHR<br>(BLK)   | PE<br>(PE)     | 0/Ē<br>(0/Ē) | STOP<br>(BCP1) | MP<br>(BCP0)   | CKS1<br>(CKS1) | CKS0<br>(CKS0) | SCI_0  |

| BRR_0                    | Bit7           | Bit6           | Bit5           | Bit4         | Bit3           | Bit2           | Bit1           | Bit0           | -      |

| SCR_0                    | TIE            | RIE            | TE             | RE           | MPIE           | TEIE           | CKE1           | CKE0           | -      |

| TDR_0                    | Bit7           | Bit6           | Bit5           | Bit4         | Bit3           | Bit2           | Bit1           | Bit0           | -      |

| SSR_0*1                  | TDRE<br>(TDRE) | RDRF<br>(RDRF) | ORER<br>(ORER) | FER<br>(ERS) | PER<br>(PER)   | TEND<br>(TEND) | MPB<br>(MPB)   | MPBT<br>(MPBT) | -      |

| RDR_0                    | Bit7           | Bit6           | Bit5           | Bit4         | Bit3           | Bit2           | Bit1           | Bit0           | _      |

| SCMR_0                   | _              | _              | _              |              | SDIR           | SINV           | _              | SMIF           | -      |

| SMR_1*1                  | C/Ā<br>(GM)    | CHR<br>(BLK)   | PE<br>(PE)     | O/Ē<br>(O/Ē) | STOP<br>(BCP1) | MP<br>(BCP0)   | CKS1<br>(CKS1) | CKS0<br>(CKS0) | SCI_1  |

| BRR_1                    | Bit7           | Bit6           | Bit5           | Bit4         | Bit3           | Bit2           | Bit1           | Bit0           | -      |

| SCR_1                    | TIE            | RIE            | TE             | RE           | MPIE           | TEIE           | CKE1           | CKE0           | _      |

| TDR_1                    | Bit7           | Bit6           | Bit5           | Bit4         | Bit3           | Bit2           | Bit1           | Bit0           | _      |

| SSR_1*1                  | TDRE<br>(TDRE) | RDRF<br>(RDRF) | ORER<br>(ORER) | FER<br>(ERS) | PER<br>(PER)   | TEND<br>(TEND) | MPB<br>(MPB)   | MPBT<br>(MPBT) | _      |

| RDR_1                    | Bit7           | Bit6           | Bit5           | Bit4         | Bit3           | Bit2           | Bit1           | Bit0           | _      |

| SCMR_1                   | _              | _              | _              | _            | SDIR           | SINV           | _              | SMIF           | -      |

| SMR_2*1                  | C/Ā<br>(GM)    | CHR<br>(BLK)   | PE<br>(PE)     | 0/Ē<br>(0/Ē) | STOP<br>(BCP1) | MP<br>(BCP0)   | CKS1<br>(CKS1) | CKS0<br>(CKS0) | SCI_2  |

| BRR_2                    | Bit7           | Bit6           | Bit5           | Bit4         | Bit3           | Bit2           | Bit1           | Bit0           | -      |

| SCR_2                    | TIE            | RIE            | TE             | RE           | MPIE           | TEIE           | CKE1           | CKE0           | -      |

| TDR_2                    | Bit7           | Bit6           | Bit5           | Bit4         | Bit3           | Bit2           | Bit1           | Bit0           | -      |

| SSR_2*1                  | TDRE<br>(TDRE) | RDRF<br>(RDRF) | ORER<br>(ORER) | FER<br>(ERS) | PER<br>(PER)   | TEND<br>(TEND) | MPB<br>(MPB)   | MPBT<br>(MPBT) | -      |

| RDR_2                    | Bit7           | Bit6           | Bit5           | Bit4         | Bit3           | Bit2           | Bit1           | Bit0           | -      |

| SCMR_2                   | _              | _              | _              | _            | SDIR           | SINV           |                | SMIF           | -      |

| Register<br>Abbreviation | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3   | Bit 2 | Bit 1 | Bit 0 | Module    |

|--------------------------|--------|-------|-------|-------|---------|-------|-------|-------|-----------|

| ADDRAH                   | AD9    | AD8   | AD7   | AD6   | AD5     | AD4   | AD3   | AD2   | A/D       |

| ADDRAL                   | AD1    | AD0   | _     |       | —       |       | _     | _     | converter |

| ADDRBH                   | AD9    | AD8   | AD7   | AD6   | AD5     | AD4   | AD3   | AD2   | _         |

| ADDRBL                   | AD1    | AD0   | _     |       |         |       |       |       | _         |

| ADDRCH                   | AD9    | AD8   | AD7   | AD6   | AD5     | AD4   | AD3   | AD2   | _         |

| ADDRCL                   | AD1    | AD0   | _     | _     | _       |       |       | _     | _         |

| ADDRDH                   | AD9    | AD8   | AD7   | AD6   | AD5     | AD4   | AD3   | AD2   | _         |

| ADDRDL                   | AD1    | AD0   | _     | _     | _       |       |       | _     | _         |

| ADCSR                    | ADF    | ADIE  | ADST  | SCAN  | СНЗ     | CH2   | CH1   | CH0   | _         |

| ADCR                     | TRGS1  | TRGS0 | _     | _     | CKS1    | CKS0  | _     | _     | _         |

| TCSR_1                   | OVF    | WT/IT | TME   | PSS   | RST/NMI | CKS2  | CKS1  | CKS0  | WDT_1     |

| TCNT_1                   | Bit7   | Bit6  | Bit5  | Bit4  | Bit3    | Bit2  | Bit1  | Bit0  | _         |

| FCCS                     | _      | _     | _     | FLER  | _       | _     | _     | SCO   | FLASH     |

| FPCS                     | _      | _     | _     | _     | _       |       |       | PPVS  | -         |

| FECS                     | _      | _     | _     | _     | _       | _     | _     | EPVB  | _         |

| FKEY                     | K7     | K6    | K5    | K4    | K3      | K2    | K1    | K0    | _         |

| FMATS                    | MS7    | MS6   | MS5   | MS4   | MS3     | MS2   | MS1   | MS0   | _         |

| FTDAR                    | TDER   | TDA6  | TDA5  | TDA4  | TDA3    | TDA2  | TDA1  | TDA0  | _         |

| FVACR                    | FVCHGE |       | _     | _     | _       | _     | _     | _     | _         |

| FVADRR                   | Bit31  | Bit30 | Bit29 | Bit28 | Bit27   | Bit26 | Bit25 | Bit24 | _         |

| FVADRE                   | Bit23  | Bit22 | Bit21 | Bit20 | Bit19   | Bit18 | Bit17 | Bit16 | _         |

| FVADRH                   | Bit15  | Bit14 | Bit13 | Bit12 | Bit11   | Bit10 | Bit9  | Bit8  | _         |

| FVADRL                   | Bit7   | Bit6  | Bit5  | Bit4  | Bit3    | Bit2  | Bit1  | Bit0  |           |

| PORT1                    | P17    | P16   | P15   | P14   | P13     | P12   | P11   | P10   | PORT      |

| PORT2                    | P27    | P26   | P25   | P24   | P23     | P22   | P21   | P20   | _         |

| PORT3                    | P37    | P36   | P35   | P34   | P33     | P32   | P31   | P30   | _         |

| PORT4                    | P47    | P46   | P45   | P44   | P43     | P42   | P41   | P40   |           |

| PORT5                    | _      | _     | _     | _     | _       | P52   | P51   | P50   | _         |

| PORT7                    | P77    | P76   | P75   | P74   | P73     | P72   | P71   | P70   | _         |

| PORT9                    | P97    | P96   | P95   | P94   | P93     | P92   | P91   | P90   | _         |

| PORTA                    | PA7    | PA6   | PA5   | PA4   | PA3     | PA2   | PA1   | PA0   | _         |

RENESAS

| Item                                            | Symbo             | ol Min. | Max. | Unit | Test Conditions |

|-------------------------------------------------|-------------------|---------|------|------|-----------------|

| NMI setup time                                  | t <sub>nmis</sub> | 250     | _    | ns   | Figure 24.8     |

| NMI hold time                                   | t <sub>nmin</sub> | 10      | _    | ns   |                 |

| NMI pulse width (exiting software standby mode) | t <sub>nmiw</sub> | 200     | —    | ns   |                 |

| IRQ setup time                                  | t <sub>irqs</sub> | 250     | _    | ns   |                 |

| IRQ hold time                                   | t <sub>irqh</sub> | 10      | _    | ns   |                 |

| IRQ pulse width (exiting software standby mode) | t <sub>iRQW</sub> | 200     | _    | ns   |                 |

Note: \* The regular specifications are supported in the H8S/2506 Group only.

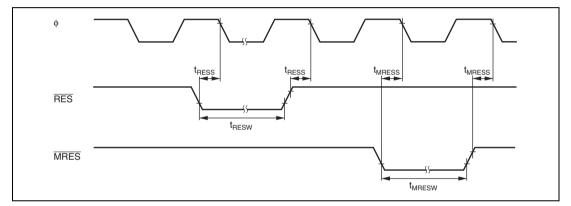

Figure 24.7 Reset Input Timing

Appendix