#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Discontinued at Digi-Key                                                      |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | TriCore™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                            |

| Speed                      | 66MHz                                                                         |

| Connectivity               | CANbus, SPI, UART/USART                                                       |

| Peripherals                | DMA, POR, WDT                                                                 |

| Number of I/O              | 81                                                                            |

| Program Memory Size        | 1MB (1M × 8)                                                                  |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 48K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.42V ~ 1.58V                                                                 |

| Data Converters            | A/D 36x12b                                                                    |

| Oscillator Type            | External                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 176-LQFP                                                                      |

| Supplier Device Package    | PG-LQFP-176-2                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/ft1162128f66hlaaxp |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Data Sheet, V1.0, Apr. 2008

# TC1161/TC1162 32-Bit Single-Chip Microcontroller TriCore

## Microcontrollers

Never stop thinking

#### TC1161/TC1162 Data Sheet Revision History: V1.0, 2008-04

| sion: V0.3 2007-03                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Subjects (major changes since last revision)                                                                                                       |

| VSSOSC3 is deleted from the TC1161/TC1162 Logic Symbol.                                                                                            |

| TDATA0 of Pin 17, TCLK0 of Pin 20, TCLK0 of Pin 74 and TDATA0 of Pin 77 are updated in the Pinning Diagram and Pin Definition and Functions Table. |

| Transmit DMA request in Block Diagram of ASC Interfaces is updated.                                                                                |

| Alternate output functions in block diagram of SSC interfaces are updated.                                                                         |

| Programmable baud rate of the MLI is updated.                                                                                                      |

| TDATA0 and TCLK0 of the block diagram of MLI interfaces are updated.                                                                               |

| The description for WDT double reset detection is updated.                                                                                         |

| The power sequencing details is updated.                                                                                                           |

| MLI timing, maximum operating frequency limit is extended, t31 is added.                                                                           |

| Thermal resistance junction leads is updated.                                                                                                      |

|                                                                                                                                                    |

#### Trademarks

TriCore® is a trademark of Infineon Technologies AG.

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

#### **Summary of Features**

- One 2-channel Fast Analog-to-Digital Converter unit (FADC) with concatenated comb filters for hardware data reduction: supporting 10-bit resolution, with minimum conversion time of 318.2 ns

- 32 analog input lines for ADC and FADC

- 81 digital general purpose I/O lines

- Digital I/O ports with 3.3 V capability

- On-chip debug support for OCDS Level 1 and 2 (CPU, DMA)

- Power Management System

- Clock Generation Unit with PLL

- Core supply voltage of 1.5 V

- I/O voltage of 3.3 V

- Full Industrial and Multi-Market temperature range: -40° to +85°C

- PG-LQFP-176-2 package

#### **General Device Information**

#### 2.4 Pad Driver and Input Classes Overview

The TC1161/TC1162 provides different types and classes of input and output lines. For understanding of the abbreviations in Table 2-2 starting at the next page, Table 2-1 gives an overview on the pad type and class types.

| Class | Power<br>Supply | Туре                | Sub Class                            | Speed<br>Grade | Termination                    |

|-------|-----------------|---------------------|--------------------------------------|----------------|--------------------------------|

| Α     | 3.3V            | LVTTL I/O,<br>LVTTL | <b>A1</b><br>(e.g. GPIO)             | 6 MHz          | No                             |

|       |                 | outputs             | A2<br>(e.g. serial<br>I/Os)          | 40 MHz         | Series termination recommended |

|       |                 |                     | <b>A3</b><br>(e.g. BRKIN,<br>BRKOUT) | 66 MHz/        | Yes, series<br>termination     |

|       |                 |                     | A4<br>(e.g.Trace Clock)              | 66 MHz         | Yes, series<br>termination     |

| С     | 3.3V            | LVDS                | _                                    | 50 MHz         | Parallel termination           |

| D     |                 | Analog<br>input     | -                                    | _              | -                              |

#### Table 2-1 Pad Driver and Input Classes Overview

#### **General Device Information**

#### Table 2-2Pin Definitions and Functions (cont'd)

| Symbol              | Pins                                            | I/O | Pad<br>Driver<br>Class | Power<br>Supply | Functions                                           |

|---------------------|-------------------------------------------------|-----|------------------------|-----------------|-----------------------------------------------------|

| Power Su            | upplies                                         | S   |                        |                 |                                                     |

| V <sub>DDM</sub>    | 54                                              | _   | -                      | _               | ADC Analog Part Power Supply (3.3 V)                |

| V <sub>SSM</sub>    | 53                                              | _   | _                      | _               | ADC Analog Part Ground for $V_{\text{DDM}}$         |

| V <sub>DDMF</sub>   | 24                                              | _   | -                      | _               | FADC Analog Part Power Supply (3.3 V)               |

| V <sub>SSMF</sub>   | 25                                              | _   | -                      | _               | FADC Analog Part Ground for $V_{\text{DDMF}}$       |

| $V_{DDAF}$          | 23                                              | -   | -                      | -               | FADC Analog Part Logic Power Supply (1.5 V)         |

| V <sub>SSAF</sub>   | 22                                              | _   | -                      | _               | FADC Analog Part Logic Ground for $V_{\text{DDAF}}$ |

| V <sub>AREF0</sub>  | 52                                              | _   | -                      | _               | ADC Reference Voltage                               |

|                     | 51                                              | _   | -                      | _               | ADC Reference Ground                                |

| V <sub>FAREF</sub>  | 26                                              | _   | -                      | _               | FADC Reference Voltage                              |

|                     | 27                                              | _   | -                      | _               | FADC Reference Ground                               |

| V <sub>DDOSC</sub>  | 105                                             | -   | -                      | -               | Main Oscillator and PLL Power Supply (1.5 V)        |

| V <sub>DDOSC3</sub> | 106                                             | _   | -                      | _               | Main Oscillator Power Supply (3.3 V)                |

| V <sub>ssosc</sub>  | 104                                             | _   | -                      | -               | Main Oscillator and PLL Ground                      |

|                     | 141                                             | _   | -                      | _               | Power Supply for Flash (3.3 V)                      |

| V <sub>DD</sub>     | 10,<br>68,<br>84,<br>99,<br>123,<br>153,<br>170 | _   | -                      | _               | Core Power Supply (1.5 V)                           |

#### **Functional Description**

#### Segment 14

From the SPB point of view (DMA and Cerberus), this memory segment allows accesses to the PMU Overlay memory (OVRAM), the DMI Local Data RAM (LDRAM), and the PMI scratch-pad RAM (SPRAM).

From the CPU point of view (PMI and DMI), this memory segment is reserved in the TC1161/TC1162.

#### Segment 15

From the SPB point of view (DMA and Cerberus), this memory segment allows accesses to all SFRs and CSFRs, and the MLI transfer windows.

From the CPU point of view (PMI and DMI), this memory segment allows accesses to all SFRs and CSFRs, and the MLI transfer windows.

#### **Functional Description**

#### 3.3.4 Address Map of the FPI Bus System

Table 3-3 and Table 3-4 shows the address maps of the FPI Bus System.

#### 3.3.4.1 Segments 0 to 14

**Table 3-3** shows the address maps of segments 0 to 14 as it is seen from the SPB bus masters, DMA and OCDS.

#### Table 3-3SPB Address Map of Segment 0 to 14

| Seg- | Address                                            | Size             | Description                      | Access   | з Туре   |

|------|----------------------------------------------------|------------------|----------------------------------|----------|----------|

| ment | Range                                              |                  |                                  | Read     | Write    |

| 0-7  | 0000 0000 <sub>H</sub> -<br>0000 0007 <sub>H</sub> | 8 byte           | Reserved (virtual address space) | MPN trap | MPN trap |

| _    | 0000 0008 <sub>H</sub> -<br>7FFF FFFF <sub>H</sub> | 8 × 256<br>Mbyte |                                  | SPBBE    | SPBBE    |

### TC1161/TC1162

#### Preliminary

#### **Functional Description**

#### Table 3-3 SPB Address Map of Segment 0 to 14 (cont'd)

| Seg- | Address                                            | Size           | Description                   | Access Type          |                        |  |

|------|----------------------------------------------------|----------------|-------------------------------|----------------------|------------------------|--|

| ment | Range                                              |                |                               | Read                 | Write                  |  |

| 10   | A000 0000 <sub>H</sub> -<br>A00F FFFF <sub>H</sub> | 1 Mbyte        | Program Flash (PFLASH)        | access               | access <sup>1)</sup>   |  |

|      | A010 0000 <sub>H</sub> -<br>A017 FFFF <sub>H</sub> | ≈ 0.5<br>Mbyte | Reserved                      | access <sup>2)</sup> | access <sup>1)2)</sup> |  |

|      | A017 8000 <sub>H</sub> -<br>A07F FFFF <sub>H</sub> | 6.5 Mbyte      | Reserved                      | LMBBE &<br>SPBBE     | LMBBE                  |  |

|      | A080 0000 <sub>H</sub> -<br>AFDF FFFF <sub>H</sub> | 246<br>Mbyte   | Reserved                      | LMBBE &<br>SPBBE     | LMBBE                  |  |

|      | AFE0 0000 <sub>H</sub> -<br>AFE0 1FFF <sub>H</sub> | 8 Kbyte        | Data Flash (DFLASH)<br>Bank 0 | access               | access <sup>1)</sup>   |  |

|      | AFE0 2000 <sub>H</sub> -<br>AFE0 3FFF <sub>H</sub> | 8 Kbyte        | Reserved                      | access <sup>2)</sup> | access <sup>1)2)</sup> |  |

|      | AFE0 4000 <sub>H</sub> -<br>AFE0 FFFF <sub>H</sub> | 48 Kbyte       | Reserved                      | LMBBE &<br>SPBBE     | LMBBE                  |  |

|      | AFE1 0000 <sub>H</sub> -<br>AFE1 1FFF <sub>H</sub> | 8 Kbyte        | Data Flash (DFLASH)<br>Bank 1 | access               | access <sup>1)</sup>   |  |

|      | AFE1 2000 <sub>H</sub> -<br>AFE1 3FFF <sub>H</sub> | 8 Kbyte        | Reserved                      | access <sup>2)</sup> | access <sup>1)2)</sup> |  |

|      | AFE1 4000 <sub>H</sub> -<br>AFF1 FFFF <sub>H</sub> |                |                               | LMBBE &<br>SPBBE     | ignore                 |  |

|      | AFF2 0000 <sub>H</sub> -<br>AFF5 FFFF <sub>H</sub> | 256<br>Kbyte   | Reserved                      |                      |                        |  |

|      | AFF6 0000 <sub>H</sub> -<br>AFFF BFFF <sub>H</sub> | 624<br>Kbyte   | Reserved                      |                      |                        |  |

|      | AFFF C000 <sub>H</sub> -<br>AFFF FFFF <sub>H</sub> | 16 Kbyte       | Boot ROM (BROM)               | access               |                        |  |

| 11   | B000 0000 <sub>H</sub> -<br>BFFF FFFF <sub>H</sub> | 256<br>Mbyte   | Reserved                      | SPBBE                | SPBBE                  |  |

| 12   | C000 0000 <sub>H</sub> -<br>C000 0FFF <sub>H</sub> | 4 Kbyte        | Overlay memory<br>(OVRAM)     | SPBBE                | SPBBE                  |  |

|      | С000 1000 <sub>н</sub> -<br>CFFF FFFF <sub>H</sub> | ≈ 256<br>Mbyte | Reserved                      | SPBBE                | SPBBE                  |  |

#### **Functional Description**

#### 3.3.5 Address Map of the Local Memory Bus (LMB)

Table 3-5 shows the address map as seen from the LMB bus masters (PMI and DMI).

| Seg- Address      |                                                    | Size             | Description                      | Action               |                        |  |

|-------------------|----------------------------------------------------|------------------|----------------------------------|----------------------|------------------------|--|

| ment              | Range                                              |                  |                                  | Read                 | Write                  |  |

| 0-7 <sup>1)</sup> | 0000 0000 <sub>H</sub> -<br>0000 0007 <sub>H</sub> | 8 byte           | Reserved (virtual address space) | MPN trap             | MPN trap               |  |

|                   | 0000 0008 <sub>H</sub> -<br>7FFF FFFF <sub>H</sub> | 8 × 256<br>Mbyte |                                  | SPBBET               | SPBBE                  |  |

| 8 <sup>1)</sup>   | 8000 0000 <sub>H</sub> -<br>800F FFFF <sub>H</sub> | 1 Mbyte          | Program Flash (PFLASH)           | access               | access <sup>2)</sup>   |  |

|                   | 8010 0000 <sub>H</sub> -<br>8017 7FFF <sub>H</sub> | ≈ 0.5<br>Mbyte   | Reserved                         | access <sup>3)</sup> | access <sup>2)3)</sup> |  |

|                   | 8017 8000 <sub>H</sub> -<br>807F FFFF <sub>H</sub> | 6.5 Mbyte        | Reserved                         | LMBBET               | LMBBET                 |  |

|                   | 8080 0000 <sub>H</sub> -<br>8FDF FFFF <sub>H</sub> | 246<br>Mbyte     | Reserved                         | LMBBET               | LMBBET                 |  |

|                   | 8FE0 0000 <sub>H</sub> -<br>8FE0 1FFF <sub>H</sub> | 8 Kbyte          | Data Flash (DFLASH)<br>Bank 0    | access               | access <sup>2)</sup>   |  |

|                   | 8FE0 2000 <sub>H</sub> -<br>8FE0 3FFF <sub>H</sub> | 8 Kbyte          | Reserved                         | access <sup>3)</sup> | access <sup>2)3)</sup> |  |

|                   | 8FE0 4000 <sub>H</sub> -<br>8FE0 FFFF <sub>H</sub> | 48 Kbyte         | Reserved                         | LMBBET               | LMBBET                 |  |

|                   | 8FE1 0000 <sub>H</sub> -<br>8FE1 1FFF <sub>H</sub> | 8 Kbyte          | Data Flash (DFLASH)<br>Bank 1    | access               | access <sup>2)</sup>   |  |

|                   | 8FE1 2000 <sub>H</sub> -<br>8FE1 3FFF <sub>H</sub> | 8 Kbyte          | Reserved                         | access <sup>3)</sup> | access <sup>2)3)</sup> |  |

|                   | 8FE1 4000 <sub>H</sub> -<br>8FF1 FFFF <sub>H</sub> | 1 Mbyte          | Reserved                         | LMBBET               | LMBBET                 |  |

|                   | 8FF2 0000 <sub>H</sub> -<br>8FF5 FFFF <sub>H</sub> | 256 Kbyte        | Reserved                         |                      |                        |  |

|                   | 8FF6 0000 <sub>H</sub> -<br>8FFF BFFF <sub>H</sub> | 624 Kbyte        | Reserved                         |                      |                        |  |

|                   | 8FFF C000 <sub>H</sub> -<br>8FFF FFFF <sub>H</sub> | 16 Kbyte         | Boot ROM (BROM)                  | access               | ]                      |  |

#### Table 3-5LMB Address Map

## TC1161/TC1162

#### Preliminary

#### **Functional Description**

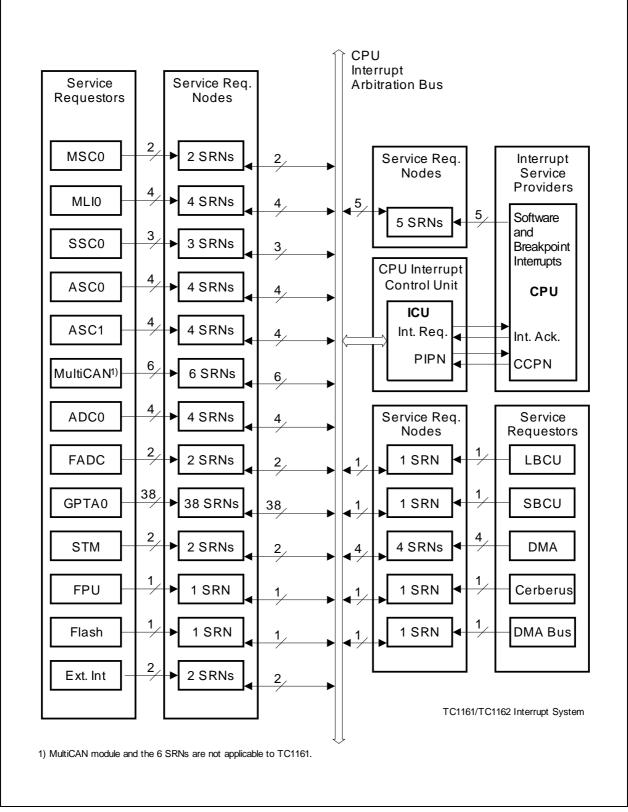

Figure 3-2 Block Diagram of the TC1161/TC1162 Interrupt System

#### **Functional Description**

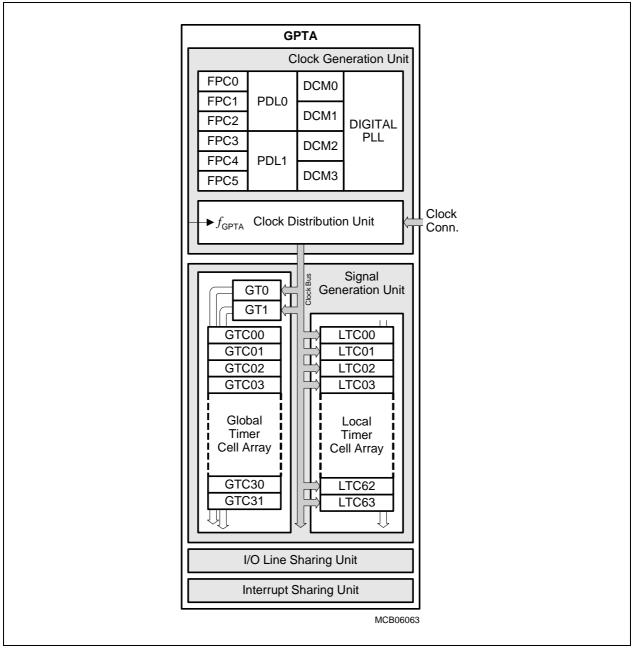

#### 3.12 General Purpose Timer Array

The GPTA provides a set of timer, compare, and capture functionalities that can be flexibly combined to form signal measurement and signal generation units. They are optimized for tasks typical of electrical motor control applications, but can also be used to generate simple and complex signal waveforms needed in other industrial applications.

The TC1161/TC1162 contains one General Purpose Timer Array (GPTA0). **Figure 3-9** shows a global view of the GPTA module.

Figure 3-9 Block Diagram of the GPTA Module

#### **Functional Description**

- Duty Cycle Measurement (DCM)

- Four independent units

- 0 100% margin and time-out handling

- $-f_{\rm GPTA}$  maximum resolution

- $-f_{\rm GPTA}/2$  maximum input signal frequency

- Digital Phase Locked Loop (PLL)

- One unit

- Arbitrary multiplication factor between 1 and 65535

- $f_{\rm GPTA}$  maximum resolution

- $-f_{GPTA}/2$  maximum input signal frequency

- Clock Distribution Unit (CDU)

- One unit

•

– Provides nine clock output signals:  $f_{\rm GPTA}$ , divided  $f_{\rm GPTA}$  clocks, FPC1/FPC4 outputs, DCM clock, LTC prescaler clock

#### **Signal Generation Unit**

- Global Timers (GT)

- Two independent units

- Two operating modes (Free-Running Timer and Reload Timer)

- 24-bit data width

- $-f_{\rm GPTA}$  maximum resolution

- $-f_{\rm GPTA}/2$  maximum input signal frequency

- Global Timer Cell (GTC)

- 32 units related to the Global Timers

- Two operating modes (Capture, Compare and Capture after Compare)

- 24-bit data width

- $f_{\rm GPTA}$  maximum resolution

- $-f_{\rm GPTA}/2$  maximum input signal frequency

- Local Timer Cell (LTC)

- 64 independent units

- Three basic operating modes (Timer, Capture and Compare) for 63 units

- Special compare modes for one unit

- 16-bit data width

- $-f_{GPTA}$  maximum resolution

- $-f_{GPTA}/2$  maximum input signal frequency

#### **Interrupt Control Unit**

• 111 interrupt sources, generating up to 38 service requests

#### **Functional Description**

## 3.14 Fast Analog-to-Digital Converter Unit (FADC)

The on-chip FADC module of the TC1161/TC1162 basically is a 2-channel A/D converter with 10-bit resolution that operates by the method of the successive approximation.

As shown in Figure 3-11, the main FADC functional blocks are:

- The Input Stage contains the differential inputs and the programmable amplifier

- The A/D Converter is responsible for the analog-to-digital conversion

- The Data Reduction Unit contains programmable antialiasing and data reduction filters

- The Channel Trigger Control block determines the trigger and gating conditions for the two FADC channels

- The Channel Timers can independently trigger the conversion of each FADC channel

- The A/D Control block is responsible for the overall FADC functionality

The FADC module is supplied by the following power supply and reference voltage lines:

- $V_{\text{DDMF}}/V_{\text{DDMF}}$ :FADC Analog Part Power Supply (3.3 V)

- V<sub>DDAF</sub>/V<sub>DDAF</sub>:FADC Analog Part Logic Power Supply (1.5 V)

- V<sub>FAREF</sub>/V<sub>FAGND</sub>:FADC Reference Voltage (3.3 V)/FADC Reference Ground

#### **Functional Description**

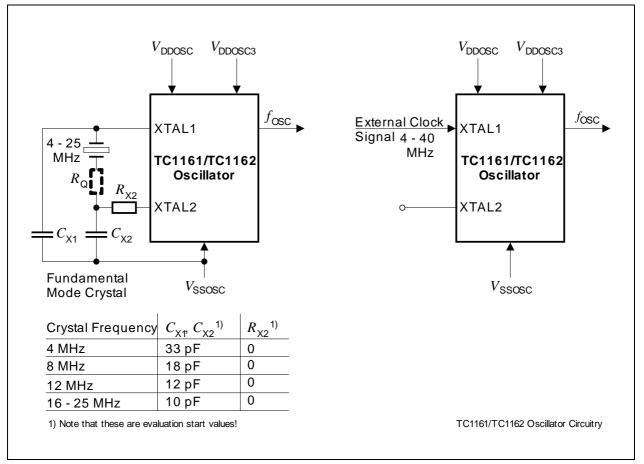

Oscillation measurement with the final target system is strongly recommended to verify the input amplitude at XTAL1 and to determine the actual oscillation allowance (margin negative resistance) for the oscillator-crystal system.

When using an external clock signal, the signal must be connected to XTAL1. XTAL2 is left open (unconnected). The external clock frequency can be in the range of 0 - 40 MHz if the PLL is bypassed, and 4 - 40 MHz if the PLL is used.

The oscillator can also be used in combination with a ceramic resonator. The final circuitry must also be verified by the resonator vendor.

**Figure 3-15** shows the recommended external oscillator circuitries for both operating modes, external crystal mode and external input clock mode. A block capacitor is recommended to be placed between  $V_{\text{DDOSC}}/V_{\text{DDOSC3}}$  and  $V_{\text{SSOSC}}$ .

#### Figure 3-15 Oscillator Circuitries

Note: For crystal operation, it is strongly recommended to measure the negative resistance in the final target system (layout) to determine the optimum parameters for the oscillator operation. Please refer to the minimum and maximum values of the negative resistance specified by the crystal supplier.

### TC1161/TC1162

#### Preliminary

#### **Electrical Parameters**

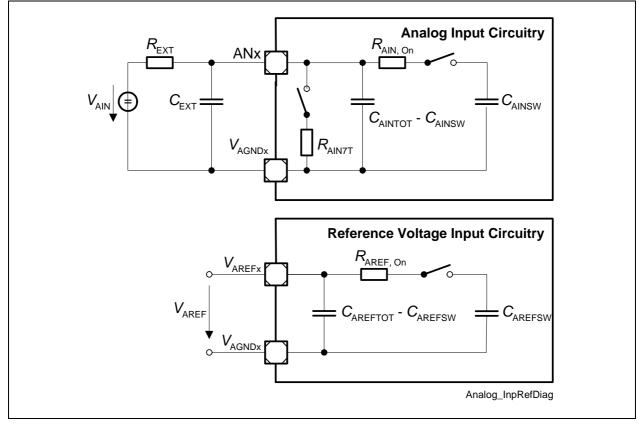

Figure 4-2 ADC0 Input Circuits

#### **Electrical Parameters**

#### 4.3.4 Power, Pad and Reset Timing

Figure 4-12 provides the characteristics of the power, pad and reset timing in the TC1161/TC1162.

| Parameter                                                                     | Symbol                |    | Limit                              | Unit                            |                  |

|-------------------------------------------------------------------------------|-----------------------|----|------------------------------------|---------------------------------|------------------|

|                                                                               |                       |    | Min.                               | Max.                            |                  |

| Min. $V_{\text{DDP}}$ voltage to ensure defined pad states <sup>1)</sup>      | V <sub>DDPPA</sub>    | CC | 0.6                                | -                               | V                |

| Oscillator start-up time <sup>2)</sup>                                        | t <sub>OSCS</sub>     | CC | _                                  | 10                              | ms               |

| Minimum PORST active time after power supplies are stable at operating levels | t <sub>POA</sub>      | SR | 10                                 | _                               | ms               |

| HDRST pulse width                                                             | t <sub>HD</sub>       | CC | 1024 clock cycles <sup>3)</sup>    | -                               | f <sub>sys</sub> |

| PORST rise time                                                               | t <sub>POR</sub>      | SR | -                                  | 50                              | ms               |

| Setup time to PORST rising edge <sup>4)</sup>                                 | t <sub>POS</sub>      | SR | 0                                  | -                               | ns               |

| Hold time from PORST rising edge <sup>4)</sup>                                | t <sub>POH</sub>      | SR | 100                                | -                               | ns               |

| Setup time to HDRST rising edge <sup>5)</sup>                                 | t <sub>HDS</sub>      | SR | 0                                  | -                               | ns               |

| Hold time from HDRST rising edge <sup>5)</sup>                                | t <sub>HDH</sub>      | SR | 100 +<br>(2 × 1/f <sub>SYS</sub> ) | -                               | ns               |

| Ports inactive after PORST reset active <sup>6)7)</sup>                       | t <sub>PIP</sub>      | CC | -                                  | 150                             | ns               |

| Ports inactive after HDRST reset active <sup>8)</sup>                         | t <sub>Pl</sub>       | CC | _                                  | 150 +<br>5 × 1/f <sub>SYS</sub> | ns               |

| Minimum $V_{\text{DDP}}$ <b>PORST</b> activation threshold. <sup>9)</sup>     | V <sub>PORST3.3</sub> | SR | -                                  | 2.9                             | V                |

| Minimum $V_{\text{DD}}$ <b>PORST</b> activation threshold. <sup>9)</sup>      | V <sub>PORST1.5</sub> | SR | -                                  | 1.32                            | V                |

| Power-on Reset Boot Time <sup>10)</sup>                                       | t <sub>BP</sub>       | CC | 2.15                               | 3.50                            | ms               |

| Hardware/Software Reset Boot Time at $f_{CPU}$ =66MHz <sup>11)</sup>          | t <sub>B</sub>        | CC | 560                                | 860                             | μS               |

1) This parameter is valid under assumption that  $\overrightarrow{\text{PORST}}$  signal is constantly at low-level during the power-up/power-down of the  $V_{\text{DDP}}$ .

<sup>2)</sup> This parameter is verified by device characterization. The external oscillator circuitry must be optimized by the customer and checked for negative resistance as recommended and specified by crystal suppliers.

<sup>3)</sup> Any HDRST activation is internally prolonged to 1024 FPI bus clock ( $f_{SYS}$ ) cycles.

#### **Electrical Parameters**

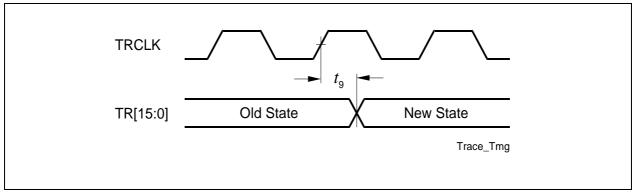

#### 4.3.6 Debug Trace Timing

$V_{SS} = 0 \text{ V}; V_{DDP} = 3.13 \text{ to } 3.47 \text{ V} \text{ (Class A)}; T_A = -40 \text{ }^{\circ}\text{C} \text{ to } +85 \text{ }^{\circ}\text{C}; C_L \text{ (TRCLK)} = 25 \text{ pF}; C_L \text{ (TR[15:0])} = 50 \text{ pF}$

#### Table 4-14 Debug Trace Timing Parameter<sup>1)</sup>

| Parameter                     | Sym            | bol | Lin  | Unit |    |

|-------------------------------|----------------|-----|------|------|----|

|                               |                |     | Min. | Max. |    |

| TR[15:0] new state from TRCLK | t <sub>9</sub> | CC  | -1   | 4    | ns |

1) Not subject to production test, verified by design/characterization.

Figure 4-14 Debug Trace Timing

#### TC1161/TC1162

#### Preliminary

#### **Electrical Parameters**

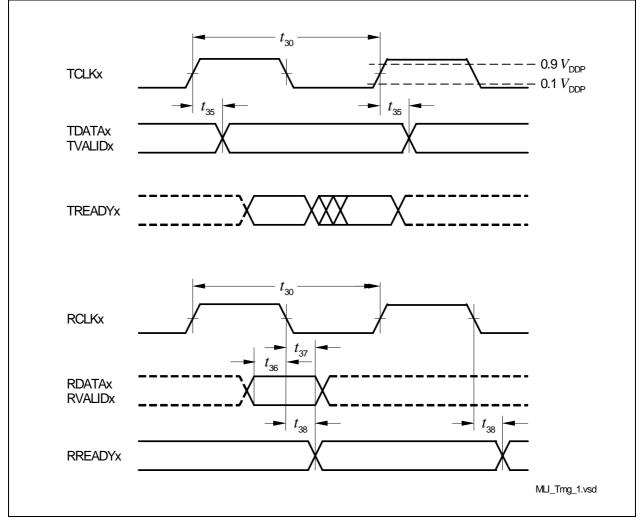

#### Figure 4-17 MLI Interface Timing

Note: The generation of RREADYx is in the input clock domain of the receiver. The reception of TREADYx is asynchronous to TCLKx.

#### Packaging and Reliability

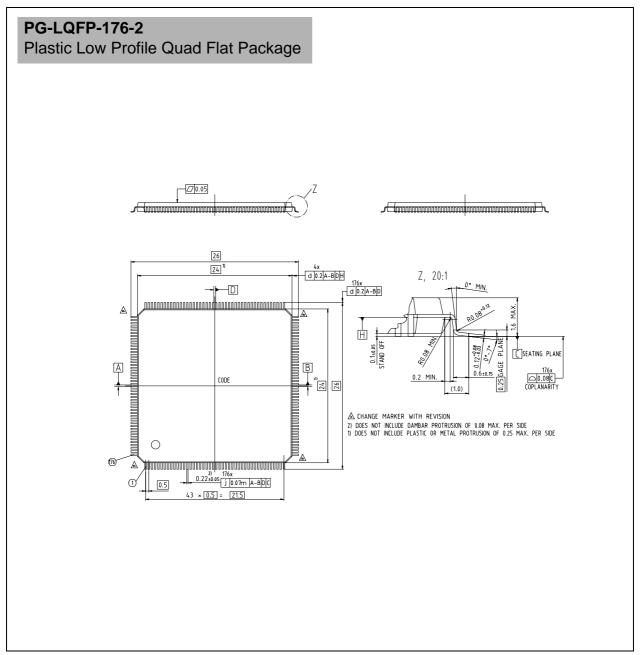

## 5 Packaging and Reliability

**Chapter 5** provides the information of the TC1161/TC1162 package and reliability section.

#### 5.1 Package Parameters

Table 5-1 provides the thermal characteristics of the package.

| Table 5-1Package Parameters (PG-LQFP-176-2) |

|---------------------------------------------|

|---------------------------------------------|

| Parameter                                          | Symbol            |    | Limit Values |      | Unit | Notes |  |

|----------------------------------------------------|-------------------|----|--------------|------|------|-------|--|

|                                                    |                   |    | Min.         | Max. |      |       |  |

| Thermal resistance junction case top <sup>1)</sup> | R <sub>TJCT</sub> | CC | -            | 5.4  | K/W  | -     |  |

| Thermal resistance junction leads                  | R <sub>TJL</sub>  | CC | -            | 21.5 | K/W  | -     |  |

1) The thermal resistances between the case top and the ambient (R<sub>TCAT</sub>), the leads and the ambient (R<sub>TLA</sub>) are to be combined with the thermal resistances between the junction and the case top (R<sub>TJCT</sub>), the junction and the leads (R<sub>TJL</sub>) given above, in order to calculate the total thermal resistance between the junction and the ambient (R<sub>TLA</sub>). The thermal resistances between the case top and the ambient (R<sub>TCAT</sub>), the leads and the ambient (R<sub>TLA</sub>) depend on the external system (PCB, case) characteristics, and are under user responsibility. The junction temperature can be calculated using the following equation: T<sub>J</sub>=T<sub>A</sub>+R<sub>TJA</sub> × P<sub>D</sub>, where the R<sub>TJA</sub> is the total thermal resistance between the junction and the ambient resistance R<sub>TJA</sub> can be obtained from the upper four partial thermal resistances.

#### Packaging and Reliability

#### 5.2 Package Outline

Figure 5-1 shows the package outlines of the TC1161/TC1162.

Figure 5-1 Package Outlines PG-LQFP-176-2

You can find all of our packages, sorts of packing and others in our Infineon Internet Page "Products": http://www.infineon.com/products.

SMD = Surface Mounted Device

Dimensions in mm