# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Discontinued at Digi-Key                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | 80C52                                                                     |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 48MHz                                                                     |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART, USB                           |

| Peripherals                | LED, POR, PWM, WDT                                                        |

| Number of I/O              | 18                                                                        |

| Program Memory Size        | 8KB (8K x 8)                                                              |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                               |

| Data Converters            | ·                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 32-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 32-VQFN (5x5)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at83c5134-pntul |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

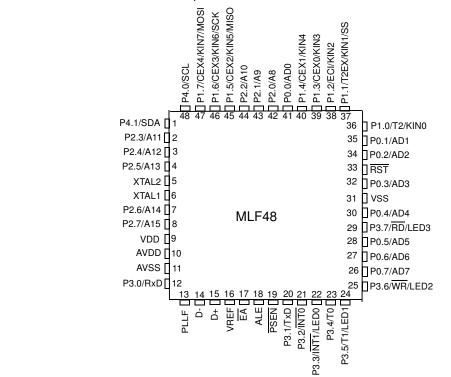

Figure 4-2. AT83C5134/35/36 48-pin MLF Pinout

Figure 4-3. AT83C5134/35/36 28-pin SO Pinout

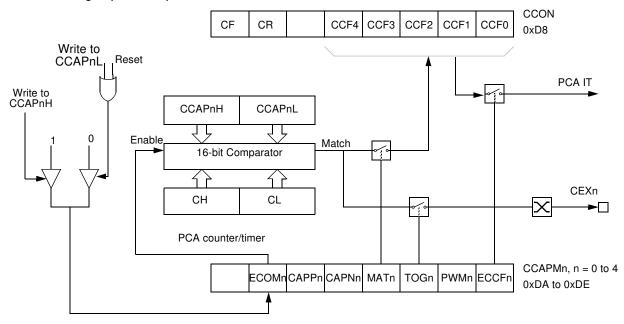

Figure 13-5. PCA High-speed Output Mode

Before enabling ECOM bit, CCAPnL and CCAPnH should be set with a non zero value, otherwise an unwanted match could happen.

Once ECOM set, writing CCAPnL will clear ECOM so that an unwanted match doesn't occur while modifying the compare value. Writing to CCAPnH will set ECOM. For this reason, user software should write CCAPnL first, and then CCAPnH. Of course, the ECOM bit can still be controlled by accessing to CCAPMn register.

#### 13.4 Pulse Width Modulator Mode

All of the PCA modules can be used as PWM outputs. Figure 13-6 shows the PWM function. The frequency of the output depends on the source for the PCA timer. All of the modules will have the same frequency of output because they all share the PCA timer. The duty cycle of each module is independently variable using the module's capture register CCAPLn. When the value of the PCA CL SFR is less than the value in the module's CCAPLn SFR the output will be low, when it is equal to or greater than the output will be high. When CL overflows from FF to 00, CCAPLn is reloaded with the value in CCAPHn. This allows updating the PWM without glitches. The PWM and ECOM bits in the module's CCAPMn register must be set to enable the PWM mode.

| Baud Rates | F <sub>osc</sub> = 16 | .384 MHz  | F <sub>OSC</sub> = 24 MHz |           |  |

|------------|-----------------------|-----------|---------------------------|-----------|--|

| Dudu hates | BRL                   | Error (%) | BRL                       | Error (%) |  |

| 115200     | 247                   | 1.23      | 243                       | 0.16      |  |

| 57600      | 238                   | 1.23      | 230                       | 0.16      |  |

| 38400      | 229                   | 1.23      | 217                       | 0.16      |  |

| 28800      | 220                   | 1.23      | 204                       | 0.16      |  |

| 19200      | 203                   | 0.63      | 178                       | 0.16      |  |

| 9600       | 149                   | 0.31      | 100                       | 0.16      |  |

| 4800       | 43                    | 1.23      | -                         | -         |  |

Example of computed value when X2 = 1, SMOD1 = 1, SPD = 1

Example of computed value when X2 = 0, SMOD1 = 0, SPD = 0

|            | F <sub>osc</sub> = 16 | .384 MHz | F <sub>osc</sub> = 24 MHz |           |  |

|------------|-----------------------|----------|---------------------------|-----------|--|

| Baud Rates | BRL Error (%)         |          | BRL                       | Error (%) |  |

| 4800       | 247                   | 1.23     | 243                       | 0.16      |  |

| 2400       | 238                   | 1.23     | 230                       | 0.16      |  |

| 1200       | 220                   | 1.23     | 202                       | 3.55      |  |

| 600        | 185                   | 0.16     | 152                       | 0.16      |  |

The baud rate generator can be used for mode 1 or 3 (refer to Figure 14-4.), but also for mode 0 for UART, thanks to the bit SRC located in BDRCON register (Table 14-4.)

#### 14.4 UART Registers

SADEN - Slave Address Mask Register for UART (B9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| - | - | - | - | - | - | - | - |

Reset Value = 0000 0000b

#### SADDR - Slave Address Register for UART (A9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| - | - | - | - | - | - | - | - |

Reset Value = 0000 0000b

SBUF - Serial Buffer Register for UART (99h)

Reset Value = XXXX XXXXb

BRL - Baud Rate Reload Register for the internal baud rate generator, UART (9Ah)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| - | - | - | - | - | - | - | - |

Reset Value = 0000 0000b

#### Table 14-2.T2CON Register

T2CON - Timer 2 Control Register (C8h)

| 7             | 6               | 5                                                            | 4                                                                                                                                                                                                                                          | 3                                                     | 2               | 1               | 0              |  |  |

|---------------|-----------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------|-----------------|----------------|--|--|

| TF2           | EXF2            | RCLK                                                         | TCLK                                                                                                                                                                                                                                       | EXEN2                                                 | TR2             | C/T2#           | CP/RL2#        |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                  |                                                                                                                                                                                                                                            |                                                       |                 |                 |                |  |  |

| 7             | TF2             |                                                              | ed by software.                                                                                                                                                                                                                            |                                                       | K = 0 and TCL   | K = 0.          |                |  |  |

| 6             | EXF2            | Set when a ca<br>= 1.<br>When set, cau<br>enabled.           | When set, causes the CPU to vector to Timer 2 interrupt routine when Timer 2 interrupt is enabled.<br>Must be cleared by software. EXF2 doesn't cause an interrupt in Up/down counter mode                                                 |                                                       |                 |                 |                |  |  |

| 5             | RCLK            | Cleared to use                                               |                                                                                                                                                                                                                                            | low as receive o<br>as receive clock                  |                 |                 |                |  |  |

| 4             | TCLK            | Cleared to use                                               |                                                                                                                                                                                                                                            | <b>T</b><br>low as transmit<br>as transmit cloc       |                 |                 |                |  |  |

| 3             | EXEN2           | Cleared to ign<br>Set to cause a                             |                                                                                                                                                                                                                                            | T2EX pin for Tir<br>bad when a neg                    |                 |                 | s detected, if |  |  |

| 2             | TR2             | Timer 2 Run<br>Cleared to tur<br>Set to turn on              | n off Timer 2.                                                                                                                                                                                                                             |                                                       |                 |                 |                |  |  |

| 1             | C/T2#           | Cleared for tin                                              | <b>Timer/Counter 2 select bit</b><br>Cleared for timer operation (input from internal clock system: F <sub>CLK PERIPH</sub> ).<br>Set for counter operation (input from T2 input pin, falling edge trigger). Must be 0 for clock out mode. |                                                       |                 |                 |                |  |  |

| 0             | CP/RL2#         | If RCLK = 1 or<br>2 overflow.<br>Cleared to Au<br>EXEN2 = 1. | to-reload on Ti                                                                                                                                                                                                                            | /RL2# is ignore<br>mer 2 overflows<br>ansitions on T2 | or negative tra | Insitions on T2 |                |  |  |

Reset Value = 0000 0000b Bit addressable

## Table 16-3.IPL0 Register

IPL0 - Interrupt Priority Register (B8h)

| 7             | 6               | 5                             | 4                                            | 3                | 2                | 1       | 0    |

|---------------|-----------------|-------------------------------|----------------------------------------------|------------------|------------------|---------|------|

| -             | PPCL            | PT2L                          | PSL                                          | PT1L             | PX1L             | PTOL    | PX0L |

| Bit<br>Number | Bit<br>Mnemonic | Description                   |                                              |                  |                  |         |      |

| 7             | -               | Reserved<br>The value rea     | ad from this bit                             | is indeterminate | e. Do not set th | is bit. |      |

| 6             | PPCL            |                               | ot Priority bit<br>H for priority le         | evel.            |                  |         |      |

| 5             | PT2L            |                               | flow interrup                                |                  |                  |         |      |

| 4             | PSL             | Serial port P<br>Refer to PSH | riority bit<br>for priority lev              | el.              |                  |         |      |

| 3             | PT1L            |                               | flow interrup<br>H for priority le           | •                |                  |         |      |

| 2             | PX1L            |                               | e <b>rrupt 1 Priori</b><br>H for priority le |                  |                  |         |      |

| 1             | PT0L            |                               | flow interrup<br>I for priority le           |                  |                  |         |      |

| 0             | PX0L            |                               | e <b>rrupt 0 Priori</b><br>H for priority le |                  |                  |         |      |

Reset Value = x000 0000b Bit addressable

AT83C5134/35/36

Table 16-6.IPL1 RegisterIPL1 - Interrupt Priority Register (B2h)

| 7             | 6               | 5                             | 4                                                                | 3                | 2                | 1       | 0     |  |

|---------------|-----------------|-------------------------------|------------------------------------------------------------------|------------------|------------------|---------|-------|--|

| -             | PUSBL           | -                             | -                                                                | -                | PSPIL            | PTWIL   | PKBDL |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                   |                                                                  |                  |                  |         |       |  |

| 7             | -               | Reserved<br>The value rea     | ad from this bit                                                 | is indeterminate | e. Do not set th | is bit. |       |  |

| 6             | PUSBL           | USB Interrup<br>Refer to PUS  | ot Priority bit<br>BH for priority                               | level.           |                  |         |       |  |

| 5             | -               | Reserved<br>The value rea     | ad from this bit                                                 | is indeterminate | e. Do not set th | is bit. |       |  |

| 4             | -               | Reserved<br>The value rea     | ad from this bit                                                 | is indeterminate | e. Do not set th | is bit. |       |  |

| 3             | -               | Reserved<br>The value rea     | ad from this bit                                                 | is indeterminate | e. Do not set th | is bit. |       |  |

| 2             | PSPIL           | SPI Interrupt<br>Refer to PSP | : <b>Priority bit</b><br>IH for priority le                      | evel.            |                  |         |       |  |

| 1             | PTWIL           |                               | TWI Interrupt Priority bit<br>Refer to PTWIH for priority level. |                  |                  |         |       |  |

| 0             | PKBL            |                               | <b>terrupt Priorit</b><br>H for priority le                      |                  |                  |         |       |  |

Reset Value = X0XX X000b Not bit addressable

#### 17.2.2 Power Reduction Mode

P1 inputs allow exit from idle and power down modes as detailed in section "Power-down Mode".

### 17.3 Registers

### Table 17-1. KBF Register

KBF - Keyboard Flag Register (9Eh)

| 7          | 6               | 5                              | 4                                                                                                                                                                                                                                                | 3                                                    | 2                 | 1    | 0       |  |

|------------|-----------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-------------------|------|---------|--|

| KBF7       | KBF6            | KBF5                           | KBF4                                                                                                                                                                                                                                             | KBF3                                                 | KBF2              | KBF1 | KBF0    |  |

| Bit Number | Bit<br>Mnemonic | Description                    |                                                                                                                                                                                                                                                  |                                                      |                   |      |         |  |

| 7          | KBF7            | Keyboard inte                  | are when the Perrupt request if                                                                                                                                                                                                                  | ort line 7 detect<br>the KBKBIE.7<br>eading KBF SF   | bit in KBIE regis |      | rates a |  |

| 6          | KBF6            | Keyboard inte                  | are when the Perrupt request if                                                                                                                                                                                                                  | ort line 6 detect<br>the KBIE.6 bit<br>eading KBF SF | n KBIE register   |      | rates a |  |

| 5          | KBF5            | Keyboard inte                  | are when the Perrupt request if                                                                                                                                                                                                                  | ort line 5 detect<br>the KBIE.5 bit<br>eading KBF SF | n KBIE register   |      | rates a |  |

| 4          | KBF4            | Keyboard inte                  | are when the Perrupt request if                                                                                                                                                                                                                  | ort line 4 detect<br>the KBIE.4 bit<br>eading KBF SF | n KBIE register   |      | rates a |  |

| 3          | KBF3            | Keyboard inte                  | are when the Perrupt request if                                                                                                                                                                                                                  | ort line 3 detect<br>the KBIE.3 bit<br>eading KBF SF | n KBIE register   | •    | rates a |  |

| 2          | KBF2            | Keyboard inte                  | are when the P                                                                                                                                                                                                                                   | ort line 2 detect<br>the KBIE.2 bit                  |                   | •    | rates a |  |

| 1          | KBF1            | Set by hardwa<br>Keyboard inte | <b>Keyboard line 1 flag</b><br>Set by hardware when the Port line 1 detects a programmed level. It generates a<br>Keyboard interrupt request if the KBIE.1 bit in KBIE register is set.<br>Cleared by hardware when reading KBF SFR by software. |                                                      |                   |      |         |  |

| 0          | KBF0            | Keyboard inte                  | are when the Perrupt request if                                                                                                                                                                                                                  | ort line 0 detect<br>the KBIE.0 bit<br>eading KBF SF | n KBIE register   |      | rates a |  |

Reset Value = 0000 0000b

# 18. Programmable LED

AT83C5134/35/36 have up to 4 programmable LED current sources, configured by the register LEDCON.

# Table 18-1. LEDCON Register

LEDCON (S:F1h) LED Control Register

| 7          | 6               | 5                                                                                                          | 4                                                                                                                                                           | 3                                                                                                                                                                  | 2          | 1    | 0 |  |  |

|------------|-----------------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|---|--|--|

| LE         | LED3            |                                                                                                            | ED2                                                                                                                                                         | LE                                                                                                                                                                 | D1         | LED0 |   |  |  |

| Bit Number | Bit<br>Mnemonic | Description                                                                                                |                                                                                                                                                             |                                                                                                                                                                    |            |      |   |  |  |

| 7:6        | LED3            | Port         LED3           0         0           1         1           1         1                        | Standard C51<br>2 mA current s<br>4 mA current s                                                                                                            | Configuration<br>Standard C51 Port<br>2 mA current source when P3.7 is low<br>4 mA current source when P3.7 is low<br>10 mA current source when P3.7 is low        |            |      |   |  |  |

| 5:4        | LED2            | Port         /LED2           0         0           0         1           1         0           1         1 | Standard C51<br>2 mA current s<br>4 mA current s                                                                                                            | <u>Configuration</u><br>Standard C51 Port<br>2 mA current source when P3.6 is low<br>4 mA current source when P3.6 is low<br>10 mA current source when P3.6 is low |            |      |   |  |  |

| 3:2        | LED1            | Port/LED1           0         0           0         1           1         0           1         1          | Configuration<br>Standard C51 Port<br>2 mA current source when P3.5 is low<br>4 mA current source when P3.5 is low<br>10 mA current source when P3.5 is low |                                                                                                                                                                    |            |      |   |  |  |

| 1:0        | LED0            | Port/LED0           0         0           1         0           1         1                                | 4 mA current                                                                                                                                                |                                                                                                                                                                    | 3.3 is low |      |   |  |  |

Reset Value = 00h

#### **19.3 Functional Description**

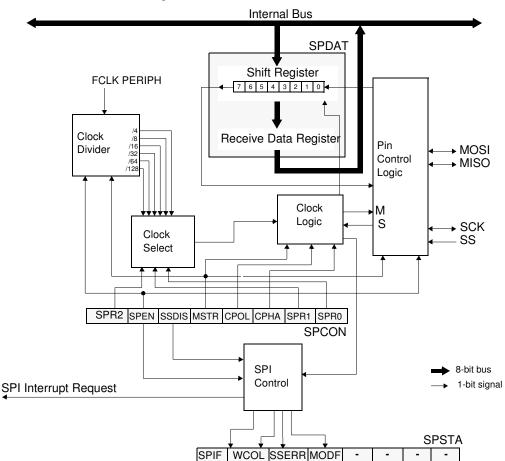

Figure 19-2 shows a detailed structure of the SPI module.

Figure 19-2. SPI Module Block Diagram

#### 19.3.1 Operating Modes

The Serial Peripheral Interface can be configured as one of the two modes: Master mode or Slave mode. The configuration and initialization of the SPI module is made through one register:

• The Serial Peripheral CONtrol register (SPCON)

Once the SPI is configured, the data exchange is made using:

- SPCON

- The Serial Peripheral STAtus register (SPSTA)

- The Serial Peripheral DATa register (SPDAT)

During an SPI transmission, data is simultaneously transmitted (shifted out serially) and received (shifted in serially). A serial clock line (SCK) synchronizes shifting and sampling on the two serial data lines (MOSI and MISO). A Slave Select line ( $\overline{SS}$ ) allows individual selection of a Slave SPI device; Slave devices that are not selected do not interfere with SPI bus activities.

When the Master device transmits data to the Slave device via the MOSI line, the Slave device responds by sending data to the Master device via the MISO line. This implies full-duplex transmission with both data out and data in synchronized with the same clock (Figure 19-3).

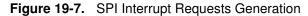

Mode Fault flag, MODF: This bit becomes set to indicate that the level on the SS is inconsistent with the mode of the SPI. MODF with SSDIS reset, generates receiver/error CPU interrupt requests.

Figure 19-7 gives a logical view of the above statements.

#### 19.3.5 Registers

There are three registers in the module that provide control, status and data storage functions. These registers are describes in the following paragraphs.

#### 19.3.5.1 Serial Peripheral Control Register (SPCON)

- The Serial Peripheral Control Register does the following:

- Selects one of the Master clock rates

- Configure the SPI module as Master or Slave

- Selects serial clock polarity and phase

- Enables the SPI module

- Frees the SS pin for a general-purpose

Table 19-3 describes this register and explains the use of each bit.

#### Table 19-3. SPCON Register

| 7             | 6            | 5                                                                                                                           | 4                                                                                                                                                                                                                      | 3    | 2    | 1    | 0    |  |

|---------------|--------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|--|

| SPR2          | SPEN         | SSDIS                                                                                                                       | MSTR                                                                                                                                                                                                                   | CPOL | СРНА | SPR1 | SPR0 |  |

| Bit<br>Number | Bit Mnemonic | Description                                                                                                                 | I                                                                                                                                                                                                                      |      |      |      |      |  |

| 7             | SPR2         | -                                                                                                                           | Serial Peripheral Rate 2<br>Bit with SPR1 and SPR0 define the clock rate.                                                                                                                                              |      |      |      |      |  |

| 6             | SPEN         | Cleared to c                                                                                                                | heral Enable<br>lisable the SPI<br>e the SPI inter                                                                                                                                                                     |      |      |      |      |  |

| 5             | SSDIS        | Set to disab                                                                                                                | $\overline{SS}$ Disable<br>Cleared to enable $\overline{SS}$ in both Master and Slave modes.<br>Set to disable $\overline{SS}$ in both Master and Slave modes. In Slave mode, this bit has no<br>effect if CPHA = "0". |      |      |      |      |  |

| 5             | MSTR         | Cleared to c                                                                                                                | <b>heral Master</b><br>onfigure the SI<br>gure the SPI as                                                                                                                                                              |      |      |      |      |  |

| 4             | CPOL         | <b>Clock Polarity</b><br>Cleared to have the SCK set to "0" in idle state.<br>Set to have the SCK set to "1" in idle state. |                                                                                                                                                                                                                        |      |      |      |      |  |

# 20. Two Wire Interface (TWI)

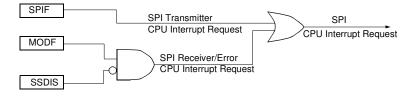

This section describes the 2-wire interface. The 2-wire bus is a bi-directional 2-wire serial communication standard. It is designed primarily for simple but efficient integrated circuit (IC) control. The system is comprised of two lines, SCL (Serial Clock) and SDA (Serial Data) that carry information between the ICs connected to them. The serial data transfer is limited to 100 Kbit/s in standard mode. Various communication configuration can be designed using this bus. Figure 20-1 shows a typical 2-wire bus configuration. All the devices connected to the bus can be master and slave.

Figure 20-1. 2-wire Bus Configuration

|                |                                         | Appli           | cation soft | ware respo | nse |      |                                                                                                |

|----------------|-----------------------------------------|-----------------|-------------|------------|-----|------|------------------------------------------------------------------------------------------------|

| Status<br>Code | Status of the Two-<br>wire Bus and Two- |                 |             | To SSC     | CON |      |                                                                                                |

| SSSTA          | wire Hardware                           | To/From SSDAT   | SSSTA       | SSSTO      | SSI | SSAA | Next Action Taken by Two-wire Hardware                                                         |

| 08h            | A START condition has been transmitted  | Write SLA+R     | x           | 0          | 0   | х    | SLA+R will be transmitted.                                                                     |

|                | A repeated START                        | Write SLA+R     | х           | 0          | 0   | х    | SLA+R will be transmitted.                                                                     |

| 10h            | condition has been<br>transmitted       | Write SLA+W     | x           | 0          | 0   | х    | SLA+W will be transmitted.<br>Logic will switch to master transmitter mode.                    |

| 38h            | Arbitration lost in<br>SLA+R or NOT ACK | No SSDAT action | 0           | 0          | 0   | х    | Two-wire bus will be released and not addressed slave mode will be entered.                    |

| 3011           | bit                                     | No SSDAT action | 1           | 0          | 0   | х    | A START condition will be transmitted when the bus becomes free.                               |

| 40h            | SLA+R has been<br>transmitted; ACK has  | No SSDAT action | 0           | 0          | 0   | 0    | Data byte will be received and NOT ACK will be returned.                                       |

|                | been received                           | No SSDAT action | 0           | 0          | 0   | 1    | Data byte will be received and ACK will be returned.                                           |

|                | SLA+R has been                          | No SSDAT action | 1           | 0          | 0   | х    | Repeated START will be transmitted.<br>STOP condition will be transmitted and SSSTO flag       |

| 48h            | transmitted; NOT ACK                    | No SSDAT action | 0           | 1          | 0   | х    | will be reset.                                                                                 |

|                | has been received                       | No SSDAT action | 1           | 1          | 0   | х    | STOP condition followed by a START condition will be transmitted and SSSTO flag will be reset. |

| 50h            | Data byte has been<br>received; ACK has | Read data byte  | 0           | 0          | 0   | 0    | Data byte will be received and NOT ACK will be returned.                                       |

|                | been returned                           | Read data byte  | 0           | 0          | 0   | 1    | Data byte will be received and ACK will be returned.                                           |

|                |                                         | Read data byte  | 1           | 0          | 0   | х    | Repeated START will be transmitted.                                                            |

| 58h            | Data byte has been received; NOT ACK    | Read data byte  | 0           | 1          | 0   | Х    | STOP condition will be transmitted and SSSTO flag will be reset.                               |

|                | has been returned                       | Read data byte  | 1           | 1          | 0   | х    | STOP condition followed by a START condition will be transmitted and SSSTO flag will be reset. |

Table 20-6. Status in Master Receiver Mode

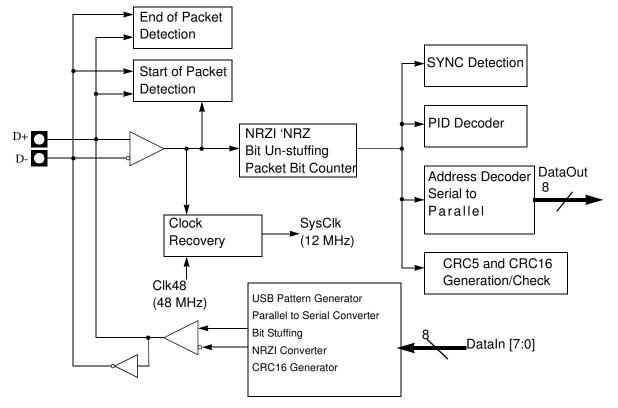

- · Address checking.

- Clock generation (via DPLL).

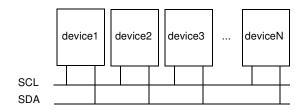

#### 21.1.2 Function Interface Unit (FIU)

The Function Interface Unit provides the interface between the AT89C5131 and the SIE. It manages transactions at the packet level with minimal intervention from the device firmware, which reads and writes the endpoint FIFOs.

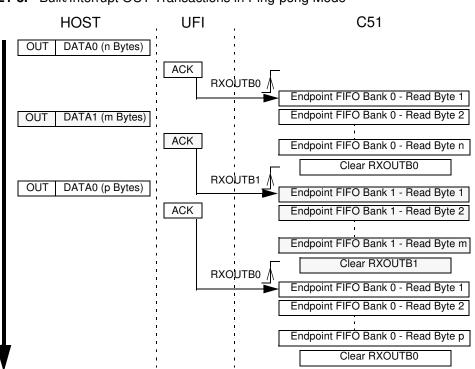

#### 21.4.2 Bulk/Interrupt OUT Transactions in Ping-pong Mode

Figure 21-8. Bulk/Interrupt OUT Transactions in Ping-pong Mode

An endpoint will be first enabled and configured before being able to receive Bulk or Interrupt packets.

When a valid OUT packet is received on the endpoint bank 0, the RXOUTB0 bit is set by the USB controller. This triggers an interrupt if enabled. The firmware has to select the corresponding endpoint, store the number of data bytes by reading the UBYCTLX and UBYCTHX registers. If the received packet is a ZLP (Zero Length Packet), the UBYCTLX and UBYCTHX register values are equal to 0 and no data has to be read.

When all the endpoint FIFO bytes have been read, the firmware will clear the RXOUB0 bit to allow the USB controller to accept the next OUT packet on the endpoint bank 0. This action switches the endpoint bank 0 and 1. Until the RXOUTB0 bit has been cleared by the firmware, the USB controller will answer a NAK handshake for each OUT requests on the bank 0 endpoint FIFO.

When a new valid OUT packet is received on the endpoint bank 1, the RXOUTB1 bit is set by the USB controller. This triggers an interrupt if enabled. The firmware empties the bank 1 endpoint FIFO before clearing the RXOUTB1 bit. Until the RXOUTB1 bit has been cleared by the firmware, the USB controller will answer a NAK handshake for each OUT requests on the bank 1 endpoint FIFO.

The RXOUTB0 and RXOUTB1 bits are alternatively set by the USB controller at each new valid packet receipt.

The firmware has to clear one of these two bits after having read all the data FIFO to allow a new valid packet to be stored in the corresponding bank.

#### Table 21-2. Priority Levels

| IPHUSB | IPLUSB | USB Priority Level |

|--------|--------|--------------------|

| 0      | 0      | 0 Lowest           |

| 0      | 1      | 1                  |

| 1      | 0      | 2                  |

| 1      | 1      | 3 Highest          |

#### 21.10.2 USB Interrupt Control System

As shown in Figure 21-16, many events can produce a USB interrupt:

- TXCMPL: Transmitted In Data (see Table 21-9 on page 125). This bit is set by hardware when the Host accept a In packet.

- RXOUTB0: Received Out Data Bank 0 (see Table 21-9 on page 125). This bit is set by hardware when an Out packet is accepted by the endpoint and stored in bank 0.

- RXOUTB1: Received Out Data Bank 1 (only for Ping-pong endpoints) (see Table 21-9 on page 125). This bit is set by hardware when an Out packet is accepted by the endpoint and stored in bank 1.

- RXSETUP: Received Setup (see Table 21-9 on page 125). This bit is set by hardware when an SETUP packet is accepted by the endpoint.

- STLCRC: STALLED (only for Control, Bulk and Interrupt endpoints) (see Table 21-9 on page 125). This bit is set by hardware when a STALL handshake has been sent as requested by STALLRQ, and is reset by hardware when a SETUP packet is received.

- SOFINT: Start of Frame Interrupt (See "USBIEN Register USBIEN (S:BEh) USB Global Interrupt Enable Register" on page 122.). This bit is set by hardware when a USB Start of Frame packet has been received.

- WUPCPU: Wake-Up CPU Interrupt (See "USBIEN Register USBIEN (S:BEh) USB Global Interrupt Enable Register" on page 122.). This bit is set by hardware when a USB resume is detected on the USB bus, after a SUSPEND state.

- SPINT: Suspend Interrupt (See "USBIEN Register USBIEN (S:BEh) USB Global Interrupt Enable Register" on page 122.). This bit is set by hardware when a USB suspend is detected on the USB bus.

#### Table 21-10. UEPDATX Register

UEPDATX (S:CFh)

USB FIFO Data Endpoint X (X = EPNUM set in UEPNUM Register UEPNUM (S:C7h) USB Endpoint Number)

| 7          | 6            | 5                                    | 4     | 3                     | 2                    | 1                 | 0       |

|------------|--------------|--------------------------------------|-------|-----------------------|----------------------|-------------------|---------|

| FDAT7      | FDAT6        | FDAT5                                | FDAT4 | FDAT3                 | FDAT2                | FDAT1             | FDAT0   |

| Bit Number | Bit Mnemonic | Description                          |       |                       |                      |                   |         |

| 7 - 0      | FDAT[7:0]    | Endpoint X FIFO<br>Data byte to be w |       | ta byte to be read fr | om the FIFO, for the | e Endpoint X (see | EPNUM). |

Reset Value = XXh

#### Table 21-11. UBYCTLX Register

UBYCTLX (S:E2h)

USB Byte Count Low Register X (X = EPNUM set in UEPNUM Register UEPNUM (S:C7h) USB Endpoint Number)

| 7          | 6            | 5                               | 4               | 3                                         | 2                                                                   | 1                  | 0               |

|------------|--------------|---------------------------------|-----------------|-------------------------------------------|---------------------------------------------------------------------|--------------------|-----------------|

| BYCT7      | BYCT6        | BYCT5                           | BYCT4           | ВҮСТЗ                                     | BYCT2                                                               | BYCT1              | ВҮСТО           |

| Bit Number | Bit Mnemonic | Description                     |                 |                                           |                                                                     |                    |                 |

| 7 - 0      | BYCT[7:0]    | UBYCTHX Regist<br>UEPNUM (S:C7h | er UBYCTHX (S:E | 3h) USB Byte Coun<br>Imber) (see Figure 2 | ta packet. The most<br>th High Register X (X<br>21-11 on page 126). | K = EPNUM set in U | JEPNUM Register |

Reset Value = 00h

## Table 21-12. UBYCTHX Register

#### UBYCTHX (S:E3h)

USB Byte Count High Register X (X = EPNUM set in UEPNUM Register UEPNUM (S:C7h) USB Endpoint Number)

| 7          | 6            | 5                         | 4                                     | 3                  | 2                                                                | 1              | 0     |

|------------|--------------|---------------------------|---------------------------------------|--------------------|------------------------------------------------------------------|----------------|-------|

| -          | -            | -                         | -                                     | -                  | -                                                                | BYCT9          | BYCT8 |

| Bit Number | Bit Mnemonic | Description               |                                       |                    |                                                                  |                |       |

| 7-2        | -            | Reserved<br>The value rea | d from these bits is                  | always 0. Do not s | et these bits.                                                   |                |       |

| 2-0        | BYCT[10:8]   | UBYCTLX Re                | nt Byte of the byte gister UBYCTLX (S | S:E2h) USB Byte Co | data packet. The L<br>ount Low Register ><br>(see Figure 21-11 c | (X = EPNUM set |       |

Reset Value = 00h

# 126 AT83C5134/35/36

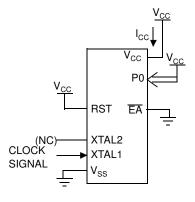

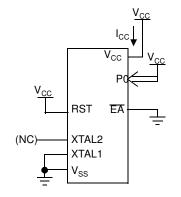

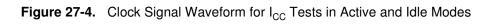

Figure 27-2.  $I_{CC}$  Test Condition, Idle Mode

All other pins are disconnected.

All other pins are disconnected.

#### 27.2.1 LED's

Table 27-1.

LED Outputs DC Parameters

| S | Symbol          | Parameter                                   | Min | Тур | Max | Unit | Test Conditions     |

|---|-----------------|---------------------------------------------|-----|-----|-----|------|---------------------|

|   |                 |                                             | 1   | 2   | 4   | mA   | 2 mA configuration  |

|   | I <sub>OL</sub> | Output Low Current, P3.6 and P3.7 LED modes | 2   | 4   | 8   | mA   | 4 mA configuration  |

|   |                 |                                             | 5   | 10  | 20  | mA   | 10 mA configuration |

Note: 1. (Ta = -20°C to +50°C, V<sub>CC</sub> - V<sub>OL</sub> = 2 V  $\pm$  20%)

# 28. Ordering Information

Table Possible Order Entries

| Part Number         | Memory Size                     | Supply Voltage | Temperature Range  | Package   | Packing     |

|---------------------|---------------------------------|----------------|--------------------|-----------|-------------|

| AT83C5134xxx-PNTUL  | 8KB                             | 2.7 to 3.6V    | Industrial & Green | QFN32     | Tray        |

|                     |                                 |                |                    |           |             |

| AT83C5135xxx-PNTUL  | 16KB                            | 2.7 to 3.6V    | Industrial & Green | QFN32     | Tray        |

|                     |                                 |                |                    |           |             |

| AT83C5136xxx-PNTUL  | 32KB                            | 2.7 to 3.6V    | Industrial & Green | QFN32     | Tray        |

| AT83C5136xxx-PLTUL  | 32KB                            | 2.7 to 3.6V    | Industrial & Green | QFN/MLF48 | Tray        |

| AT83C5136xxx-TISUL  | 32KB                            | 2.7 to 3.6V    | Industrial & Green | SO28      | Stick       |

| AT83C5136-RDTUL     | 32                              | 2.7 to 3.6V    | Industrial & Green | VQFP64    | Tray        |

| AT83C5136xxx-DDW    | 32KB                            | 2.7 to 3.6V    | Industrial & Green | Die       | Inked Wafer |

|                     |                                 |                |                    |           |             |

| AT83EC5136xxx-PNTUL | 32KB with 512-byte of<br>EEPROM | 2.7 to 3.6V    | Industrial & Green | QFN/MLF48 | Tray        |

| AT83EI5136xxx-PNTUL | 32KB with 32-kbyte of<br>EEPROM | 2.7 to 3.6V    | Industrial & Green | QFN/MLF48 | Tray        |

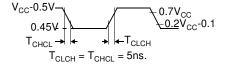

### 29.4 QFN32

# AT83C5134/35/36

|          | 13.5                                                                                                                 | PCA Watchdog Timer                                                                                                                                                                                       | 48                                                                                                     |

|----------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| 14       | Serial I                                                                                                             | //O Port                                                                                                                                                                                                 | 49                                                                                                     |

|          | 14.1                                                                                                                 | Framing Error Detection                                                                                                                                                                                  | 49                                                                                                     |

|          | 14.2                                                                                                                 | Automatic Address Recognition                                                                                                                                                                            | 50                                                                                                     |

|          | 14.3                                                                                                                 | Baud Rate Selection for UART for Mode 1 and 3                                                                                                                                                            | 52                                                                                                     |

|          | 14.4                                                                                                                 | UART Registers                                                                                                                                                                                           | 55                                                                                                     |

| 15       | Dual D                                                                                                               | ata Pointer Register                                                                                                                                                                                     | 59                                                                                                     |

| 16       | Interru                                                                                                              | pt System                                                                                                                                                                                                | 61                                                                                                     |

|          | 16.1                                                                                                                 | Overview                                                                                                                                                                                                 | 61                                                                                                     |

|          | 16.2                                                                                                                 | Registers                                                                                                                                                                                                | 62                                                                                                     |

|          | 16.3                                                                                                                 | Interrupt Sources and Vector Addresses                                                                                                                                                                   | 69                                                                                                     |

| 17       | Keyboa                                                                                                               | ard Interface                                                                                                                                                                                            | 70                                                                                                     |

|          | 17.1                                                                                                                 | Introduction                                                                                                                                                                                             | 70                                                                                                     |

|          | 17.2                                                                                                                 | Description                                                                                                                                                                                              | 70                                                                                                     |

|          | 17.3                                                                                                                 | Registers                                                                                                                                                                                                | 71                                                                                                     |

| 18       | Progra                                                                                                               | mmable LED                                                                                                                                                                                               | 74                                                                                                     |

|          |                                                                                                                      |                                                                                                                                                                                                          |                                                                                                        |

| 19       | Serial                                                                                                               | Peripheral Interface (SPI)                                                                                                                                                                               | 75                                                                                                     |

| 19       | <b>Serial</b><br>19.1                                                                                                | Peripheral Interface (SPI)<br>Features                                                                                                                                                                   |                                                                                                        |

| 19       |                                                                                                                      |                                                                                                                                                                                                          | 75                                                                                                     |

| 19       | 19.1                                                                                                                 | Features                                                                                                                                                                                                 | 75<br>75                                                                                               |

| 19<br>20 | 19.1<br>19.2<br>19.3                                                                                                 | Features<br>Signal Description                                                                                                                                                                           | 75<br>75<br>77                                                                                         |

| -        | 19.1<br>19.2<br>19.3                                                                                                 | Features<br>Signal Description<br>Functional Description                                                                                                                                                 | 75<br>75<br>77<br>. <b> 84</b>                                                                         |

| -        | 19.1<br>19.2<br>19.3<br><b>Two W</b>                                                                                 | Features<br>Signal Description<br>Functional Description                                                                                                                                                 | 75<br>75<br>77<br>. <b> 84</b>                                                                         |

| -        | 19.1<br>19.2<br>19.3<br><b>Two W</b><br>20.1                                                                         | Features<br>Signal Description<br>Functional Description<br><i>Tire Interface (TWI)</i><br>Description                                                                                                   | 75<br>75<br>77<br><b>84</b><br>86<br>89                                                                |

| -        | 19.1<br>19.2<br>19.3<br><b>Two W</b><br>20.1<br>20.2<br>20.3                                                         | Features<br>Signal Description<br>Functional Description<br><b><i>Tire Interface (TWI)</i></b><br>Description<br>Notes                                                                                   | 75<br>75<br>77<br>84<br>86<br>89<br>99                                                                 |

| 20       | 19.1<br>19.2<br>19.3<br><b>Two W</b><br>20.1<br>20.2<br>20.3                                                         | Features                                                                                                                                                                                                 | 75<br>75<br>77<br>84<br>86<br>89<br>99<br>99                                                           |

| 20       | 19.1<br>19.2<br>19.3<br><b>Two W</b><br>20.1<br>20.2<br>20.3<br><b>USB C</b>                                         | Features<br>Signal Description<br>Functional Description<br><i>Vire Interface (TWI)</i><br>Description<br>Notes<br>Registers<br><i>ontroller</i>                                                         | 75<br>75<br>77<br>84<br>86<br>89<br>99<br>99<br>. 101<br>101                                           |

| 20       | 19.1<br>19.2<br>19.3<br><b>Two W</b><br>20.1<br>20.2<br>20.3<br><b>USB C</b><br>21.1                                 | Features<br>Signal Description<br>Functional Description<br><b>Vire Interface (TWI)</b><br>Description<br>Notes<br>Registers<br><b>ontroller</b><br>Description<br>Configuration<br>Read/Write Data FIFO | 75<br>75<br>77<br>84<br>86<br>89<br>99<br>99<br>101<br>103<br>105                                      |

| 20       | 19.1<br>19.2<br>19.3<br><b>Two W</b><br>20.1<br>20.2<br>20.3<br><b>USB C</b><br>21.1<br>21.2                         | Features                                                                                                                                                                                                 | 75<br>75<br>77<br>84<br>86<br>89<br>99<br>99<br>101<br>103<br>105                                      |

| 20       | 19.1<br>19.2<br>19.3<br><b>Two W</b><br>20.1<br>20.2<br>20.3<br><b>USB C</b><br>21.1<br>21.2<br>21.3                 | Features<br>Signal Description<br>Functional Description<br><b>Vire Interface (TWI)</b><br>Description<br>Notes<br>Registers<br><b>ontroller</b><br>Description<br>Configuration<br>Read/Write Data FIFO | 75<br>75<br>77<br>84<br>86<br>89<br>99<br>99<br>101<br>103<br>105<br>106                               |

| 20       | 19.1<br>19.2<br>19.3<br><b>Two W</b><br>20.1<br>20.2<br>20.3<br><b>USB C</b><br>21.1<br>21.2<br>21.3<br>21.4         | Features                                                                                                                                                                                                 | 75<br>75<br>77<br>84<br>86<br>89<br>99<br>101<br>103<br>105<br>106<br>111                              |

| 20       | 19.1<br>19.2<br>19.3<br><b>Two W</b><br>20.1<br>20.2<br>20.3<br><b>USB C</b><br>21.1<br>21.2<br>21.3<br>21.4<br>21.5 | Features                                                                                                                                                                                                 | 75<br>75<br>77<br>84<br>86<br>89<br>99<br>99<br>. 101<br>101<br>103<br>105<br>106<br>111<br>112<br>113 |