#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusDiscontinued at Digi-KeyCore Processor8052Core Size8-BitSpeed48ME2ConnectivityEBI/EMI, IPC, SPI, UART/USART, USBPeripheralsLED, POR, PWM, WDTNumber of I/O34Program Memory Size32KB (32K × 8)FROM SizeIX-8RAM Size1K × 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VDisciltor Type-Oscillator Type-Oscillator Type-Autoring Type-Autoring Type-Disciltor Type-Oscillator Type-Supplier Device Package-Supplier Device Package-Supplier Device Package-Supplier Device Package-Prochase URLMitse//www.exfl.com/product-detail/microchip-technology/at83c513c-pitul |                            |                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------------------------------------------------------|

| Core Size8-BitSpeed48MHzConnectivityEBI/EMI, I²C, SPI, UART/USART, USBPeripheralsLED, POR, PWM, WDTNumber of I/O34Program Memory Size32KB (32K x 8)Program Memory TypeFLASHEEPROM Size32K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Operating Temperature-40°C ~ 85°C (TA)Mounting Type-Package / Case-Supplier Device Package-                                                                                                                                                                                                                            | Product Status             | Discontinued at Digi-Key                                                  |

| Speed48MHzConnectivityEB/EMI, I²C, SPI, UART/USART, USBPeripheralsLED, POR, PWM, WDTNumber of I/O34Program Memory Size32KB (32K x 8)Program Memory TypeFLASHEEPROM Size32K x 8RAM Size1K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting Type-Package / Case-Supplier Device Package-                                                                                                                                                                                                      | Core Processor             | 80C52                                                                     |

| ConnectivityEBI/EMI, I²C, SPI, UART/USART, USBPeripheralsLED, POR, PWM, WDTNumber of I/O34Program Memory Size32KB (32K x 8)Program Memory TypeFLASHEEPROM Size32K x 8RAM Size1K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting Type-Package / Case-Supplier Device Package-                                                                                                                                                                                                               | Core Size                  | 8-Bit                                                                     |

| PeripheralsLED, POR, PWM, WDTNumber of I/O34Program Memory Size32KB (32K x 8)Program Memory TypeFLASHEEPROM Size32K x 8RAM Size1K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting Type-Package / Case-Supplier Device Package-                                                                                                                                                                                                                                                             | Speed                      | 48MHz                                                                     |

| Number of I/O34Program Memory Size32KB (32K x 8)Program Memory TypeFLASHEEPROM Size32K x 8RAM Size1K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting Type-Package / Case-Supplier Device Package-                                                                                                                                                                                                                                                                                          | Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART, USB                           |

| Program Memory Size32KB (32K × 8)Program Memory TypeFLASHEEPROM Size32K × 8RAM Size1K × 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting Type-Package / Case-Supplier Device Package-                                                                                                                                                                                                                                                                                                         | Peripherals                | LED, POR, PWM, WDT                                                        |

| Program Memory TypeFLASHEEPROM Size32K x 8RAM Size1K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting Type-Package / Case-Supplier Device Package-                                                                                                                                                                                                                                                                                                                                          | Number of I/O              | 34                                                                        |

| EEPROM Size32K x 8RAM Size1K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting Type-Package / Case-Supplier Device Package-                                                                                                                                                                                                                                                                                                                                                                  | Program Memory Size        | 32KB (32K x 8)                                                            |

| RAM SizeIK x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting Type-Package / Case-Supplier Device Package-Https://www.e.vfl.com/product.detail/microchin.technology/at82c5126.nltul                                                                                                                                                                                                                                                                                                           | Program Memory Type        | FLASH                                                                     |

| Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting Type-Package / Case-Supplier Device Package-Http://www.e.vfl.com/product datail/microchin technology/at82c5126 altul                                                                                                                                                                                                                                                                                                                          | EEPROM Size                | 32K x 8                                                                   |

| Data Converters       -         Oscillator Type       Internal         Operating Temperature       -40°C ~ 85°C (TA)         Mounting Type       -         Package / Case       -         Supplier Device Package       -                                                                                                                                                                                                                                                                                                                                                | RAM Size                   | 1K x 8                                                                    |

| Oscillator Type     Internal       Operating Temperature     -40°C ~ 85°C (TA)       Mounting Type     -       Package / Case     -       Supplier Device Package     -                                                                                                                                                                                                                                                                                                                                                                                                  | Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                               |

| Operating Temperature     -40°C ~ 85°C (TA)       Mounting Type     -       Package / Case     -       Supplier Device Package     -                                                                                                                                                                                                                                                                                                                                                                                                                                     | Data Converters            | -                                                                         |

| Mounting Type     -       Package / Case     -       Supplier Device Package     -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Oscillator Type            | Internal                                                                  |

| Package / Case     -       Supplier Device Package     -       https://www.e.vfl.com/product.detail/microchip.technology/at83c5136.pltul                                                                                                                                                                                                                                                                                                                                                                                                                                 | Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Supplier Device Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Mounting Type              | -                                                                         |

| https://www.o.yfl.com/product.dotail/microship.tochpology/at92c5126.pltul                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Package / Case             | -                                                                         |

| Purchase URL https://www.e-xfl.com/product-detail/microchip-technology/at83c5136-pltul                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Supplier Device Package    | -                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at83c5136-pltul |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

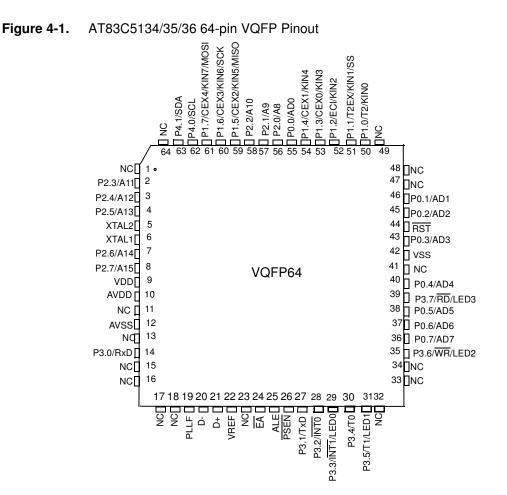

# 4. Pinout Description

4.1 Pinout

| Table 4-3. | Serial I/O Signal Description |

|------------|-------------------------------|

|------------|-------------------------------|

| Signal<br>Name | Туре | Description                                                                        | Alternate<br>Function |

|----------------|------|------------------------------------------------------------------------------------|-----------------------|

| RxD            | I    | Serial Input<br>The serial input for Extended UART. This I/O is 5 Volt Tolerant.   | P3.0                  |

| TxD            | 0    | Serial Output<br>The serial output for Extended UART. This I/O is 5 Volt Tolerant. | P3.1                  |

# **Table 4-4.**Timer 0, Timer 1 and Timer 2 Signal Description

| Signal<br>Name | Туре   | Description                                                                                                                                                                                                                                                                                                                                           | Alternate<br>Function |

|----------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| INTO           | I      | Timer 0 Gate Input         INT0 serves as external run control for timer 0, when selected by GATE0 bit in TCON register.         External Interrupt 0         INT0 input set IE0 in the TCON register. If bit IT0 in this register is set, bits IE0 are set by a falling edge on INT0. If bit IT0 is cleared, bits IE0 is set by a low level on INT0. | P3.2                  |

| INT1           | I      | Timer 1 Gate Input         INT1 serves as external run control for Timer 1, when selected by GATE1 bit in TCON register.         External Interrupt 1         INT1 input set IE1 in the TCON register. If bit IT1 in this register is set, bits IE1 are set by a falling edge on INT1. If bit IT1 is cleared, bits IE1 is set by a low level on INT1. | P3.3                  |

| то             | I      | <b>Timer Counter 0 External Clock Input</b><br>When Timer 0 operates as a counter, a falling edge on the T0 pin increments the count.                                                                                                                                                                                                                 | P3.4                  |

| T1             | I      | <b>Timer/Counter 1 External Clock Input</b><br>When Timer 1 operates as a counter, a falling edge on the T1 pin increments the count.                                                                                                                                                                                                                 | P3.5                  |

| T2             | I<br>O | Timer/Counter 2 External Clock Input<br>Timer/Counter 2 Clock Output                                                                                                                                                                                                                                                                                  | P1.0                  |

| T2EX           | I      | Timer/Counter 2 Reload/Capture/Direction Control Input                                                                                                                                                                                                                                                                                                | P1.1                  |

# Table 4-5. LED Signal Description

| Signal<br>Name | Туре | Description                                                                                                                                                                                                                                                                                                        | Alternate<br>Function        |

|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| LED[3:0]       | 0    | <b>Direct Drive LED Output</b><br>These pins can be directly connected to the Cathode of standard LEDs without external current limiting resistors. The typical current of each output can be programmed by software to 2, 6 or 10 mA. Several outputs can be connected together to get higher drive capabilities. | P3.3<br>P3.5<br>P3.6<br>P3.7 |

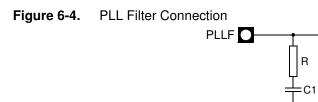

The typical values are:  $R = 560 \Omega$ , C1 = 820 pf, C2 = 150 pF.

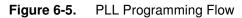

#### 6.3.2 PLL Programming

The PLL is programmed using the flow shown in Figure 6-5. As soon as clock generation is enabled user must wait until the lock indicator is set to ensure the clock output is stable.

C2

#### 6.3.3 Divider Values

To generate a 48 MHz clock using the PLL, the divider values have to be configured following the oscillator frequency. The typical divider values are shown in Table 6-1.

| Oscillator Frequency | R+1 | N+1 | PLLDIV |

|----------------------|-----|-----|--------|

| 3 MHz                | 16  | 1   | F0h    |

| 6 MHz                | 8   | 1   | 70h    |

| 8 MHz                | 6   | 1   | 50h    |

| 12 MHz               | 4   | 1   | 30h    |

| 16 MHz               | 3   | 1   | 20h    |

| 18 MHz               | 8   | 3   | 72h    |

| 20 MHz               | 12  | 5   | B4h    |

| 24 MHz               | 2   | 1   | 10h    |

Table 6-1.

Typical Divider Values

| Oscillator Frequency | R+1 | N+1 | PLLDIV |

|----------------------|-----|-----|--------|

| 32 MHz               | 3   | 2   | 21h    |

| 40 MHz               | 12  | 10  | B9h    |

# 6.4 Registers

Table 6-2.CKCON0 (S:8Fh)Clock Control Register 0

| 7          | 6               | 5                                                                                                                                                                                                                                                   | 4                                                                                                                                                                                                                                                                         | 3                                 | 2                               | 1                                                                                              | 0                                                          |  |

|------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------|--|

| TWIX2      | WDX2            | PCAX2                                                                                                                                                                                                                                               | SIX2                                                                                                                                                                                                                                                                      | T2X2                              | T1X2                            | T0X2                                                                                           | X2                                                         |  |

| Bit Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                                         | Description                                                                                                                                                                                                                                                               |                                   |                                 |                                                                                                |                                                            |  |

| 7          | TWIX2           | has no effect<br>Clear to select                                                                                                                                                                                                                    | This control bit is validated when the CPU clock X2 is set. When X2 is low, this bit                                                                                                                                                                                      |                                   |                                 |                                                                                                |                                                            |  |

| 6          | WDX2            | This control I<br>has no effect<br>Clear to select                                                                                                                                                                                                  | Watchdog Clock<br>This control bit is validated when the CPU clock X2 is set. When X2 is low, this bit<br>nas no effect.<br>Clear to select 6 clock periods per peripheral clock cycle.<br>Set to select 12 clock periods per peripheral clock cycle.                     |                                   |                                 |                                                                                                |                                                            |  |

| 5          | PCAX2           | This control I<br>has no effect<br>Clear to selec                                                                                                                                                                                                   | Programmable Counter Array Clock<br>This control bit is validated when the CPU clock X2 is set. When X2 is low, this bit<br>has no effect.<br>Clear to select 6 clock periods per peripheral clock cycle.<br>Set to select 12 clock periods per peripheral clock cycle.   |                                   |                                 |                                                                                                |                                                            |  |

| 4          | SIX2            | This control I<br>has no effect<br>Clear to select                                                                                                                                                                                                  | Enhanced UART Clock (Mode 0 and 2)<br>This control bit is validated when the CPU clock X2 is set. When X2 is low, this bit<br>has no effect.<br>Clear to select 6 clock periods per peripheral clock cycle.<br>Set to select 12 clock periods per peripheral clock cycle. |                                   |                                 |                                                                                                |                                                            |  |

| 3          | T2X2            | This control I<br>has no effect<br>Clear to select                                                                                                                                                                                                  | Timer2 Clock<br>This control bit is validated when the CPU clock X2 is set. When X2 is low, this bit<br>has no effect.<br>Clear to select 6 clock periods per peripheral clock cycle.<br>Set to select 12 clock periods per peripheral clock cycle.                       |                                   |                                 |                                                                                                |                                                            |  |

| 2          | T1X2            | Timer1 Clock<br>This control bit is validated when the CPU clock X2 is set. When X2 is low, this b<br>has no effect.<br>Clear to select 6 clock periods per peripheral clock cycle.<br>Set to select 12 clock periods per peripheral clock cycle.   |                                                                                                                                                                                                                                                                           |                                   |                                 |                                                                                                | s low, this bit                                            |  |

| 1          | T0X2            | Timer0 Clock<br>This control bit is validated when the CPU clock X2 is set. When X2 is low, this bit<br>has no effect.<br>Clear to select 6 clock periods per peripheral clock cycle.<br>Set to select 12 clock periods per peripheral clock cycle. |                                                                                                                                                                                                                                                                           |                                   |                                 |                                                                                                | s low, this bit                                            |  |

| 0          | X2              | System Clock<br>Clear to select<br>Set to select 6                                                                                                                                                                                                  | t 12 clock perio                                                                                                                                                                                                                                                          | ods per machine<br>per machine cy | e cycle (STD m<br>cle (X2 mode, | ode, F <sub>CPU</sub> = F <sub>P</sub><br>F <sub>CPU =</sub> F <sub>PER =</sub> F <sub>C</sub> | <sub>ER =</sub> F <sub>OSC</sub> /2).<br><sub>DSC</sub> ). |  |

Reset Value = 0000 0000b

#### Table 7-13. USB SFR's

| Mnemonic | Add | Name                            | 7     | 6     | 5     | 4      | 3     | 2      | 1     | 0     |

|----------|-----|---------------------------------|-------|-------|-------|--------|-------|--------|-------|-------|

| UBYCTLX  | E2h | USB Byte Counter Low<br>(EP X)  | BYCT7 | BYCT6 | BYCT5 | BYCT4  | BYCT3 | BYCT2  | BYCT1 | BYCT0 |

| UBYCTHX  | E3h | USB Byte Counter High<br>(EP X) | -     | -     | -     | -      | -     | BYCT10 | BYCT9 | BYCT8 |

| UFNUML   | BAh | USB Frame Number<br>Low         | FNUM7 | FNUM6 | FNUM5 | FNUM4  | FNUM3 | FNUM2  | FNUM1 | FNUM0 |

| UFNUMH   | BBh | USB Frame Number<br>High        | -     | -     | CRCOK | CRCERR | -     | FNUM10 | FNUM9 | FNUM8 |

## Table 7-14. Other SFR's

| Mnemonic | Add | Name                 | 7     | 6     | 5      | 4    | 3    | 2    | 1      | 0     |

|----------|-----|----------------------|-------|-------|--------|------|------|------|--------|-------|

| PCON     | 87h | Power Control        | SMOD1 | SMOD0 | -      | POF  | GF1  | GF0  | PD     | IDL   |

| AUXR     | 8Eh | Auxiliary Register 0 | DPU   | -     | MO     | -    | XRS1 | XRS2 | EXTRAM | A0    |

| AUXR1    | A2h | Auxiliary Register 1 | -     | -     | ENBOOT | -    | GF3  | -    | -      | DPS   |

| CKCON0   | 8Fh | Clock Control 0      | TWIX2 | WDX2  | PCAX2  | SIX2 | T2X2 | T1X2 | T0X2   | X2    |

| CKCON1   | AFh | Clock Control 1      | -     | -     | -      | -    | -    | -    | -      | SPIX2 |

| LEDCON   | F1h | LED Control          | LE    | D3    | LE     | D2   | LE   | D1   | LE     | D0    |

# 11. On-chip Expanded RAM (ERAM)

The AT83C5134/35/36 provides additional Bytes of random access memory (RAM) space for increased data parameters handling and high level language usage.

AT83C5134/35/36 devices have an expanded RAM in the external data space; maximum size and location are described in Table 11-1.

Table 11-1.

Description of Expanded RAM

|                 | · ·       | Add   | ress |

|-----------------|-----------|-------|------|

| Part Number     | ERAM Size | Start | End  |

| AT83C5134/35/36 | 1024      | 00h   | 3FFh |

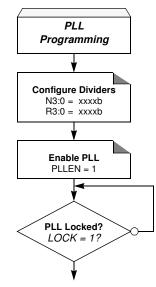

The AT83C5134/35/36 has on-chip data memory which is mapped into the following four separate segments.

- 1. The Lower 128 bytes of RAM (addresses 00h to 7Fh) are directly and indirectly addressable.

- 2. The Upper 128 bytes of RAM (addresses 80h to FFh) are indirectly addressable only.

- 3. The Special Function Registers, SFRs, (addresses 80h to FFh) are directly addressable only.

- 4. The expanded RAM bytes are indirectly accessed by MOVX instructions, and with the EXTRAM bit cleared in the AUXR register (see Table 11-1)

The lower 128 bytes can be accessed by either direct or indirect addressing. The Upper 128 bytes can be accessed by indirect addressing only. The Upper 128 bytes occupy the same address space as the SFR. That means they have the same address, but are physically separate from SFR space.

#### Figure 11-1. Internal and External Data Memory Address

When an instruction accesses an internal location above address 7Fh, the CPU knows whether the access is to the upper 128 bytes of data RAM or to SFR space by the addressing mode used in the instruction.

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                |  |  |

|---------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 4             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit                                                                                                                             |  |  |

| 3             | XRS1            | ERAM Size                                                                                                                                                                                                  |  |  |

| 2             | XRS0            | XRS1XRS0         ERAM size           0         0         256 bytes           0         1         512 bytes           1         0         768 bytes           1         1         1024 bytes (default)      |  |  |

| 1             | EXTRAM          | <b>EXTRAM bit</b><br>Cleared to access internal ERAM using MOVX at $\overline{Ri}$ at DPTR.<br>Set to access external memory.                                                                              |  |  |

| 0             | AO              | ALE Output bit<br>Cleared, ALE is emitted at a constant rate of 1/6 the oscillator frequency (or 1/3 if X2<br>mode is used) (default).<br>Set, ALE is active only when a MOVX or MOVC instruction is used. |  |  |

Reset Value = 0X0X 1100b Not bit addressable

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                    |

|---------------|-----------------|----------------------------------------------------------------------------------------------------------------|

| 1             | CCF1            | PCA Module 1 Interrupt Flag<br>Must be cleared by software.<br>Set by hardware when a match or capture occurs. |

| 0             | CCF0            | PCA Module 0 Interrupt Flag<br>Must be cleared by software.<br>Set by hardware when a match or capture occurs. |

Reset Value = 000X 0000b

Not bit addressable

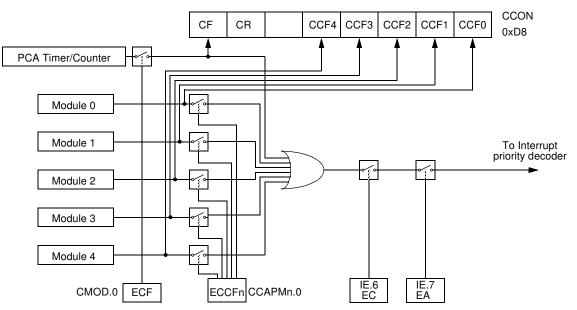

The watchdog timer function is implemented in module 4 (See Figure 13-4).

The PCA interrupt system is shown in Figure 13-2.

**PCA Modules:** each one of the five compare/capture modules has six possible functions. It can perform:

- 16-bit capture, positive-edge triggered

- 16-bit capture, negative-edge triggered

- · 16-bit capture, both positive and negative-edge triggered

- 16-bit Software Timer

- 16-bit High-speed Output

- 8-bit Pulse Width Modulator

In addition, module 4 can be used as a Watchdog Timer.

Each module in the PCA has a special function register associated with it. These registers are: CCAPM0 for module 0, CCAPM1 for module 1, etc. (see Table 13-3). The registers contain the bits that control the mode that each module will operate in.

SADEN - Slave Address Mask Register (B9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

SADDR - Slave Address Register (A9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

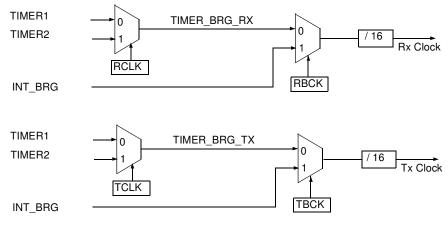

# 14.3 Baud Rate Selection for UART for Mode 1 and 3

The Baud Rate Generator for transmit and receive clocks can be selected separately via the T2CON and BDRCON registers.

Figure 14-4. Baud Rate Selection

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                                                     |  |  |  |  |  |

|---------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7             | FE              | Framing Error bit (SMOD0 = 1)<br>Clear to reset the error state, not cleared by a valid stop bit.<br>Set by hardware when an invalid stop bit is detected.<br>SMOD0 must be set to enable access to the FE bit                                                  |  |  |  |  |  |

|               | SM0             | Serial port Mode bit 0<br>Refer to SM1 for serial port mode selection.<br>SMOD0 must be cleared to enable access to the SM0 bit                                                                                                                                 |  |  |  |  |  |

| 6             | SM1             | $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                          |  |  |  |  |  |

| 5             | SM2             | Serial port Mode 2 bit/Multiprocessor Communication Enable bit<br>Clear to disable multiprocessor communication feature.<br>Set to enable multiprocessor communication feature in mode 2 and 3, and eventually<br>mode 1. This bit should be cleared in mode 0. |  |  |  |  |  |

| 4             | REN             | Reception Enable bit<br>Clear to disable serial reception.<br>Set to enable serial reception.                                                                                                                                                                   |  |  |  |  |  |

| 3             | TB8             | Transmitter Bit 8/Ninth bit to Transmit in Modes 2 and 3<br>Clear to transmit a logic 0 in the 9th bit.<br>Set to transmit a logic 1 in the 9th bit.                                                                                                            |  |  |  |  |  |

| 2             | RB8             | Receiver Bit 8/Ninth bit received in modes 2 and 3<br>Cleared by hardware if 9th bit received is a logic 0.<br>Set by hardware if 9th bit received is a logic 1.<br>In mode 1, if SM2 = 0, RB8 is the received stop bit. In mode 0 RB8 is not used.             |  |  |  |  |  |

| 1             | ті              | Transmit Interrupt flag<br>Clear to acknowledge interrupt.<br>Set by hardware at the end of the 8th bit time in mode 0 or at the beginning of the stop bit<br>in the other modes.                                                                               |  |  |  |  |  |

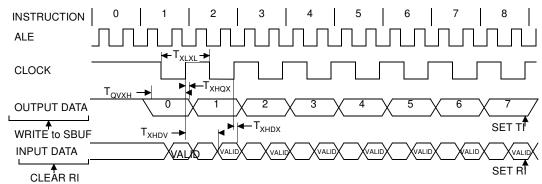

| 0             | RI              | Receive Interrupt flag<br>Clear to acknowledge interrupt.<br>Set by hardware at the end of the 8th bit time in mode 0, see Figure 14-2. and Figure 14-<br>3. in the other modes.                                                                                |  |  |  |  |  |

Reset Value = 0000 0000b Bit addressable

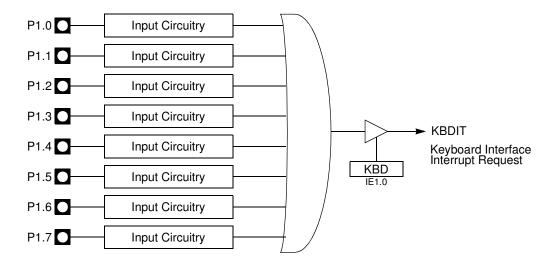

# 17. Keyboard Interface

# 17.1 Introduction

The AT83C5134/35/36 implements a keyboard interface allowing the connection of a 8 x n matrix keyboard. It is based on 8 inputs with programmable interrupt capability on both high or low level. These inputs are available as an alternate function of P1 and allow to exit from idle and power down modes.

# 17.2 Description

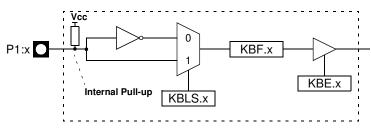

The keyboard interface communicates with the C51 core through 3 special function registers: KBLS, the Keyboard Level Selection register (Table 17-3), KBE, The Keyboard interrupt Enable register (Table 17-2), and KBF, the Keyboard Flag register (Table 17-1).

#### 17.2.1 Interrupt

The keyboard inputs are considered as 8 independent interrupt sources sharing the same interrupt vector. An interrupt enable bit (KBD in IE1) allows global enable or disable of the keyboard interrupt (see Figure 17-1). As detailed in Figure 17-2 each keyboard input has the capability to detect a programmable level according to KBLS.x bit value. Level detection is then reported in interrupt flags KBF.x that can be masked by software using KBE.x bits.

This structure allow keyboard arrangement from 1 by n to 8 by n matrix and allow usage of P1 inputs for other purpose.

Figure 17-1. Keyboard Interface Block Diagram

70 AT83C5134/35/36

|                |                                         | Appli                | cation soft | ware respo | nse                                 |      |                                                                                                |

|----------------|-----------------------------------------|----------------------|-------------|------------|-------------------------------------|------|------------------------------------------------------------------------------------------------|

| Status<br>Code | Status of the Two-<br>wire Bus and Two- |                      | To SSCON    |            |                                     |      |                                                                                                |

| SSSTA          | wire Hardware                           | To/From SSDAT        | SSSTA       | SSSTO      | SSI                                 | SSAA | Next Action Taken by Two-wire Hardware                                                         |

| 08h            | A START condition has been transmitted  | Write SLA+R          | x           | 0          | 0                                   | х    | SLA+R will be transmitted.                                                                     |

|                | A repeated START                        | Write SLA+R          | х           | 0          | 0                                   | х    | SLA+R will be transmitted.                                                                     |

| 10h            | condition has been<br>transmitted       | Write SLA+W          | x           | 0          | 0                                   | х    | SLA+W will be transmitted.<br>Logic will switch to master transmitter mode.                    |

| 38h            | Arbitration lost in<br>SLA+R or NOT ACK | No SSDAT action      | 0           | 0          | 0                                   | х    | Two-wire bus will be released and not addressed slave mode will be entered.                    |

| 3011           | bit                                     | No SSDAT action      | 1           | 0          | 0                                   | х    | A START condition will be transmitted when the bus becomes free.                               |

| 40h            | SLA+R has been<br>transmitted; ACK has  | No SSDAT action      | 0           | 0          | 0                                   | 0    | Data byte will be received and NOT ACK will be returned.                                       |

|                | been received                           | No SSDAT action      | 0           | 0          | 0                                   | 1    | Data byte will be received and ACK will be returned.                                           |

|                | SLA+R has been                          | No SSDAT action      | 1           | 0          | 0                                   | х    | Repeated START will be transmitted.<br>STOP condition will be transmitted and SSSTO flag       |

| 48h            | transmitted; NOT ACK                    | No SSDAT action      | 0           | 1          | 0                                   | х    | will be reset.                                                                                 |

|                | has been received                       | No SSDAT action      | 1           | 1          | 0                                   | х    | STOP condition followed by a START condition will be transmitted and SSSTO flag will be reset. |

| 50h            | Data byte has been<br>received; ACK has | Read data byte       | 0           | 0          | 0                                   | 0    | Data byte will be received and NOT ACK will be returned.                                       |

|                | been returned                           | Read data byte       | 0           | 0          | 0                                   | 1    | Data byte will be received and ACK will be returned.                                           |

|                |                                         | Read data byte 1 0 0 |             | х          | Repeated START will be transmitted. |      |                                                                                                |

| 58h            | Data byte has been received; NOT ACK    | Read data byte       | 0           | 1          | 0                                   | Х    | STOP condition will be transmitted and SSSTO flag will be reset.                               |

|                | has been returned                       | Read data byte       | 1           | 1          | 0                                   | х    | STOP condition followed by a START condition will be transmitted and SSSTO flag will be reset. |

Table 20-6. Status in Master Receiver Mode

The firmware has to clear one of these two bits after having read all the data FIFO to allow a new packet to be stored in the corresponding bank.

If the Host sends more bytes than supported by the endpoint FIFO, the overflow data won't be stored, but the USB controller will consider that the packet is valid if the CRC is correct.

#### 21.6.3 Isochronous IN Transactions in Standard Mode

An endpoint will be first enabled and configured before being able to send Isochronous packets.

The firmware will fill the FIFO with the data to be sent and set the TXRDY bit in the UEPSTAX register to allow the USB controller to send the data stored in FIFO at the next IN request concerning this endpoint.

If the TXRDY bit is not set when the IN request occurs, nothing will be sent by the USB controller.

When the IN packet has been sent, the TXCMPL bit in the UEPSTAX register is set by the USB controller. This triggers a USB interrupt if enabled. The firmware will clear the TXCMPL bit before filling the endpoint FIFO with new data.

The firmware will never write more bytes than supported by the endpoint FIFO

#### 21.6.4 Isochronous IN Transactions in Ping-pong Mode

An endpoint will be first enabled and configured before being able to send Isochronous packets.

The firmware will fill the FIFO bank 0 with the data to be sent and set the TXRDY bit in the UEP-STAX register to allow the USB controller to send the data stored in FIFO at the next IN request concerning the endpoint. The FIFO banks are automatically switched, and the firmware can immediately write into the endpoint FIFO bank 1.

If the TXRDY bit is not set when the IN request occurs, nothing will be sent by the USB controller.

When the IN packet concerning the bank 0 has been sent, the TXCMPL bit is set by the USB controller. This triggers a USB interrupt if enabled. The firmware will clear the TXCMPL bit before filling the endpoint FIFO bank 0 with new data. The FIFO banks are then automatically switched.

When the IN packet concerning the bank 1 has been sent, the TXCMPL bit is set by the USB controller. This triggers a USB interrupt if enabled. The firmware will clear the TXCMPL bit before filling the endpoint FIFO bank 1 with new data.

The bank switch is performed by the USB controller each time the TXRDY bit is set by the firmware. Until the TXRDY bit has been set by the firmware for an endpoint bank, the USB controller won't send anything at each IN requests concerning this bank.

The firmware will never write more bytes than supported by the endpoint FIFO.

# 21.7 Miscellaneous

#### 21.7.1 USB Reset

The EORINT bit in the USBINT register is set by hardware when a End Of Reset has been detected on the USB bus. This triggers a USB interrupt if enabled. The USB controller is still enabled, but all the USB registers are reset by hardware. The firmware will clear the EORINT bit to allow the next USB reset detection.

# Table 21-4.USBINT RegisterUSBINT (S:BDh)USB Global Interrupt Register

| 7          | 6               | 5                                                            | 4                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3                 | 2               | 1       | 0     |  |

|------------|-----------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------|---------|-------|--|

| -          | -               | WUPCPU                                                       | EORINT                                                                                                                                                                                                                                                                                                                                                                                                                             | SOFINT            | -               | -       | SPINT |  |

| Bit Number | Bit<br>Mnemonic | Description                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |                 |         |       |  |

| 7-6        | -               | Reserved<br>The value read                                   | d from these bi                                                                                                                                                                                                                                                                                                                                                                                                                    | ts is always 0. I | Do not set thes | e bits. |       |  |

| 5          | WUPCPU          | This bit is set activated by a triggers a USE When receiving | <b>Vake Up CPU Interrupt</b><br>his bit is set by hardware when the USB controller is in SUSPEND state and is re-<br>ctivated by a non-idle signal FROM USB line (not by an upstream resume). This<br>iggers a USB interrupt when EWUPCPU is set in Table 21-5 on page 122.<br>/hen receiving this interrupt, user has to enable all USB clock inputs.<br>his bit will be cleared by software (USB clocks must be enabled before). |                   |                 |         |       |  |

| 4          | EORINT          | This bit is set l<br>controller. This<br>122).               | End Of Reset Interrupt<br>This bit is set by hardware when a End Of Reset has been detected by the USB<br>controller. This triggers a USB interrupt when EEORINT is set (see Figure 21-5 on page<br>122).<br>This bit will be cleared by software.                                                                                                                                                                                 |                   |                 |         |       |  |

| 3          | SOFINT          | This bit is set I<br>This triggers a                         | Start of Frame Interrupt<br>This bit is set by hardware when an USB Start of Frame PID (SOF) has been detected.<br>This triggers a USB interrupt when ESOFINT is set (see Table 21-5 on page 122).<br>This bit will be cleared by software.                                                                                                                                                                                        |                   |                 |         |       |  |

| 2          | -               | Reserved<br>The value read                                   | <b>Reserved</b><br>The value read from this bit is always 0. Do not set this bit.                                                                                                                                                                                                                                                                                                                                                  |                   |                 |         |       |  |

| 1          | -               | Reserved<br>The value read                                   | Reserved<br>The value read from this bit is always 0. Do not set this bit.                                                                                                                                                                                                                                                                                                                                                         |                   |                 |         |       |  |

| 0          | SPINT           | This bit is set state for 3 ms)<br>Table 21-5 on             | <b>Suspend Interrupt</b><br>This bit is set by hardware when a USB Suspend (Idle bus for three frame periods: a J<br>state for 3 ms) is detected. This triggers a USB interrupt when ESPINT is set in see<br>Table 21-5 on page 122.<br>This bit will be cleared by software BEFORE any other USB operation to re-activate the                                                                                                     |                   |                 |         |       |  |

Reset Value = 00h

# 24. Power Management

# 24.1 Idle Mode

An instruction that sets PCON.0 indicates that it is the last instruction to be executed before going into the Idle mode. In the Idle mode, the internal clock signal is gated off to the CPU, but not to the interrupt, Timer, and Serial Port functions. The CPU status is preserved in its entirety: the Stack Pointer, Program Counter, Program Status Word, Accumulator and all other registers maintain their data during Idle. The port pins hold the logical states they had at the time Idle was activated. ALE and PSEN hold at logic high level.

There are two ways to terminate the Idle mode. Activation of any enabled interrupt will cause PCON.0 to be cleared by hardware, terminating the Idle mode. The interrupt will be serviced, and following RETI the next instruction to be executed will be the one following the instruction that put the device into idle.

The flag bits GF0 and GF1 can be used to give an indication if an interrupt occurred during normal operation or during an Idle. For example, an instruction that activates Idle can also set one or both flag bits. When Idle is terminated by an interrupt, the interrupt service routine can examine the flag bits.

The other way of terminating the Idle mode is with a hardware reset. Since the clock oscillator is still running, the hardware reset needs to be held active for only two machine cycles (24 oscillator periods) to complete the reset.

## 24.2 Power-down Mode

To save maximum power, a power-down mode can be invoked by software (refer to Table 13, PCON register).

In power-down mode, the oscillator is stopped and the instruction that invoked power-down mode is the last instruction executed. The internal RAM and SFRs retain their value until the power-down mode is terminated.  $V_{CC}$  can be lowered to save further power. Either a hardware reset or an external interrupt can cause an exit from power-down. To properly terminate power-down, the reset or external interrupt should not be executed before  $V_{CC}$  is restored to its normal operating level and must be held active long enough for the oscillator to restart and stabilize.

Only:

- external interrupt INTO,

- external interrupt INT1,

- · Keyboard interrupt and

- USB Interrupt

are useful to exit from power-down. For that, interrupt must be enabled and configured as level or edge sensitive interrupt input. When Keyboard Interrupt occurs after a power down mode, 1024 clocks are necessary to exit to power-down mode and enter in operating mode.

Holding the pin low restarts the oscillator but bringing the pin high completes the exit as detailed in Figure 24-1. When both interrupts are enabled, the oscillator restarts as soon as one of the two inputs is held low and power-down exit will be completed when the first input is released. In this case, the higher priority interrupt service routine is executed. Once the interrupt is serviced, the next instruction to be executed after RETI will be the one following the instruction that put AT83C5134/35/36 into power-down mode.

# 27.4.8 Shift Register Timing Waveform

#### 27.4.9 External Clock Drive Characteristics (XTAL1) Table 27-11. AC Parameters

| Symbol                               | Parameter               | Min | Мах | Units |

|--------------------------------------|-------------------------|-----|-----|-------|

| T <sub>CLCL</sub>                    | Oscillator Period       | 21  |     | ns    |

| T <sub>CHCX</sub>                    | High Time               | 5   |     | ns    |

| T <sub>CLCX</sub>                    | Low Time                | 5   |     | ns    |

| T <sub>CLCH</sub>                    | Rise Time               |     | 5   | ns    |

| T <sub>CHCL</sub>                    | Fall Time               |     | 5   | ns    |

| T <sub>CHCX</sub> /T <sub>CLCX</sub> | Cyclic ratio in X2 mode | 40  | 60  | %     |

#### 27.4.10 External Clock Drive Waveforms

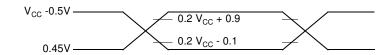

#### 27.4.11 AC Testing Input/Output Waveforms

INPUT/OUTPUT

AC inputs during testing are driven at V<sub>CC</sub> - 0.5 for a logic "1" and 0.45V for a logic "0". Timing measurement are made at V<sub>IH</sub> min for a logic "1" and V<sub>IL</sub> max for a logic "0".

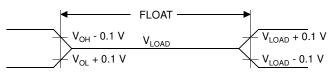

#### 27.4.12 Float Waveforms

For timing purposes as port pin is no longer floating when a 100 mV change from load voltage occurs and begins to float when a 100 mV change from the loaded  $V_{OH}/V_{OL}$  level occurs.  $I_{OL}/I_{OH} \ge \pm 20$  mA.

# AT83C5134/35/36

# Table 27-12. Memory AC Timing VDD = $3.3V \pm 10\%$ , T<sub>A</sub> = -40 to +85°C

| Symbol            | Parameter                      | Min | Тур | Max | Unit |

|-------------------|--------------------------------|-----|-----|-----|------|

| T <sub>SVRL</sub> | Input PSEN Valid to RST Edge   | 50  |     |     | ns   |

| T <sub>RLSX</sub> | Input PSEN Hold after RST Edge | 50  |     |     | ns   |

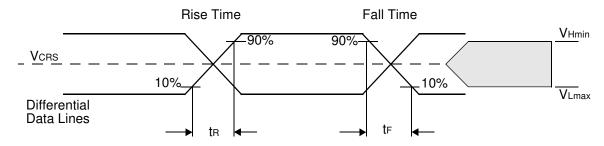

# 27.5 USB AC Parameters

## Table 27-13. USB AC Parameters

| Symbol              | Parameter                                      | Min     | Тур | Мах     | Unit | Test Conditions |

|---------------------|------------------------------------------------|---------|-----|---------|------|-----------------|

| t <sub>R</sub>      | Rise Time                                      | 4       |     | 20      | ns   |                 |

| t <sub>F</sub>      | Fall Time                                      | 4       |     | 20      | ns   |                 |

| t <sub>FDRATE</sub> | Full-speed Data Rate                           | 11.9700 |     | 12.0300 | Mb/s |                 |

| V <sub>CRS</sub>    | Crossover Voltage                              | 1.3     |     | 2.0     | V    |                 |

| t <sub>DJ1</sub>    | Source Jitter Total to Next<br>Transaction     | -3.5    |     | 3.5     | ns   |                 |

| t <sub>DJ2</sub>    | Source Jitter Total for Paired<br>Transactions | -4      |     | 4       | ns   |                 |

| t <sub>JR1</sub>    | Receiver Jitter to Next<br>Transaction         | -18.5   |     | 18.5    | ns   |                 |

| t <sub>JR2</sub>    | Receiver Jitter for Paired<br>Transactions     | -9      |     | 9       | ns   |                 |

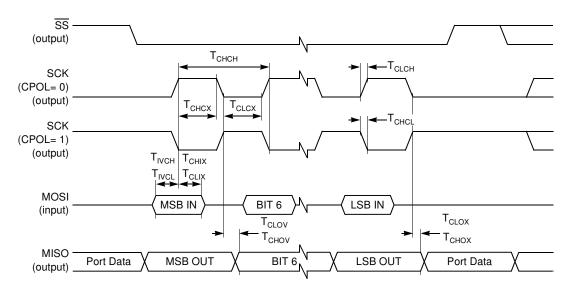

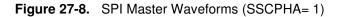

# 27.6 SPI Interface AC Parameters

27.6.0.1 Definition of Symbols

Table 27-14.

SPI Interface Timing Symbol Definitions

| Signals |          |  |  |

|---------|----------|--|--|

| С       | Clock    |  |  |

| 1       | Data In  |  |  |

| 0       | Data Out |  |  |

|   | Conditions      |  |  |  |  |  |

|---|-----------------|--|--|--|--|--|

| н | High            |  |  |  |  |  |

| L | Low             |  |  |  |  |  |

| V | Valid           |  |  |  |  |  |

| х | No Longer Valid |  |  |  |  |  |

| Z | Floating        |  |  |  |  |  |

Figure 27-7. SPI Master Waveforms (SSCPHA= 0)

Note: 1. SS handled by software using general purpose port pin.

SS handled by software using general purpose port pin.

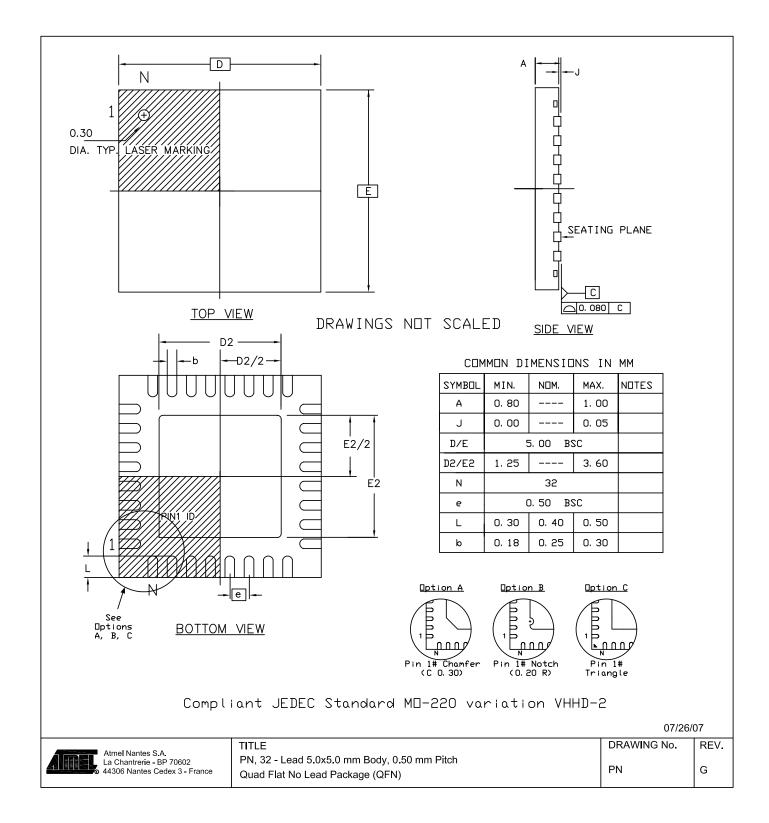

# NOTES: MLF PACKAGE FAMILY

- 1. DIE THICKNESS ALLOWABLE IS 0.305mm MAXIMUM(.012 INCHES MAXIMUM)

- 2. DIMENSIONING & TOLERANCES CONFORM TO ASME Y14.5M. 1994.

- 3 DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED

BETWEEN 0.20 AND 0.25mm FROM TERMINAL TIP.

- 4 PACKAGE WARPAGE MAX 0.08mm.

- 5 THE PIN #1 IDENTIFIER MUST BE EXISTED ON THE TOP SURFACE OF THE PACKAGE BY USING INDENTATION MARK OR OTHER FEATURE OF PACKAGE BODY.

- 6 EXACT SHAPE AND SIZE OF THIS FIXTURE IS OPTIONAL

# 29.4 QFN32