Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | M8C                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 24MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | LVD, POR, PWM, WDT                                                          |

| Number of I/O              | 26                                                                          |

| Program Memory Size        | 8KB (8K x 8)                                                                |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                |                                                                             |

| RAM Size                   | 256 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.25V                                                                  |

| Data Converters            | A/D 8x14b; D/A 4x8b                                                         |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

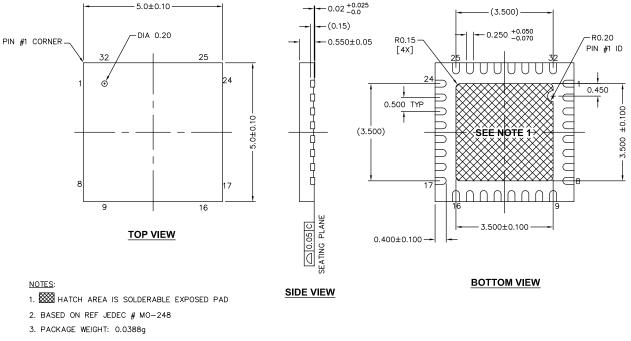

| Mounting Type              | Surface Mount                                                               |

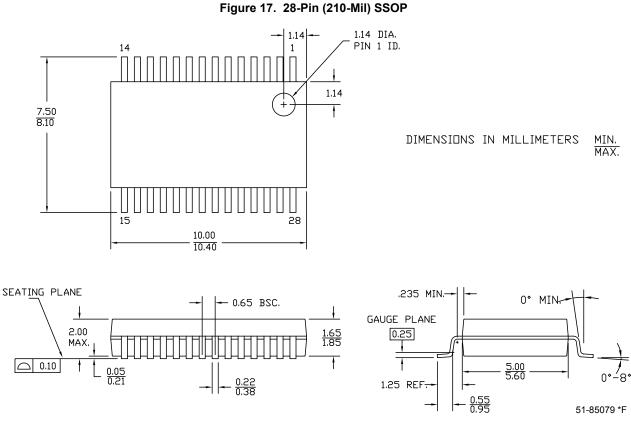

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c23433-24pvxi |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **PSoC Functional Overview**

The PSoC family consists of many programmable system-on-chips with on-chip controller devices. These devices are designed to replace multiple traditional MCU-based system components with a low-cost single-chip programmable device. PSoC devices include configurable blocks of analog and digital logic, and programmable interconnects. This architecture make it possible for you to create customized peripheral configurations that match the requirements of each individual application. additionally, a fast central processing unit (CPU), flash memory, SRAM data memory, and configurable I/O are included in a range of convenient pinouts and packages.

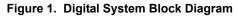

The PSoC architecture, as shown in the Logic Block Diagram on page 1, consists of four main areas: PSoC core, digital system, analog system, and system resources. Configurable global busing allows combining all of the device resources into a complete custom system. The PSoC CY8C23x33 family can have up to three I/O ports that connect to the global digital and analog interconnects, providing access to four digital blocks and four analog blocks.

# **PSoC Core**

The PSoC core is a powerful engine that supports a rich feature set. The core includes a CPU, memory, clocks, and configurable general Purpose I/O (GPIO)

The M8C CPU core is a powerful processor with speeds up to 24 MHz, providing a four million instructions per second MIPS 8-bit Harvard-architecture microprocessor. The CPU uses an interrupt controller with 11 vectors, to simplify programming of real time embedded events. program execution is timed and protected using the included sleep and watch dog timers (WDT).

Memory encompasses 8 KB of flash for program storage, 256 bytes of SRAM for data storage, and up to 2 KB of EEPROM emulated using the flash. Program flash uses four protection levels on blocks of 64 bytes, allowing customized software IP protection.

The PSoC device incorporates flexible internal clock generators, including a 24 MHz internal main oscillator (IMO) accurate to  $\pm 5\%$  <sup>[2]</sup> over temperature and voltage. The 24 MHz IMO can also be doubled to 48 MHz for use by the digital system. A low power 32 kHz internal low speed oscillator (ILO) is provided for the sleep timer and WDT. If crystal accuracy is desired, the ECO (32.768 kHz external crystal oscillator) is available for use as a real time clock (RTC) and can optionally generate a crystal-accurate 24 MHz system clock using a PLL. The clocks, together with programmable clock dividers (as a system resource), provide the flexibility to integrate almost any timing requirement into the PSoC device.

PSoC GPIOs provide connection to the CPU, digital and analog resources of the device. Each pin's drive mode may be selected from eight options, allowing great flexibility in external interfacing. Every pin also has the capability to generate a system interrupt on high level, low level, and change from last read.

# **Digital System**

The Digital system consists of 4 digital PSoC blocks. Each block is an 8-bit resource that is used alone or combined with other blocks to form 8, 16, 24, and 32-bit peripherals, which are called user module references.

Digital peripheral configurations are:

- PWMs (8-and 16-bit)

- PWMs with Dead band (8- and 16-bit)

- Counters (8- to 32- bit)

- Timers (8- to 32- bit)

- UART 8 bit with selectable parity (up to 1)

- Serial peripheral interface (SPI) master and slave (up to 1)

- I<sup>2</sup>C slave and multi master (1 available as a system resource)

- Cyclical redundancy checker (CRC)/Generator (8 to 32 bit)

- IrDA (up to 1)

Pseudo Random Sequence Generators (8- to 32- bit)

The digital blocks can be connected to any GPIO through a series of global buses that can route any signal to any pin. The buses also allow for signal multiplexing and for performing logic operations. This configurability frees your designs from the constraints of a fixed peripheral controller.

Digital blocks are provided in rows of four, where the number of blocks varies by PSoC device family. This allows the optimum choice of system resources for your application. Family resources are shown in the table titled PSoC Device Characteristics on page 5.

#### Note

<sup>2.</sup> Errata: When the device is operated within 0 °C to 70 °C, the frequency tolerance is reduced to ±2.5%, but if operated at extreme temperature (below 0 °C or above 70 °C), frequency tolerance deviates from ±2.5% to ±5%. For more information, see Errata on page 50.

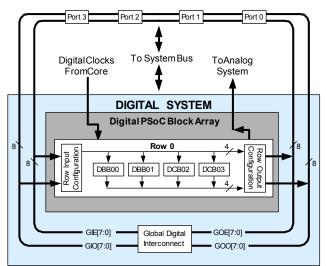

# Analog System

The analog system consists of an 8-bit SAR ADC and four configurable blocks. The programmable 8-bit SAR ADC is an optimized ADC that runs up to 300 Ksps, with monotonic guarantee. It also has the features to support a motor control application.

Each analog block consists of an opamp circuit allowing the creation of complex analog signal flows. Analog peripherals are very flexible and can be customized to support specific application requirements. Some of the more common PSoC analog functions (most available as user modules) are:

- Filters (2 band pass, low-pass)

- Amplifiers (up to 2, with selectable gain to 48x)

- Instrumentation amplifiers (1 with selectable gain to 93x)

- Comparators (1, with 16 selectable thresholds)

- DAC (6 or 9-bit DAC)

- Multiplying DAC (6 or 9-bit DAC)

- High current output drivers (two with 30 mA drive)

- 1.3-V reference (as a system resource)

- DTMF dialer

- Modulators

- Correlators

- Peak detectors

- Many other topologies possible

Analog blocks are arranged in a column of three, which includes one continuous time (CT) and two switched capacitor (SC) blocks. The Analog column 0 contains the SAR8 ADC block rather than the standard SC blocks.

#### Figure 2. Analog System Block Diagram

# Additional System Resources

System resources, some of which are listed in the previous sections, provide additional capability useful to complete systems. Additional resources include a multiplier, decimator, low voltage detection, and power-on-reset. Brief statements describing the merits of each system resource follow:

- Digital clock dividers provide three customizable clock frequencies for use in applications. The clocks may be routed to both the digital and analog systems. Additional clocks can be generated using digital PSoC blocks as clock dividers.

- A multiply accumulate (MAC) provides a fast 8-bit multiplier with 32-bit accumulate, to assist in both general math and digital filters.

- The decimator provides a custom hardware filter for digital signal processing applications including the creation of delta sigma ADCs.

- The I<sup>2</sup>C module provides 100- and 400-kHz communication over two wires. Slave, master, and multi-master modes are all supported.

- Low-Voltage detection interrupts can signal the application of falling voltage levels, while the advanced POR circuit eliminates the need for a system supervisor.

- An internal 1.3-V reference provides an absolute reference for the analog system, including ADCs and DACs.

# **PSoC Device Characteristics**

Depending on the PSoC device characteristics, the digital and analog systems can have 16, 8, or 4 digital blocks and 12, 6, or 3 analog blocks. Table 1 lists the resources available for specific PSoC device groups.

| PSoC Part<br>Number | Digital<br>I/O | Digital<br>Rows | Digital<br>Blocks | Analog<br>Inputs | Analog<br>Outputs | Analog<br>Columns | Analog<br>Blocks               | SRAM<br>Size | Flash<br>Size | SAR<br>ADC |

|---------------------|----------------|-----------------|-------------------|------------------|-------------------|-------------------|--------------------------------|--------------|---------------|------------|

| CY8C29x66           | up to 64       | 4               | 16                | up to 12         | 4                 | 4                 | 12                             | 2 K          | 32 K          | No         |

| CY8C28xxx           | up to 44       | up to 3         | up to 12          | up to 44         | up to 4           | up to 6           | up to<br>12 + 4 <sup>[3]</sup> | 1 K          | 16 K          | Yes        |

| CY8C27x43           | up to 44       | 2               | 8                 | up to 12         | 4                 | 4                 | 12                             | 256          | 16 K          | No         |

| CY8C24x94           | up to 56       | 1               | 4                 | up to 48         | 2                 | 2                 | 6                              | 1 K          | 16 K          | No         |

| CY8C24x23A          | up to 24       | 1               | 4                 | up to 12         | 2                 | 2                 | 6                              | 256          | 4 K           | No         |

| CY8C23x33           | up to 26       | 1               | 4                 | up to 12         | 2                 | 2                 | 4                              | 256          | 8 K           | Yes        |

| CY8C24x33           | up to 26       | 1               | 4                 | up to 12         | 2                 | 2                 | 4                              | 256          | 8 K           | Yes        |

| CY8C22x45           | up to 38       | 2               | 8                 | up to 38         | 0                 | 4                 | 6 <sup>[3]</sup>               | 1 K          | 16 K          | No         |

| CY8C21x45           | up to 24       | 1               | 4                 | up to 24         | 0                 | 4                 | 6 <sup>[3]</sup>               | 512          | 8 K           | Yes        |

| CY8C21x34           | up to 28       | 1               | 4                 | up to 28         | 0                 | 2                 | 4 <sup>[3]</sup>               | 512          | 8 K           | No         |

| CY8C21x23           | up to 16       | 1               | 4                 | up to 8          | 0                 | 2                 | 4 <sup>[3]</sup>               | 256          | 4 K           | No         |

| CY8C20x34           | up to 28       | 0               | 0                 | up to 28         | 0                 | 0                 | 3 <sup>[3,4]</sup>             | 512          | 8 K           | No         |

| CY8C20xx6           | up to 36       | 0               | 0                 | up to 36         | 0                 | 0                 | 3 <sup>[3,4]</sup>             | up to<br>2 K | up to<br>32 K | No         |

Table 1. PSoC Device Characteristics

3. Limited analog functionality.

4. Two analog blocks and one CapSense®.

# **Getting Started**

The quickest way to understand PSoC silicon is to read this data sheet and then use the PSoC Designer integrated development environment (IDE). This data sheet is an overview of the PSoC integrated circuit and presents specific pin, register, and electrical specifications.

For in-depth information, along with detailed programming details, see the PSoC<sup>®</sup> Technical Reference Manual.

For up-to-date ordering, packaging, and electrical specification information, see the latest PSoC device data sheets on the web at http://www.cypress.com.

# **Application Notes**

Cypress application notes are an excellent introduction to the wide variety of possible PSoC designs and can be found at http://www.cypress.com

# **Development Kits**

PSoC Development Kits are available online from cypress at http://www.cypress.com and through a growing number of regional and global distributors, which include Arrow, Avnet, Digi-Key, Farnell, Future Electronics, and Newark.

# Training

Free PSoC technical training (on demand, webinars, and workshops), which is available online at http:// www.cypress.com, covers a wide variety of topics and skill levels to assist you in your designs.

# **CYPros Consultants**

Certified PSoC consultants offer everything from technical assistance to completed PSoC designs. To contact or become a PSoC consultant go to http://www.cypress.com and look for CYPros.

# **Solutions Library**

Visit our growing library of solution-focused designs. Here you can find various application designs that include firmware and hardware design files that enable you to complete your designs quickly.

# **Technical Support**

For assistance with technical issues, search KnowledgeBase articles and forums at http://www.cypress.com. If you cannot find an answer to your question, call technical support at 1-800-541-4736.

# **Register Reference**

This section lists the registers of the CY8C23433 PSoC device by using mapping tables, in offset order.

# **Register Conventions**

The register conventions specific to this section are listed in Table 4.

#### Table 4. Register Conventions

| Convention | Description                  |

|------------|------------------------------|

| R          | Read register or bit(s)      |

| W          | Write register or bit(s)     |

| L          | Logical register or bit(s)   |

| С          | Clearable register or bit(s) |

| #          | Access is bit specific       |

# **Register Mapping Tables**

The PSoC device has a total register address space of 512 bytes. The register space is referred to as I/O space and is divided into two banks Bank 0 and Bank 1. The XIO bit in the Flag register (CPU\_F) determines which bank the user is currently in. When the XIO bit is set to 1 the user is in Bank 1.

**Note** In the following register mapping tables, blank fields are reserved and must not be accessed.

#### Table 6. Register Map Bank 1 Table: Configuration Space

| Name               | Addr (1,Hex) |      | ble: Configui<br>Name | Addr (1,Hex) | Access | Name        | Addr (1,Hex) | Access | Name      | Addr (1,Hex) | Δοτορείο |

|--------------------|--------------|------|-----------------------|--------------|--------|-------------|--------------|--------|-----------|--------------|----------|

| PRT0DM0            | 00           | RW   | Name                  | 40           | ALLESS | Name        | 80           | ALLESS | Name      | C0           | Access   |

| PRT0DM1            | 01           | RW   |                       | 41           |        |             | 81           |        |           | C1           |          |

| PRTOICO            | 02           | RW   |                       | 42           |        |             | 82           |        |           | C2           |          |

| PRT0IC1            | 03           | RW   |                       | 43           |        |             | 83           |        |           | C3           |          |

| PRT1DM0            | 04           | RW   |                       | 40           |        | ASD11CR0    | 84           | RW     |           | C4           |          |

| PRT1DM1            | 05           | RW   |                       | 45           |        | ASD11CR1    | 85           | RW     |           | C5           |          |

| PRT1IC0            | 06           | RW   |                       | 46           |        | ASD11CR2    | 86           | RW     |           | C6           |          |

| PRT1IC1            | 00           | RW   |                       | 40           |        | ASD11CR3    | 87           | RW     |           | C0<br>C7     |          |

| PRT2DM0            | 07           | RW   |                       | 48           |        | ASDITICKS   | 88           | I.V.V  |           | C8           |          |

| PRT2DM0<br>PRT2DM1 | 08           | RW   |                       | 40           |        |             | 89           |        |           | C8           |          |

| PRT2DMT<br>PRT2IC0 | 09<br>0A     |      |                       |              |        |             |              |        |           |              |          |

|                    |              | RW   |                       | 4A           |        |             | 8A           |        |           | CA           |          |

| PRT2IC1            | 0B           | RW   |                       | 4B           |        |             | 8B           |        |           | CB           |          |

| PRT3DM0            | 0C           | RW   |                       | 4C           |        |             | 8C           |        |           | CC           |          |

| PRT3DM1            | 0D           | RW   |                       | 4D           |        |             | 8D           |        |           | CD           |          |

| PRT3IC0            | 0E           | RW   |                       | 4E           |        |             | 8E           |        |           | CE           |          |

| PRT3IC1            | 0F           | RW   |                       | 4F           |        |             | 8F           |        |           | CF           |          |

|                    | 10           |      |                       | 50           |        |             | 90           |        | GDI_O_IN  | D0           | RW       |

|                    | 11           |      |                       | 51           |        |             | 91           |        | GDI_E_IN  | D1           | RW       |

|                    | 12           |      |                       | 52           |        |             | 92           |        | GDI_O_OU  | D2           | RW       |

|                    | 13           |      |                       | 53           |        |             | 93           |        | GDI_E_OU  | D3           | RW       |

|                    | 14           |      |                       | 54           |        | ASC21CR0    | 94           | RW     |           | D4           |          |

|                    | 15           |      |                       | 55           |        | ASC21CR1    | 95           | RW     |           | D5           |          |

|                    | 16           |      |                       | 56           |        | ASC21CR2    | 96           | RW     |           | D6           |          |

|                    | 17           |      |                       | 57           |        | ASC21CR3    | 97           | RW     |           | D7           |          |

|                    | 18           |      |                       | 58           |        |             | 98           |        |           | D8           |          |

|                    | 19           |      |                       | 59           |        |             | 99           |        |           | D9           |          |

|                    | 1A           |      |                       | 5A           |        |             | 9A           |        |           | DA           |          |

|                    | 1B           |      |                       | 5B           |        |             | 9B           |        |           | DB           |          |

|                    | 1C           |      |                       | 5C           |        |             | 9C           |        |           | DC           |          |

|                    | 1D           |      |                       | 5D           |        |             | 9D           |        | OSC GO EN | DD           | RW       |

|                    | 1E           |      |                       | 5E           |        |             | 9E           |        | OSC_CR4   | DE           | RW       |

|                    | 1F           |      |                       | 5F           |        |             | 9F           |        | OSC CR3   | DF           | RW       |

| DBB00FN            | 20           | RW   | CLK CR0               | 60           | RW     |             | A0           |        | OSC_CR0   | E0           | RW       |

| DBB00IN            | 21           | RW   | CLK CR1               | 61           | RW     |             | A1           |        | OSC_CR1   | E1           | RW       |

| DBB00OU            | 22           | RW   | ABF CR0               | 62           | RW     |             | A2           |        | OSC CR2   | E2           | RW       |

| DDD0000            | 23           | 1.00 | AMD CR0               | 63           | RW     |             | A3           |        | VLT_CR    | E3           | RW       |

| DBB01FN            | 20           | RW   |                       | 64           | 1.00   |             | A4           |        | VLT_CMP   | E4           | R        |

| DBB01IN            | 25           | RW   |                       | 65           |        |             | A5           |        |           | E5           |          |

| DBB011N<br>DBB01OU | 25           | RW   | AMD CR1               | 66           | RW     |             | AS           |        |           | E5<br>E6     |          |

| DBB0100            | 20           |      | AMD_CR1               | 67           | RW     |             | A0<br>A7     |        |           | E7           |          |

| DCB02FN            | 27           |      | ALI_CRU               | 68           | RW     |             | A7<br>A8     |        |           |              | 14/      |

|                    |              | RW   |                       |              |        | SARADC_TRS  |              | RW     | IMO_TR    | E8           | W        |

| DCB02IN            | 29           | RW   |                       | 69           |        | SARADC_TRCL | A9           | RW     | ILO_TR    | E9           | W        |

| DCB02OU            | 2A           | RW   |                       | 6A           |        | SARADC_TRCH | AA           | RW     | BDG_TR    | EA           | RW       |

| DODOOFUL           | 2B           | 514  | 7140.000              | 6B           |        | SARADC_CR2  | AB           | #      | ECO_TR    | EB           | W        |

| DCB03FN            | 2C           | RW   | TMP_DR0               | 6C           | RW     | SARADC_LCR  | AC           | RW     |           | EC           |          |

| DCB03IN            | 2D           | RW   | TMP_DR1               | 6D           | RW     |             | AD           |        |           | ED           |          |

| DCB03OU            | 2E           | RW   | TMP_DR2               | 6E           | RW     |             | AE           |        |           | EE           |          |

|                    | 2F           |      | TMP_DR3               | 6F           | RW     |             | AF           |        |           | EF           |          |

|                    | 30           |      | ACB00CR3              | 70           | RW     | RDIORI      | BO           | RW     |           | F0           |          |

|                    | 31           |      | ACB00CR0              | 71           | RW     | RDI0SYN     | B1           | RW     |           | F1           |          |

|                    | 32           |      | ACB00CR1              | 72           | RW     | RDI0IS      | B2           | RW     |           | F2           |          |

|                    | 33           |      | ACB00CR2              | 73           | RW     | RDI0LT0     | B3           | RW     |           | F3           |          |

|                    | 34           |      | ACB01CR3              | 74           | RW     | RDI0LT1     | B4           | RW     |           | F4           |          |

|                    | 35           |      | ACB01CR0              | 75           | RW     | RDI0RO0     | B5           | RW     |           | F5           |          |

|                    | 36           |      | ACB01CR1              | 76           | RW     | RDI0RO1     | B6           | RW     |           | F6           |          |

|                    | 37           |      | ACB01CR2 *            | 77           | RW     |             | B7           |        | CPU_F     | F7           | RL       |

|                    | 38           |      |                       | 78           |        |             | B8           |        |           | F8           |          |

|                    | 39           |      |                       | 79           |        |             | B9           |        |           | F9           |          |

|                    |              |      |                       | 7A           |        |             | BA           |        | FLS PR1   | FA           | RW       |

|                    | 3A           |      |                       |              |        |             |              |        |           |              | · · ·    |

|                    |              |      |                       |              |        |             | BB           |        |           | FB           |          |

|                    | 3B           |      |                       | 7B           |        |             | BB<br>BC     |        |           | FB<br>FC     |          |

|                    | 3B<br>3C     |      |                       | 7B<br>7C     |        |             | BC           |        |           | FC           |          |

|                    | 3B           |      |                       | 7B           |        |             |              |        | CPU SCR1  |              | #        |

Gray fields are reserved. # Access is bit specific.

# DC Operational Amplifier Specifications

The following table lists the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40^{\circ}C \le T_A \le 85^{\circ}C$ , or 3.0 V to 3.6 V and  $-40^{\circ}C \le T_A \le 85^{\circ}C$ , respectively. Typical parameters apply to 5 V and 3.3 V at 25°C and are for design guidance only.

The Operational amplifier is a component of both the analog continuous time PSoC blocks and the analog switched cap PSoC blocks. The guaranteed specifications are measured in the analog continuous time PSoC block. Typical parameters apply to 5 V at 25°C and are for design guidance only.

| Table 11 | 5-V DC O | perational Am | olifier S | necifications |

|----------|----------|---------------|-----------|---------------|

|          | J-V DC C |               |           |               |

| Symbol               | Description                                                                                                                                                                                                                       | Min                                                | Тур                                | Max                                      | Units                | Notes                                                                                                                                                                                                          |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------------------------|------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>OSOA</sub>    | Input offset voltage (absolute value)<br>Power = low, Opamp bias = high<br>Power = medium, Opamp bias = high<br>Power = high, Opamp bias = high                                                                                   | -<br>-<br>-                                        | 1.6<br>1.3<br>1.2                  | 10<br>8<br>7.5                           | mV<br>mV<br>mV       |                                                                                                                                                                                                                |

| TCV <sub>OSOA</sub>  | Average input offset voltage drift                                                                                                                                                                                                | _                                                  | 7.0                                | 35.0                                     | μV/°C                |                                                                                                                                                                                                                |

| I <sub>EBOA</sub>    | Input leakage current (Port 0 analog pins)                                                                                                                                                                                        | -                                                  | 20                                 | -                                        | pА                   | Gross tested to 1 µA                                                                                                                                                                                           |

| C <sub>INOA</sub>    | Input capacitance (Port 0 analog pins)                                                                                                                                                                                            | -                                                  | 4.5                                | 9.5                                      | pF                   | Package and pin dependent.<br>Temp = 25°C                                                                                                                                                                      |

| V <sub>CMOA</sub>    | Common mode voltage range<br>Common mode voltage range (high power or high<br>opamp bias)                                                                                                                                         | 0.0<br>0.5                                         |                                    | V <sub>DD</sub><br>V <sub>DD</sub> – 0.5 | V<br>V               | The common-mode input<br>voltage range is measured<br>through an analog output<br>buffer. The specification<br>includes the limitations<br>imposed by the character-<br>istics of the analog output<br>buffer. |

| G <sub>OLOA</sub>    | Open loop gain<br>Power = low, Opamp bias = high<br>Power = medium, Opamp bias = high<br>Power = high, Opamp bias = high                                                                                                          | 60<br>60<br>80                                     | _<br>_<br>_                        | -<br>-<br>-                              | dB<br>-<br>-         | Specification is applicable at<br>high power. For all other bias<br>modes (except high power,<br>high opamp bias), minimum is<br>60 dB.                                                                        |

| V <sub>OHIGHOA</sub> | High output voltage swing (internal signals)<br>Power = low, Opamp bias = high<br>Power = medium, Opamp bias = high<br>Power = high, Opamp bias = high                                                                            | $V_{DD} - 0.2$<br>$V_{DD} - 0.2$<br>$V_{DD} - 0.5$ | _<br>_<br>_                        | -<br>-<br>-                              | V<br>V<br>V          |                                                                                                                                                                                                                |

| Volowoa              | Low output voltage swing (internal signals)<br>Power = low, Opamp bias = high<br>Power = medium, Opamp bias = high<br>Power = high, Opamp bias = high                                                                             | -<br>-<br>-                                        | _<br>_<br>_                        | 0.2<br>0.2<br>0.5                        | V<br>V<br>V          |                                                                                                                                                                                                                |

| I <sub>SOA</sub>     | Supply current (including associated AGND buffer)<br>Power = low, Opamp bias = high<br>Power = medium, Opamp bias = low<br>Power = medium, Opamp bias = high<br>Power = high, Opamp bias = low<br>Power = high, Opamp bias = high | -<br>-<br>-<br>-<br>-                              | 300<br>600<br>1200<br>2400<br>4600 | 400<br>800<br>1600<br>3200<br>6400       | μΑ<br>μΑ<br>μΑ<br>μΑ |                                                                                                                                                                                                                |

| PSRR <sub>OA</sub>   | Supply voltage rejection ratio                                                                                                                                                                                                    | 52                                                 | 80                                 | -                                        | dB                   | $\begin{array}{l} V_{ss} \leq VIN \leq (V_{DD} - 2.25) \text{ or} \\ (V_{DD} - 1.25V) \leq VIN \leq V_{DD} \end{array}$                                                                                        |

### Table 12. 3.3-V DC Operational Amplifier Specifications

| Symbol               | Description                                                                                                                                                                                                                                                           | Min                                                | Тур                                    | Max                                    | Units                      | Notes                                                                                                                                                                                                     |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------|----------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>OSOA</sub>    | Input offset voltage (absolute value)<br>Power = low, Opamp bias = high<br>Power = medium, Opamp bias = high<br>Power = high, Opamp bias = high                                                                                                                       | -<br>-<br>-                                        | 1.65<br>1.32<br>-                      | 10<br>8<br>-                           | mV<br>mV<br>mV             | Power = high, Opamp bias = high setting is not allowed for $3.3 V V_{DD}$ operation.                                                                                                                      |

| TCV <sub>OSOA</sub>  | Average input offset voltage drift                                                                                                                                                                                                                                    | -                                                  | 7.0                                    | 35.0                                   | µV/°C                      |                                                                                                                                                                                                           |

| I <sub>EBOA</sub>    | Input leakage current (port 0 analog pins)                                                                                                                                                                                                                            | -                                                  | 20                                     | -                                      | pА                         | Gross tested to 1 µA                                                                                                                                                                                      |

| C <sub>INOA</sub>    | Input capacitance (port 0 analog pins)                                                                                                                                                                                                                                | -                                                  | 4.5                                    | 9.5                                    | pF                         | Package and pin dependent.<br>Temp = 25 °C                                                                                                                                                                |

| V <sub>CMOA</sub>    | Common mode voltage range                                                                                                                                                                                                                                             | 0.2                                                | -                                      | V <sub>DD</sub> – 0.2                  | V                          | The common-mode input voltage<br>range is measured through an<br>analog output buffer. The<br>specification includes the<br>limitations imposed by the<br>characteristics of the analog<br>output buffer. |

| G <sub>OLOA</sub>    | Open loop gain<br>Power = low, ppamp Opamp bias = low<br>Power = medium, Opamp bias = low<br>Power = high, Opamp bias = low                                                                                                                                           | 60<br>60<br>80                                     |                                        | -<br>-<br>-                            | dB<br>dB<br>dB             | Specification is applicable at low<br>Opamp bias. For high Opamp bias<br>mode (except high power, high<br>Opamp bias), minimum is 60 dB.                                                                  |

| V <sub>OHIGHOA</sub> | High output voltage swing (internal signals)<br>Power = low, Opamp bias = low<br>Power = medium, Opamp bias = low<br>Power = high, Opamp bias = low                                                                                                                   | $V_{DD} - 0.2$<br>$V_{DD} - 0.2$<br>$V_{DD} - 0.2$ |                                        | -<br>-<br>-                            | V<br>V<br>V                | Power = high, Opamp bias = high setting is not allowed for $3.3 \text{ V} \text{V}_{\text{DD}}$ operation.                                                                                                |

| V <sub>OLOWOA</sub>  | Low output voltage swing (internal signals)<br>Power = low, ppamp Opamp bias = low<br>Power = medium, Opamp bias = low<br>Power = high, Opamp bias = low                                                                                                              |                                                    |                                        | 0.2<br>0.2<br>0.2                      | V<br>V<br>V                | Power = high, Opamp bias = high setting is not allowed for $3.3 \text{ V} \text{V}_{\text{DD}}$ operation.                                                                                                |

| I <sub>SOA</sub>     | Supply current (including associated AGND<br>buffer)<br>Power = low, Opamp bias = low<br>Power = low, Opamp bias = high<br>Power = medium, Opamp bias = low<br>Power = medium, Opamp bias = high<br>Power = high, Opamp bias = low<br>Power = high, Opamp bias = high |                                                    | 150<br>300<br>600<br>1200<br>2400<br>- | 200<br>400<br>800<br>1600<br>3200<br>- | mA<br>mA<br>mA<br>mA<br>mA | Power = high, Opamp bias = high<br>setting is not allowed for 3.3 V V <sub>DD</sub><br>operation.                                                                                                         |

| PSRR <sub>OA</sub>   | Supply voltage rejection ratio                                                                                                                                                                                                                                        | 64                                                 | 80                                     | -                                      | dB                         | $V_{SS} \pm V_{IN} \pm (V_{DD} - 2.25) \text{ or} \\ (V_{DD} - 1.25 \text{ V}) \pm V_{IN} \pm V_{DD}$                                                                                                     |

#### DC Low-Power Comparator Specifications

The following table lists the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40 \text{ °C} \le T_A \le 85 \text{ °C}$ , or 3.0 V to 3.6 V and  $-40 \text{ °C} \le T_A \le 85 \text{ °C}$ , respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

#### Table 13. DC Low-Power Comparator Specifications

| Symbol              | Description                                        | Min | Тур | Мах                   | Units |

|---------------------|----------------------------------------------------|-----|-----|-----------------------|-------|

| V <sub>REFLPC</sub> | Low power comparator (LPC) reference voltage range | 0.2 | -   | V <sub>DD</sub> – 1.0 | V     |

| I <sub>SLPC</sub>   | LPC supply current                                 | -   | 10  | 40                    | μA    |

| V <sub>OSLPC</sub>  | LPC voltage offset                                 | _   | 2.5 | 30                    | mV    |

| Table 16. 5-V DC Analog Reference Specifications (continued) | Table 16. | 5-V DC Analog | <b>Reference Specifications</b> | (continued) |

|--------------------------------------------------------------|-----------|---------------|---------------------------------|-------------|

|--------------------------------------------------------------|-----------|---------------|---------------------------------|-------------|

| Reference<br>ARF_CR<br>[5:3] | Reference Power<br>Settings              | Symbol             | Reference | Description     | Min             | Тур                     | Мах                     | Units |

|------------------------------|------------------------------------------|--------------------|-----------|-----------------|-----------------|-------------------------|-------------------------|-------|

| 0b110                        | RefPower = high                          | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap     | 2.512           | 2.594                   | 2.654                   | V     |

|                              | Opamp bias = high                        | V <sub>AGND</sub>  | AGND      | Bandgap         | 1.250           | 1.303                   | 1.346                   | V     |

|                              |                                          | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> + 0.011 | V <sub>SS</sub> + 0.027 | V     |

|                              | RefPower = high                          | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap     | 2.515           | 2.592                   | 2.654                   | V     |

|                              | Opamp bias = low                         | V <sub>AGND</sub>  | AGND      | Bandgap         | 1.253           | 1.301                   | 1.340                   | V     |

|                              |                                          | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> + 0.006 | V <sub>SS</sub> + 0.02  | V     |

|                              | RefPower =                               | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap     | 2.518           | 2.593                   | 2.651                   | V     |

|                              | medium<br>Opamp bias = high              | V <sub>AGND</sub>  | AGND      | Bandgap         | 1.254           | 1.301                   | 1.338                   | V     |

|                              |                                          | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> + 0.004 | V <sub>SS</sub> + 0.017 | V     |

|                              | RefPower =<br>medium<br>Opamp bias = low | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap     | 2.517           | 2.594                   | 2.650                   | V     |

|                              |                                          | V <sub>AGND</sub>  | AGND      | Bandgap         | 1.255           | 1.300                   | 1.337                   | V     |

|                              |                                          | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> + 0.003 | V <sub>SS</sub> + 0.015 | V     |

| 0b111                        | RefPower = high                          | V <sub>REFHI</sub> | Ref High  | 3.2 × Bandgap   | 4.011           | 4.143                   | 4.203                   | V     |

|                              | Opamp bias = high                        | V <sub>AGND</sub>  | AGND      | 1.6 × Bandgap   | 2.020           | 2.075                   | 2.118                   | V     |

|                              |                                          | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> + 0.011 | V <sub>SS</sub> + 0.026 | V     |

|                              | RefPower = high                          | V <sub>REFHI</sub> | Ref High  | 3.2 × Bandgap   | 4.022           | 4.138                   | 4.203                   | V     |

|                              | Opamp bias = low                         | V <sub>AGND</sub>  | AGND      | 1.6 × Bandgap   | 2.023           | 2.075                   | 2.114                   | V     |

|                              |                                          | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> + 0.006 | V <sub>SS</sub> + 0.017 | V     |

|                              | RefPower =                               | V <sub>REFHI</sub> | Ref High  | 3.2 × Bandgap   | 4.026           | 4.141                   | 4.207                   | V     |

|                              | medium<br>Opamp bias = high              | V <sub>AGND</sub>  | AGND      | 1.6 × Bandgap   | 2.024           | 2.075                   | 2.114                   | V     |

|                              |                                          | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> + 0.004 | V <sub>SS</sub> + 0.015 | V     |

|                              | RefPower =                               | V <sub>REFHI</sub> | Ref High  | 3.2 × Bandgap   | 4.030           | 4.143                   | 4.206                   | V     |

|                              | medium<br>Opamp bias = low               | V <sub>AGND</sub>  | AGND      | 1.6 × Bandgap   | 2.024           | 2.076                   | 2.112                   | V     |

|                              |                                          | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> + 0.003 | V <sub>SS</sub> + 0.013 | V     |

# Table 17. 3.3-V DC Analog Reference Specifications

| Reference<br>ARF_CR<br>[5:3] | Reference Power<br>Settings               | Symbol             | Reference | Description                                                | Min                           | Тур                           | Max                           | Units |

|------------------------------|-------------------------------------------|--------------------|-----------|------------------------------------------------------------|-------------------------------|-------------------------------|-------------------------------|-------|

| 0b000                        | RefPower = high<br>Opamp bias = high      | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub> /2 + Bandgap                               | V <sub>DD</sub> /2 +<br>1.170 | V <sub>DD</sub> /2 +<br>1.288 | V <sub>DD</sub> /2 +<br>1.376 | V     |

|                              |                                           | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                         | V <sub>DD</sub> /2 –<br>0.098 | V <sub>DD</sub> /2 +<br>0.003 | V <sub>DD</sub> /2 +<br>0.097 | V     |

|                              |                                           | V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – Bandgap                               | V <sub>DD</sub> /2 –<br>1.386 | V <sub>DD</sub> /2 –<br>1.287 | V <sub>DD</sub> /2 –<br>1.169 | V     |

|                              | RefPower = high<br>Opamp bias = low       | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub> /2 + Bandgap                               | V <sub>DD</sub> /2 +<br>1.210 | V <sub>DD</sub> /2 +<br>1.290 | V <sub>DD</sub> /2 +<br>1.355 | V     |

|                              |                                           | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                         | V <sub>DD</sub> /2 –<br>0.055 | V <sub>DD</sub> /2 +<br>0.001 | V <sub>DD</sub> /2 +<br>0.054 | V     |

|                              |                                           | V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – Bandgap                               | V <sub>DD</sub> /2 –<br>1.359 | V <sub>DD</sub> /2 –<br>1.292 | V <sub>DD</sub> /2 –<br>1.214 | V     |

|                              | RefPower =<br>medium<br>Opamp bias = high | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub> /2 + Bandgap                               | V <sub>DD</sub> /2 +<br>1.198 | V <sub>DD</sub> /2 +<br>1.292 | V <sub>DD</sub> /2 +<br>1.368 | V     |

|                              |                                           | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                         | V <sub>DD</sub> /2 –<br>0.041 | V <sub>DD</sub> /2            | V <sub>DD</sub> /2 + 0.04     | V     |

|                              |                                           | V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – Bandgap                               | V <sub>DD</sub> /2 –<br>1.362 | V <sub>DD</sub> /2 –<br>1.295 | V <sub>DD</sub> /2 –<br>1.220 | V     |

|                              | RefPower =<br>medium<br>Opamp bias = low  | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub> /2 + Bandgap                               | V <sub>DD</sub> /2 +<br>1.202 | V <sub>DD</sub> /2 +<br>1.292 | V <sub>DD</sub> /2 +<br>1.364 | V     |

|                              |                                           | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                         | V <sub>DD</sub> /2 –<br>0.033 | V <sub>DD</sub> /2            | V <sub>DD</sub> /2 +<br>0.030 | V     |

|                              |                                           | V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – Bandgap                               | V <sub>DD</sub> /2 –<br>1.364 | V <sub>DD</sub> /2 –<br>1.297 | V <sub>DD</sub> /2 –<br>1.222 | V     |

| 0b001                        | RefPower = high<br>Opamp bias = high      | V <sub>REFHI</sub> | Ref High  | P2[4]+P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] + P2[6]<br>- 0.072      | P2[4] + P2[6]<br>- 0.017      | P2[4] + P2[6]<br>+ 0.041      | V     |

|                              |                                           | V <sub>AGND</sub>  | AGND      | P2[4]                                                      | P2[4]                         | P2[4]                         | P2[4]                         | -     |

|                              |                                           | V <sub>REFLO</sub> | Ref Low   | P2[4]–P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] – P2[6]<br>– 0.029      | P2[4] – P2[6]<br>+ 0.010      | P2[4] – P2[6]<br>+ 0.048      | V     |

|                              | RefPower = high<br>Opamp bias = low       | V <sub>REFHI</sub> | Ref High  | P2[4]+P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] + P2[6]<br>- 0.066      | P2[4] + P2[6]<br>- 0.010      | P2[4] + P2[6]<br>+ 0.043      | V     |

|                              |                                           | V <sub>AGND</sub>  | AGND      | P2[4]                                                      | P2[4]                         | P2[4]                         | P2[4]                         | -     |

|                              |                                           | V <sub>REFLO</sub> | Ref Low   | P2[4]–P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] – P2[6]<br>– 0.024      | P2[4] – P2[6]<br>+ 0.004      | P2[4] – P2[6]<br>+ 0.034      | V     |

|                              | RefPower =<br>medium                      | V <sub>REFHI</sub> | Ref High  | P2[4]+P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] + P2[6]<br>- 0.073      | P2[4] + P2[6]<br>- 0.007      | P2[4] + P2[6]<br>+ 0.053      | V     |

|                              | Opamp bias = high                         | V <sub>AGND</sub>  | AGND      | P2[4]                                                      | P2[4]                         | P2[4]                         | P2[4]                         | -     |

|                              |                                           | V <sub>REFLO</sub> | Ref Low   | P2[4]–P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] – P2[6]<br>– 0.028      | P2[4] – P2[6]<br>+ 0.002      | P2[4] – P2[6]<br>+ 0.033      | V     |

|                              | RefPower =<br>medium                      | V <sub>REFHI</sub> | Ref High  | P2[4]+P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] + P2[6]<br>- 0.073      | P2[4] + P2[6]<br>- 0.006      | P2[4] + P2[6]<br>+ 0.056      | V     |

|                              | Opamp bias = low                          | V <sub>AGND</sub>  | AGND      | P2[4]                                                      | P2[4]                         | P2[4]                         | P2[4]                         | -     |

|                              |                                           | V <sub>REFLO</sub> | Ref Low   | P2[4]–P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] – P2[6]<br>– 0.030      | P2[4] – P2[6]                 | P2[4] – P2[6]<br>+ 0.032      | V     |

| Reference<br>ARF_CR<br>[5:3] | Reference Power<br>Settings                   | Symbol             | Reference | Description     | Min             | Тур                     | Мах                     | Units |

|------------------------------|-----------------------------------------------|--------------------|-----------|-----------------|-----------------|-------------------------|-------------------------|-------|

| 0b110                        | RefPower = high                               | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap     | 2.460           | 2.594                   | 2.695                   | V     |

|                              | Opamp bias = high                             | V <sub>AGND</sub>  | AGND      | Bandgap         | 1.257           | 1.302                   | 1.335                   | V     |

|                              |                                               | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> + 0.01  | V <sub>SS</sub> + 0.029 | V     |

|                              | RefPower = high<br>Opamp bias = low           | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap     | 2.462           | 2.592                   | 2.692                   | V     |

|                              |                                               | V <sub>AGND</sub>  | AGND      | Bandgap         | 1.256           | 1.301                   | 1.332                   | V     |

|                              |                                               | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> + 0.005 | V <sub>SS</sub> + 0.017 | V     |

|                              | RefPower =<br>medium<br>Opamp bias = high     | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap     | 2.473           | 2.593                   | 2.682                   | V     |

|                              |                                               | V <sub>AGND</sub>  | AGND      | Bandgap         | 1.257           | 1.301                   | 1.330                   | V     |

|                              | 5                                             | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> + 0.003 | V <sub>SS</sub> + 0.014 | V     |

|                              | RefPower =                                    | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap     | 2.470           | 2.594                   | 2.685                   | V     |

|                              | medium<br>Opamp bias = low                    | V <sub>AGND</sub>  | AGND      | Bandgap         | 1.256           | 1.300                   | 1.332                   | V     |

|                              | - F F                                         | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> + 0.002 | V <sub>SS</sub> + 0.012 | V     |

| 0b111                        | All power settings<br>Not allowed at 3.3<br>V | -                  | -         | -               | -               | -                       | _                       | -     |

# Table 17. 3.3-V DC Analog Reference Specifications (continued)

# DC Analog PSoC Block Specifications

The following table lists the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 3.0 V to 3.6 V and–40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

#### Table 18. DC Analog PSoC Block Specifications

| Symbol          | Description                           | Min | Тур               | Мах | Units |

|-----------------|---------------------------------------|-----|-------------------|-----|-------|

| R <sub>CT</sub> | Resistor unit value (continuous time) | -   | 12.2              | -   | kΩ    |

| C <sub>SC</sub> | Capacitor unit value (switch cap)     | -   | 80 <sup>[9]</sup> | -   | fF    |

DC POR and LVD Specifications

The following table lists the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 3.0 V to 3.6 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

**Note** The bits PORLEV and VM in the following table refer to bits in the VLT\_CR register. See the *PSoC Mixed-Signal Array Technical Reference Manual* for more information on the VLT\_CR register.

#### Table 19. DC POR and LVD Specifications

| Symbol                                                                                                          | Description                                                                                                                                          | Min                                                  | Тур                                                  | Max                                                                  | Units                 | Notes                                                                                         |

|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------|

| V <sub>PPOR1</sub><br>V <sub>PPOR2</sub>                                                                        | V <sub>DD</sub> value for PPOR trip<br>PORLEV[1:0] = 01b<br>PORLEV[1:0] = 10b                                                                        | _                                                    | 2.82<br>4.55                                         | 2.95<br>4.70                                                         | V<br>V                | V <sub>DD</sub> must be greater than or equal to 2.5 V during startup or reset from watchdog. |

| $\begin{array}{c} V_{LVD1} \\ V_{LVD2} \\ V_{LVD3} \\ V_{LVD4} \\ V_{LVD5} \\ V_{LVD6} \\ V_{LVD7} \end{array}$ | Vdd value for LVD trip<br>VM[2:0] = 001b<br>VM[2:0] = 010b<br>VM[2:0] = 011b<br>VM[2:0] = 100b<br>VM[2:0] = 101b<br>VM[2:0] = 110b<br>VM[2:0] = 111b | 2.85<br>2.95<br>3.06<br>4.37<br>4.50<br>4.62<br>4.71 | 2.92<br>3.02<br>3.13<br>4.48<br>4.64<br>4.73<br>4.81 | 2.99 <sup>[10]</sup><br>3.09<br>3.20<br>4.55<br>4.75<br>4.83<br>4.95 | V<br>V<br>V<br>V<br>V |                                                                                               |

#### Notes

9. C<sub>SC</sub> is a design guarantee parameter, not tested value

10. Always greater than 50 mV above V<sub>PPOR</sub> (PORLEV=01) for falling supply.

### DC Programming Specifications

The following table lists the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40^{\circ}C \le T_A \le 85^{\circ}C$ , or 3.0 V to 3.6 V and  $-40^{\circ}C \le T_A \le 85^{\circ}C$ , respectively. Typical parameters apply to 5 V and 3.3 V at 25°C and are for design guidance only.

#### Table 20. DC Programming Specifications

| Symbol                | Description                                                                     | Min                   | Тур | Max                    | Units | Notes                                                                                         |

|-----------------------|---------------------------------------------------------------------------------|-----------------------|-----|------------------------|-------|-----------------------------------------------------------------------------------------------|

| V <sub>DDP</sub>      | V <sub>DD</sub> for programming and erase                                       | 4.5                   | 5   | 5.5                    | V     | This specification applies to<br>the functional requirements<br>of external programmer tools  |

| V <sub>DDLV</sub>     | Low V <sub>DD</sub> for verify                                                  | 3.0                   | 3.1 | 3.2                    | V     | This specification applies to<br>the functional requirements<br>of external programmer tools  |

| V <sub>DDHV</sub>     | High V <sub>DD</sub> for verify                                                 | 5.1                   | 5.2 | 5.3                    | V     | This specification applies to<br>the functional requirements<br>of external programmer tools  |

| V <sub>DDIWRITE</sub> | Supply voltage for flash write operation                                        | 3.0                   | _   | 5.25                   | V     | This specification applies to<br>this device when it is<br>executing internal flash<br>writes |

| I <sub>DDP</sub>      | Supply current during programming or verify                                     | -                     | 5   | 25                     | mA    |                                                                                               |

| V <sub>ILP</sub>      | Input low voltage during programming or verify                                  | -                     | —   | 0.8                    | V     |                                                                                               |

| V <sub>IHP</sub>      | Input high voltage during programming or verify                                 | 2.1                   | -   | -                      | V     |                                                                                               |

| I <sub>ILP</sub>      | Input current when applying vilp to P1[0] or P1[1] during programming or verify | _                     | -   | 0.2                    | mA    | Driving internal pull down resistor                                                           |

| I <sub>IHP</sub>      | Input current when applying vihp to P1[0] or P1[1] during programming or verify | -                     | _   | 1.5                    | mA    | Driving internal pull down resistor                                                           |

| V <sub>OLV</sub>      | Output low voltage during programming or verify                                 | _                     | -   | V <sub>SS</sub> + 0.75 | V     |                                                                                               |

| V <sub>OHV</sub>      | Output high voltage during programming or verify                                | V <sub>DD</sub> - 1.0 | -   | V <sub>DD</sub>        | V     |                                                                                               |

| Flash <sub>ENPB</sub> | Flash endurance (per block)                                                     | 50,000                | -   | -                      | -     | Erase/write cycles per block                                                                  |

| Flash <sub>ENT</sub>  | Flash endurance (total) <sup>[11]</sup>                                         | 1,800,000             | -   | _                      | _     | Erase/write cycles                                                                            |

| Flash <sub>DR</sub>   | Flash data retention                                                            | 10                    | -   | -                      | Years |                                                                                               |

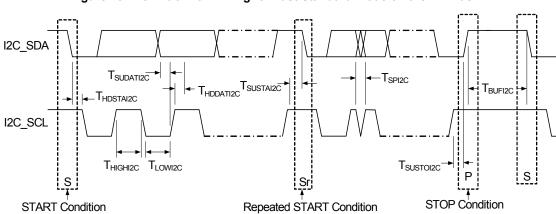

# DC I<sup>2</sup>C Specifications

The following table lists the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 3.0 V to 3.6 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters apply to 5 V and 3.3 V at 25°C and are for design guidance only.

### Table 21. DC I<sup>2</sup>C Specifications<sup>[12]</sup>

| Symbol             | Description      | Min                 | Тур | Max                  | Units | Notes                            |

|--------------------|------------------|---------------------|-----|----------------------|-------|----------------------------------|

| V <sub>ILI2C</sub> | Input low level  | -                   | -   | $0.3 \times V_{DD}$  | V     | $3.0~V \leq V_{DD} \leq 3.6~V$   |

|                    |                  | -                   | -   | $0.25 \times V_{DD}$ | V     | $4.75~V \leq V_{DD} \leq 5.25~V$ |

| V <sub>IHI2C</sub> | Input high level | $0.7 \times V_{DD}$ | -   | _                    | V     | $3.0~V \leq V_{DD} \leq 5.25~V$  |

#### Notes

A maximum of 36 x 50,000 block endurance cycles is allowed. This may be balanced between operations on 36x1 blocks of 50,000 maximum cycles each, 36x2 blocks of 25,000 maximum cycles each, or 36x4 blocks of 12,500 maximum cycles each (to limit the total number of cycles to 36x50,000 and that no single block ever sees more than 50,000 cycles). For the full industrial range, the user must employ a temperature sensor user module (FlashTemp) and feed the result to the temperature argument before writing. Refer to 0xthe Flash APIs Application Note AN2015 at http://www.cypress.com under Application Notes for more information.

All GPIOs meet the DC GPIO V<sub>IL</sub> and V<sub>IH</sub> specifications found in the DC GPIO Specifications sections. The I<sup>2</sup>C GPIO pins also meet the above specs.

# SAR8 ADC DC Specifications

The following table lists the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40^{\circ}C \le T_A \le 85^{\circ}C$ , or 3.0 V to 3.6 V and  $-40^{\circ}C \le T_A \le 85^{\circ}C$ , respectively. Typical parameters apply to 5 V and 3.3 V at 25°C and are for design guidance only.

### Table 22. SAR8 ADC DC Specifications

| Symbol                    | Description                                                             | Min                  | Тур | Max  | Units | Notes                                                                                                                                                                                                 |

|---------------------------|-------------------------------------------------------------------------|----------------------|-----|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VADCVREF                  | Reference voltage at pin P3[0] when configured as ADC reference voltage | 3.0                  | _   | 5.25 | V     | The voltage level at P3[0]<br>(when configured as ADC<br>reference voltage) must<br>always be maintained to be<br>less than chip supply voltage<br>level on $V_{DD}$ pin.<br>$V_{ADCVREF} < V_{DD}$ . |

| I <sub>ADCVREF</sub>      | Current when P3[0] is configured as ADC $V_{REF}$                       | 3                    | -   | -    | mA    |                                                                                                                                                                                                       |

| INL                       | Integral non-linearity                                                  | -1.5                 | -   | +1.5 | LSB   |                                                                                                                                                                                                       |

| INL<br>(limited<br>range) | Integral non-linearity accommodating a shift in the offset at 0x80      | -1.2 <sup>[12]</sup> | -   | +1.2 | LSB   | The maximum LSB is over a sub-range not exceeding 1/16 of the full-scale range. 0x7F and 0x80 points specs are excluded here                                                                          |

| DNL                       | Differential non-linearity                                              | -2.3                 | -   | +2.3 | LSB   | ADC conversion is<br>monotonic over full range                                                                                                                                                        |

| DNL<br>(limited<br>range) | Differential non-linearity excluding 0x7F-0x80 transition               | -1                   | -   | +1   | LSB   | ADC conversion is<br>monotonic over full range.<br>0x7F to 0x80 transition specs<br>are excluded here.                                                                                                |

Note

12. SAR converters require a stable input voltage during the sampling period. If the voltage into the SAR8 changes by more than 1 LSB during the sampling period then the accuracy specifications may not be met

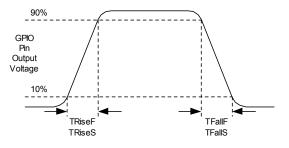

# AC GPIO Specifications

The following table lists the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40^{\circ}C \le T_A \le 85^{\circ}C$ , or 3.0 V to 3.6 V and  $-40^{\circ}C \le T_A \le 85^{\circ}C$ , respectively. Typical parameters apply to 5 V and 3.3 V at 25°C and are for design guidance only.

Table 24. 5-V and 3.3-V AC GPIO Specifications

| Symbol            | Description                                  | Min | Тур | Max  | Units | Notes                                        |

|-------------------|----------------------------------------------|-----|-----|------|-------|----------------------------------------------|

| F <sub>GPIO</sub> | GPIO operating frequency                     | 0   | -   | 12.3 | MHz   | Normal strong mode                           |

| TRiseF            | Rise time, normal strong mode, cload = 50 pF | 3   | -   | 18   | ns    | V <sub>DD</sub> = 4.5 V to 5.25 V, 10% - 90% |

| TFallF            | Fall time, normal strong mode, cload = 50 pF | 2   | -   | 18   | ns    | V <sub>DD</sub> = 4.5 V to 5.25 V, 10% - 90% |

| TRiseS            | Rise time, slow strong mode, cload = 50 pF   | 10  | 27  | -    | ns    | V <sub>DD</sub> = 3 V to 5.25 V, 10% - 90%   |

| TFallS            | Fall time, slow strong mode, cload = 50 pF   | 10  | 22  | -    | ns    | V <sub>DD</sub> = 3 V to 5.25 V, 10% - 90%   |

| Symbol                | Description                                                                                  | Standa | rd Mode | Fast | Mode | Units |

|-----------------------|----------------------------------------------------------------------------------------------|--------|---------|------|------|-------|

| Symbol                | Description                                                                                  | Min    | Max     | Min  | Max  | Units |

| F <sub>SCLI2C</sub>   | SCL clock frequency                                                                          | 0      | 100     | -    | -    | kHz   |