Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                         |

|----------------------------|---------------------------------------------------------|

| Product Status             | Obsolete                                                |

| Core Processor             | 8051                                                    |

| Core Size                  | 8-Bit                                                   |

| Speed                      | 24MHz                                                   |

| Connectivity               | UART/USART                                              |

| Peripherals                | WDT                                                     |

| Number of I/O              | 32                                                      |

| Program Memory Size        | 8KB (8K x 8)                                            |

| Program Memory Type        | FLASH                                                   |

| EEPROM Size                | -                                                       |

| RAM Size                   | 256 x 8                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                               |

| Data Converters            | -                                                       |

| Oscillator Type            | Internal                                                |

| Operating Temperature      | 0°C ~ 70°C (TA)                                         |

| Mounting Type              | Surface Mount                                           |

| Package / Case             | 44-LCC (J-Lead)                                         |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/at89s52-24jc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

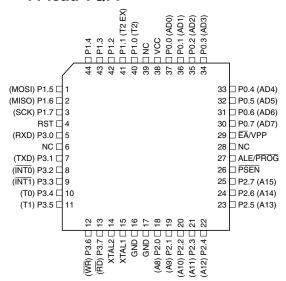

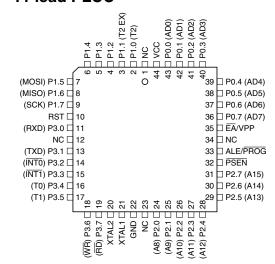

# 2. Pin Configurations

#### 2.1 40-lead PDIP

|                |    |    | 1            |

|----------------|----|----|--------------|

| (T2) P1.0 🗆    | 1  | 40 | □ vcc        |

| (T2 EX) P1.1 🗆 | 2  | 39 | DP0.0 (AD0)  |

| P1.2 🗆         | 3  | 38 | DP0.1 (AD1)  |

| P1.3 🗆         | 4  | 37 | 🗆 P0.2 (AD2) |

| P1.4 🗆         | 5  | 36 | 🗆 P0.3 (AD3) |

| (MOSI) P1.5 🗆  | 6  | 35 | 🗆 P0.4 (AD4) |

| (MISO) P1.6 🗆  | 7  | 34 | 🗆 P0.5 (AD5) |

| (SCK) P1.7 🗆   | 8  | 33 | 🗆 P0.6 (AD6) |

| RST 🗆          | 9  | 32 | 🗆 P0.7 (AD7) |

| (RXD) P3.0 🗆   | 10 | 31 | EA/VPP       |

| (TXD) P3.1 🗆   | 11 | 30 | ALE/PROG     |

| (INT0) P3.2 🗆  | 12 | 29 | D PSEN       |

| (INT1) P3.3 🗆  | 13 | 28 | 🗆 P2.7 (A15) |

| (T0) P3.4 🗆    | 14 | 27 | 🗆 P2.6 (A14) |

| (T1) P3.5 🗆    | 15 | 26 | 🗆 P2.5 (A13) |

| (WR) P3.6 🗆    | 16 | 25 | 🗆 P2.4 (A12) |

| (RD) P3.7 🗆    | 17 | 24 | 🗆 P2.3 (A11) |

| XTAL2 🗆        | 18 | 23 | 🗆 P2.2 (A10) |

| XTAL1 🗆        | 19 | 22 | 🗆 P2.1 (A9)  |

| GND 🗆          | 20 | 21 | 🗆 P2.0 (A8)  |

|                |    |    |              |

#### 2.2 44-lead TQFP

#### 2.3 44-lead PLCC

# AT89S52

2

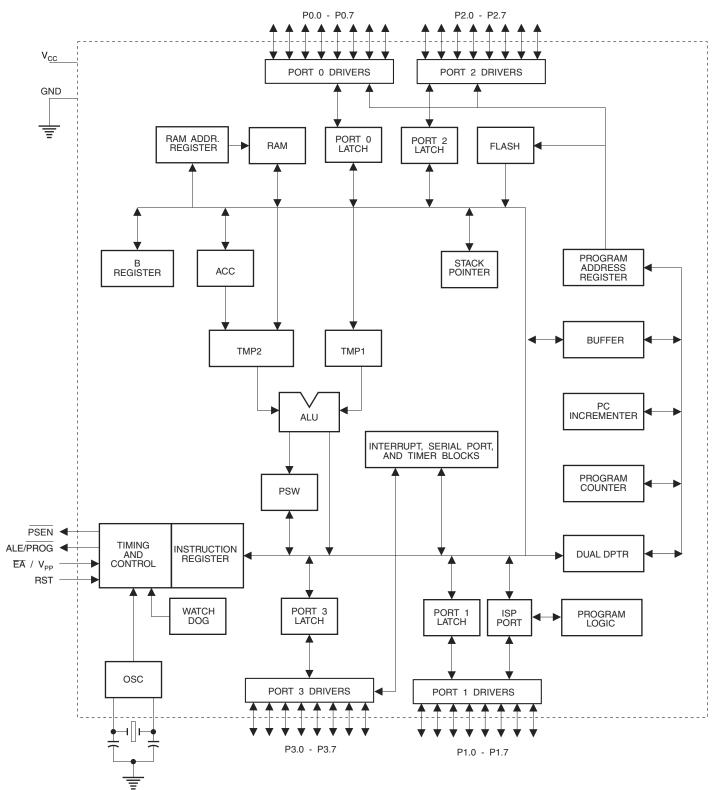

# 3. Block Diagram

### 4.6 Port 3

Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. The Port 3 output buffers can sink/source four TTL inputs. When 1s are written to Port 3 pins, they are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 3 pins that are externally being pulled low will source current ( $I_{IL}$ ) because of the pull-ups.

Port 3 receives some control signals for Flash programming and verification.

Port 3 also serves the functions of various special features of the AT89S52, as shown in the following table.

| Port Pin | Alternate Functions                    |

|----------|----------------------------------------|

| P3.0     | RXD (serial input port)                |

| P3.1     | TXD (serial output port)               |

| P3.2     | INTO (external interrupt 0)            |

| P3.3     | INT1 (external interrupt 1)            |

| P3.4     | T0 (timer 0 external input)            |

| P3.5     | T1 (timer 1 external input)            |

| P3.6     | WR (external data memory write strobe) |

| P3.7     | RD (external data memory read strobe)  |

#### 4.7 RST

Reset input. A high on this pin for two machine cycles while the oscillator is running resets the device. This pin drives high for 98 oscillator periods after the Watchdog times out. The DISRTO bit in SFR AUXR (address 8EH) can be used to disable this feature. In the default state of bit DISRTO, the RESET HIGH out feature is enabled.

### 4.8 ALE/PROG

Address Latch Enable (ALE) is an output pulse for latching the low byte of the address during accesses to external memory. This pin is also the program pulse input (PROG) during Flash programming.

In normal operation, ALE is emitted at a constant rate of 1/6 the oscillator frequency and may be used for external timing or clocking purposes. Note, however, that one ALE pulse is skipped during each access to external data memory.

If desired, ALE operation can be disabled by setting bit 0 of SFR location 8EH. With the bit set, ALE is active only during a MOVX or MOVC instruction. Otherwise, the pin is weakly pulled high. Setting the ALE-disable bit has no effect if the microcontroller is in external execution mode.

### 4.9 PSEN

Program Store Enable (PSEN) is the read strobe to external program memory.

When the AT89S52 is executing code from external program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external data memory.

#### 4.10 EA/VPP

External Access Enable.  $\overline{EA}$  must be strapped to GND in order to enable the device to fetch code from external program memory locations starting at 0000H up to FFFFH. Note, however, that if lock bit 1 is programmed,  $\overline{EA}$  will be internally latched on reset.

EA should be strapped to V<sub>CC</sub> for internal program executions.

This pin also receives the 12-volt programming enable voltage (V<sub>PP</sub>) during Flash programming.

#### 4.11 XTAL1

Input to the inverting oscillator amplifier and input to the internal clock operating circuit.

#### 4.12 XTAL2

Output from the inverting oscillator amplifier.

#### 5. Special Function Registers

A map of the on-chip memory area called the Special Function Register (SFR) space is shown in Table 5-1.

Note that not all of the addresses are occupied, and unoccupied addresses may not be implemented on the chip. Read accesses to these addresses will in general return random data, and write accesses will have an indeterminate effect.

User software should not write 1s to these unlisted locations, since they may be used in future products to invoke new features. In that case, the reset or inactive values of the new bits will always be 0.

**Timer 2 Registers:** Control and status bits are contained in registers T2CON (shown in Table 5-2) and T2MOD (shown in Table 10-2) for Timer 2. The register pair (RCAP2H, RCAP2L) are the Capture/Reload registers for Timer 2 in 16-bit capture mode or 16-bit auto-reload mode.

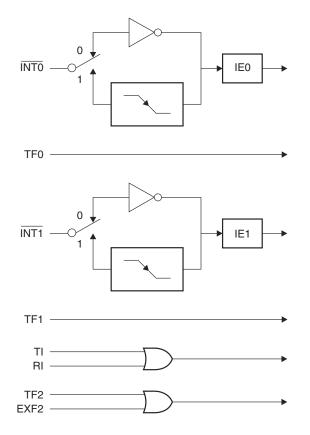

**Interrupt Registers:** The individual interrupt enable bits are in the IE register. Two priorities can be set for each of the six interrupt sources in the IP register.

6

|      | . ///000          |                   |                    | 1000               |                  |                  |                    |                  | _ |

|------|-------------------|-------------------|--------------------|--------------------|------------------|------------------|--------------------|------------------|---|

| 0F8H |                   |                   |                    |                    |                  |                  |                    |                  | 0 |

| 0F0H | B<br>00000000     |                   |                    |                    |                  |                  |                    |                  | 0 |

| 0E8H |                   |                   |                    |                    |                  |                  |                    |                  | 0 |

| 0E0H | ACC<br>00000000   |                   |                    |                    |                  |                  |                    |                  | 0 |

| 0D8H |                   |                   |                    |                    |                  |                  |                    |                  | 0 |

| 0D0H | PSW<br>00000000   |                   |                    |                    |                  |                  |                    |                  | 0 |

| 0C8H | T2CON<br>00000000 | T2MOD<br>XXXXXX00 | RCAP2L<br>00000000 | RCAP2H<br>00000000 | TL2<br>00000000  | TH2<br>00000000  |                    |                  | 0 |

| 0C0H |                   |                   |                    |                    |                  |                  |                    |                  | 0 |

| 0B8H | IP<br>XX000000    |                   |                    |                    |                  |                  |                    |                  | 0 |

| 0B0H | P3<br>11111111    |                   |                    |                    |                  |                  |                    |                  | 0 |

| 0A8H | IE<br>0X000000    |                   |                    |                    |                  |                  |                    |                  | 0 |

| 0A0H | P2<br>11111111    |                   | AUXR1<br>XXXXXXX0  |                    |                  |                  | WDTRST<br>XXXXXXXX |                  | 0 |

| 98H  | SCON<br>00000000  | SBUF<br>XXXXXXXX  |                    |                    |                  |                  |                    |                  | 9 |

| 90H  | P1<br>11111111    |                   |                    |                    |                  |                  |                    |                  | 9 |

| 88H  | TCON<br>00000000  | TMOD<br>00000000  | TL0<br>00000000    | TL1<br>00000000    | TH0<br>00000000  | TH1<br>00000000  | AUXR<br>XXX00XX0   |                  | 8 |

| 80H  | P0<br>11111111    | SP<br>00000111    | DP0L<br>00000000   | DP0H<br>00000000   | DP1L<br>00000000 | DP1H<br>00000000 |                    | PCON<br>0XXX0000 | 8 |

Table 5-1.

AT89S52 SFR Map and Reset Values

WDT overflows, it will generate an output RESET pulse at the RST pin. The RESET pulse duration is 98xTOSC, where TOSC = 1/FOSC. To make the best use of the WDT, it should be serviced in those sections of code that will periodically be executed within the time required to prevent a WDT reset.

### 7.2 WDT During Power-down and Idle

In Power-down mode the oscillator stops, which means the WDT also stops. While in Powerdown mode, the user does not need to service the WDT. There are two methods of exiting Power-down mode: by a hardware reset or via a level-activated external interrupt which is enabled prior to entering Power-down mode. When Power-down is exited with hardware reset, servicing the WDT should occur as it normally does whenever the AT89S52 is reset. Exiting Power-down with an interrupt is significantly different. The interrupt is held low long enough for the oscillator to stabilize. When the interrupt is brought high, the interrupt is serviced. To prevent the WDT from resetting the device while the interrupt pin is held low, the WDT is not started until the interrupt is pulled high. It is suggested that the WDT be reset during the interrupt service for the interrupt used to exit Power-down mode.

To ensure that the WDT does not overflow within a few states of exiting Power-down, it is best to reset the WDT just before entering Power-down mode.

Before going into the IDLE mode, the WDIDLE bit in SFR AUXR is used to determine whether the WDT continues to count if enabled. The WDT keeps counting during IDLE (WDIDLE bit = 0) as the default state. To prevent the WDT from resetting the AT89S52 while in IDLE mode, the user should always set up a timer that will periodically exit IDLE, service the WDT, and reenter IDLE mode.

With WDIDLE bit enabled, the WDT will stop to count in IDLE mode and resumes the count upon exit from IDLE.

## 8. UART

The UART in the AT89S52 operates the same way as the UART in the AT89C51 and AT89C52. For further information on the UART operation, please click on the document link below:

http://www.atmel.com/dyn/resources/prod\_documents/DOC4316.PDF

### 9. Timer 0 and 1

Timer 0 and Timer 1 in the AT89S52 operate the same way as Timer 0 and Timer 1 in the AT89C51 and AT89C52. For further information on the timers' operation, please click on the document link below:

http://www.atmel.com/dyn/resources/prod\_documents/DOC4316.PDF

## 10. Timer 2

Timer 2 is a 16-bit Timer/Counter that can operate as either a timer or an event counter. The type of operation is selected by bit  $C/\overline{12}$  in the SFR T2CON (shown in Table 5-2). Timer 2 has three operating modes: capture, auto-reload (up or down counting), and baud rate generator. The modes are selected by bits in T2CON, as shown in Table 10-1. Timer 2 consists of two 8-bit registers, TH2 and TL2. In the Timer function, the TL2 register is incremented every machine cycle. Since a machine cycle consists of 12 oscillator periods, the count rate is 1/12 of the oscillator frequency.

| RCLK +TCLK | CP/RL2 | TR2 | MODE                |

|------------|--------|-----|---------------------|

| 0          | 0      | 1   | 16-bit Auto-reload  |

| 0          | 1      | 1   | 16-bit Capture      |

| 1          | Х      | 1   | Baud Rate Generator |

| Х          | Х      | 0   | (Off)               |

Table 10-1.

Timer 2 Operating Modes

In the Counter function, the register is incremented in response to a 1-to-0 transition at its corresponding external input pin, T2. In this function, the external input is sampled during S5P2 of every machine cycle. When the samples show a high in one cycle and a low in the next cycle, the count is incremented. The new count value appears in the register during S3P1 of the cycle following the one in which the transition was detected. Since two machine cycles (24 oscillator periods) are required to recognize a 1-to-0 transition, the maximum count rate is 1/24 of the oscillator frequency. To ensure that a given level is sampled at least once before it changes, the level should be held for at least one full machine cycle.

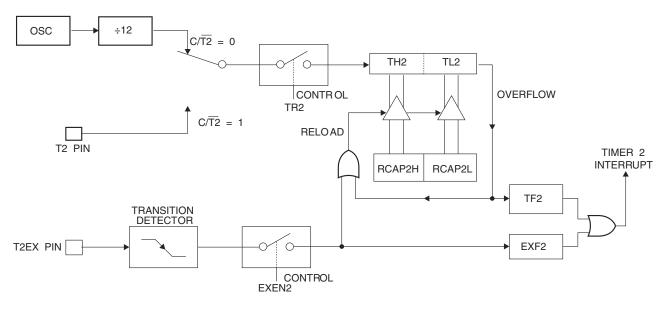

#### 10.1 Capture Mode

In the capture mode, two options are selected by bit EXEN2 in T2CON. If EXEN2 = 0, Timer 2 is a 16-bit timer or counter which upon overflow sets bit TF2 in T2CON. This bit can then be used to generate an interrupt. If EXEN2 = 1, Timer 2 performs the same operation, but a 1-to-0 transition at external input T2EX also causes the current value in TH2 and TL2 to be captured into RCAP2H and RCAP2L, respectively. In addition, the transition at T2EX causes bit EXF2 in T2CON to be set. The EXF2 bit, like TF2, can generate an interrupt. The capture mode is illustrated in Figure 10-1.

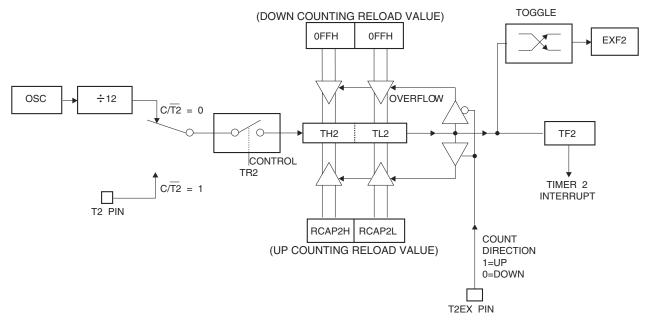

### 10.2 Auto-reload (Up or Down Counter)

Timer 2 can be programmed to count up or down when configured in its 16-bit auto-reload mode. This feature is invoked by the DCEN (Down Counter Enable) bit located in the SFR T2MOD (see Table 10-2). Upon reset, the DCEN bit is set to 0 so that timer 2 will default to count up. When DCEN is set, Timer 2 can count up or down, depending on the value of the T2EX pin.

Figure 10-2. Timer 2 Auto Reload Mode (DCEN = 0)

Figure 10-3. Timer 2 Auto Reload Mode (DCEN = 1)

### Table 13-1. Interrupt Enable (IE) Register

| (MSE    | B)                 |                   |            | (LSB)                                          |                |                 |        |     |        |

|---------|--------------------|-------------------|------------|------------------------------------------------|----------------|-----------------|--------|-----|--------|

|         | EA                 | -                 | ET2        | ES                                             | ET1            | EX1             | ET0    | EX0 |        |

| Ena     | ble Bit = 1 enable | es the interrupt. |            |                                                |                |                 |        |     |        |

| Ena     | ble Bit = 0 disabl | es the interrupt. |            |                                                |                |                 |        |     |        |

| Symbo   | )l                 | Position          | F          | unction                                        |                |                 |        |     |        |

| EA      |                    | IE.7              |            | Disables all interrup<br>nterrupt source is ir |                |                 |        |     | ) bit. |

| _       |                    | IE.6              | F          | leserved.                                      |                |                 |        |     |        |

| ET2     |                    | IE.5              | г          | imer 2 interrupt en                            | able bit.      |                 |        |     |        |

| ES      |                    | IE.4              | S          | Serial Port interrupt                          | enable bit.    |                 |        |     |        |

| ET1     |                    | IE.3              | г          | imer 1 interrupt en                            | able bit.      |                 |        |     |        |

| EX1     |                    | IE.2              | E          | External interrupt 1                           | enable bit.    |                 |        |     |        |

| ET0     |                    | IE.1              | г          | imer 0 interrupt en                            | able bit.      |                 |        |     |        |

| EX0     |                    | IE.0              | E          | External interrupt 0                           | enable bit.    |                 |        |     |        |

| User so | oftware should r   | never write 1s to | reserved t | oits, because they r                           | nay be used in | future AT89 pro | ducts. |     |        |

#### Figure 13-1. Interrupt Sources

18 AT89S52

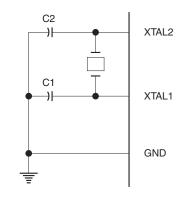

## 14. Oscillator Characteristics

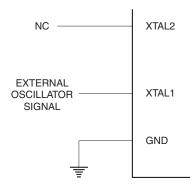

XTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier that can be configured for use as an on-chip oscillator, as shown in Figure 16-1. Either a quartz crystal or ceramic resonator may be used. To drive the device from an external clock source, XTAL2 should be left unconnected while XTAL1 is driven, as shown in Figure 16-2. There are no requirements on the duty cycle of the external clock signal, since the input to the internal clock-ing circuitry is through a divide-by-two flip-flop, but minimum and maximum voltage high and low time specifications must be observed.

## 15. Idle Mode

In idle mode, the CPU puts itself to sleep while all the on-chip peripherals remain active. The mode is invoked by software. The content of the on-chip RAM and all the special functions registers remain unchanged during this mode. The idle mode can be terminated by any enabled interrupt or by a hardware reset.

Note that when idle mode is terminated by a hardware reset, the device normally resumes program execution from where it left off, up to two machine cycles before the internal reset algorithm takes control. On-chip hardware inhibits access to internal RAM in this event, but access to the port pins is not inhibited. To eliminate the possibility of an unexpected write to a port pin when idle mode is terminated by a reset, the instruction following the one that invokes idle mode should not write to a port pin or to external memory.

## 16. Power-down Mode

In the Power-down mode, the oscillator is stopped, and the instruction that invokes Power-down is the last instruction executed. The on-chip RAM and Special Function Registers retain their values until the Power-down mode is terminated. Exit from Power-down mode can be initiated either by a hardware reset or by an enabled external interrupt. Reset redefines the SFRs but does not change the on-chip RAM. The reset should not be activated before  $V_{CC}$  is restored to its normal operating level and must be held active long enough to allow the oscillator to restart and stabilize.

Figure 16-1. Oscillator Connections

Note: 1. C1, C2 =  $30 \text{ pF} \pm 10 \text{ pF}$  for Crystals =  $40 \text{ pF} \pm 10 \text{ pF}$  for Ceramic Resonators

#### Figure 16-2. External Clock Drive Configuration

Table 16-1.

Status of External Pins During Idle and Power-down Modes

| Mode       | Program<br>Memory | ALE | PSEN | PORT0 | PORT1 | PORT2   | PORT3 |

|------------|-------------------|-----|------|-------|-------|---------|-------|

| Idle       | Internal          | 1   | 1    | Data  | Data  | Data    | Data  |

| Idle       | External          | 1   | 1    | Float | Data  | Address | Data  |

| Power-down | Internal          | 0   | 0    | Data  | Data  | Data    | Data  |

| Power-down | External          | 0   | 0    | Float | Data  | Data    | Data  |

## **17. Program Memory Lock Bits**

The AT89S52 has three lock bits that can be left unprogrammed (U) or can be programmed (P) to obtain the additional features listed in Table 17-1.

|   | Program | Lock Bits |     |                                                                                                                                                                                                                                     |

|---|---------|-----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | LB1     | LB2       | LB3 | Protection Type                                                                                                                                                                                                                     |

| 1 | U       | U         | U   | No program lock features                                                                                                                                                                                                            |

| 2 | Ρ       | U         | U   | MOVC instructions executed from external program memory are disabled from fetching code bytes from internal memory, $\overline{\text{EA}}$ is sampled and latched on reset, and further programming of the Flash memory is disabled |

| 3 | Р       | Р         | U   | Same as mode 2, but verify is also disabled                                                                                                                                                                                         |

| 4 | Р       | Р         | Р   | Same as mode 3, but external execution is also disabled                                                                                                                                                                             |

**Table 17-1.**Lock Bit Protection Modes

When lock bit 1 is programmed, the logic level at the  $\overline{EA}$  pin is sampled and latched during reset. If the device is powered up without a reset, the latch initializes to a random value and holds that value until reset is activated. The latched value of  $\overline{EA}$  must agree with the current logic level at that pin in order for the device to function properly.

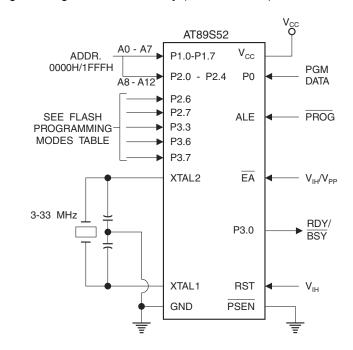

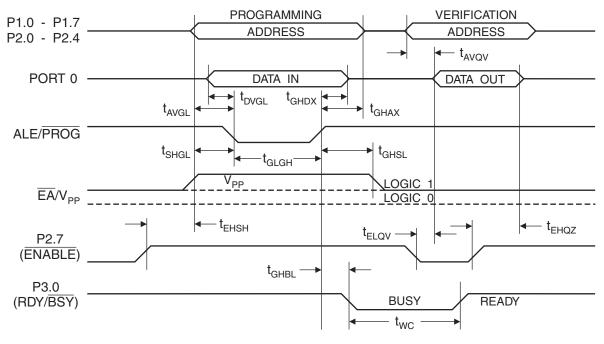

Figure 22-1. Programming the Flash Memory (Parallel Mode)

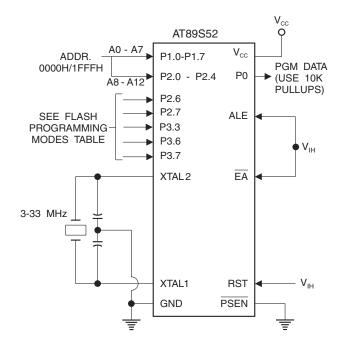

Figure 22-2. Verifying the Flash Memory (Parallel Mode)

# 23. Flash Programming and Verification Characteristics (Parallel Mode)

| Symbol              | Parameter                             | Min                  | Max                  | Units |

|---------------------|---------------------------------------|----------------------|----------------------|-------|

| V <sub>PP</sub>     | Programming Supply Voltage            | 11.5                 | 12.5                 | V     |

| I <sub>PP</sub>     | Programming Supply Current            |                      | 10                   | mA    |

| I <sub>CC</sub>     | V <sub>CC</sub> Supply Current        |                      | 30                   | mA    |

| 1/t <sub>CLCL</sub> | Oscillator Frequency                  | 3                    | 33                   | MHz   |

| t <sub>AVGL</sub>   | Address Setup to PROG Low             | 48 t <sub>CLCL</sub> |                      |       |

| t <sub>GHAX</sub>   | Address Hold After PROG               | 48 t <sub>CLCL</sub> |                      |       |

| t <sub>DVGL</sub>   | Data Setup to PROG Low                | 48 t <sub>CLCL</sub> |                      |       |

| t <sub>GHDX</sub>   | Data Hold After PROG                  | 48 t <sub>CLCL</sub> |                      |       |

| t <sub>EHSH</sub>   | P2.7 (ENABLE) High to V <sub>PP</sub> | 48 t <sub>CLCL</sub> |                      |       |

| t <sub>SHGL</sub>   | V <sub>PP</sub> Setup to PROG Low     | 10                   |                      | μs    |

| t <sub>GHSL</sub>   | V <sub>PP</sub> Hold After PROG       | 10                   |                      | μs    |

| t <sub>GLGH</sub>   | PROG Width                            | 0.2                  | 1                    | μs    |

| t <sub>AVQV</sub>   | Address to Data Valid                 |                      | 48 t <sub>CLCL</sub> |       |

| t <sub>ELQV</sub>   | ENABLE Low to Data Valid              |                      | 48 t <sub>CLCL</sub> |       |

| t <sub>EHQZ</sub>   | Data Float After ENABLE               | 0                    | 48 t <sub>CLCL</sub> |       |

| t <sub>GHBL</sub>   | PROG High to BUSY Low                 |                      | 1.0                  | μs    |

| t <sub>wc</sub>     | Byte Write Cycle Time                 |                      | 50                   | μs    |

$T_A = 20^{\circ}C$  to  $30^{\circ}C$ ,  $V_{CC} = 4.5$  to 5.5V

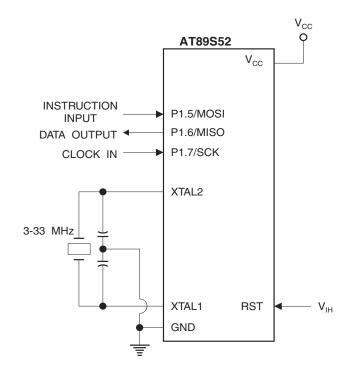

Figure 23-2. Flash Memory Serial Downloading

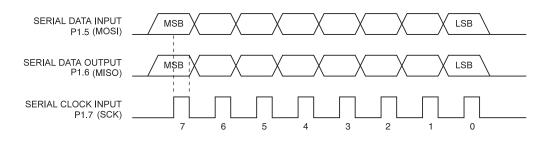

# 24. Flash Programming and Verification Waveforms – Serial Mode

Figure 24-1. Serial Programming Waveforms

| Table 24-1. Serial Pro | gramming Instruction Set |

|------------------------|--------------------------|

|------------------------|--------------------------|

|                                     | Instruction<br>Format |                                                                    |                        |                                               |                                                                                             |

|-------------------------------------|-----------------------|--------------------------------------------------------------------|------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------|

| Instruction                         | Byte 1                | Byte 2                                                             | Byte 3                 | Byte 4                                        | Operation                                                                                   |

| Programming Enable                  | 1010 1100             | 0101 0011                                                          | xxxx xxxx              | xxxx xxxx<br>0110 1001<br>(Output on<br>MISO) | Enable Serial Programming while RST is high                                                 |

| Chip Erase                          | 1010 1100             | 100x xxxx                                                          | XXXX XXXX              | XXXX XXXX                                     | Chip Erase Flash memory array                                                               |

| Read Program Memory<br>(Byte Mode)  | 0010 0000             | A12<br>A11<br>A12<br>A12<br>A12<br>A12<br>A12<br>A12<br>A12<br>A12 | AAAA 4567<br>AAAA 4567 | 0000 0000                                     | Read data from Program memory in the byte mode                                              |

| Write Program Memory<br>(Byte Mode) | 0100 0000             | A11 2<br>A11 2<br>A90<br>A30<br>A11 2<br>A30<br>A11 2<br>A12       | AAAA 4567              | 0000 0000<br>7000 0000                        | Write data to Program memory in the byte mode                                               |

| Write Lock Bits <sup>(1)</sup>      | 1010 1100             | 1110 00 品品                                                         | xxxx xxxx              | xxxx xxxx                                     | Write Lock bits. See Note (1).                                                              |

| Read Lock Bits                      | 0010 0100             | XXXX XXXX                                                          | XXXX XXXX              | xxx BIB2 XXX                                  | Read back current status of<br>the lock bits (a programmed<br>lock bit reads back as a "1") |

| Read Signature Bytes                | 0010 1000             | A11 2<br>A11 2<br>A90<br>A30<br>A12                                | ⊱xxx xxx0              | Signature Byte                                | Read Signature Byte                                                                         |

| Read Program Memory<br>(Page Mode)  | 0011 0000             | A12 XXX<br>A12 XXX<br>A200<br>A12 XXX                              | Byte 0                 | Byte 1<br>Byte 255                            | Read data from Program<br>memory in the Page Mode<br>(256 bytes)                            |

| Write Program Memory<br>(Page Mode) | 0101 0000             | A11 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2                            | Byte 0                 | Byte 1<br>Byte 255                            | Write data to Program<br>memory in the Page Mode<br>(256 bytes)                             |

Note:

1. B1 = 0,  $B2 = 0 \longrightarrow Mode 1$ , no lock protection

$B1 = 0, B2 = 1 \dots$  Mode 2, lock bit 1 activated  $B1 = 1, B2 = 0 \dots$  Mode 3, lock bit 2 activated

B1 = 1,  $B2 = 1 \longrightarrow Mode 4$ , lock bit 3 activated

$\underline{Each}$  of the lock bit modes needs to be activated sequentially before Mode 4 can be executed.

After Reset signal is high, SCK should be low for at least 64 system clocks before it goes high to clock in the enable data bytes. No pulsing of Reset signal is necessary. SCK should be no faster than 1/16 of the system clock at XTAL1.

For Page Read/Write, the data always starts from byte 0 to 255. After the command byte and upper address byte are latched, each byte thereafter is treated as data until all 256 bytes are shifted in/out. Then the next instruction will be ready to be decoded.

# **25. Serial Programming Characteristics**

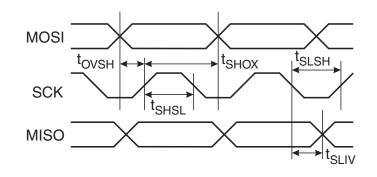

Figure 25-1. Serial Programming Timing

**Table 25-1.**Serial Programming Characteristics,  $T_A = -40$ · C to 85· C,  $V_{CC} = 4.0 - 5.5V$  (Unless Otherwise Noted)

| Symbol              | Parameter                         | Min                 | Тур | Max                        | Units |

|---------------------|-----------------------------------|---------------------|-----|----------------------------|-------|

| 1/t <sub>CLCL</sub> | Oscillator Frequency              | 3                   |     | 33                         | MHz   |

| t <sub>CLCL</sub>   | Oscillator Period                 | 30                  |     |                            | ns    |

| t <sub>SHSL</sub>   | SCK Pulse Width High              | 8 t <sub>CLCL</sub> |     |                            | ns    |

| t <sub>SLSH</sub>   | SCK Pulse Width Low               | 8 t <sub>CLCL</sub> |     |                            | ns    |

| t <sub>ovsh</sub>   | MOSI Setup to SCK High            | t <sub>CLCL</sub>   |     |                            | ns    |

| t <sub>SHOX</sub>   | MOSI Hold after SCK High          | 2 t <sub>CLCL</sub> |     |                            | ns    |

| t <sub>SLIV</sub>   | SCK Low to MISO Valid             | 10                  | 16  | 32                         | ns    |

| t <sub>ERASE</sub>  | Chip Erase Instruction Cycle Time |                     |     | 500                        | ms    |

| t <sub>swc</sub>    | Serial Byte Write Cycle Time      |                     |     | 64 t <sub>CLCL</sub> + 400 | μs    |

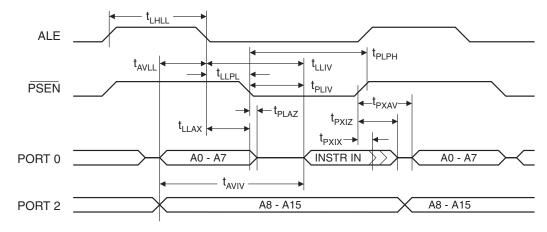

# 29. External Program Memory Read Cycle

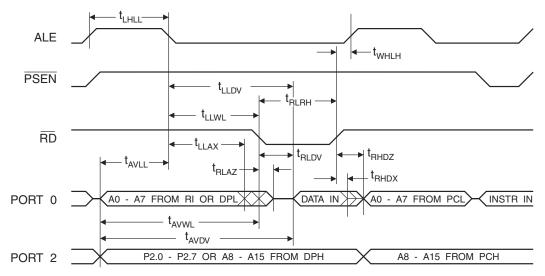

# 30. External Data Memory Read Cycle

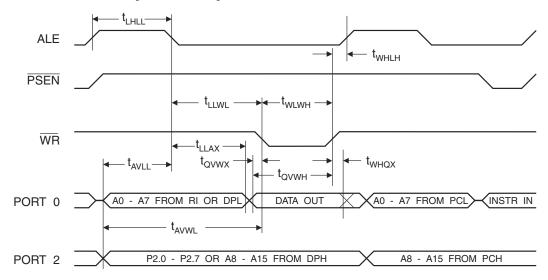

# 31. External Data Memory Write Cycle

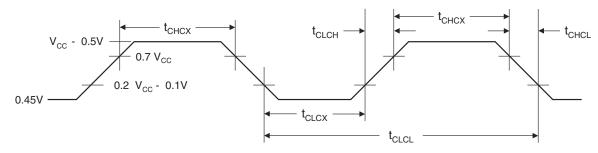

## 32. External Clock Drive Waveforms

# **33. External Clock Drive**

| Symbol              | Parameter            | Min | Мах | Units |

|---------------------|----------------------|-----|-----|-------|

| 1/t <sub>CLCL</sub> | Oscillator Frequency | 0   | 33  | MHz   |

| t <sub>CLCL</sub>   | Clock Period         | 30  |     | ns    |

| t <sub>CHCX</sub>   | High Time            | 12  |     | ns    |

| t <sub>CLCX</sub>   | Low Time             | 12  |     | ns    |

| t <sub>CLCH</sub>   | Rise Time            |     | 5   | ns    |

| t <sub>CHCL</sub>   | Fall Time            |     | 5   | ns    |

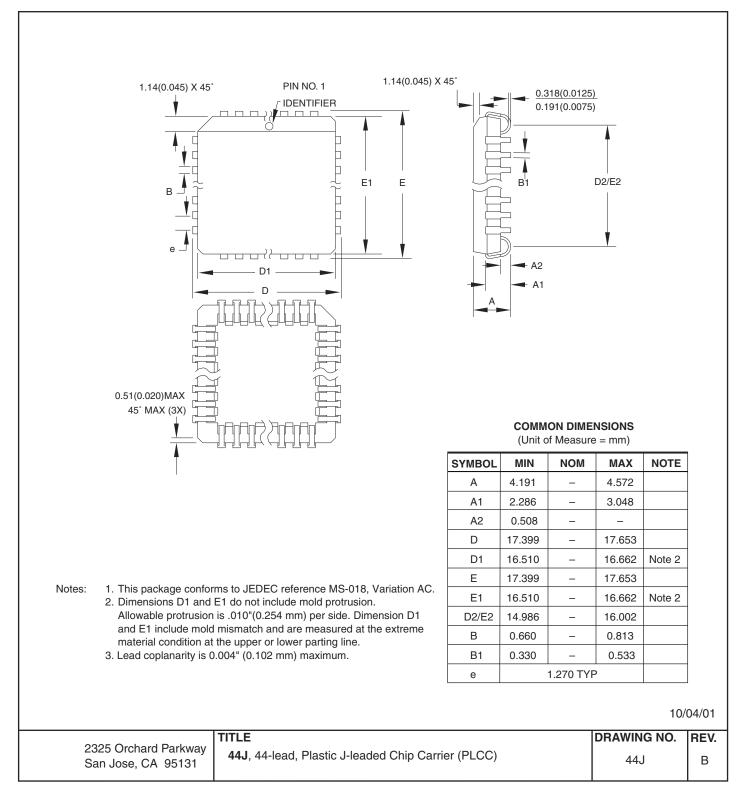

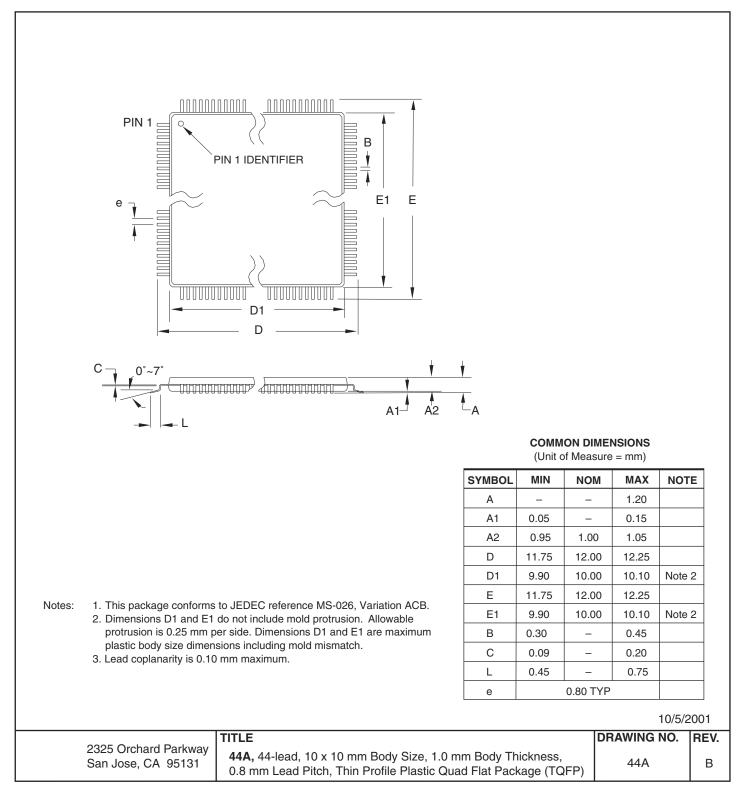

## **39. Packaging Information**

### 39.1 44A – TQFP

### 39.2 44J – PLCC