Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 5                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 4x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 8-VDFN Exposed Pad                                                        |

| Supplier Device Package    | 8-DFN (3x3)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f1840-e-mf |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC12(L)F1840

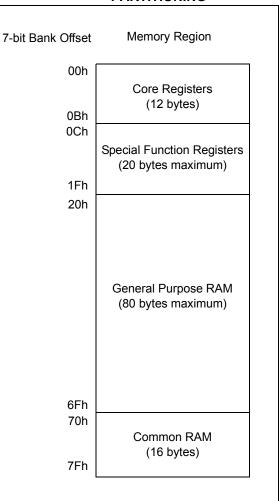

## 3.3.1 SPECIAL FUNCTION REGISTER

The Special Function Registers are registers used by the application to control the desired operation of peripheral functions in the device. The Special Function Registers occupy the 20 bytes after the core registers of every data memory bank (addresses x0Ch/x8Ch through x1Fh/x9Fh). The registers associated with the operation of the peripherals are described in the appropriate peripheral chapter of this data sheet.

## 3.3.2 GENERAL PURPOSE RAM

There are up to 80 bytes of GPR in each data memory bank. The Special Function Registers occupy the 20 bytes after the core registers of every data memory bank (addresses x0Ch/x8Ch through x1Fh/x9Fh).

### 3.3.2.1 Linear Access to GPR

The general purpose RAM can be accessed in a non-banked method via the FSRs. This can simplify access to large memory structures. See **Section 3.6.2** "Linear Data Memory" for more information.

## 3.3.3 COMMON RAM

There are 16 bytes of common RAM accessible from all banks.

#### FIGURE 3-2: BANKED MEMORY PARTITIONING

## 3.3.4 DEVICE MEMORY MAPS

The memory maps for the device family are as shown in Table 3-3.

## 7.4 MCLR

The  $\overline{\text{MCLR}}$  is an optional external input that can reset the device. The  $\overline{\text{MCLR}}$  function is controlled by the MCLRE bit of Configuration Words and the LVP bit of Configuration Words (Table 7-2).

| TABLE 7-2: MCLR CONFIGURATION |

|-------------------------------|

|-------------------------------|

| MCLRE | LVP | MCLR     |

|-------|-----|----------|

| 0     | 0   | Disabled |

| 1     | 0   | Enabled  |

| x     | 1   | Enabled  |

## 7.4.1 MCLR ENABLED

When MCLR is enabled and the pin is held low, the device is held in Reset. The MCLR pin is connected to VDD through an internal weak pull-up.

The device has a noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

**Note:** A Reset does not drive the MCLR pin low.

## 7.4.2 MCLR DISABLED

When MCLR is disabled, the pin functions as a general purpose input and the internal weak pull-up is under software control. See **Section 12.2 "PORTA Registers"** for more information.

## 7.5 Watchdog Timer (WDT) Reset

The Watchdog Timer generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The  $\overline{TO}$  and  $\overline{PD}$  bits in the STATUS register are changed to indicate the WDT Reset. See **Section 10.0** "**Watchdog Timer (WDT)**" for more information.

## 7.6 RESET Instruction

A RESET instruction will cause a device Reset. The  $\overline{RI}$  bit in the PCON register will be set to '0'. See Table 7-4 for default conditions after a RESET instruction has occurred.

## 7.7 Stack Overflow/Underflow Reset

The device can reset when the Stack Overflows or Underflows. The STKOVF or STKUNF bits of the PCON register indicate the Reset condition. These Resets are enabled by setting the STVREN bit in Configuration Word 2. See **Section 3.5.2 "Overflow/Underflow Reset"** for more information.

## 7.8 **Programming Mode Exit**

Upon exit of Programming mode, the device will behave as if a POR had just occurred.

## 7.9 Power-Up Timer

The Power-up Timer optionally delays device execution after a BOR or POR event. This timer is typically used to allow VDD to stabilize before allowing the device to start running.

The Power-up Timer is controlled by the PWRTE bit of Configuration Words.

## 7.10 Start-up Sequence

Upon the release of a POR or BOR, the following must occur before the device will begin executing:

- 1. Power-up Timer runs to completion (if enabled).

- 2. Oscillator start-up timer runs to completion (if required for oscillator source).

- 3. MCLR must be released (if enabled).

The total time-out will vary based on oscillator configuration and Power-up Timer configuration. See Section 5.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for more information.

The Power-up Timer and oscillator start-up timer run independently of MCLR Reset. If MCLR is kept low long enough, the Power-up Timer and oscillator start-up timer will expire. Upon bringing MCLR high, the device will begin execution immediately (see Figure 7-3). This is useful for testing purposes or to synchronize more than one device operating in parallel.

| U-0               | U-0 | R/W-1/1           | R/W-1/1 | R/W-1/1        | R/W-1/1          | R/W-1/1          | R/W-1/1      |

|-------------------|-----|-------------------|---------|----------------|------------------|------------------|--------------|

| _                 | _   | WPUA5             | WPUA4   | WPUA3          | WPUA2            | WPUA1            | WPUA0        |

| bit 7             |     |                   |         |                |                  |                  | bit 0        |

|                   |     |                   |         |                |                  |                  |              |

| Legend:           |     |                   |         |                |                  |                  |              |

| R = Readable bit  |     | W = Writable      | bit     | U = Unimpler   | mented bit, read | as '0'           |              |

| u = Bit is unchan | ged | x = Bit is unkr   | nown    | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is set  |     | '0' = Bit is clea | ared    |                |                  |                  |              |

## REGISTER 12-6: WPUA: WEAK PULL-UP PORTA REGISTER

bit 7-6 Unimplemented: Read as '0'

bit 5-0 WPUA<5:0>: Weak Pull-up Register bits<sup>(1, 2)</sup> 1 = Pull-up enabled 0 = Pull-up disabled

**Note 1:** Global WPUEN bit of the OPTION register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

| Name       | Bit 7   | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|------------|---------|--------|--------|--------|--------|---------|---------|---------|---------------------|

| ANSELA     | —       |        | —      | ANSA4  |        | ANSA2   | ANSA1   | ANSA0   | 103                 |

| APFCON     | RXDTSEL | SDOSEL | SSSEL  |        | T1GSEL | TXCKSEL | P1BSEL  | CCP1SEL | 99                  |

| LATA       | —       | _      | LATA5  | LATA4  | _      | LATA2   | LATA1   | LATA0   | 103                 |

| OPTION_REG | WPUEN   | INTEDG | TMR0CS | TMR0SE | PSA    |         | PS<2:0> |         | 145                 |

| PORTA      | —       | _      | RA5    | RA4    | RA3    | RA2     | RA1     | RA0     | 102                 |

| TRISA      | —       | _      | TRISA5 | TRISA4 | TRISA3 | TRISA2  | TRISA1  | TRISA0  | 102                 |

| WPUA       | _       |        | WPUA5  | WPUA4  | WPUA3  | WPUA2   | WPUA1   | WPUA0   | 104                 |

## TABLE 12-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

## TABLE 12-3: SUMMARY OF CONFIGURATION WORD WITH PORTA

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1   | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|-----------|---------|---------------------|

|         | 13:8 |         | —       | FCMEN    | IESO     | CLKOUTEN | BOREI    | N<1:0>    | CPD     | 22                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDTE     | E<1:0>   |          | FOSC<2:0> |         | 33                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by PORTA.

## 19.11 Register Definitions: Comparator Control

| R/W-0/0         | R-0/0                    | R/W-0/0                               | R/W-0/0         | U-0            | R/W-1/1          | R/W-0/0         | R/W-0/0         |

|-----------------|--------------------------|---------------------------------------|-----------------|----------------|------------------|-----------------|-----------------|

| C10N            | C10UT                    | C10E                                  | C1POL           | _              | C1SP             | C1HYS           | C1SYNC          |

| bit 7           |                          |                                       |                 |                | •                |                 | bit 0           |

| <u> </u>        |                          |                                       |                 |                |                  |                 |                 |

| Legend:         |                          |                                       |                 |                |                  |                 |                 |

| R = Readable    |                          | W = Writable                          |                 |                | emented bit, rea |                 |                 |

| u = Bit is unc  | 0                        | x = Bit is unkr                       |                 | -n/n = Value   | at POR and BC    | DR/Value at all | other Resets    |

| '1' = Bit is se | t                        | '0' = Bit is cle                      | ared            |                |                  |                 |                 |

| bit 7           | C1ON: Com                | parator Enable                        | bit             |                |                  |                 |                 |

|                 |                          | ator is enabled                       |                 |                |                  |                 |                 |

|                 | 0 = Compara              | ator is disabled                      | and consumes    | no active pov  | wer              |                 |                 |

| bit 6           | C1OUT: Cor               | nparator Output                       | bit             |                |                  |                 |                 |

|                 |                          | 1 (inverted pola                      | <u>rity):</u>   |                |                  |                 |                 |

|                 | 1 = C1VP <<br>0 = C1VP > |                                       |                 |                |                  |                 |                 |

|                 |                          | 0 <u>(non-inverted</u>                | d polarity):    |                |                  |                 |                 |

|                 | 1 = C1VP >               |                                       | <u> </u>        |                |                  |                 |                 |

|                 | 0 = C1VP <               | C1VN                                  |                 |                |                  |                 |                 |

| bit 5           | C10E: Com                | parator Output I                      | Enable bit      |                |                  |                 |                 |

|                 |                          | •                                     |                 | Requires that  | the associated T | RIS bit be clea | red to actually |

|                 |                          | e pin. Not affect<br>is internal only | ed by C1ON.     |                |                  |                 |                 |

| bit 4           |                          | nparator Output                       | Polarity Selec  | t bit          |                  |                 |                 |

|                 |                          | ator output is inv                    | -               |                |                  |                 |                 |

|                 | 0 = Compara              | ator output is no                     | t inverted      |                |                  |                 |                 |

| bit 3           | Unimpleme                | nted: Read as '                       | 0'              |                |                  |                 |                 |

| bit 2           | C1SP: Com                | parator Speed/F                       | ower Select bi  | t              |                  |                 |                 |

|                 |                          | ator operates in<br>ator operates in  |                 |                |                  |                 |                 |

| bit 1           | C1HYS: Cor               | nparator Hyster                       | esis Enable bit |                |                  |                 |                 |

|                 |                          | ator hysteresis<br>ator hysteresis    |                 |                |                  |                 |                 |

| bit 0           | -                        | omparator Outp                        |                 | s Mode bit     |                  |                 |                 |

|                 |                          |                                       |                 |                | ronous to chang  | ges on Timer1   | clock source.   |

|                 | Output u                 | updated on the                        | falling edge of | Timer1 clock   | source.          | -               |                 |

|                 | 0 = Compar               | ator output to T                      | imer1 and I/O   | oin is asynchr | onous.           |                 |                 |

# PIC12(L)F1840

| R/W-x/u          | U-0                                        | U-0              | U-0            | R/W-x/u           | R/W-x/u          | R/W-x/u          | R/W-x/u      |  |  |  |

|------------------|--------------------------------------------|------------------|----------------|-------------------|------------------|------------------|--------------|--|--|--|

| MDMSODIS         | _                                          |                  | _              |                   | MDMS             | 6<3:0>           |              |  |  |  |

| bit 7            |                                            |                  | •              |                   |                  |                  | bit C        |  |  |  |

|                  |                                            |                  |                |                   |                  |                  |              |  |  |  |

| Legend:          |                                            |                  |                |                   |                  |                  |              |  |  |  |

| R = Readable     | bit                                        | W = Writable     | bit            | U = Unimpler      | nented bit, read | l as '0'         |              |  |  |  |

| u = Bit is unch  | anged                                      | x = Bit is unkr  | nown           | -n/n = Value a    | at POR and BO    | R/Value at all c | other Resets |  |  |  |

| '1' = Bit is set |                                            | '0' = Bit is cle | ared           |                   |                  |                  |              |  |  |  |

|                  |                                            |                  |                |                   |                  |                  |              |  |  |  |

| bit 7            | MDMSODIS:                                  | Modulation So    | urce Output I  | Disable bit       |                  |                  |              |  |  |  |

|                  | 1 = Output si                              | gnal driving the | e peripheral c | output pin (selec | ted by MDMS<     | 3:0>) is disable | ed           |  |  |  |

|                  |                                            |                  |                | output pin (selec |                  |                  |              |  |  |  |

| bit 6-4          | Unimplemen                                 | ted: Read as '   | 0'             |                   |                  |                  |              |  |  |  |

| bit 3-0          | MDMS<3:0> Modulation Source Selection bits |                  |                |                   |                  |                  |              |  |  |  |

|                  | 1111 = Rese                                | erved. No chan   | nel connecte   | ed.               |                  |                  |              |  |  |  |

|                  | 1110 = Rese                                | erved. No chan   | nel connecte   | ed.               |                  |                  |              |  |  |  |

|                  | 1101 = Rese                                | erved. No chan   | nel connecte   | ed.               |                  |                  |              |  |  |  |

|                  | 1100 = Rese                                | erved. No chan   | nel connecte   | ed.               |                  |                  |              |  |  |  |

|                  | 1011 = Rese                                | erved. No chan   | nel connecte   | ed.               |                  |                  |              |  |  |  |

|                  | 1010 = EUS                                 | ART TX output    | t.             |                   |                  |                  |              |  |  |  |

|                  | 1001 = Rese                                | erved. No chan   | nel connecte   | ed.               |                  |                  |              |  |  |  |

|                  | 1000 = MSS                                 | P1 SDO outpu     | ıt             |                   |                  |                  |              |  |  |  |

|                  | 0111 = Rese                                | erved. No chan   | nel connecte   | ed.               |                  |                  |              |  |  |  |

|                  | 0110 = Com                                 | parator 1 outp   | ut             |                   |                  |                  |              |  |  |  |

|                  | 0101 = Rese                                | erved. No chan   | nel connecte   | ed.               |                  |                  |              |  |  |  |

|                  | 0100 = Rese                                | erved. No chan   | nel connecte   | ed.               |                  |                  |              |  |  |  |

|                  | 0011 = Rese                                | erved. No chan   | nel connecte   | ed.               |                  |                  |              |  |  |  |

|                  | 0010 = CCP                                 | 1 output (PWN    | 1 Output mod   | le only)          |                  |                  |              |  |  |  |

|                  | 0001 = MDN                                 |                  | •              |                   |                  |                  |              |  |  |  |

|                  |                                            | BIT bit of MDCO  | N register is  | modulation sou    | Irco             |                  |              |  |  |  |

## REGISTER 23-2: MDSRC: MODULATION SOURCE CONTROL REGISTER

| R/W-x/u          | R/W-x/u         | R/W-x/u                                                 | U-0           | R/W-x/u            | R/W-x/u            | R/W-x/u           | R/W-x/u        |  |  |

|------------------|-----------------|---------------------------------------------------------|---------------|--------------------|--------------------|-------------------|----------------|--|--|

| MDCHODIS         | MDCHPOL         | MDCHSYNC                                                | _             |                    | MDCH               | 1<3:0>            |                |  |  |

| bit 7            |                 |                                                         |               |                    |                    |                   | bit (          |  |  |

|                  |                 |                                                         |               |                    |                    |                   |                |  |  |

| Legend:          |                 |                                                         |               |                    |                    |                   |                |  |  |

| R = Readable     |                 | W = Writable bi                                         | -             | •                  | nented bit, read   |                   |                |  |  |

| u = Bit is unch  | anged           | x = Bit is unkno                                        | wn            | -n/n = Value a     | at POR and BO      | R/Value at all o  | other Resets   |  |  |

| '1' = Bit is set |                 | '0' = Bit is clear                                      | ed            |                    |                    |                   |                |  |  |

| bit 7            |                 | Modulator High                                          | Carriar Out   | nut Disabla hit    |                    |                   |                |  |  |

|                  |                 | ignal driving the r                                     |               |                    |                    | 3.02) is disable  | bd             |  |  |

|                  |                 | signal driving the p                                    |               |                    |                    | ,                 |                |  |  |

| bit 6            | MDCHPOL:        | Modulator High C                                        | arrier Pola   | rity Select bit    |                    |                   |                |  |  |

|                  | 1 = Selected    | l high carrier sign                                     | al is inverte | ed                 |                    |                   |                |  |  |

|                  | 0 = Selected    | l high carrier sign                                     | al is not inv | verted             |                    |                   |                |  |  |

| bit 5            |                 | SYNC: Modulator High Carrier Synchronization Enable bit |               |                    |                    |                   |                |  |  |

|                  |                 | or waits for a falli                                    | ng edge or    | n the high time of | carrier signal be  | efore allowing a  | a switch to th |  |  |

|                  | low time        | or Output is not s                                      | vnchronize    | d to the high tim  | e carrier signal   | (1)               |                |  |  |

| bit 4            |                 | nted: Read as '0'                                       | ynenionize    |                    |                    |                   |                |  |  |

| bit 3-0          | •               | Modulator Data H                                        | High Carrie   | r Selection bits   | (1)                |                   |                |  |  |

|                  |                 | erved. No chann                                         | -             |                    |                    |                   |                |  |  |

|                  | •               |                                                         |               |                    |                    |                   |                |  |  |

|                  | •               |                                                         |               |                    |                    |                   |                |  |  |

|                  | •               | awad Na ahaan                                           |               | a d                |                    |                   |                |  |  |

|                  |                 | erved. No chann<br>P1 output (PWM (                     |               |                    |                    |                   |                |  |  |

|                  |                 | erence Clock mod                                        |               |                    |                    |                   |                |  |  |

|                  | 0010 = MD       | CIN2 port pin                                           | <b>J</b>      |                    |                    |                   |                |  |  |

|                  |                 | CIN1 port pin                                           |               |                    |                    |                   |                |  |  |

|                  | 0000 = Vss      |                                                         |               |                    |                    |                   |                |  |  |

| Note 1: Na       | rowed carrier r | oulse widths or sr                                      | ours may or   | cour in the signa  | al stream if the o | carrier is not sv | nchronized     |  |  |

## REGISTER 23-3: MDCARH: MODULATION HIGH CARRIER CONTROL REGISTER

Note 1: Narrowed carrier pulse widths or spurs may occur in the signal stream if the carrier is not synchronized.

#### 24.2.6 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register, APFCON. To determine which pins can be moved and what their default locations are upon a reset, see Section 12.1 "Alternate Pin Function" for more information.

| Bit 7       | Bit 6                                                                                                          | Bit 5                                                                                                                                               | Bit 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Bit 3                            | Bit 2                                                                                                                                                                                                                                                                                                                                                                          | Bit 1                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Register<br>on Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXDTSEL     | SDOSEL                                                                                                         | SSSEL                                                                                                                                               | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | T1GSEL                           | TXCKSEL                                                                                                                                                                                                                                                                                                                                                                        | P1BSEL                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CCP1SEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| P1M•        | <1:0>                                                                                                          | DC1B                                                                                                                                                | <1:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                  | CCP1M<                                                                                                                                                                                                                                                                                                                                                                         | :3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 189                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Capture/Cor | mpare/PWM                                                                                                      | Register 1 L                                                                                                                                        | ow Byte (LSE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3)                               |                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 172                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Capture/Cor | mpare/PWM                                                                                                      | Register 1 H                                                                                                                                        | igh Byte (MS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SB)                              |                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 172                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GIE         | PEIE                                                                                                           | TMR0IE                                                                                                                                              | INTE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | IOCIE                            | TMR0IF                                                                                                                                                                                                                                                                                                                                                                         | INTF                                                                                                                                                                                                                                                                                                                                                                                                                                                      | IOCIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TMR1GIE     | ADIE                                                                                                           | RCIE                                                                                                                                                | TXIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SSP1IE                           | CCP1IE                                                                                                                                                                                                                                                                                                                                                                         | TMR2IE                                                                                                                                                                                                                                                                                                                                                                                                                                                    | TMR1IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| OSFIE       | _                                                                                                              | C1IE                                                                                                                                                | EEIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | BCL1IE                           | _                                                                                                                                                                                                                                                                                                                                                                              | _                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TMR1GIF     | ADIF                                                                                                           | RCIF                                                                                                                                                | TXIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SSP1IF                           | CCP1IF                                                                                                                                                                                                                                                                                                                                                                         | TMR2IF                                                                                                                                                                                                                                                                                                                                                                                                                                                    | TMR1IF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| OSFIF       | _                                                                                                              | C1IF                                                                                                                                                | EEIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | BCL1IF                           | _                                                                                                                                                                                                                                                                                                                                                                              | _                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TMR1C       | S<1:0>                                                                                                         | T1CKP                                                                                                                                               | S<1:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | T1OSCEN                          | T1SYNC                                                                                                                                                                                                                                                                                                                                                                         | _                                                                                                                                                                                                                                                                                                                                                                                                                                                         | TMR10N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 154                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TMR1GE      | T1GPOL                                                                                                         | T1GTM                                                                                                                                               | T1GSPM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | T1GGO/DONE                       | T1GVAL                                                                                                                                                                                                                                                                                                                                                                         | T1GSS                                                                                                                                                                                                                                                                                                                                                                                                                                                     | S<1:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 155                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Holding Reg | ister for the                                                                                                  | Least Signific                                                                                                                                      | cant Byte of t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | he 16-bit TMR1 F                 | Register                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 150*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Holding Reg | ister for the                                                                                                  | Most Signific                                                                                                                                       | ant Byte of tl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ne 16-bit TMR1 R                 | Register                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 150*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| —           | _                                                                                                              | TRISA5                                                                                                                                              | TRISA4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | TRISA3                           | TRISA2                                                                                                                                                                                                                                                                                                                                                                         | TRISA1                                                                                                                                                                                                                                                                                                                                                                                                                                                    | TRISA0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|             | RXDTSEL<br>P1M-<br>Capture/Con<br>GIE<br>TMR1GIE<br>OSFIE<br>TMR1GIF<br>OSFIF<br>TMR1C<br>TMR1C<br>Holding Reg | RXDTSELSDOSELP1M<1:0>Capture/Compare/PWMCapture/Compare/PWMGIEPEIETMR1GIEADIEOSFIE—TMR1GIFADIFOSFIF—TMR1CS<1:0>TMR1GET1GPOLHolding Register for the | RXDTSEL       SDOSEL       SSSEL         P1M<1:0>       DC1B         Capture/Compare/PWM Register 1 Ltd       Capture/Compare/PWM Register 1 H         GIE       PEIE       TMR0IE         TMR1GIE       ADIE       RCIE         OSFIE       —       C1IE         TMR1GIF       ADIF       RCIF         OSFIF       —       C1IF         TMR1CS<1:0>       T1CKP         TMR1GE       T1GPOL       T1GTM         Holding Register for the Least Signific       Holding Register for the Most Signific | RXDTSEL       SDOSEL       SSSEL | RXDTSELSDOSELSSSELT1GSELP1M<1:0>DC1B<1:0>Capture/Compare/PWM Register 1 Low Byte (LSB)Capture/Compare/PWM Register 1 High Byte (MSB)GIEPEIETMR0IEINTEIOCIETMR1GIEADIERCIETXIEOSFIEC1IEEEIEBCL1IETMR1GIFADIFRCIFTXIFSSP1IFOSFIFC1IFEEIFBCL1IFTMR1CS<1:0>T1CKPS<1:0>T1OSCENTMR1GET1GPOLT1GTMT1GSPMT1GGO/DONEHolding Register for the Least Significant Byte of the 16-bit TMR1 F | RXDTSELSDOSELSSSELT1GSELTXCKSELP1M<1:0>DC1B<1:0>CCP1MCapture/Compare/PWM Register 1 Low Byte (LSB)Capture/Compare/PWM Register 1 High Byte (MSB)GIEPEIETMR0IEINTEIOCIETMR0IFTMR1GIEADIERCIETXIESSP1IECCP1IEOSFIE—C1IEEEIEBCL1IE—TMR1GIFADIFRCIFTXIFSSP1IFCCP1IFOSFIF—C1IFEEIFBCL1IF—TMR1CS<1:0>T1CKPS<1:0>T1OSCENT1SYNCTMR1GET1GPOLT1GTMT1GSPMT1GGO/DONET1GVALHolding Register for the Least Significant Byte of the 16-bit TMR1 RegisterHolding Register | RXDTSELSDOSELSSSELT1GSELTXCKSELP1BSELP1M<1:0>DC1B<1:0>CCP1M<3:0>Capture/Compare/PWM Register 1 Low Byte (LSB)Capture/Compare/PWM Register 1 High Byte (MSB)GIEPEIETMR0IEINTEIOCIETMR0IFINTFTMR1GIEADIERCIETXIESSP1IECCP1IETMR2IEOSFIEC1IEEEIEBCL1IETMR1GIFADIFRCIFTXIFSSP1IFCCP1IFTMR2IFOSFIFC1IFEEIFBCL1IFTMR1CS<1:0>T1CKPS<1:0>T1OSCENT1SYNCTMR1GET1GPOLT1GTMT1GSPMT1GGO/DONET1GVALT1GSSHolding Register for the Least Significant Byte of the 16-bit TMR1 RegisterHolding Register for the Most Significant Byte of the 16-bit TMR1 Register | RXDTSELSDOSELSSSELT1GSELTXCKSELP1BSELCCP1SELP1M<1:0>DC1B<1:0>CCP1M<3:0>Capture/Compare/PWM Register 1 Low Byte (LSB)Capture/Compare/PWM Register 1 High Byte (MSB)GIEPEIETMR0IEINTEIOCIETMR0IFINTFIOCIFTMR1GIEADIERCIETXIESSP1IECCP1IETMR2IETMR1IEOSFIE—C1IEEEIEBCL1IE————TMR1GIFADIFRCIFTXIFSSP1IFCCP1IFTMR2IFTMR1IFOSFIF—C1IFEEIFBCL1IF————TMR1GIFADIFRCIFTXIFSSP1IFCCP1IFTMR2IFTMR1IFOSFIF—C1IFEEIFBCL1IF————TMR1GET1GPOLT1CKPS<1:0>T1OSCENT1SYNC—TMR1ONTMR1GET1GPOLT1GTMT1GSPMT1GGO/DONET1GVALT1GSS<1:0>Holding Register for the Least Significant Byte of the 16-bit TMR1 RegisterHolding RegisterIntervertional Byte of the 16-bit TMR1 Register |

TABLE 24-3: SUMMARY OF REGISTERS ASSOCIATED WITH COMPARE

- = Unimplemented location, read as '0'. Shaded cells are not used by Compare mode. Legend:

\* Page provides register information.

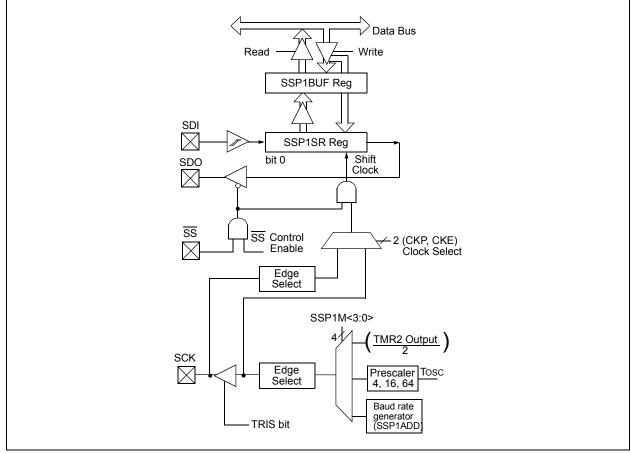

## 25.0 MASTER SYNCHRONOUS SERIAL PORT MODULE

## 25.1 Master SSP (MSSP1) Module Overview

The Master Synchronous Serial Port (MSSP1) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP1 module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)

The SPI interface supports the following modes and features:

- Master mode

- Slave mode

- Clock Parity

- Slave Select Synchronization (Slave mode only)

- · Daisy-chain connection of slave devices

Figure 25-1 is a block diagram of the SPI interface module.

## 25.2 SPI Mode Overview

The Serial Peripheral Interface (SPI) bus is a synchronous serial data communication bus that operates in Full-Duplex mode. Devices communicate in a master/slave environment where the master device initiates the communication. A slave device is controlled through a Chip Select known as Slave Select.

The SPI bus specifies four signal connections:

- · Serial Clock (SCK)

- Serial Data Out (SDO)

- · Serial Data In (SDI)

- Slave Select (SS)

Figure 25-1 shows the block diagram of the MSSP1 module when operating in SPI mode.

The SPI bus operates with a single master device and one or more slave devices. When multiple slave devices are used, an independent Slave Select connection is required from the master device to each slave device.

Figure 25-4 shows a typical connection between a master device and multiple slave devices.

The master selects only one slave at a time. Most slave devices have tri-state outputs so their output signal appears disconnected from the bus when they are not selected.

Transmissions involve two shift registers, eight bits in size, one in the master and one in the slave. With either the master or the slave device, data is always shifted out one bit at a time, with the Most Significant bit (MSb) shifted out first. At the same time, a new Least Significant bit (LSb) is shifted into the same register.

Figure 25-5 shows a typical connection between two processors configured as master and slave devices.

Data is shifted out of both shift registers on the programmed clock edge and latched on the opposite edge of the clock.