# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                |

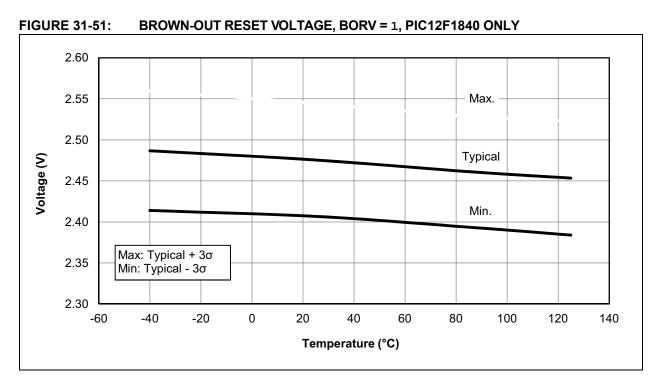

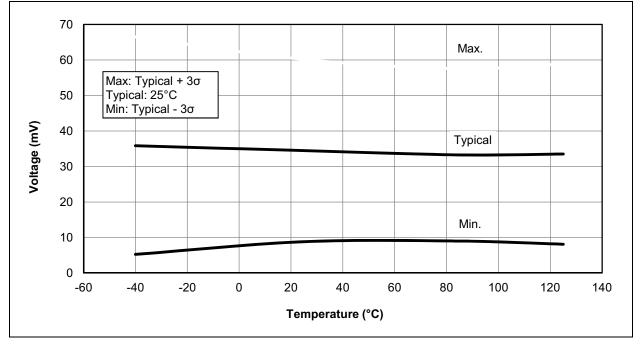

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 5                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                              |

| Data Converters            | A/D 4x10b; D/A 1x5b                                                      |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 8-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f1840-e-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.1 Automatic Interrupt Context Saving

During interrupts, certain registers are automatically saved in shadow registers and restored when returning from the interrupt. This saves stack space and user code. See **Section 8.5 "Automatic Context Saving"**, for more information.

# 2.2 16-level Stack with Overflow and Underflow

These devices have an external stack memory 15 bits wide and 16 words deep. A Stack Overflow or Underflow will set the appropriate bit (STKOVF or STKUNF) in the PCON register, and if enabled will cause a software Reset. See **Section 3.5 "Stack"** for more details.

### 2.3 File Select Registers

There are two 16-bit File Select Registers (FSR). FSRs can access all file registers and program memory, which allows one Data Pointer for all memory. When an FSR points to program memory, there is one additional instruction cycle in instructions using INDF to allow the data to be fetched. General purpose memory can now also be addressed linearly, providing the ability to access contiguous data larger than 80 bytes. There are also new instructions to support the FSRs. See **Section 3.6 "Indirect Addressing"** for more details.

### 2.4 Instruction Set

There are 49 instructions for the enhanced mid-range CPU to support the features of the CPU. See **Section 29.0 "Instruction Set Summary"** for more details.

| Address            | Name        | Bit 7           | Bit 6                                | Bit 5           | Bit 4           | Bit 3       | Bit 2         | Bit 1      | Bit 0   | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|--------------------|-------------|-----------------|--------------------------------------|-----------------|-----------------|-------------|---------------|------------|---------|----------------------|---------------------------------|

| Bank 4             |             |                 |                                      |                 |                 |             |               |            |         |                      |                                 |

| 20Ch               | WPUA        | —               |                                      | WPUA5           | WPUA4           | WPUA3       | WPUA2         | WPUA1      | WPUA0   | 11 1111              | 11 1111                         |

| 20Dh<br>to<br>210h | _           | Unimplement     | ed                                   |                 |                 |             |               |            |         | -                    | _                               |

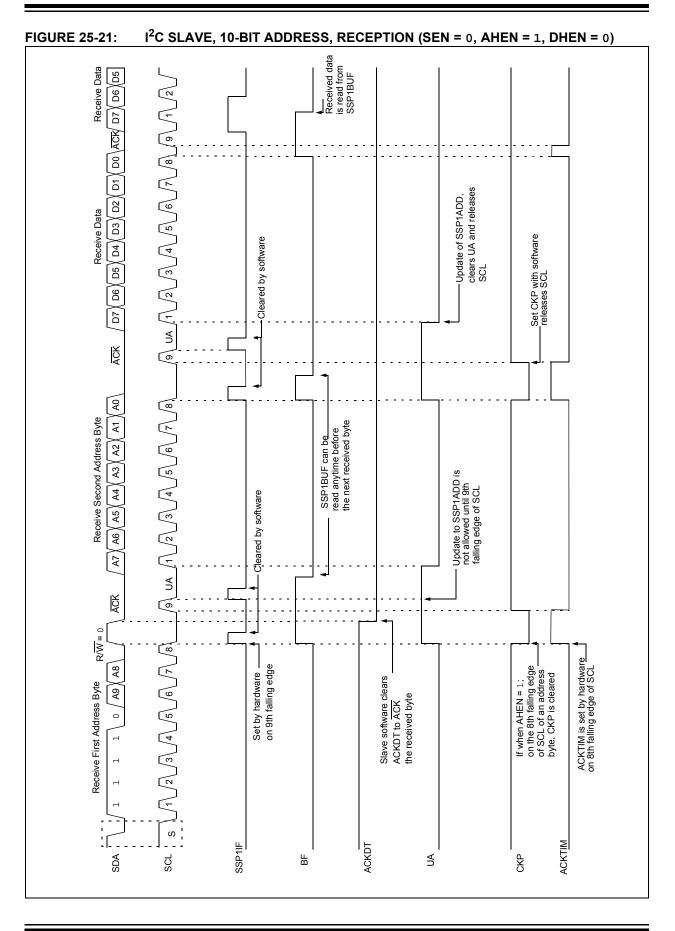

| 211h               | SSP1BUF     | Synchronous     | Serial Port Re                       | eceive Buffer/T | ransmit Regis   | ster        |               |            |         | xxxx xxxx            | uuuu uuuu                       |

| 212h               | SSP1ADD     |                 |                                      |                 | ADD<7           | :0>         |               |            |         | 0000 0000            | 0000 0000                       |

| 213h               | SSP1MSK     |                 |                                      |                 | MSK<7           | :0>         |               |            |         | 1111 1111            | 1111 1111                       |

| 214h               | SSP1STAT    | SMP             | CKE                                  | D/A             | Р               | S           | R/W           | UA         | BF      | 0000 0000            | 0000 0000                       |

| 215h               | SSP1CON1    | WCOL            | SSP10V                               | SSP1EN          | CKP             |             | SSP1N         | 1<3:0>     |         | 0000 0000            | 0000 0000                       |

| 216h               | SSP1CON2    | GCEN            | ACKSTAT                              | ACKDT           | ACKEN           | RCEN        | PEN           | RSEN       | SEN     | 0000 0000            | 0000 0000                       |

| 217h               | SSP1CON3    | ACKTIM          | PCIE                                 | SCIE            | BOEN            | SDAHT       | SBCDE         | AHEN       | DHEN    | 0000 0000            | 0000 0000                       |

| 218h<br>to<br>21Fh | _           | Unimplement     | ed                                   |                 |                 |             |               |            |         | _                    | _                               |

| Bank 5             | 5           |                 |                                      |                 |                 |             |               |            |         |                      |                                 |

| 28Ch<br>to<br>290h | _           | Unimplement     | Inimplemented                        |                 |                 |             |               |            |         | _                    | _                               |

| 291h               | CCPR1L      | Capture/Com     | Capture/Compare/PWM Register 1 (LSB) |                 |                 |             |               |            |         | XXXX XXXX            | uuuu uuuu                       |

| 292h               | CCPR1H      | Capture/Com     | pare/PWM Re                          | gister 1 (MSB)  | )               | -           |               |            |         | xxxx xxxx            | uuuu uuuu                       |

| 293h               | CCP1CON     | P1M             | <1:0>                                | DC1B            | <1:0>           |             | CCP1N         | /<3:0>     |         | 0000 0000            | 0000 0000                       |

| 294h               | PWM1CON     | P1RSEN          |                                      |                 | F               | 21DC<6:0>   |               |            |         | 0000 0000            | 0000 0000                       |

| 295h               | CCP1AS      | CCP1ASE         |                                      | CCP1AS<2:0>     | -               | PSS1A       | C<1:0>        | PSS1B      | 3D<1:0> | 0000 0000            | 0000 0000                       |

| 296h               | PSTR1CON    | —               | —                                    | —               | STR1SYNC        | Reserved    | Reserved      | STR1B      | STR1A   | 0 rr01               | 0 rr01                          |

| 297h<br>to<br>29Fh | _           | Unimplement     | ed                                   |                 |                 |             |               |            |         | _                    | _                               |

| Bank 6             | ;           |                 |                                      |                 |                 |             |               |            |         |                      |                                 |

| 30Ch<br>to<br>31Fh | _           | Unimplement     | Unimplemented                        |                 |                 |             |               |            | -       | _                    |                                 |

| Bank 7             | ,           |                 |                                      |                 |                 |             |               |            |         | 1                    |                                 |

| 38Ch<br>to<br>390h | _           | Unimplement     | ed                                   |                 |                 |             |               |            |         | -                    | —                               |

| 391h               | IOCAP       | _               | _                                    | IOCAP5          | IOCAP4          | IOCAP3      | IOCAP2        | IOCAP1     | IOCAP0  | 00 0000              | 00 0000                         |

| 392h               | IOCAN       | —               | _                                    | IOCAN5          | IOCAN4          | IOCAN3      | IOCAN2        | IOCAN1     | IOCAN0  | 00 0000              | 00 0000                         |

| 393h               | IOCAF       | —               | _                                    | IOCAF5          | IOCAF4          | IOCAF3      | IOCAF2        | IOCAF1     | IOCAF0  | 00 0000              | 00 0000                         |

| 394h<br>to<br>399h | _           | Unimplement     | ed                                   |                 |                 |             |               |            |         | _                    | _                               |

| 39Ah               | CLKRCON     | CLKREN          | CLKROE                               | CLKRSLR         | CLKRD           | C<1:0>      | C             | LKRDIV<2:0 | )>      | 0011 0000            | 0011 0000                       |

| 39Bh               | —           | Unimplement     | ed                                   |                 |                 |             |               |            |         | -                    | —                               |

| 39Ch               | MDCON       | MDEN            | MDOE                                 | MDSLR           | MDOPOL          | MDOUT       | —             | —          | MDBIT   | 00100                | 00100                           |

| 39Dh               | MDSRC       | MDMSODIS        | _                                    | _               | _               |             | MDMS          | 6<3:0>     |         | x xxxx               | u uuuu                          |

| 39Eh               | MDCARL      | MDCLODIS        | MDCLPOL                              | MDCLSYNC        | _               |             | MDCL          | <3:0>      |         | xxx- xxxx            | uuu- uuuu                       |

| 39Fh               | MDCARH      | MDCHODIS        | MDCHPOL                              | MDCHSYNC        | —               |             | MDCH          | <3:0>      |         | xxx- xxxx            | uuu- uuuu                       |

| Legend:            | x = unknown | n, u = unchange | ed, q = value                        | depends on co   | ndition, - = un | implemented | , r = reserve | d.         |         |                      |                                 |

### TABLE 3-6: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved Shaded locations are unimplemented, read as '0'.

**Note 1:** These registers can be addressed from any bank.

2: PIC12F1840 only.

3: Unimplemented, read as '1'.

### 5.2.1.4 4x PLL

The oscillator module contains a 4x PLL that can be used with both external and internal clock sources to provide a system clock source. The input frequency for the 4x PLL must fall within specifications. See the PLL Clock Timing Specifications in **Section 30.0 "Electrical Specifications"**.

The 4x PLL may be enabled for use by one of two methods:

- 1. Program the PLLEN bit in Configuration Words to a '1'.

- Write the SPLLEN bit in the OSCCON register to a '1'. If the PLLEN bit in Configuration Words is programmed to a '1', then the value of SPLLEN is ignored.

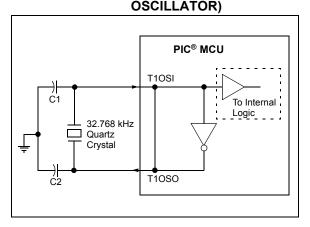

#### 5.2.1.5 TIMER1 Oscillator

The Timer1 oscillator is a separate crystal oscillator that is associated with the Timer1 peripheral. It is optimized for timekeeping operations with a 32.768 kHz crystal connected between the T1OSO and T1OSI device pins.

The Timer1 oscillator can be used as an alternate system clock source and can be selected during run-time using clock switching. Refer to **Section 5.3 "Clock Switching"** for more information.

### FIGURE 5-5:

QUARTZ CRYSTAL OPERATION (TIMER1

- Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- 3: For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

- TB097, "Interfacing a Micro Crystal MS1V-T1K 32.768 kHz Tuning Fork Crystal to a PIC16F690/SS" (DS91097)

- AN1288, "Design Practices for Low-Power External Oscillators" (DS01288)

### 5.2.1.6 External RC Mode

The external Resistor-Capacitor (RC) modes support the use of an external RC circuit. This allows the designer maximum flexibility in frequency choice while keeping costs to a minimum when clock accuracy is not required.

The RC circuit connects to OSC1. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. The function of the OSC2/CLKOUT pin is determined by the CLKOUTEN bit in Configuration Words.

Figure 5-6 shows the external RC mode connections.

### 9.1.1 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction

- SLEEP instruction will execute as a NOP.

- WDT and WDT prescaler will not be cleared

- TO bit of the STATUS register will not be set

- PD bit of the STATUS register will not be cleared.

- If the interrupt occurs **during or after** the execution of a **SLEEP** instruction

- SLEEP instruction will be completely executed

- Device will immediately wake-up from Sleep

- WDT and WDT prescaler will be cleared

- TO bit of the STATUS register will be set

- PD bit of the STATUS register will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

| FIGURE 9-                                    | I. WAN                                                                                        |                                      |                             | INKU                |                    | RUPI                            |                    |                                       |

|----------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------|-----------------------------|---------------------|--------------------|---------------------------------|--------------------|---------------------------------------|

| OSC1 <sup>(1)</sup><br>CLKOUT <sup>(2)</sup> | 1                                                                                             | Q1 Q2 Q3  Q4<br>\_/\_/\_/<br>        |                             | T1osc <sup>(3</sup> |                    | Q1 Q2 Q3 Q4<br>/~_/~_/~_/<br>// | Q1 Q2 Q3 Q4<br>    | Q1 Q2 Q3 Q4<br>~~~~~~                 |

| Interrupt flag                               |                                                                                               |                                      | /                           | •                   | Interrupt Laten    | cy <sup>(4)</sup>               | ·<br>              | · · · · · · · · · · · · · · · · · · · |

| GIE bit<br>(INTCON reg.)                     | ;;                                                                                            |                                      | Processor in                | '                   |                    |                                 | ·<br>·             |                                       |

| Instruction Flow<br>PC                       | х РС X                                                                                        | PC + 1                               | X PC                        | + 2                 | ( PC + 2           | PC + 2                          | X 0004h            | X 0005h                               |

| Instruction {<br>Fetched                     | Inst(PC) = Sleep                                                                              | Inst(PC + 1)                         | 1                           | 1<br>1<br>1         | Inst(PC + 2)       | 1<br>1<br>1                     | Inst(0004h)        | Inst(0005h)                           |

| Instruction {<br>Executed {                  | Inst(PC - 1)                                                                                  | Sleep                                | i<br>1                      | 1<br>1<br>1         | Inst(PC + 1)       | Forced NOP                      | Forced NOP         | Inst(0004h)                           |

| 2:<br>3:                                     | XT, HS or LP Oscilla<br>CLKOUT is shown h<br>T1osc; See <b>Sectior</b><br>GIE = 1 assumed. Ir | ere for timing re<br>30.0 "Electrica | ference.<br>al Specificatio |                     | calls the ISR at 0 | 0004h. If GIE = 0,              | execution will con | tinue in-line.                        |

#### FIGURE 9-1: WAKE-UP FROM SLEEP THROUGH INTERRUPT

| Name   | Bit 7  | Bit 6 | Bit 5     | Bit 4 | Bit 3     | Bit 2 | Bit 1    | Bit 0  | Register<br>on Page |

|--------|--------|-------|-----------|-------|-----------|-------|----------|--------|---------------------|

| OSCCON | SPLLEN |       | IRCF<3:0> |       |           |       | SCS<1:0> |        | 53                  |

| STATUS | —      | _     | —         | TO    | PD        | Z     | DC       | С      | 15                  |

| WDTCON | —      | _     |           | ١     | WDTPS<4:0 | >     |          | SWDTEN | 83                  |

### TABLE 10-4: SUMMARY OF CONFIGURATION WORD WITH WATCHDOG TIMER

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4  | Bit 11/3 | Bit 10/2   | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|-----------|----------|------------|---------|---------|---------------------|

| CONFIG1 | 13:8 | _       | _       | FCMEN    | IESO      | CLKOUTEN | BOREN<1:0> |         | —       | 22                  |

| CONFIGT | 7:0  | CP      | MCLRE   | PWRTE    | WDTE<1:0> |          | FOSC<2:0>  |         |         | 33                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Watchdog Timer.

R/W-x/u LATA0

bit 0

| U-0   | U-0 | R/W-x/u | R/W-x/u | U-0 | R/W-x/u | R/W-x/u | _ |

|-------|-----|---------|---------|-----|---------|---------|---|

| —     | —   | LATA5   | LATA4   | —   | LATA2   | LATA1   |   |

| bit 7 |     |         |         |     |         |         |   |

### REGISTER 12-4: LATA: PORTA DATA LATCH REGISTER

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Unimplemented: Read as '0'                                |

|---------|-----------------------------------------------------------|

| bit 5-4 | LATA<5:4>: RA<5:4> Output Latch Value bits <sup>(1)</sup> |

| bit 3   | Unimplemented: Read as '0'                                |

| bit 2-0 | LATA<2:0>: RA<2:0> Output Latch Value bits <sup>(1)</sup> |

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

### REGISTER 12-5: ANSELA: PORTA ANALOG SELECT REGISTER

| U-0   | U-0 | U-0 | R/W-1/1 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|-----|---------|-----|---------|---------|---------|

| —     | —   | —   | ANSA4   | —   | ANSA2   | ANSA1   | ANSA0   |

| bit 7 |     |     |         |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                        |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | <ul> <li>ANSA4: Analog Select between Analog or Digital Function on pins RA4, respectively</li> <li>1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.</li> <li>0 = Digital I/O. Pin is assigned to port or digital special function.</li> </ul>                     |

| bit 3   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                        |

| bit 2-0 | <ul> <li>ANSA&lt;2:0&gt;: Analog Select between Analog or Digital Function on pins RA&lt;2:0&gt;, respectively</li> <li>1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.</li> <li>0 = Digital I/O. Pin is assigned to port or digital special function.</li> </ul> |

| Note 1: | When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.                                                                                                                                                         |

## 13.0 INTERRUPT-ON-CHANGE

The PORTA pins can be configured to operate as Interrupt-On-Change (IOC) pins. An interrupt can be generated by detecting a signal that has either a rising edge or a falling edge. Any individual PORTA pin, or combination of PORTA pins, can be configured to generate an interrupt. The interrupt-on-change module has the following features:

- Interrupt-on-Change enable (Master Switch)

- Individual pin configuration

- · Rising and falling edge detection

- Individual pin interrupt flags

Figure 13-1 is a block diagram of the IOC module.

### 13.1 Enabling the Module

To allow individual PORTA pins to generate an interrupt, the IOCIE bit of the INTCON register must be set. If the IOCIE bit is disabled, the edge detection on the pin will still occur, but an interrupt will not be generated.

### 13.2 Individual Pin Configuration

For each PORTA pin, a rising edge detector and a falling edge detector are present. To enable a pin to detect a rising edge, the associated IOCAPx bit of the IOCAP register is set. To enable a pin to detect a falling edge, the associated IOCANx bit of the IOCAN register is set.

A pin can be configured to detect rising and falling edges simultaneously by setting both the IOCAPx bit and the IOCANx bit of the IOCAP and IOCAN registers, respectively.

### 13.3 Interrupt Flags

The IOCAFx bits located in the IOCAF register are status flags that correspond to the Interrupt-on-change pins of PORTA. If an expected edge is detected on an appropriately enabled pin, then the status flag for that pin will be set, and an interrupt will be generated if the IOCIE bit is set. The IOCIF bit of the INTCON register reflects the status of all IOCAFx bits.

### 13.4 Clearing Interrupt Flags

The individual status flags, (IOCAFx bits), can be cleared by resetting them to zero. If another edge is detected during this clearing operation, the associated status flag will be set at the end of the sequence, regardless of the value actually being written.

In order to ensure that no detected edge is lost while clearing flags, only AND operations masking out known changed bits should be performed. The following sequence is an example of what should be performed.

### EXAMPLE 13-1: CLEARING INTERRUPT FLAGS (PORTA EXAMPLE)

MOVLW 0xff XORWF IOCAF, W ANDWF IOCAF, F

### 13.5 Operation in Sleep

The interrupt-on-change interrupt sequence will wake the device from Sleep mode, if the IOCIE bit is set.

If an edge is detected while in Sleep mode, the IOCAF register will be updated prior to the first instruction executed out of Sleep.

### 17.7 Register Definitions: DAC Control

### REGISTER 17-1: DACCON0: VOLTAGE REFERENCE CONTROL REGISTER 0

| R/W-0/0          | R/W-0/0                                                                                                                                                                                                                                        | R/W-0/0                                                                                                                                                                    | U-0 | R/W-0/0         | R/W-0/0              | U-0                 | U-0    |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------|----------------------|---------------------|--------|

| DACEN            | DACLPS                                                                                                                                                                                                                                         | DACOE                                                                                                                                                                      | _   | DACP            | SS<1:0>              | _                   | _      |

| bit 7            |                                                                                                                                                                                                                                                |                                                                                                                                                                            |     |                 |                      |                     | bit 0  |

| Legend:          |                                                                                                                                                                                                                                                |                                                                                                                                                                            |     |                 |                      |                     |        |

| R = Readable I   | bit                                                                                                                                                                                                                                            | W = Writable bi                                                                                                                                                            | t   | U = Unimpleme   | ented bit, read as ' | 0'                  |        |

| u = Bit is uncha | anged                                                                                                                                                                                                                                          | x = Bit is unkno                                                                                                                                                           | wn  | -n/n = Value at | POR and BOR/Va       | llue at all other F | Resets |

| '1' = Bit is set |                                                                                                                                                                                                                                                | '0' = Bit is clear                                                                                                                                                         | ed  |                 |                      |                     |        |

| bit 7            | DACEN: DAC Enable bit<br>1 = DAC is enabled<br>0 = DAC is disabled                                                                                                                                                                             |                                                                                                                                                                            |     |                 |                      |                     |        |

| bit 6            | 1 = DAC Posi                                                                                                                                                                                                                                   | <ul> <li>DACLPS: DAC Low-Power Voltage State Select bit</li> <li>1 = DAC Positive reference source selected</li> <li>0 = DAC Negative reference source selected</li> </ul> |     |                 |                      |                     |        |

| bit 5            | <ul> <li>DAC Negative reference source selected</li> <li>DACOE: DAC Voltage Output Enable bit</li> <li>1 = DAC voltage level is also an output on the DACOUT pin</li> <li>0 = DAC voltage level is disconnected from the DACOUT pin</li> </ul> |                                                                                                                                                                            |     |                 |                      |                     |        |

| bit 4            | Unimplemente                                                                                                                                                                                                                                   | ed: Read as '0'                                                                                                                                                            |     |                 |                      |                     |        |

| bit 3-2          | DACPSS<1:0>: DAC Positive Source Select bits<br>11 = Reserved, do not use<br>10 = FVR Buffer2 output<br>01 = VREF pin<br>00 = VDD                                                                                                              |                                                                                                                                                                            |     |                 |                      |                     |        |

| bit 1-0          | Unimplemente                                                                                                                                                                                                                                   | ed: Read as '0'                                                                                                                                                            |     |                 |                      |                     |        |

### REGISTER 17-2: DACCON1: VOLTAGE REFERENCE CONTROL REGISTER 1

| U-0   | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0   | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|---------|---------|-----------|---------|---------|

| —     | —   | —   |         |         | DACR<4:0> |         |         |

| bit 7 |     |     |         |         |           |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 DACR<4:0>: DAC Voltage Output Select bits

### TABLE 17-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE DAC MODULE

| Name    | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2     | Bit 1 | Bit 0  | Register<br>on page |

|---------|-------|--------|-------|-------|-------|-----------|-------|--------|---------------------|

| FVRCON  | FVREN | FVRRDY | TSEN  | TSRNG | CDAFV | R<1:0>    | ADFVF | R<1:0> | 111                 |

| DACCON0 | DACEN | DACLPS | DACOE | _     | DACPS | S<1:0>    |       | _      | 130                 |

| DACCON1 | —     |        | _     |       |       | DACR<4:0> |       |        | 130                 |

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the DAC module.

| R/W-0/0          | R/W-0/0                                                                                                                                  | R/W-0/0                              | R/W-0/0                                                                                                 | R/W-0/0         | R/W-0/0           | R/W-0/0          | R/W-0/0      |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------|-------------------|------------------|--------------|--|--|

| SRSPE            | SRSCKE                                                                                                                                   | Reserved                             | SRSC1E                                                                                                  | SRRPE           | SRRCKE            | Reserved         | SRRC1E       |  |  |

| bit 7            |                                                                                                                                          |                                      |                                                                                                         |                 |                   |                  | bit 0        |  |  |

|                  |                                                                                                                                          |                                      |                                                                                                         |                 |                   |                  |              |  |  |

| Legend:          |                                                                                                                                          |                                      |                                                                                                         |                 |                   |                  |              |  |  |

| R = Readable     | bit                                                                                                                                      | W = Writable                         | bit                                                                                                     | U = Unimpler    | mented bit, read  | d as '0'         |              |  |  |

| u = Bit is unch  | anged                                                                                                                                    | x = Bit is unkr                      | nown                                                                                                    | -n/n = Value a  | at POR and BO     | R/Value at all o | other Resets |  |  |

| '1' = Bit is set |                                                                                                                                          | '0' = Bit is cle                     | ared                                                                                                    |                 |                   |                  |              |  |  |

|                  |                                                                                                                                          |                                      |                                                                                                         |                 |                   |                  |              |  |  |

| bit 7            | SRSPE: SR                                                                                                                                | Latch Periphera                      | al Set Enable b                                                                                         | pit             |                   |                  |              |  |  |

|                  |                                                                                                                                          | is set when the                      |                                                                                                         |                 |                   |                  |              |  |  |

|                  | •                                                                                                                                        | has no effect or                     |                                                                                                         | of the SR latch | l                 |                  |              |  |  |

| bit 6            |                                                                                                                                          | R Latch Set Clo                      |                                                                                                         |                 |                   |                  |              |  |  |

|                  |                                                                                                                                          | t of SR latch is<br>nas no effect or |                                                                                                         |                 |                   |                  |              |  |  |

| h:4 <b>F</b>     |                                                                                                                                          |                                      | •                                                                                                       |                 |                   |                  |              |  |  |

| bit 5            |                                                                                                                                          | ead as '0'. Mai                      |                                                                                                         | ear.            |                   |                  |              |  |  |

| bit 4            | ••••••                                                                                                                                   | R Latch C1 Set                       |                                                                                                         |                 |                   |                  |              |  |  |

|                  |                                                                                                                                          |                                      | set when the C1 Comparator output is high<br>ator output has no effect on the set input of the SR latch |                 |                   |                  |              |  |  |

| bit 3            | -                                                                                                                                        | Latch Periphera                      |                                                                                                         | •               |                   |                  |              |  |  |

| DIL 3            |                                                                                                                                          | •                                    |                                                                                                         |                 |                   |                  |              |  |  |

|                  | <ul> <li>1 = SR latch is reset when the SRI pin is high</li> <li>0 = SRI pin has no effect on the reset input of the SR latch</li> </ul> |                                      |                                                                                                         |                 |                   |                  |              |  |  |

| bit 2            | •                                                                                                                                        | R Latch Reset (                      | •                                                                                                       |                 |                   |                  |              |  |  |

|                  | 1 = Reset in                                                                                                                             | put of SR latch                      | is pulsed with                                                                                          | SRCLK           |                   |                  |              |  |  |

|                  |                                                                                                                                          | has no effect or                     |                                                                                                         |                 | ch                |                  |              |  |  |

| bit 1            | Reserved: R                                                                                                                              | ead as '0'. Mai                      | ntain this bit cl                                                                                       | ear.            |                   |                  |              |  |  |

| bit 0            | SRRC1E: SF                                                                                                                               | R Latch C1 Res                       | et Enable bit                                                                                           |                 |                   |                  |              |  |  |

|                  | 1 = SR latch                                                                                                                             | is reset when t                      | the C1 Compa                                                                                            | rator output is | high              |                  |              |  |  |

|                  |                                                                                                                                          |                                      |                                                                                                         |                 | ut of the SR late | ch               |              |  |  |

|                  |                                                                                                                                          |                                      |                                                                                                         |                 |                   |                  |              |  |  |

### REGISTER 18-2: SRCON1: SR LATCH CONTROL 1 REGISTER

### TABLE 18-2: SUMMARY OF REGISTERS ASSOCIATED WITH SR LATCH MODULE

| Name   | Bit 7 | Bit 6      | Bit 5    | Bit 4  | Bit 3  | Bit 2  | Bit 1    | Bit 0  | Register<br>on Page |

|--------|-------|------------|----------|--------|--------|--------|----------|--------|---------------------|

| SRCON0 | SRLEN | SRCLK<2:0> |          |        | SRQEN  | SRNQEN | SRPS     | SRPR   | 133                 |

| SRCON1 | SRSPE | SRSCKE     | Reserved | SRSC1E | SRRPE  | SRRCKE | Reserved | SRRC1E | 134                 |

| TRISA  | _     |            | TRISA5   | TRISA4 | TRISA3 | TRISA2 | TRISA1   | TRISA0 | 102                 |

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the SR Latch module.

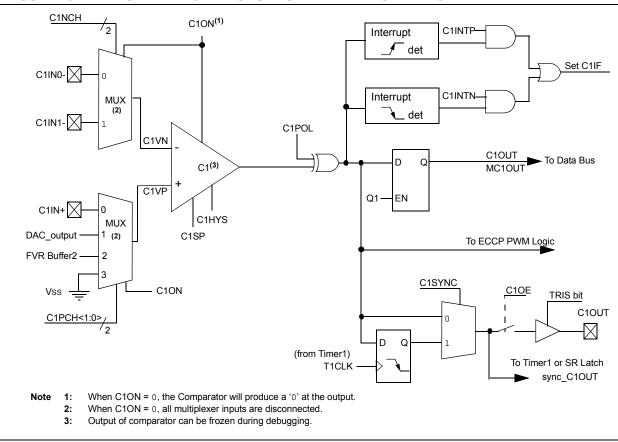

### FIGURE 19-2: COMPARATOR 1 MODULE SIMPLIFIED BLOCK DIAGRAM

### 24.3 PWM Overview

Pulse-Width Modulation (PWM) is a scheme that provides power to a load by switching quickly between fully on and fully off states. The PWM signal resembles a square wave where the high portion of the signal is considered the on state and the low portion of the signal is considered the off state. The high portion, also known as the pulse width, can vary in time and is defined in steps. A larger number of steps applied, which lengthens the pulse width, also supplies more power to the load. Lowering the number of steps applied, which shortens the pulse width, supplies less power. The PWM period is defined as the duration of one complete cycle or the total amount of on and off time combined.

PWM resolution defines the maximum number of steps that can be present in a single PWM period. A higher resolution allows for more precise control of the pulse width time and in turn the power that is applied to the load.

The term duty cycle describes the proportion of the on time to the off time and is expressed in percentages, where 0% is fully off and 100% is fully on. A lower duty cycle corresponds to less power applied and a higher duty cycle corresponds to more power applied.

Figure 24-3 shows a typical waveform of the PWM signal.

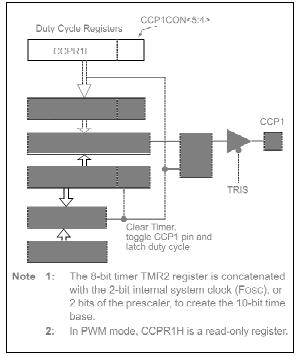

#### 24.3.1 STANDARD PWM OPERATION

The standard PWM mode generates a Pulse-Width Modulation (PWM) signal on the CCP1 pin with up to 10 bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- · PR2 registers

- T2CON registers

- · CCPR1L registers

- · CCP1CON registers

Figure 24-4 shows a simplified block diagram of PWM operation.

- Note 1: The corresponding TRIS bit must be cleared to enable the PWM output on the CCP1 pin.

- **2:** Clearing the CCP1CON register will relinquish control of the CCP1 pin.

#### FIGURE 24-3: CCP1 PWM OUTPUT SIGNAL

#### SIMPLIFIED PWM BLOCK DIAGRAM

## 24.5 Register Definitions: CCP Control

### REGISTER 24-1: CCP1CON: CCP1 CONTROL REGISTER

| R/W-00           | R/W-0/0                                                                                 | R/W-0/0                                                                                                                           | R/W-0/0         | R/W-0/0            | R/W-0/0            | R/W-0/0   | R/W-0/0 |  |  |

|------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------|--------------------|-----------|---------|--|--|

| P1N              | P1M<1:0> DC1B<1:0>                                                                      |                                                                                                                                   | 8<1:0>          |                    | CCP1I              | vl<3:0>   |         |  |  |

| bit 7            |                                                                                         |                                                                                                                                   |                 |                    |                    |           | bit (   |  |  |

| Legend:          |                                                                                         |                                                                                                                                   |                 |                    |                    |           |         |  |  |

| R = Readable     | bit                                                                                     | W = Writable bi                                                                                                                   | t               | U = Unimpleme      | ented bit, read as | · 'O'     |         |  |  |

| u = Bit is unch  |                                                                                         | x = Bit is unkno                                                                                                                  |                 | •                  | POR and BOR/\      |           | Reset   |  |  |

| '1' = Bit is set |                                                                                         | '0' = Bit is clear                                                                                                                |                 |                    |                    |           |         |  |  |

|                  |                                                                                         |                                                                                                                                   |                 |                    |                    |           |         |  |  |

| bit 7-6          | <b>P1M&lt;1:0&gt;:</b> En                                                               | hanced PWM Ou                                                                                                                     | tput Configurat | ion bits           |                    |           |         |  |  |

|                  | Capture mode:                                                                           |                                                                                                                                   |                 |                    |                    |           |         |  |  |

|                  | Unused                                                                                  |                                                                                                                                   |                 |                    |                    |           |         |  |  |

|                  | <u>Compare mode</u><br>Unused                                                           | <u>e:</u>                                                                                                                         |                 |                    |                    |           |         |  |  |

|                  | PWM mode:                                                                               |                                                                                                                                   |                 |                    |                    |           |         |  |  |

|                  |                                                                                         | <u>2&gt; = 00,01,10:</u>                                                                                                          | ( <b>2</b> )    |                    | (4)                |           |         |  |  |

|                  |                                                                                         | •                                                                                                                                 | re/Compare inp  | out; P1B assigned  | as port pins(")    |           |         |  |  |

|                  | <u>If CCP1M&lt;3:</u><br>11 = Reserv                                                    |                                                                                                                                   |                 |                    |                    |           |         |  |  |

|                  |                                                                                         |                                                                                                                                   | , P1B modulate  | d with dead-band   | control            |           |         |  |  |

|                  | 01 = Reserv                                                                             |                                                                                                                                   |                 |                    | _                  |           |         |  |  |

|                  | 00 = Single output; P1A modulated; P1B assigned as port pins                            |                                                                                                                                   |                 |                    |                    |           |         |  |  |

| bit 5-4          | DC1B<1:0>: PWM Duty Cycle Least Significant bits                                        |                                                                                                                                   |                 |                    |                    |           |         |  |  |

|                  | <u>Capture mode:</u><br>Unused                                                          |                                                                                                                                   |                 |                    |                    |           |         |  |  |

|                  | Compare mode                                                                            | Compare mode:                                                                                                                     |                 |                    |                    |           |         |  |  |

|                  | Unused                                                                                  |                                                                                                                                   |                 |                    |                    |           |         |  |  |

|                  | PWM mode:                                                                               |                                                                                                                                   |                 |                    |                    |           |         |  |  |

|                  |                                                                                         |                                                                                                                                   | -               | cycle. The eight M | Sbs are found in   | CCPR1L.   |         |  |  |

| bit 3-0          | CCP1M<3:0>:                                                                             | ECCP1 Mode Se                                                                                                                     | elect bits      |                    |                    |           |         |  |  |

|                  |                                                                                         | 11 = Compare mode: Special Event Trigger (CCP1 resets Timer, sets CCP1IF bit, and starts ADC conversion if ADC module is enabled) |                 |                    |                    |           |         |  |  |

|                  |                                                                                         |                                                                                                                                   | ,               | terrupt only; ECCI | P1 pin reverts to  | I/O state |         |  |  |

|                  | •                                                                                       |                                                                                                                                   | •               | high; clear output | •                  | · · · · · |         |  |  |

|                  | 1000 = Compare mode: initialize ECCP1 pin low; set output on compare match (set CCP1IF) |                                                                                                                                   |                 |                    |                    |           |         |  |  |

|                  | 0111 = Captu                                                                            | ure mode: every 1                                                                                                                 | 6th risina edae | 2                  |                    |           |         |  |  |

|                  |                                                                                         | ure mode: every 4                                                                                                                 |                 |                    |                    |           |         |  |  |

|                  | •                                                                                       | ure mode: every r                                                                                                                 |                 |                    |                    |           |         |  |  |

|                  | 0100 = Captu                                                                            | ure mode: every f                                                                                                                 | alling edge     |                    |                    |           |         |  |  |

|                  | 0011 = Rese                                                                             | rved                                                                                                                              |                 |                    |                    |           |         |  |  |

|                  |                                                                                         | pare mode: toggle                                                                                                                 | e output on mat | ch                 |                    |           |         |  |  |

|                  | 0001 = Rese                                                                             |                                                                                                                                   |                 |                    |                    |           |         |  |  |

|                  | 0000 = Captu                                                                            | ure/Compare/PW                                                                                                                    | M off (resets E | CCP1 module)       |                    |           |         |  |  |

|                  | PWM mode:                                                                               |                                                                                                                                   |                 |                    |                    |           |         |  |  |

|                  |                                                                                         | mode: P1A activ                                                                                                                   | e-low; P1B act  | ive-low            |                    |           |         |  |  |

|                  | 1110 = PWM                                                                              | mode: P1A activ                                                                                                                   | e-low; P1B act  | ive-high           |                    |           |         |  |  |

|                  |                                                                                         | mode: P1A activ                                                                                                                   | -               |                    |                    |           |         |  |  |

|                  | 1100 = PWM                                                                              | mode: P1A activ                                                                                                                   | e-nigh; P1B ac  | tive-high          |                    |           |         |  |  |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ label ] BCF f,b                                                   |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                         |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label]BTFSC f,b                                                                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                               |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                              |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.<br>If bit 'b', in register 'f', is '0', the next instruction is discarded, and a NOP is executed instead, making this a 2-cycle instruction. |

| BRA              | Relative Branch                                                                                                                                                                                                                  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]BRA label<br>[ <i>label</i> ]BRA \$+k                                                                                                                                                                            |

| Operands:        | -256 $\leq$ label - PC + 1 $\leq$ 255 -256 $\leq$ k $\leq$ 255                                                                                                                                                                   |

| Operation:       | $(PC) + 1 + k \rightarrow PC$                                                                                                                                                                                                    |

| Status Affected: | None                                                                                                                                                                                                                             |

| Description:     | Add the signed 9-bit literal 'k' to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + $1 + k$ . This instruction is a 2-cycle instruction. This branch has a limited range. |

| BRW              | Relative Branch with W                                                                                                                                                                                            |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BRW                                                                                                                                                                                                     |

| Operands:        | None                                                                                                                                                                                                              |

| Operation:       | $(PC) + (W) \to PC$                                                                                                                                                                                               |

| Status Affected: | None                                                                                                                                                                                                              |

| Description:     | Add the contents of W (unsigned) to<br>the PC. Since the PC will have incre-<br>mented to fetch the next instruction,<br>the new address will be PC + 1 + (W).<br>This instruction is a 2-cycle instruc-<br>tion. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ label ] BSF f,b                                                   |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                         |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label]BTFSS f,b                                                                                                                                                                                                |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b < 7 \end{array}$                                                                                                                                                |  |  |  |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                         |  |  |  |

| Status Affected: | None                                                                                                                                                                                                            |  |  |  |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next<br>instruction is discarded and a NOP is<br>executed instead, making this a<br>2-cycle instruction. |  |  |  |

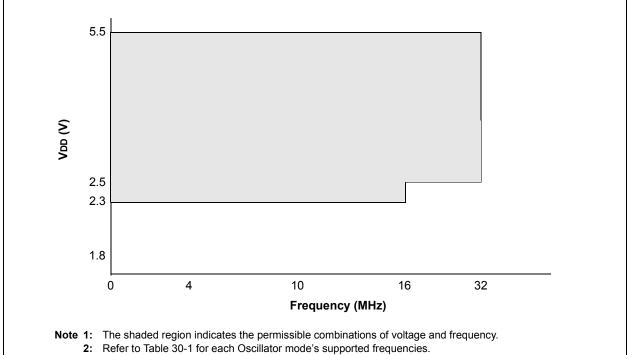

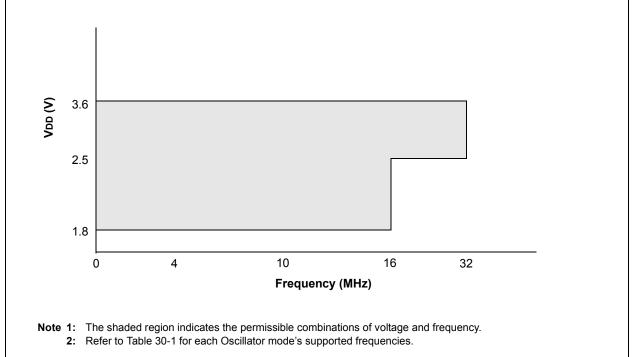

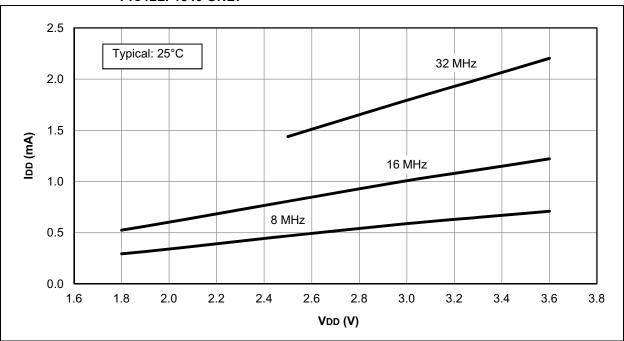

# **30.0 ELECTRICAL SPECIFICATIONS**

# Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias40°C to +125°C                                                                 |                                                                            |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|--|--|--|--|

| Storage temperature                                                                                          | 65°C to +150°C                                                             |  |  |  |  |  |

| Voltage on VDD with respect to Vss, PIC12F1840                                                               | 0.3V to +6.5V                                                              |  |  |  |  |  |

| Voltage on VDD with respect to Vss, PIC12LF1840                                                              | -0.3V to +4.0V                                                             |  |  |  |  |  |

| Voltage on MCLR with respect to Vss                                                                          | 0.3V to +9.0V                                                              |  |  |  |  |  |

| Voltage on all other pins with respect to Vss                                                                |                                                                            |  |  |  |  |  |

| Total power dissipation <sup>(1)</sup> 800 mV                                                                |                                                                            |  |  |  |  |  |

| Maximum current out of Vss pin, -40°C $\leq$ TA $\leq$ +85°C for industrial                                  | aximum current out of Vss pin, -40°C $\leq$ TA $\leq$ +85°C for industrial |  |  |  |  |  |

| Maximum current out of Vss pin, -40°C $\leq$ Ta $\leq$ +125°C for extended                                   |                                                                            |  |  |  |  |  |

| Maximum current into VDD pin, -40°C $\leq$ TA $\leq$ +85°C for industrial                                    |                                                                            |  |  |  |  |  |

| Maximum current into VDD pin, -40°C $\leq$ TA $\leq$ +125°C for extended                                     |                                                                            |  |  |  |  |  |

| Clamp current, Ik (VPIN < 0 or VPIN > VDD)                                                                   | ± 20 mA                                                                    |  |  |  |  |  |

| Maximum output current sunk by any I/O pin                                                                   |                                                                            |  |  |  |  |  |

| Maximum output current sourced by any I/O pin                                                                | 25 mA                                                                      |  |  |  |  |  |

| <b>Note 1:</b> Power dissipation is calculated as follows: PDIS = VDD x {IDD $-\Sigma$ IOH} + $\Sigma$ {(VDD | – Voh) x Ioh} + $\Sigma$ (Vol x Iol).                                      |  |  |  |  |  |