# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 5                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                              |

| Data Converters            | A/D 4x10b; D/A 1x5b                                                      |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 8-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f1840-i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

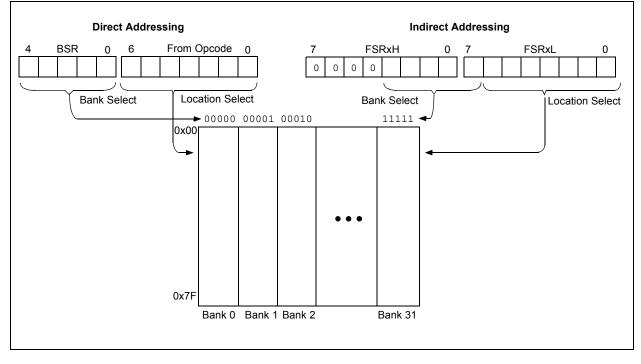

#### 3.6.1 TRADITIONAL DATA MEMORY

The traditional data memory is a region from FSR address 0x000 to FSR address 0xFFF. The addresses correspond to the absolute addresses of all SFR, GPR and common registers.

#### FIGURE 3-9: TRADITIONAL DATA MEMORY MAP

#### **Register Definitions: EEPROM and Flash Control** 11.7

#### REGISTER 11-1: EEDATL: EEPROM DATA LOW BYTE REGISTER

| R/W-x/u            | R/W-x/u                                             | R/W-x/u              | R/W-x/u | R/W-x/u           | R/W-x/u         | R/W-x/u              | R/W-x/u |

|--------------------|-----------------------------------------------------|----------------------|---------|-------------------|-----------------|----------------------|---------|

|                    |                                                     |                      | EEDA    | T<7:0>            |                 |                      |         |

| bit 7              |                                                     |                      |         |                   |                 |                      | bit 0   |

|                    |                                                     |                      |         |                   |                 |                      |         |

| Legend:            |                                                     |                      |         |                   |                 |                      |         |

| R = Readable bit   | R = Readable bit U = Unimplemented bit, read as '0' |                      |         |                   |                 |                      |         |

| u = Bit is unchang | ed                                                  | x = Bit is unknowr   | 1       | -n/n = Value at F | OR and BOR/Valu | ue at all other Rese | ets     |

| '1' = Bit is set   |                                                     | '0' = Bit is cleared |         |                   |                 |                      |         |

bit 7-0

#### EEDAT<7:0>: Read/write value for EEPROM data byte or Least Significant bits of program memory

#### REGISTER 11-2: EEDATH: EEPROM DATA HIGH BYTE REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u     | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |

|-------|-----|---------|-------------|---------|---------|---------|---------|--|

| —     | _   |         | EEDAT<13:8> |         |         |         |         |  |

| bit 7 |     |         |             |         |         |         | bit 0   |  |

|       |     |         |             |         |         |         |         |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 EEDAT<13:8>: Read/write value for Most Significant bits of program memory

#### REGISTER 11-3: EEADRL: EEPROM ADDRESS REGISTER

| R/W-0/0    | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|------------|---------|---------|---------|---------|---------|---------|---------|--|

| EEADR<7:0> |         |         |         |         |         |         |         |  |

| bit 7      |         |         |         |         |         |         | bit 0   |  |

|            |         |         |         |         |         |         |         |  |

| Legend:    |         |         |         |         |         |         |         |  |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 EEADR<7:0>: Specifies the Least Significant bits for program memory address or EEPROM address

#### REGISTER 11-4: EEADRH: EEPROM ADDRESS HIGH BYTE REGISTER

| U-1   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|---------|-------------|---------|---------|---------|

| (1)   |         |         |         | EEADR<14:8> |         |         |         |

| bit 7 |         |         |         |             |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 Unimplemented: Read as '1'

EEADR<14:8>: Specifies the Most Significant bits for program memory address or EEPROM address bit 6-0

Note 1: Unimplemented, read as '1'.

R/W-x/u LATA0

bit 0

| U-0   | U-0 | R/W-x/u | R/W-x/u | U-0 | R/W-x/u | R/W-x/u | _ |

|-------|-----|---------|---------|-----|---------|---------|---|

| —     | —   | LATA5   | LATA4   | —   | LATA2   | LATA1   |   |

| bit 7 |     |         |         |     |         |         |   |

#### REGISTER 12-4: LATA: PORTA DATA LATCH REGISTER

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Unimplemented: Read as '0'                                |

|---------|-----------------------------------------------------------|

| bit 5-4 | LATA<5:4>: RA<5:4> Output Latch Value bits <sup>(1)</sup> |

| bit 3   | Unimplemented: Read as '0'                                |

| bit 2-0 | LATA<2:0>: RA<2:0> Output Latch Value bits <sup>(1)</sup> |

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

#### REGISTER 12-5: ANSELA: PORTA ANALOG SELECT REGISTER

| U-0   | U-0 | U-0 | R/W-1/1 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|-----|---------|-----|---------|---------|---------|

| —     | —   | —   | ANSA4   | —   | ANSA2   | ANSA1   | ANSA0   |

| bit 7 |     |     |         |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                        |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | <ul> <li>ANSA4: Analog Select between Analog or Digital Function on pins RA4, respectively</li> <li>1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.</li> <li>0 = Digital I/O. Pin is assigned to port or digital special function.</li> </ul>                     |

| bit 3   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                        |

| bit 2-0 | <ul> <li>ANSA&lt;2:0&gt;: Analog Select between Analog or Digital Function on pins RA&lt;2:0&gt;, respectively</li> <li>1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.</li> <li>0 = Digital I/O. Pin is assigned to port or digital special function.</li> </ul> |

| Note 1: | When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.                                                                                                                                                         |

## 14.3 Register Definitions: FVR Control

| R/W-0/0         | R-q/q                                        | R/W-0/0                                                    | R/W-0/0                                         | R/W-0/0                                                                                     | R/W-0/0                                                                                      | R/W-0/0                                               | R/W-0/0                                  |

|-----------------|----------------------------------------------|------------------------------------------------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------------------------------|

| FVREN           | FVRRDY <sup>(1)</sup>                        | TSEN                                                       | TSRNG                                           | CDAF                                                                                        | VR<1:0>                                                                                      | ADFV                                                  | R<1:0>                                   |

| bit 7           |                                              |                                                            |                                                 |                                                                                             |                                                                                              |                                                       | bit (                                    |

|                 |                                              |                                                            |                                                 |                                                                                             |                                                                                              |                                                       |                                          |

| Legend:         |                                              |                                                            |                                                 |                                                                                             |                                                                                              |                                                       |                                          |

| R = Readable    |                                              | W = Writable                                               |                                                 |                                                                                             | mented bit, read                                                                             |                                                       |                                          |

| u = Bit is und  | •                                            | x = Bit is unki                                            | nown                                            | -n/n = Value a                                                                              | at POR and BO                                                                                | R/Value at all o                                      | ther Resets                              |

| '1' = Bit is se | t                                            | '0' = Bit is cle                                           | ared                                            | q = Value der                                                                               | pends on condit                                                                              | ion                                                   |                                          |

| bit 7           | 1 = Fixed Vo                                 | d Voltage Refe<br>Itage Referenc                           | e is enabled                                    | bit                                                                                         |                                                                                              |                                                       |                                          |

|                 | 0 = Fixed Vo                                 | Itage Referenc                                             | e is disabled                                   |                                                                                             |                                                                                              |                                                       |                                          |

| bit 6           | 1 = Fixed Vo                                 | ed Voltage Re<br>Itage Referenc<br>Itage Referenc          | e output is rea                                 |                                                                                             | enabled                                                                                      |                                                       |                                          |

| bit 5           | 1 = Tempera                                  | erature Indicato<br>ture Indicator is<br>ture Indicator is | s enabled                                       | 3)                                                                                          |                                                                                              |                                                       |                                          |

| bit 4           | <b>TSRNG:</b> Tem<br>1 = VOUT = V            | perature Indica<br>/DD - 4VT (High<br>/DD - 2VT (Low       | ator Range Se<br>I Range)                       | election bit                                                                                |                                                                                              |                                                       |                                          |

| bit 3-2         | 11 = Compar<br>10 = Compar<br>01 = Compar    | ator, DAC and<br>ator, DAC and<br>ator, DAC and            | CPS module<br>CPS module<br>CPS module          | Fixed Voltage F<br>Fixed Voltage F<br>Fixed Voltage I                                       | ference Selectio<br>Reference Perip<br>Reference Perip<br>Reference Perip<br>Reference Perip | heral output is<br>heral output is<br>heral output is | 2x (2.048V) <sup>(2</sup><br>1x (1.024V) |

| bit 1-0         | 11 = ADC Fix<br>10 = ADC Fix<br>01 = ADC Fix | ed Voltage Re<br>ed Voltage Re<br>ed Voltage Re            | ference Perip<br>ference Perip<br>ference Perip | nce Selection I<br>heral output is<br>heral output is<br>heral output is<br>heral output is | 4x (4.096V) <sup>(2)</sup><br>2x (2.048V) <sup>(2)</sup><br>1x (1.024V)                      |                                                       |                                          |

|                 | VRRDY is always                              |                                                            | •                                               | ם סע                                                                                        |                                                                                              |                                                       |                                          |

2: Fixed Voltage Reference output cannot exceed VDD.

3: See Section 15.0 "Temperature Indicator Module" for additional information.

#### TABLE 14-2: SUMMARY OF REGISTERS ASSOCIATED WITH FIXED VOLTAGE REFERENCE

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0  | Register<br>on page |

|--------|-------|--------|-------|-------|-------|--------|-------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | CDAFV | R<1:0> | ADFVF | ۲<1:0> | 111                 |

Legend: Shaded cells are unused by the Fixed Voltage Reference module.

#### 16.2 ADC Operation

#### 16.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/ DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

| Note: | The GO/DONE bit should not be set in the |

|-------|------------------------------------------|

|       | same instruction that turns on the ADC.  |

|       | Refer to Section 16.2.6 "ADC Conver-     |

|       | sion Procedure".                         |

#### 16.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- · Set the ADIF Interrupt Flag bit

- Update the ADRESH and ADRESL registers with new conversion result

#### 16.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH and ADRESL registers will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

Note: A device Reset forces all registers to their Reset state. Thus, the ADC module is turned off and any pending conversion is terminated.

#### 16.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC oscillator source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

#### 16.2.5 SPECIAL EVENT TRIGGER

The Special Event Trigger of the CCPx/ECCPX module allows periodic ADC measurements without software intervention. When this trigger occurs, the GO/DONE bit is set by hardware and the Timer1 counter resets to zero.

#### TABLE 16-2: SPECIAL EVENT TRIGGER

| Device        | ECCP1 |

|---------------|-------|

| PIC12(L)F1840 | ECCP1 |

Using the Special Event Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

Refer to Section 24.0 "Capture/Compare/PWM Modules" for more information.

#### 17.7 Register Definitions: DAC Control

#### REGISTER 17-1: DACCON0: VOLTAGE REFERENCE CONTROL REGISTER 0

| R/W-0/0          | R/W-0/0                                                                                                                                                                                        | R/W-0/0                                                                                                                                                                    | U-0 | R/W-0/0         | R/W-0/0              | U-0                 | U-0    |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------|----------------------|---------------------|--------|

| DACEN            | DACLPS                                                                                                                                                                                         | DACOE                                                                                                                                                                      | _   | DACP            | SS<1:0>              | _                   | _      |

| bit 7            |                                                                                                                                                                                                |                                                                                                                                                                            |     |                 |                      |                     | bit 0  |

| Legend:          |                                                                                                                                                                                                |                                                                                                                                                                            |     |                 |                      |                     |        |

| R = Readable I   | bit                                                                                                                                                                                            | W = Writable bi                                                                                                                                                            | t   | U = Unimpleme   | ented bit, read as ' | 0'                  |        |

| u = Bit is uncha | anged                                                                                                                                                                                          | x = Bit is unkno                                                                                                                                                           | wn  | -n/n = Value at | POR and BOR/Va       | llue at all other F | Resets |

| '1' = Bit is set |                                                                                                                                                                                                | '0' = Bit is clear                                                                                                                                                         | ed  |                 |                      |                     |        |

| bit 7            | 1 = DAC is en<br>0 = DAC is dis                                                                                                                                                                | DACEN: DAC Enable bit<br>1 = DAC is enabled<br>0 = DAC is disabled                                                                                                         |     |                 |                      |                     |        |

| bit 6            | 1 = DAC Posi                                                                                                                                                                                   | <ul> <li>DACLPS: DAC Low-Power Voltage State Select bit</li> <li>1 = DAC Positive reference source selected</li> <li>0 = DAC Negative reference source selected</li> </ul> |     |                 |                      |                     |        |

| bit 5            | <ul> <li>DACOE: DAC Voltage Output Enable bit</li> <li>1 = DAC voltage level is also an output on the DACOUT pin</li> <li>0 = DAC voltage level is disconnected from the DACOUT pin</li> </ul> |                                                                                                                                                                            |     |                 |                      |                     |        |

| bit 4            | Unimplemented: Read as '0'                                                                                                                                                                     |                                                                                                                                                                            |     |                 |                      |                     |        |

| bit 3-2          | DACPSS<1:0>: DAC Positive Source Select bits<br>11 = Reserved, do not use<br>10 = FVR Buffer2 output<br>01 = VREF pin<br>00 = VDD                                                              |                                                                                                                                                                            |     |                 |                      |                     |        |

| bit 1-0          | Unimplemente                                                                                                                                                                                   | ed: Read as '0'                                                                                                                                                            |     |                 |                      |                     |        |

#### REGISTER 17-2: DACCON1: VOLTAGE REFERENCE CONTROL REGISTER 1

| U-0   | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0   | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|---------|---------|-----------|---------|---------|

| —     | —   | —   |         |         | DACR<4:0> |         |         |

| bit 7 |     |     |         |         |           |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 DACR<4:0>: DAC Voltage Output Select bits

#### TABLE 17-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE DAC MODULE

| Name    | Bit 7 | Bit 6  | Bit 5 | Bit 4     | Bit 3 | Bit 2  | Bit 1 | Bit 0  | Register<br>on page |

|---------|-------|--------|-------|-----------|-------|--------|-------|--------|---------------------|

| FVRCON  | FVREN | FVRRDY | TSEN  | TSRNG     | CDAFV | R<1:0> | ADFVF | R<1:0> | 111                 |

| DACCON0 | DACEN | DACLPS | DACOE | _         | DACPS | S<1:0> |       | _      | 130                 |

| DACCON1 | —     |        | _     | DACR<4:0> |       |        |       | 130    |                     |

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the DAC module.

# 19.7 Comparator Negative Input Selection

The C1NCH bit of the CM1CON1 register directs one of two analog pins to the comparator inverting input.

**Note:** To use C1IN+ and C1INx- pins as analog input, the appropriate bits must be set in the ANSEL register and the corresponding TRIS bits must also be set to disable the output drivers.

#### **19.8 Comparator Response Time**

The comparator output is indeterminate for a period of time after the change of an input source or the selection of a new reference voltage. This period is referred to as the response time. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response time to a comparator input change. See the Comparator and Voltage Reference Specifications in **Section 30.0 "Electrical Specifications"** for more details.

#### 19.9 Interaction with ECCP Logic

The C1 comparator can be used as a general purpose comparator. The output can be brought out to the C1OUT pin. When the ECCP auto-shutdown is active it can use the comparator signal. If auto-restart is also enabled, the comparator can be configured as a closed loop analog feedback to the ECCP, thereby, creating an analog controlled PWM.

| Note: | When the comparator module is first         |

|-------|---------------------------------------------|

|       | initialized the output state is unknown.    |

|       | Upon initialization, the user should verify |

|       | the output state of the comparator prior to |

|       | relying on the result, primarily when using |

|       | the result in connection with other         |

|       | peripheral features, such as the ECCP       |

|       | Auto-Shutdown mode.                         |

#### 19.10 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 19-3. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and VSS. The analog input, therefore, must be between VSS and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

2: Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

|                                      | ••••                                           |                    |                      |                                            |             |                                              |               | •)                                    |              |                                       |                                                   |

|--------------------------------------|------------------------------------------------|--------------------|----------------------|--------------------------------------------|-------------|----------------------------------------------|---------------|---------------------------------------|--------------|---------------------------------------|---------------------------------------------------|

|                                      |                                                |                    |                      |                                            |             |                                              |               |                                       |              |                                       | - 7111111<br>4                                    |

| Omerani                              | 1                                              |                    |                      | ·<br>· · · · · · · · · · · · · · · · · · · |             |                                              |               | · · · · · · · · · · · · · · · · · · · |              |                                       |                                                   |

| 80X<br>(082° = 8<br>0X8 = 0)         | ·<br>·<br>·                                    |                    |                      |                                            |             |                                              |               |                                       |              |                                       |                                                   |

|                                      |                                                | •<br>•<br>•        | ,<br>,<br>,          | 5<br>2                                     | :<br>:      | s<br>2                                       | ,<br>,<br>,   | 2<br>6                                | :            | -<br>                                 |                                                   |

| 80%<br>(0%9° = 1)<br>ORE = 6)        |                                                |                    |                      | ļ                                          |             |                                              |               |                                       |              |                                       |                                                   |

| When the<br>SEP (BLF                 | 4<br>. <u></u><br>                             |                    | с<br>с<br>с          | <<br><<br><<br><                           | ,<br>,<br>, |                                              | с<br>С<br>С   | /<br>/<br>/                           | , ,<br>, ,   |                                       |                                                   |

| Maina                                | );<br>;<br>; ///////////////////////////////// |                    | \$<br>\$<br>5        | t<br>                                      | 8<br>{      | :<br>:<br>:                                  | \$<br>}       | 6<br>6<br>26. – J <sup>anar</sup>     | х<br>1. уч   | · · · · · · · · · · · · · · · · · · · |                                                   |

| \$90 ·····                           |                                                | 94 <u>, 68</u> 7.  | N 586.               | X 68 S.,                                   | N 58.4      |                                              | X. int X.     | X 88 -                                |              | <u>68 0</u>                           | *********<br>!>`````````````````````````````````` |

| S.C.                                 | ·<br>•<br>•                                    |                    |                      |                                            |             |                                              |               |                                       |              | 1999                                  | ,<br>;<br>                                        |

|                                      | с<br>с<br>С                                    | - 338 7<br>- 338 7 | < '9999999<br>5<br>5 | , 977777<br>,<br>,                         | . (4,4,4,4) |                                              | <             | , (4,4,4,4)<br>,<br>,                 | - 00<br>- 00 |                                       |                                                   |

| lopiń<br>Samola                      | 4<br>5<br>3                                    |                    |                      |                                            |             | :<br>, 14-<br>, 3                            | i<br>iy<br>i  | , 19.<br>                             |              |                                       |                                                   |

|                                      |                                                |                    | 2<br>2               | 2<br>2<br>3                                | 5<br>5<br>- | ,<br>,<br>,                                  | 2<br>2<br>2   | s<br>2                                | 5 5<br>5 5   |                                       |                                                   |

| - \$15\$P133P<br>Boberroupk<br>P138g | 4<br>5                                         | •                  | <<br><               | ,<br>,<br>,                                |             | :<br>:                                       | <<br><        | ,<br>,                                | · · ·        |                                       |                                                   |

| 899<br>882188 8<br>882188 8          | ;                                              | 2                  | s<br>s<br>s          | <<br><<br><                                |             | 2                                            | s<br>s<br>s   | <<br><<br><                           |              | 4.                                    |                                                   |

| -05090-3700020                       | 1                                              | (                  | 9<br>1.<br>1.        |                                            | 0<br>       | ,<br>,<br>,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 9<br>1.<br>1. | 5<br>                                 |              | ,                                     | <br>                                              |

| Sydes Collegen                       |                                                |                    |                      |                                            |             |                                              |               |                                       |              |                                       |                                                   |

| detection adave -                    |                                                |                    |                      |                                            |             |                                              |               |                                       |              |                                       |                                                   |

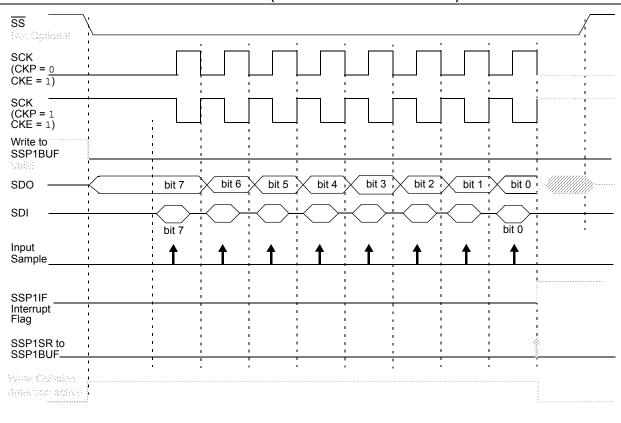

#### FIGURE 25-9: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 0)

#### FIGURE 25-10: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

#### 26.1.2.4 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error Status bit. A framing error indicates that a Stop bit was not seen at the expected time. The framing error status is accessed via the FERR bit of the RCSTA register. The FERR bit represents the status of the top unread character in the receive FIFO. Therefore, the FERR bit must be read before reading the RCREG.

The FERR bit is read-only and only applies to the top unread character in the receive FIFO. A framing error (FERR = 1) does not preclude reception of additional characters. It is not necessary to clear the FERR bit. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERR bit can be forced clear by clearing the SPEN bit of the RCSTA register which resets the EUSART. Clearing the CREN bit of the RCSTA register does not affect the FERR bit. A framing error by itself does not generate an interrupt.

| Note: | If all receive characters in the receive  |

|-------|-------------------------------------------|

|       | FIFO have framing errors, repeated reads  |

|       | of the RCREG will not clear the FERR bit. |

#### 26.1.2.5 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before the FIFO is accessed. When this happens the OERR bit of the RCSTA register is set. The characters already in the FIFO buffer can be read but no additional characters will be received until the error is cleared. The error must be cleared by either clearing the CREN bit of the RCSTA register or by resetting the EUSART by clearing the SPEN bit of the RCSTA register.

#### 26.1.2.6 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth and Most Significant data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

#### 26.1.2.7 Address Detection

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems. Address detection is enabled by setting the ADDEN bit of the RCSTA register.

Address detection requires 9-bit character reception. When address detection is enabled, only characters with the ninth data bit set will be transferred to the receive FIFO buffer, thereby setting the RCIF interrupt bit. All other characters will be ignored.

Upon receiving an address character, user software determines if the address matches its own. Upon address match, user software must disable address detection by clearing the ADDEN bit before the next Stop bit occurs. When user software detects the end of the message, determined by the message protocol used, software places the receiver back into the Address Detection mode by setting the ADDEN bit.

## 26.3 Register Definitions: EUSART Control

| R/W-/0           | R/W-0/0                                                                                           | R/W-0/0                                                      | R/W-0/0            | R/W-0/0         | R/W-0/0            | R-1/1             | R/W-0/0 |

|------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------|-----------------|--------------------|-------------------|---------|

| CSRC             | TX9                                                                                               | TXEN <sup>(1)</sup>                                          | SYNC               | SENDB           | BRGH               | TRMT              | TX9D    |

| bit 7            |                                                                                                   |                                                              | •                  |                 |                    |                   | bit     |

| Legend:          |                                                                                                   |                                                              |                    |                 |                    |                   |         |

| R = Readable     | bit                                                                                               | W = Writable b                                               | it                 | U = Unimpleme   | ented bit, read as | '0'               |         |

| u = Bit is unch  | anged                                                                                             | x = Bit is unkno                                             | wn                 | -n/n = Value at | POR and BOR/Va     | alue at all other | Resets  |

| '1' = Bit is set |                                                                                                   | '0' = Bit is clear                                           | ed                 |                 |                    |                   |         |

| bit 7            | Asynchronous<br>Don't care<br>Synchronous r<br>1 = Master n                                       |                                                              | rated internally f | from BRG)       |                    |                   |         |

| bit 6            | 1 = Selects 9                                                                                     | nsmit Enable bit<br>9-bit transmission<br>8-bit transmission |                    |                 |                    |                   |         |

| bit 5            | <b>TXEN:</b> Transn<br>1 = Transmit<br>0 = Transmit                                               |                                                              |                    |                 |                    |                   |         |

| bit 4            | SYNC: EUSAN<br>1 = Synchron<br>0 = Asynchron                                                      |                                                              | pit                |                 |                    |                   |         |

| bit 3            | Asynchronous<br>1 = Send Syr                                                                      | nc Break on next<br>ak transmission o                        | transmission (cl   | eared by hardwa | are upon completio | on)               |         |

| bit 2            | BRGH: High E<br>Asynchronous<br>1 = High sper<br>0 = Low spere<br>Synchronous I<br>Unused in this | ed<br>ed<br><u>mode:</u>                                     | bit                |                 |                    |                   |         |

| bit 1            |                                                                                                   | nit Shift Register \$                                        | Status bit         |                 |                    |                   |         |

| bit 0            | TX9D: Ninth b<br>Can be addres                                                                    | it of Transmit Dat                                           |                    |                 |                    |                   |         |

## REGISTER 26-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER

#### 26.5 EUSART Synchronous Mode

Synchronous serial communications are typically used in systems with a single master and one or more slaves. The master device contains the necessary circuitry for baud rate generation and supplies the clock for all devices in the system. Slave devices can take advantage of the master clock by eliminating the internal clock generation circuitry.

There are two signal lines in Synchronous mode: a bidirectional data line and a clock line. Slaves use the external clock supplied by the master to shift the serial data into and out of their respective receive and transmit shift registers. Since the data line is bidirectional, synchronous operation is half-duplex only. Half-duplex refers to the fact that master and slave devices can receive and transmit data but not both simultaneously. The EUSART can operate as either a master or slave device.

Start and Stop bits are not used in synchronous transmissions.

#### 26.5.1 SYNCHRONOUS MASTER MODE

The following bits are used to configure the EUSART for synchronous master operation:

- SYNC = 1

- CSRC = 1

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Setting the CSRC bit of the TXSTA register configures the device as a master. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART.

#### 26.5.1.1 Master Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a master transmits the clock on the TX/CK line. The TX/CK pin output driver is automatically enabled when the EUSART is configured for synchronous transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One clock cycle is generated for each data bit. Only as many clock cycles are generated as there are data bits.

#### 26.5.1.2 Clock Polarity

A clock polarity option is provided for Microwire compatibility. Clock polarity is selected with the SCKP bit of the BAUDCON register. Setting the SCKP bit sets the clock Idle state as high. When the SCKP bit is set, the data changes on the falling edge of each clock. Clearing the SCKP bit sets the Idle state as low. When the SCKP bit is cleared, the data changes on the rising edge of each clock.

26.5.1.3 Synchronous Master Transmission

Data is transferred out of the device on the RX/DT pin. The RX/DT and TX/CK pin output drivers are automatically enabled when the EUSART is configured for synchronous master transmit operation.

A transmission is initiated by writing a character to the TXREG register. If the TSR still contains all or part of a previous character the new character data is held in the TXREG until the last bit of the previous character has been transmitted. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR. The transmission of the character commences immediately following the transfer of the data to the TSR from the TXREG.

Each data bit changes on the leading edge of the master clock and remains valid until the subsequent leading clock edge.

Note: The TSR register is not mapped in data memory, so it is not available to the user.

- 26.5.1.4 Synchronous Master Transmission Set-up:

- 1. Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 26.4 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Disable Receive mode by clearing bits SREN and CREN.

- 4. Enable Transmit mode by setting the TXEN bit.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in the TX9D bit.

- 8. Start transmission by loading data to the TXREG register.

| RX/DT<br>pin<br>TX/CK pin<br>(SCKP = 0)           |                                                                             |

|---------------------------------------------------|-----------------------------------------------------------------------------|

| TX/CK pin<br>(SCKP = 1)<br>Write to<br>bit SREN   |                                                                             |

| SREN bit                                          | <u>'0'</u>                                                                  |

| RCIF bit<br>(Interrupt) ———<br>Read<br>RCREG ———— |                                                                             |

|                                                   | gram demonstrates Sync Master mode with bit SREN = $1$ and bit BRGH = $0$ . |

#### FIGURE 26-12: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

# TABLE 26-8:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER<br/>RECEPTION

| Name    | Bit 7   | Bit 6     | Bit 5  | Bit 4      | Bit 3       | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |  |

|---------|---------|-----------|--------|------------|-------------|--------|--------|--------|---------------------|--|

| BAUDCON | ABDOVF  | RCIDL     |        | SCKP       | BRG16       | _      | WUE    | ABDEN  | 259                 |  |

| INTCON  | GIE     | PEIE      | TMR0IE | INTE       | IOCIE       | TMR0IF | INTF   | IOCIF  | 72                  |  |

| PIE1    | TMR1GIE | ADIE      | RCIE   | TXIE       | SSPIE       | CCP1IE | TMR2IE | TMR1IE | 73                  |  |

| PIR1    | TMR1GIF | ADIF      | RCIF   | TXIF       | SSPIF       | CCP1IF | TMR2IF | TMR1IF | 75                  |  |

| RCREG   |         |           | EUS    | ART Receiv | ve Data Reg | gister |        |        | 252*                |  |

| RCSTA   | SPEN    | RX9       | SREN   | CREN       | ADDEN       | FERR   | OERR   | RX9D   | 258                 |  |

| SPBRGL  |         | BRG<7:0>  |        |            |             |        |        |        |                     |  |

| SPBRGH  |         | BRG<15:8> |        |            |             |        |        |        |                     |  |

| TXSTA   | CSRC    | TX9       | TXEN   | SYNC       | SENDB       | BRGH   | TRMT   | TX9D   | 257                 |  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for Synchronous Master Reception. \* Page provides register information.

#### 26.5.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the EUSART for synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Clearing the CSRC bit of the TXSTA register configures the device as a slave. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART.

#### 26.5.2.1 EUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes are identical (see **Section 26.5.1.3 "Synchronous Master Transmission")**, except in the case of the Sleep mode. If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in TXREG register.

- 3. The TXIF bit will not be set.

- After the first character has been shifted out of TSR, the TXREG register will transfer the second character to the TSR and the TXIF bit will now be set.

- 5. If the PEIE and TXIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

- 26.5.2.2 Synchronous Slave Transmission Set-up:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for the CK pin (if applicable).

- 3. Clear the CREN and SREN bits.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. Enable transmission by setting the TXEN bit.

- 7. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 8. Start transmission by writing the Least Significant eight bits to the TXREG register.

#### TABLE 26-9: SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

| Name                                | Bit 7   | Bit 6 | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|-------------------------------------|---------|-------|--------|-------|-------|--------|--------|--------|---------------------|

| BAUDCON                             | ABDOVF  | RCIDL | —      | SCKP  | BRG16 | —      | WUE    | ABDEN  | 259                 |

| INTCON                              | GIE     | PEIE  | TMR0IE | INTE  | IOCIE | TMR0IF | INTF   | IOCIF  | 72                  |

| PIE1                                | TMR1GIE | ADIE  | RCIE   | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 73                  |

| PIR1                                | TMR1GIF | ADIF  | RCIF   | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 75                  |

| RCSTA                               | SPEN    | RX9   | SREN   | CREN  | ADDEN | FERR   | OERR   | RX9D   | 258                 |

| TXREG EUSART Transmit Data Register |         |       |        |       |       |        |        |        |                     |

| TXSTA                               | CSRC    | TX9   | TXEN   | SYNC  | SENDB | BRGH   | TRMT   | TX9D   | 257                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for Synchronous Slave Transmission. \* Page provides register information.

# 26.5.2.3 EUSART Synchronous Slave Reception

The operation of the Synchronous Master and Slave modes is identical (Section 26.5.1.5 "Synchronous Master Reception"), with the following exceptions:

- · Sleep

- CREN bit is always set, therefore the receiver is never idle

- SREN bit, which is a "don't care" in Slave mode

A character may be received while in Sleep mode by setting the CREN bit prior to entering Sleep. Once the word is received, the RSR register will transfer the data to the RCREG register. If the RCIE enable bit is set, the interrupt generated will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will branch to the interrupt vector.

- 26.5.2.4 Synchronous Slave Reception Set-up:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for both the CK and DT pins (if applicable).

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Set the CREN bit to enable reception.

- The RCIF bit will be set when reception is complete. An interrupt will be generated if the RCIE bit was set.

- 7. If 9-bit mode is enabled, retrieve the Most Significant bit from the RX9D bit of the RCSTA register.

- 8. Retrieve the eight Least Significant bits from the receive FIFO by reading the RCREG register.

- 9. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

| Name    | Bit 7   | Bit 6 | Bit 5  | Bit 4      | Bit 3      | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|---------|-------|--------|------------|------------|--------|--------|--------|---------------------|

| BAUDCON | ABDOVF  | RCIDL | —      | SCKP       | BRG16      | —      | WUE    | ABDEN  | 259                 |

| INTCON  | GIE     | PEIE  | TMR0IE | INTE       | IOCIE      | TMR0IF | INTF   | IOCIF  | 72                  |

| PIE1    | TMR1GIE | ADIE  | RCIE   | TXIE       | SSPIE      | CCP1IE | TMR2IE | TMR1IE | 73                  |

| PIR1    | TMR1GIF | ADIF  | RCIF   | TXIF       | SSPIF      | CCP1IF | TMR2IF | TMR1IF | 75                  |

| RCREG   |         |       | EUS    | ART Receiv | e Data Reg | gister |        |        | 252*                |

| RCSTA   | SPEN    | RX9   | SREN   | CREN       | ADDEN      | FERR   | OERR   | RX9D   | 258                 |

| TXSTA   | CSRC    | TX9   | TXEN   | SYNC       | SENDB      | BRGH   | TRMT   | TX9D   | 257                 |

## TABLE 26-10: SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used for Synchronous Slave Reception.

\* Page provides register information.

#### REGISTER 27-2: CPSCON1: CAPACITIVE SENSING CONTROL REGISTER 1

| U-0                               | U-0                                                | U-0               | U-0              | U-0                                | U-0                                      | R/W-0/0 | R/W-0/0 |  |  |  |  |

|-----------------------------------|----------------------------------------------------|-------------------|------------------|------------------------------------|------------------------------------------|---------|---------|--|--|--|--|

| _                                 | —                                                  | —                 | —                | —                                  | —                                        | H<1:0>  |         |  |  |  |  |

| bit 7                             |                                                    |                   |                  |                                    |                                          |         | bit 0   |  |  |  |  |

|                                   |                                                    |                   |                  |                                    |                                          |         |         |  |  |  |  |

| Legend:                           |                                                    |                   |                  |                                    |                                          |         |         |  |  |  |  |

| R = Readable bit W = Writable bit |                                                    |                   | bit              | U = Unimplemented bit, read as '0' |                                          |         |         |  |  |  |  |

| u = Bit is un                     | changed                                            | x = Bit is unkno  | own              | -n/n = Value a                     | at POR and BOR/Value at all other Resets |         |         |  |  |  |  |

| '1' = Bit is se                   | et                                                 | '0' = Bit is clea | ired             |                                    |                                          |         |         |  |  |  |  |

|                                   |                                                    |                   |                  |                                    |                                          |         |         |  |  |  |  |

| bit 7-2                           | Unimplemen                                         | ted: Read as '0'  |                  |                                    |                                          |         |         |  |  |  |  |

| bit 1-0                           | CPSCH<1:0>: Capacitive Sensing Channel Select bits |                   |                  |                                    |                                          |         |         |  |  |  |  |

|                                   | <u>If CPSON =</u>                                  | -                 |                  |                                    |                                          |         |         |  |  |  |  |

|                                   | These bit                                          | ts are ignored. N | lo channel is se | elected.                           |                                          |         |         |  |  |  |  |

If CPSON = 1:

- $\frac{11}{11} = \frac{11}{11}$

- 11 = channel 3, (CPS3) 10 = channel 2, (CPS2)

- 01 = channel 1, (CPS1)

- 00 = channel 0, (CPS0)

| Name       | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3   | Bit 2  | Bit 1      | Bit 0  | Register<br>on Page |

|------------|-------|--------|--------|--------|---------|--------|------------|--------|---------------------|

| ANSELA     | _     | _      | _      | ANSA4  | —       | ANSA2  | ANSA1      | ANSA0  | 103                 |

| CPSCON0    | CPSON | CPSRM  | -      |        | CPSRN   | G<1:0> | CPSOUT     | TOXCS  | 282                 |

| CPSCON1    | -     |        | _      | —      | —       | -      | CPSCH<1:0> |        | 283                 |

| INTCON     | GIE   | PEIE   | TMR0IE | INTE   | IOCIE   | TMR0IF | INTF       | IOCIF  | 72                  |

| OPTION_REG | WPUEN | INTEDG | TMR0CS | TMR0SE | PSA     |        | PS<2:0>    |        |                     |

| T1CON      | TMR1C | S<1:0> | T1CKP  | S<1:0> | T1OSCEN | T1SYNC | —          | TMR10N | 154                 |

| TRISA      | _     | _      | TRISA5 | TRISA4 | TRISA3  | TRISA2 | TRISA1     | TRISA0 | 102                 |

Legend: — = Unimplemented locations, read as '0'. Shaded cells are not used by the CPS module.

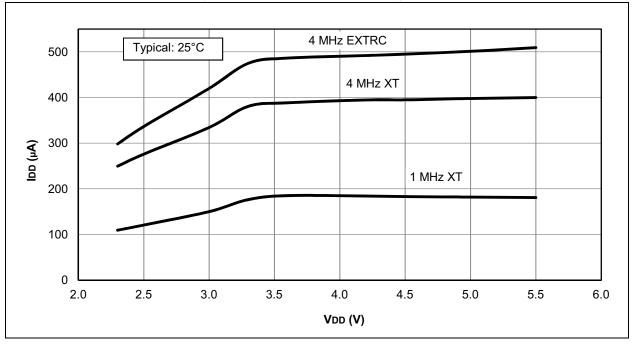

#### 30.3 DC Characteristics: Power-Down Base Current (IPD)

| PIC12LF1 | 840                     |                      | rd Opera<br>ng tempe | •     |        | TA ≤ +85 | herwise<br>5°C for inc<br>25°C for e | lustrial                                            |  |

|----------|-------------------------|----------------------|----------------------|-------|--------|----------|--------------------------------------|-----------------------------------------------------|--|

| PIC12F18 | 40                      |                      | rd Opera<br>ng tempe |       |        | TA ≤ +85 | herwise<br>5°C for inc<br>25°C for e | lustrial                                            |  |

| Param    | Device Characteristics  | Min.                 | Typt                 | Max.  | Max.   | Units    |                                      | Conditions                                          |  |

| No.      | Device Characteristics  | WIIII.               | וקעי                 | +85°C | +125°C | Units    | VDD                                  | Note                                                |  |

|          | Power-down Base Current | (IPD) <sup>(2)</sup> |                      |       |        |          |                                      |                                                     |  |

| D022     |                         | —                    | 0.02                 | 1.0   | 8.0    | μA       | 1.8                                  | WDT, BOR, FVR and T1OSC                             |  |

|          |                         | _                    | 0.03                 | 2.0   | 9.0    | μA       | 3.0                                  | disabled, all peripherals inactive                  |  |

| D022     |                         | _                    | 0.2                  | 1.3   | 10     | μA       | 2.3                                  | WDT, BOR, FVR and T1OSC                             |  |

|          |                         | _                    | 0.3                  | 2.0   | 12     | μA       | 3.0                                  | disabled, all peripherals inactive,                 |  |

|          |                         | —                    | 0.5                  | 6.0   | 15     | μA       | 5.0                                  | Low-power regulator active<br>VREGPM = 1            |  |

| D023     |                         | <b>—</b>             | 0.5                  | 6.0   | 14     | μA       | 1.8                                  | WDT Current (Note 1)                                |  |

|          |                         |                      | 0.8                  | 7.0   | 17     | μA       | 3.0                                  |                                                     |  |

| D023     |                         | _                    | 0.5                  | 6     | 15     | μA       | 2.3                                  | WDT Current                                         |  |

|          |                         | _                    | 0.8                  | 7     | 20     | μA       | 3.0                                  | VREGPM = 1 (Note 1)                                 |  |

|          |                         | _                    | 0.9                  | 8     | 22     | μA       | 5.0                                  | ]                                                   |  |

| D023A    |                         | _                    | 8.5                  | 23    | 25     | μA       | 1.8                                  | FVR Current (Note 1)                                |  |

|          |                         | _                    | 8.5                  | 24    | 27     | μA       | 3.0                                  |                                                     |  |

| D023A    |                         |                      | 18                   | 26    | 30     | μA       | 2.3                                  | FVR Current                                         |  |

|          |                         |                      | 19                   | 27    | 37     | μA       | 3.0                                  | VREGPM = 0 (Note 1)                                 |  |

|          |                         |                      | 20                   | 29    | 45     | μA       | 5.0                                  |                                                     |  |

| D024     |                         |                      | 8.0                  | 17    | 20     | μA       | 3.0                                  | BOR Current (Note 1)                                |  |

| D024     |                         |                      | 8.0                  | 17    | 30     | μA       | 3.0                                  | BOR Current                                         |  |

|          |                         | —                    | 9.0                  | 20    | 40     | μA       | 5.0                                  | VREGPM = 1 (Note 1)                                 |  |

| D025     |                         |                      | 0.3                  | 5     | 9      | μA       | 1.8                                  | T1OSC Current (Note 1)                              |  |

|          |                         |                      | 0.5                  | 9     | 12     | μA       | 3.0                                  |                                                     |  |

| D025     |                         |                      | 1.1                  | 6     | 10     | μA       | 2.3                                  | T1OSC Current                                       |  |

|          |                         |                      | 1.3                  | 9     | 20     | μA       | 3.0                                  | VREGPM = 1 (Note 1)                                 |  |

|          |                         | -                    | 1.4                  | 10    | 25     | μA       | 5.0                                  |                                                     |  |

| D026     |                         |                      | 0.1                  | 1.0   | 9      | μA       | 1.8                                  | ADC Current (Note 1, 3)                             |  |

|          |                         |                      | 0.1                  | 2.0   | 10     | μA       | 3.0                                  | No conversion in progress                           |  |

| D026     |                         |                      | 0.2                  | 3.0   | 10     | μA       | 2.3                                  | ADC Current                                         |  |

|          |                         |                      | 0.4                  | 4.0   | 11     | μA       | 3.0                                  | No conversion in progress<br>VREGPM = 1 (Note 1, 3) |  |

|          |                         | —                    | 0.5                  | 6.0   | 16     | μA       | 5.0                                  |                                                     |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral △ current can be determined by subtracting the base IDD or IPD current from this limit. Max. values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to Vss.

**3:** ADC clock source is FRC.

#### 30.4 DC Characteristics: I/O Ports (Continued)

| DC CHARACTERISTICS |       |                             | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature -40°C } \le Ta \leq +85°C \mbox{ for industrial} \\ -40°C \leq Ta \leq +125°C \mbox{ for extended} \end{array}$ |      |      |       |                                                                        |  |  |

|--------------------|-------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------------------------------------------------------------------|--|--|

| Param<br>No.       | Sym.  | Characteristic              | Min.                                                                                                                                                                                                                            | Тур† | Max. | Units | Conditions                                                             |  |  |